Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                         |

|---------------------------------|-------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                |

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.333GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                  |

| RAM Controllers                 | DDR2, DDR3                                                              |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                  |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                       |

| Package / Case                  | 1023-BBGA, FCBGA                                                        |

| Supplier Device Package         | 1023-FCPBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572clvjaule |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- Multiplexed 32-bit address and data bus operating at up to 150 MHz

- Eight chip selects support eight external slaves

- Up to 8-beat burst transfers

- The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller.

- Three protocol engines available on a per-chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- NAND Flash control machine (FCM)

- Parity support

- Default boot ROM chip select with configurable bus width (8, 16, or 32 bits)

- Four enhanced three-speed Ethernet controllers (eTSECs)

- Three-speed support (10/100/1000 Mbps)

- Four IEEE Std 802.3®, 802.3u, 802.3x, 802.3z, 802.3ac, 802.3ab-compatible controllers

- Support for various Ethernet physical interfaces:

- 1000 Mbps full-duplex IEEE 802.3 GMII, IEEE 802.3z TBI, RTBI, RGMII, and SGMII

- 10/100 Mbps full and half-duplex IEEE 802.3 MII, IEEE 802.3 RGMII, and RMII

- Flexible configuration for multiple PHY interface configurations

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (Q-in-Q) VLAN, 802.2, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Supported in all FIFO modes

- Quality of service support:

- Transmission from up to eight physical queues

- Reception to up to eight physical queues

- Full- and half-duplex Ethernet support (1000 Mbps supports only full duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE Std 802.1<sup>TM</sup> virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

#### Overview

- Ability to launch DMA from single write transaction

- Serial RapidIO interface unit

- Supports RapidIO Interconnect Specification, Revision 1.2

- Both 1x and 4x LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto-detection of 1x- and 4x-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO–compliant message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

- Single inbound doorbell message structure

- Facility to accept port-write messages

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

#### **NOTE**

From a system standpoint, if any of the I/O power supplies ramp prior to the VDD core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-on reset, and extra current may be drawn by the device.

## 3 Power Characteristics

The estimated typical power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III devices with out the L in its part ordering is shown in Table 4.

**Core Frequency** Typical-105<sup>3</sup> Maximum<sup>4</sup> **CCB Frequency** Typical-65<sup>2</sup> Unit 533 1067 12.3 17.8 18.5 533 1200 12.3 17.8 18.5 W 533 1333 22.8 W 16.3 24.5 600 1500 17.3 23.9 25.9 W

Table 4. MPC8572E Power Dissipation <sup>1</sup>

#### Notes:

The estimated typical power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III devices with the L in its port ordering is shown in Table 5.

| CCB Frequency | Core Frequency | Typical-65 <sup>2</sup> | Typical-105 <sup>3</sup> | Maximum <sup>4</sup> | Unit |

|---------------|----------------|-------------------------|--------------------------|----------------------|------|

| 533           | 1067           | 12                      | 15                       | 15.8                 | W    |

| 533           | 1200           | 12                      | 15.5                     | 16.3                 | W    |

| 533           | 1333           | 12                      | 15.9                     | 16.9                 | W    |

| 600           | 1500           | 13                      | 18.7                     | 20.0                 | W    |

Table 5. MPC8572EL Power Dissipation <sup>1</sup>

#### Notes:

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

<sup>&</sup>lt;sup>1</sup> This reflects the MPC8572E power dissipation excluding the power dissipation from B/G/L/O/T/XV<sub>DD</sub> rails.

$<sup>^2</sup>$  Typical-65 is based on  $\rm V_{DD}$  = 1.1 V,  $\rm T_j$  = 65  $^{\circ}C,$  running Dhrystone.

<sup>&</sup>lt;sup>3</sup> Typical-105 is based on  $V_{DD}$  = 1.1 V,  $T_i$  = 105 °C, running Dhrystone.

<sup>&</sup>lt;sup>4</sup> Maximum is based on  $V_{DD} = 1.1 \text{ V}$ ,  $T_i = 105 \,^{\circ}\text{C}$ , running a smoke test.

<sup>&</sup>lt;sup>1</sup> This reflects the MPC8572E power dissipation excluding the power dissipation from B/G/L/O/T/XV<sub>DD</sub> rails.

<sup>&</sup>lt;sup>2</sup> Typical-65 is based on  $V_{DD}$  = 1.1 V,  $T_i$  = 65 °C, running Dhrystone.

$<sup>^3</sup>$  Typical-105 is based on  $V_{DD}$  = 1.1 V,  $T_i$  = 105 °C, running Dhrystone.

<sup>&</sup>lt;sup>4</sup> Maximum is based on  $V_{DD}$  = 1.1 V,  $T_i$  = 105 °C, running a smoke test.

**Input Clocks**

## 4 Input Clocks

## 4.1 System Clock Timing

Table 6 provides the system clock (SYSCLK) AC timing specifications for the MPC8572E.

#### **Table 6. SYSCLK AC Timing Specifications**

At recommended operating conditions with OV<sub>DD</sub> of 3.3V  $\pm$  5%.

| Parameter/Condition       | Symbol                                | Min | Typical | Max     | Unit | Notes   |

|---------------------------|---------------------------------------|-----|---------|---------|------|---------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 33  | _       | 133     | MHz  | 1       |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                   | 7.5 | _       | 30.3    | ns   | _       |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 1.2     | ns   | 2       |

| SYSCLK duty cycle         | t <sub>KHK</sub> /t <sub>SYSCLK</sub> | 40  | _       | 60      | %    | 3       |

| SYSCLK jitter             | _                                     | _   | _       | +/- 150 | ps   | 4, 5, 6 |

#### Notes:

- Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth should be <500 kHz at –20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on SYSCLK.

## 4.2 Real Time Clock Timing

The RTC input is sampled by the platform clock (CCB clock). The output of the sampling latch is then used as an input to the counters of the PIC and the TimeBase unit of the e500. There is no jitter specification. The minimum pulse width of the RTC signal should be greater than 2x the period of the CCB clock. That is, minimum clock high time is  $2 \times t_{CCB}$ , and minimum clock low time is  $2 \times t_{CCB}$ . There is no minimum RTC frequency; RTC may be grounded if not needed.

#### **RESET Initialization**

#### **Table 8. DDRCLK AC Timing Specifications (continued)**

At recommended operating conditions with  $OV_{DD}$  of 3.3V  $\pm$  5%.

| Parameter/Condition | Symbol | Min | Typical | Max     | Unit | Notes   |

|---------------------|--------|-----|---------|---------|------|---------|

| DDRCLK jitter       | 1      | 1   | 1       | +/- 150 | ps   | 4, 5, 6 |

#### Notes:

- Caution: The DDR complex clock to DDRCLK ratio settings must be chosen such that the resulting DDR complex clock frequency does not exceed the maximum or minimum operating frequencies. Refer to Section 19.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

- 2. Rise and fall times for DDRCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The DDRCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track DDRCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on DDRCLK.

#### 4.5 Platform to eTSEC FIFO Restrictions

Note the following eTSEC FIFO mode maximum speed restrictions based on platform (CCB) frequency.

For FIFO GMII modes (both 8 and 16 bit) and 16-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/4.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 127 MHz.

For 8-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/3.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz.

## 4.6 Other Input Clocks

For information on the input clocks of other functional blocks of the platform, such as SerDes and eTSEC, see the respective sections of this document.

## 5 RESET Initialization

Table 9 describes the AC electrical specifications for the RESET initialization timing.

**Table 9. RESET Initialization Timing Specifications**

| Parameter/Condition               | Min | Max | Unit    | Notes |

|-----------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET | 100 | _   | μs      | 2     |

| Minimum assertion time for SRESET | 3   | _   | SYSCLKs | 1     |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

| PLL config input setup time with stable SYSCLK before HRESET negation                                   | 100 | _ | μѕ      | _ |

|---------------------------------------------------------------------------------------------------------|-----|---|---------|---|

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET             | 4   | _ | SYSCLKs | 1 |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET           | 2   | _ | SYSCLKs | 1 |

| Maximum valid-to-high impedance time for actively driven POR configs with respect to negation of HRESET | _   | 5 | SYSCLKs | 1 |

#### Notes:

- 1. SYSCLK is the primary clock input for the MPC8572E.

- 2. Reset assertion timing requirements for DDR3 DRAMs may differ.

Table 10 provides the PLL lock times.

**Table 10. PLL Lock Times**

| Parameter/Condition | Symbol | Min | Typical | Max |

|---------------------|--------|-----|---------|-----|

| PLL lock times      | _      | 100 | μs      | _   |

| Local bus PLL       | _      | 50  | μs      |     |

## 6 DDR2 and DDR3 SDRAM Controller

This section describes the DC and AC electrical specifications for the DDR2 and DDR3 SDRAM controller interface of the MPC8572E. Note that the required GV<sub>DD</sub>(typ) voltage is 1.8Vor 1.5 V when interfacing to DDR2 or DDR3 SDRAM, respectively.

## 6.1 DDR2 and DDR3 SDRAM Interface DC Electrical Characteristics

Table 11 provides the recommended operating conditions for the DDR SDRAM controller of the MPC8572E when interfacing to DDR2 SDRAM.

Table 11. DDR2 SDRAM Interface DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

| Parameter/Condition                              | Symbol              | Min                                 | Max                                 | Unit | Notes |

|--------------------------------------------------|---------------------|-------------------------------------|-------------------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>    | 1.71                                | 1.89                                | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> n | $0.49 \times \text{GV}_{\text{DD}}$ | $0.51 \times \text{GV}_{\text{DD}}$ | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>     | MV <sub>REF</sub> n - 0.04          | MV <sub>REF</sub> n + 0.04          | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>     | $MV_{REF}n + 0.125$                 | GV <sub>DD</sub> + 0.3              | V    | _     |

| Input low voltage                                | V <sub>IL</sub>     | -0.3                                | $MV_{REF}n - 0.125$                 | V    | _     |

| Output leakage current                           | l <sub>OZ</sub>     | -50                                 | 50                                  | μΑ   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>OH</sub>     | -13.4                               | _                                   | mA   | _     |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

## Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications (continued) At recommended operating conditions with $GV_{DD}$ of 1.8 V $\pm$ 5% for DDR2 or 1.5 V $\pm$ 5% for DDR3.

| Parameter                                      | Symbol <sup>1</sup>                         | Min    | Max   | Unit | Notes |

|------------------------------------------------|---------------------------------------------|--------|-------|------|-------|

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        |                                             | 1.95   | _     |      |       |

| ADDR/CMD output hold with respect to MCK       | t <sub>DDKHAX</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        |                                             | 1.95   | _     |      |       |

| MCS[n] output setup with respect to MCK        | t <sub>DDKHCS</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        | t <sub>DDKHCS</sub>                         | 1.95   | _     | ns   | 3     |

| MCS[n] output hold with respect to MCK         | t <sub>DDKHCX</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        |                                             | 1.95   | _     |      |       |

| MCK to MDQS Skew                               | t <sub>DDKHMH</sub>                         |        |       | ns   | 4     |

| 800 MHz                                        |                                             | -0.375 | 0.375 |      |       |

| <= 667 MHz                                     |                                             | -0.6   | 0.6   |      |       |

| MDQ/MECC/MDM output setup with respect to MDQS | t <sub>DDKHDS,</sub> t <sub>DDKLDS</sub>    |        |       | ps   | 5     |

| 800 MHz                                        |                                             | 375    | _     |      |       |

| 667 MHz                                        |                                             | 450    | _     |      |       |

| 533 MHz                                        |                                             | 538    | _     |      |       |

| 400 MHz                                        |                                             | 700    | _     |      |       |

| MDQ/MECC/MDM output hold with respect to MDQS  | t <sub>DDKHDX,</sub><br>t <sub>DDKLDX</sub> |        |       | ps   | 5     |

| 800 MHz                                        |                                             | 375    | _     |      |       |

| 667 MHz                                        |                                             | 450    | _     |      |       |

| •                                              | •                                           | •      | •     | •    |       |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

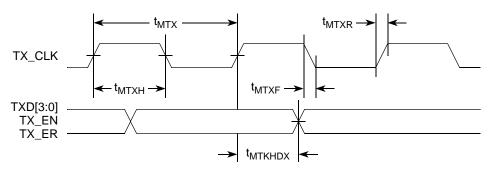

Figure 12 shows the MII transmit AC timing diagram.

Figure 12. MII Transmit AC Timing Diagram

## 8.2.3.2 MII Receive AC Timing Specifications

Table 30 provides the MII receive AC timing specifications.

#### Table 30. MII Receive AC Timing Specifications

At recommended operating conditions with LV  $_{DD}$ /TV  $_{DD}$  of 2.5/3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> <sup>2</sup>       | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    | _    | 40  | _   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | _   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>MRXR</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

#### Notes:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

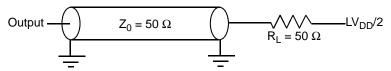

Figure 13 provides the AC test load for eTSEC.

Figure 13. eTSEC AC Test Load

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

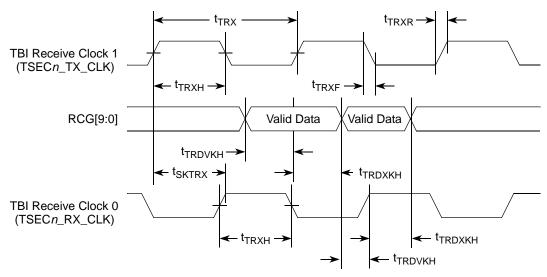

Figure 16 shows the TBI receive AC timing diagram.

Figure 16. TBI Receive AC Timing Diagram

## 8.2.5 TBI Single-Clock Mode AC Specifications

When the eTSEC is configured for TBI modes, all clocks are supplied from external sources to the relevant eTSEC interface. In single-clock TBI mode, when a 125-MHz TBI receive clock is supplied on TSEC*n* pin (no receive clock is used in this mode, whereas for the dual-clock mode this is the PMA1 receive clock). The 125-MHz transmit clock is applied in all TBI modes.

A summary of the single-clock TBI mode AC specifications for receive appears in Table 33.

Table 33. TBI single-clock Mode Receive AC Timing Specification

At recommended operating conditions with LV  $_{DD}/TV_{DD}$  of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                       | Symbol                               | Min | Тур | Max | Unit |

|-------------------------------------------|--------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                       | t <sub>TRRX</sub>                    | 7.5 | 8.0 | 8.5 | ns   |

| RX_CLK duty cycle                         | t <sub>TRRH</sub> /t <sub>TRRX</sub> | 40  | 50  | 60  | %    |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>                    | _   | _   | 250 | ps   |

| Rise time RX_CLK (20%–80%)                | t <sub>TRRR</sub>                    | _   | _   | 1.0 | ns   |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>                    | _   | _   | 1.0 | ns   |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>TRRDVKH</sub>                 | 2.0 | _   | _   | ns   |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>TRRDXKH</sub>                 | 1.0 | _   | _   | ns   |

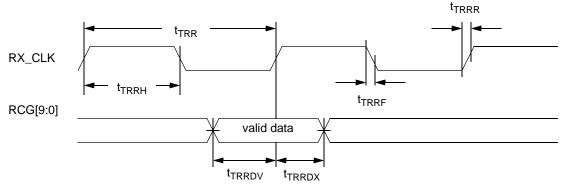

Figure 17 shows the TBI receive the timing diagram.

Figure 17. TBI Single-Clock Mode Receive AC Timing Diagram

## 8.2.6 RGMII and RTBI AC Timing Specifications

Table 34 presents the RGMII and RTBI AC timing specifications.

#### Table 34. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5 V  $\pm$  5%.

| Parameter/Condition                                 | Symbol <sup>1</sup>                 | Min  | Тур | Max  | Unit |

|-----------------------------------------------------|-------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)          | t <sub>SKRGT</sub>                  | -500 | 0   | 500  | ps   |

| Data to clock input skew (at receiver) <sup>2</sup> | t <sub>SKRGT</sub>                  | 1.0  | _   | 2.8  | ns   |

| Clock period <sup>3</sup>                           | t <sub>RGT</sub>                    | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 10BASE-T and 100BASE-TX 3, 4         | t <sub>RGTH</sub> /t <sub>RGT</sub> | 40   | 50  | 60   | %    |

| Rise time (20%–80%)                                 | t <sub>RGTR</sub>                   | _    | _   | 0.75 | ns   |

| Fall time (20%–80%)                                 | t <sub>RGTF</sub>                   | _    | _   | 0.75 | ns   |

#### Notes:

- 1. Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns will be added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns  $\pm$  40 ns and 40 ns  $\pm$  4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

described in Section 21.5, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

When operating in SGMII mode, the eTSEC EC\_GTX\_CLK125 clock is not required for this port. Instead, SerDes reference clock is required on SD2\_REF\_CLK and SD2\_REF\_CLK pins.

## 8.3.1 DC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 15, "High-Speed Serial Interfaces (HSSI)."

## 8.3.2 AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

Table 37 lists the SGMII SerDes reference clock AC requirements. Note that SD2\_REF\_CLK and SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

Table 37. SD2 REF CLK and SD2 REF CLK AC Requirements

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | _   | 10 (8)  | _   | ns    | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | _       | 100 | ps    | _     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _       | 50  | ps    | _     |

#### Note:

<sup>1. 8</sup> ns applies only when 125 MHz SerDes2 reference clock frequency is selected through cfg\_srds\_sgmii\_refclk during POR.

**Ethernet: Enhanced Three-Speed Ethernet (eTSEC)**

#### 8.3.3 SGMII Transmitter and Receiver DC Electrical Characteristics

Table 38 and Table 39 describe the SGMII SerDes transmitter and receiver AC-Coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs (SD2\_TX[n] and SD2\_TX[n]) as depicted in Figure 23.

**Table 38. SGMII DC Transmitter Electrical Characteristics**

| Parameter                                      | Symbol                 | Min   | Тур | Max                                                                      | Unit | Notes                       |

|------------------------------------------------|------------------------|-------|-----|--------------------------------------------------------------------------|------|-----------------------------|

| Supply Voltage                                 | XV <sub>DD_SRDS2</sub> | 1.045 | 1.1 | 1.155                                                                    | V    | _                           |

| Output high voltage                            | VOH                    | _     | _   | XV <sub>DD_SRDS2-Typ</sub> /2<br>+  V <sub>OD</sub>   <sub>-max</sub> /2 | mV   | 1                           |

| Output low voltage                             | VOL                    |       |     | mV                                                                       | 1    |                             |

| Output ringing                                 | V <sub>RING</sub>      | _     | _   | 10                                                                       | %    | _                           |

| Output differential voltage <sup>2, 3, 5</sup> |                        | 359   | 550 | 791                                                                      |      | Equalization setting: 1.0x  |

|                                                | lV <sub>OD</sub> I     | 329   | 505 | 725                                                                      |      | Equalization setting: 1.09x |

|                                                |                        | 299   | 458 | 659                                                                      | mV   | Equalization setting: 1.2x  |

| Output unierential voltage                     |                        | 270   | 414 | 594                                                                      |      | Equalization setting: 1.33x |

|                                                |                        | 239   | 367 | 527                                                                      |      | Equalization setting: 1.5x  |

|                                                |                        | 210   | 322 | 462                                                                      |      | Equalization setting: 1.71x |

|                                                |                        | 180   | 275 | 395                                                                      |      | Equalization setting: 2.0x  |

| Output offset voltage                          | Vos                    | 473   | 550 | 628                                                                      | mV   | 1, 4                        |

| Output impedance (single-ended)                | R <sub>O</sub>         | 40    | _   | 60                                                                       | Ω    | _                           |

| Mismatch in a pair                             | ΔR <sub>O</sub>        | _     | _   | 10                                                                       | %    | _                           |

| Change in V <sub>OD</sub> between "0" and "1"  | $\Delta  V_{OD} $      | _     | _   | 25                                                                       | mV   | _                           |

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 42. eTSEC IEEE 1588 AC Timing Specifications (continued)

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%

| Parameter/Condition           | Symbol                                                  | Min                         | Тур | Max | Unit | Note |

|-------------------------------|---------------------------------------------------------|-----------------------------|-----|-----|------|------|

| TSEC_1588_CLK_OUT duty cycle  | t <sub>T1588</sub> CLKOTH<br>/t <sub>T1588</sub> CLKOUT | 30                          | 50  | 70  | %    | _    |

| TSEC_1588_PULSE_OUT           | t <sub>T1588OV</sub>                                    | 0.5                         | _   | 3.0 | ns   | _    |

| TSEC_1588_TRIG_IN pulse width | t <sub>T1588</sub> TRIGH                                | 2*t <sub>T1588CLK_MAX</sub> | _   | _   | ns   | 2    |

#### Note

- 1.When TMR\_CTRL[CKSEL] is set as '00', the external TSEC\_1588\_CLK input is selected as the 1588 timer reference clock source, with the timing defined in Table 42, "eTSEC IEEE 1588 AC Timing Specifications." The maximum value of t<sub>T1588CLK</sub> is defined in terms of T<sub>TX\_CLK</sub>, that is the maximum clock cycle period of the equivalent interface speed that the eTSEC1 port is running at. When eTSEC1 is configured to operate in the parallel mode, the T<sub>TX\_CLK</sub> is the maximum clock period of the TSEC1\_TX\_CLK. When eTSEC1 operates in SGMII mode, the maximum value of t<sub>T1588CLK</sub> is defined in terms of the recovered clock from SGMII SerDes. For example, for SGMII 10/100/1000 Mbps modes, the maximum value of t<sub>T1588CLK</sub> is 3600, 360, 72 ns respectively. See the MPC8572E PowerQUICC™ III Integrated Communications Processor Reference Manual for detailed description of TMR\_CTRL registers.

- 2. It needs to be at least two times of the clock period of the clock selected by TMR\_CTRL[CKSEL].

# 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals ECn\_MDIO (management data input/output) and ECn\_MDC (management data clock). The electrical characteristics for GMII, SGMII, RGMII, RMII, TBI and RTBI are specified in "Section 8, "Ethernet: Enhanced Three-Speed Ethernet (eTSEC)."

## 9.1 MII Management DC Electrical Characteristics

The ECn\_MDC and ECn\_MDIO are defined to operate at a supply voltage of 3.3 V or 2.5 V. The DC electrical characteristics for ECn\_MDIO and ECn\_MDC are provided in Table 43 and Table 44.

Table 43. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=3.3 V)

| Parameter                                                                                           | Symbol                             | Min  | Max                    | Unit | Notes |

|-----------------------------------------------------------------------------------------------------|------------------------------------|------|------------------------|------|-------|

| Supply voltage (3.3 V)                                                                              | LV <sub>DD</sub> /TV <sub>DD</sub> | 3.13 | 3.47                   | V    | 1, 2  |

| Output high voltage $(LV_{DD}/TV_{DD} = Min, I_{OH} = -1.0 mA)$                                     | V <sub>OH</sub>                    | 2.10 | OV <sub>DD</sub> + 0.3 | V    | _     |

| Output low voltage (LV <sub>DD</sub> /TV <sub>DD</sub> =Min, I <sub>OL</sub> = 1.0 mA)              | V <sub>OL</sub>                    | GND  | 0.50                   | V    | _     |

| Input high voltage                                                                                  | V <sub>IH</sub>                    | 2.0  | _                      | V    | _     |

| Input low voltage                                                                                   | V <sub>IL</sub>                    | _    | 0.90                   | V    | _     |

| Input high current (LV <sub>DD</sub> /TV <sub>DD</sub> = Max, V <sub>IN</sub> <sup>3</sup> = 2.1 V) | I <sub>IH</sub>                    | _    | 40                     | μΑ   | _     |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

## Table 62. Differential Transmitter (TX) Output Specifications (continued)

| Symbol                            | Parameter                                                                                                         | Min | Nominal | Max           | Units | Comments                                                                                                                                                                                                                                 |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|---------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TX-DC-CM</sub>             | The TX DC<br>Common Mode<br>Voltage                                                                               | 0   | _       | 3.6           | V     | The allowed DC Common Mode voltage under any conditions. See Note 6.                                                                                                                                                                     |

| I <sub>TX-SHORT</sub>             | TX Short Circuit<br>Current Limit                                                                                 |     | _       | 90            | mA    | The total current the Transmitter can provide when shorted to its ground                                                                                                                                                                 |

| T <sub>TX-IDLE-MIN</sub>          | Minimum time<br>spent in<br>Electrical Idle                                                                       | 50  | _       |               | UI    | Minimum time a Transmitter must be in Electrical Idle Utilized by the Receiver to start looking for an Electrical Idle Exit after successfully receiving an Electrical Idle ordered set                                                  |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Maximum time to<br>transition to a<br>valid Electrical<br>idle after sending<br>an Electrical Idle<br>ordered set | 1   | _       | 20            | UI    | After sending an Electrical Idle ordered set, the Transmitter must meet all Electrical Idle Specifications within this time. This is considered a debounce time for the Transmitter to meet Electrical Idle after transitioning from L0. |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Maximum time to<br>transition to valid<br>TX specifications<br>after leaving an<br>Electrical idle<br>condition   |     | _       | 20            | UI    | Maximum time to meet all TX specifications when transitioning from Electrical Idle to sending differential data. This is considered a debounce time for the TX to meet all TX specifications after leaving Electrical Idle               |

| RL <sub>TX-DIFF</sub>             | Differential<br>Return Loss                                                                                       | 12  | _       | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                             |

| RL <sub>TX-CM</sub>               | Common Mode<br>Return Loss                                                                                        | 6   | _       | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                             |

| Z <sub>TX-DIFF-DC</sub>           | DC Differential TX Impedance                                                                                      | 80  | 100     | 120           | Ω     | TX DC Differential mode Low Impedance                                                                                                                                                                                                    |

| Z <sub>TX-DC</sub>                | Transmitter DC Impedance                                                                                          | 40  | _       | _             | Ω     | Required TX D+ as well as D- DC Impedance during all states                                                                                                                                                                              |

| L <sub>TX-SKEW</sub>              | Lane-to-Lane<br>Output Skew                                                                                       | _   | _       | 500 +<br>2 UI | ps    | Static skew between any two Transmitter Lanes within a single Link                                                                                                                                                                       |

| C <sub>TX</sub>                   | AC Coupling<br>Capacitor                                                                                          | 75  | _       | 200           | nF    | All Transmitters shall be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See Note 8.                                                                                       |

Table 69. Long Run Transmitter AC Timing Specifications—2.5 GBaud

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Cital acteristic            | Symbol              | Min   | Max  | Onit   | Notes                                                                      |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | _                                                                          |

| Deterministic Jitter        | $J_D$               | _     | 0.17 | UI p-p | _                                                                          |

| Total Jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit Interval               | UI                  | 400   | 400  | ps     | +/- 100 ppm                                                                |

Table 70. Long Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Ra    | ange | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit   | Notes                                                                      |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | _                                                                          |

| Deterministic Jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | _                                                                          |

| Total Jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit Interval               | UI                  | 320   | 320  | ps     | +/- 100 ppm                                                                |

For each baud rate at which an LP-Serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the transmitter output compliance mask shown in Figure 58 with the parameters specified in Figure 71 when measured at the output pins of the device and the device is driving a  $100~\Omega$  +/-5% differential resistive load. The output eye pattern of an LP-Serial transmitter that implements pre-emphasis (to equalize the link and reduce inter-symbol interference) need only comply with the Transmitter Output Compliance Mask when pre-emphasis is disabled or minimized.

link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. The amount of data represented in the eye shall be adequate to ensure that the bit error ratio is less than  $10^{-12}$ . The eye pattern shall be measured with AC coupling and the compliance template centered at 0 Volts differential. The left and right edges of the template shall be aligned with the mean zero crossing points of the measured data eye. The load for this test shall be  $100 \Omega$  resistive +/- 5% differential to 2.5 GHz.

#### 17.8.2 Jitter Test Measurements

For the purpose of jitter measurement, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for jitter measurements is the Continuous Jitter Test Pattern (CJPAT) pattern defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. Jitter shall be measured with AC coupling and at 0 Volts differential. Jitter measurement for the transmitter (or for calibration of a jitter tolerance setup) shall be performed with a test procedure resulting in a BER curve such as that described in Annex 48B of IEEE 802.3ae.

#### 17.8.3 Transmit Jitter

Transmit jitter is measured at the driver output when terminated into a load of 100  $\Omega$  resistive +/- 5% differential to 2.5 GHz.

#### 17.8.4 Jitter Tolerance

Jitter tolerance is measured at the receiver using a jitter tolerance test signal. This signal is obtained by first producing the sum of deterministic and random jitter defined in Section 17.6, "Receiver Specifications," and then adjusting the signal amplitude until the data eye contacts the 6 points of the minimum eye opening of the receive template shown in Figure 60 and Table 75. Note that for this to occur, the test signal must have vertical waveform symmetry about the average value and have horizontal symmetry (including jitter) about the mean zero crossing. Eye template measurement requirements are as defined above. Random jitter is calibrated using a high pass filter with a low frequency corner at 20 MHz and a 20 dB/decade roll-off below this. The required sinusoidal jitter specified in Section 17.6, "Receiver Specifications," is then added to the signal and the test load is replaced by the receiver being tested.

## 18 Package Description

This section describes package parameters, pin assignments, and dimensions.

Clocking

Table 82. DDR Clock Ratio (continued)

| Binary Value of<br>TSEC_1588_CLK_OUT,<br>TSEC_1588_PULSE_OUT1,<br>TSEC_1588_PULSE_OUT2 Signals | DDR:DDRCLK Ratio |  |  |

|------------------------------------------------------------------------------------------------|------------------|--|--|

| 101                                                                                            | 12:1             |  |  |

| 110                                                                                            | 14:1             |  |  |

| 111                                                                                            | Synchronous mode |  |  |

## 19.5 Frequency Options

## 19.5.1 Platform to Sysclk Frequency Options

Table 83 shows the expected frequency values for the platform frequency when using the specified CCB clock to SYSCLK ratio.

CCB to SYSCLK (MHz) **SYSCLK Ratio** 33.33 41.66 50 66.66 83 100 111 133.33 Platform /CCB Frequency (MHz) 400 444 4 533 5 415 500 555 6 400 498 600 8 400 533 10 417 500 400 12 500 600

**Table 83. Frequency Options for Platform Frequency**

# 19.5.2 Minimum Platform Frequency Requirements for High-Speed Interfaces

Section 4.4.3.6, "I/O Port Selection," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* describes various high-speed interface configuration options. Note that the CCB clock frequency must be considered for proper operation of such interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than or equal to:

See Section 21.1.3.2, "Link Width," in the MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual for PCI Express interface width details. Note that the "PCI Express link width"

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

#### **System Design Information**

logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert TRST during the power-on reset flow. Simply tying TRST to HRESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 66 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

The COP interface has a standard header, shown in Figure 65, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; so emulator vendors have issued many different pin numbering schemes. Some COP headers are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom. Still others number the pins counter-clockwise from pin 1 (as with an IC). Regardless of the numbering scheme, the signal placement recommended in Figure 65 is common to all known emulators.

## 21.9.1 Termination of Unused Signals

If the JTAG interface and COP header is not used, Freescale recommends the following connections:

- TRST should be tied to HRESET through a 0 kΩ isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 66. If this is not possible, the isolation resistor allows future access to TRST in case a JTAG interface may need to be wired onto the system in future debug situations.

- No pull-up/pull-down is required for TDI, TMS, TDO or TCK.

#### **Ordering Information**

#### Table 87. Part Numbering Nomenclature—Rev 2.1

MPC nnnn e t I pp ffm i

| Product<br>Code <sup>1</sup> | Part<br>Identifier | Security<br>Engine                 | Temperature                            | Power                          | Package<br>Sphere Type <sup>2</sup>                    | Processor Frequency/<br>DDR Data Rate <sup>3</sup>                                                                                                                                                     | Silicon<br>Revision                                                                                                   |

|------------------------------|--------------------|------------------------------------|----------------------------------------|--------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| MPC<br>PPC                   | 8572               | E = Included  Blank = Not included | Blank = 0 to 105°C<br>C = -40 to 105°C | Blank =<br>Standard<br>L = Low | PX =<br>Leaded,<br>FC-PBGA<br>VT = Pb-free,<br>FC-PBGA | AVN = 150- MHz processor; 800 MT/s DDR data rate  AUL = 1333-MHz processor; 667 MT/s DDR data rate  ATL = 1200-MHz processor; 667 MT/s DDR data rate  ARL = 1067-MHz processor; 667 MT/s DDR data rate | D= Ver. 2.1<br>(SVR =<br>0x80E8_0021)<br>SEC included<br>D= Ver. 2.1<br>(SVR =<br>0x80E0_0021)<br>SEC not<br>included |

#### Notes:

Table 88. Part Numbering Nomenclature—Rev 1.1.1

MPC nnnn e t pp ffm r

| Product<br>Code <sup>1</sup> | Part<br>Identifier | Security Engine                    | Temperature                         | Package Sphere<br>Type <sup>2</sup>                 | Processor Frequency/<br>DDR Data Rate <sup>3</sup>                                                                                                                                                  | Silicon<br>Revision                                                                                                      |

|------------------------------|--------------------|------------------------------------|-------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| MPC<br>PPC                   | 8572               | E = Included  Blank = Not included | Blank=0 to 105°C<br>C= -40 to 105°C | PX = Leaded,<br>FC-PBGA<br>VT = Pb-free,<br>FC-PBGA | AVN = 1500-MHz processor; 800 MT/s DDR data rate AUL = 1333-MHz process or; 667 MT/s DDR datarate ATL = 1200-MHz processor; 667 MT/s DDR data rate ARL = 1067-MHz processor; 667 MT/s DDR data rate | B = Ver. 1.1.1<br>(SVR =<br>0x80E8_0011)<br>SEC included<br>B = Ver. 1.1.1<br>(SVR =<br>0x80E0_0011)<br>SEC not included |

#### Notes:

#### MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

MPC stands for "Qualified." PPC stands for "Prototype"

<sup>&</sup>lt;sup>2</sup> See Section 18, "Package Description," for more information on the available package types.

Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

MPC stands for "Qualified." PPC stands for "Prototype"

See Section 18, "Package Description," for more information on the available package types.

How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. 'ÄúTypical,Äù parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including 'Äútypicals,'Äù must be validated for each customer application by customer,Äôs technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE,

JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. . Oracle and

Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2008-2011, 2014, 2016 NXP B.V.

Document Number: MPC8572EEC

Rev. 7 03/2016