# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.5GHz                                                                  |

| Co-Processors/DSP               | Signal Processing; SPE                                                  |

| RAM Controllers                 | DDR2, DDR3                                                              |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                  |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | ·                                                                       |

| Package / Case                  | 1023-BFBGA, FCBGA                                                       |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572clvtavnd |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Three inbound windows plus a configuration window on PCI Express

- Four inbound windows plus a default window on Serial RapidIO®

- Four outbound windows plus default translation for PCI Express

- Eight outbound windows plus default translation for Serial RapidIO with segmentation and sub-segmentation support

- Two 64-bit DDR2/DDR3 memory controllers

- Programmable timing supporting DDR2 and DDR3 SDRAM

- 64-bit data interface per controller

- Four banks of memory supported, each up to 4 Gbytes, for a maximum of 16 Gbytes per controller

- DRAM chip configurations from 64 Mbits to 4 Gbits with x8/x16 data ports

- Full ECC support

- Page mode support

- Up to 32 simultaneous open pages for DDR2 or DDR3

- Contiguous or discontiguous memory mapping

- Cache line, page, bank, and super-bank interleaving between memory controllers

- Read-modify-write support for RapidIO atomic increment, decrement, set, and clear transactions

- Sleep mode support for self-refresh SDRAM

- On-die termination support when using DDR2 or DDR3

- Supports auto refreshing

- On-the-fly power management using CKE signal

- Registered DIMM support

- Fast memory access through JTAG port

- 1.8-V SSTL\_1.8 compatible I/O

- Support 1.5-V operation for DDR3. The detail is TBD pending on official release of appropriate industry specifications.

- Support for battery-backed main memory

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture.

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts

- Supports 4 message interrupts per processor with 32-bit messages

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high resolution timers/counters per processor that can generate interrupts

- Supports a variety of other internal interrupt sources

Overview

- Ability to launch DMA from single write transaction

- Serial RapidIO interface unit

- Supports RapidIO Interconnect Specification, Revision 1.2

- Both 1x and 4x LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto-detection of 1x- and 4x-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO–compliant message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

- Single inbound doorbell message structure

- Facility to accept port-write messages

**RESET** Initialization

Table 8. DDRCLK AC Timing Specifications (continued)

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition | Symbol | Min | Typical | Max     | Unit | Notes   |

|---------------------|--------|-----|---------|---------|------|---------|

| DDRCLK jitter       | _      |     |         | +/- 150 | ps   | 4, 5, 6 |

Notes:

- 1. **Caution:** The DDR complex clock to DDRCLK ratio settings must be chosen such that the resulting DDR complex clock frequency does not exceed the maximum or minimum operating frequencies. Refer to Section 19.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

- 2. Rise and fall times for DDRCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The DDRCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track DDRCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on DDRCLK.

### 4.5 Platform to eTSEC FIFO Restrictions

Note the following eTSEC FIFO mode maximum speed restrictions based on platform (CCB) frequency.

For FIFO GMII modes (both 8 and 16 bit) and 16-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/4.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 127 MHz.

For 8-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/3.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz.

### 4.6 Other Input Clocks

For information on the input clocks of other functional blocks of the platform, such as SerDes and eTSEC, see the respective sections of this document.

# 5 **RESET** Initialization

Table 9 describes the AC electrical specifications for the RESET initialization timing.

#### **Table 9. RESET Initialization Timing Specifications**

| Parameter/Condition               | Min | Мах | Unit    | Notes |

|-----------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET | 100 | —   | μs      | 2     |

| Minimum assertion time for SRESET | 3   | —   | SYSCLKs | 1     |

Table 14 provides the current draw characteristics for  $MV_{REF}n$ .

| Parameter / Condition                |            | Symbol               | Min | Max  | Unit | Note |

|--------------------------------------|------------|----------------------|-----|------|------|------|

| Current draw for MV <sub>REF</sub> n | DDR2 SDRAM | I <sub>MVREF</sub> n | —   | 1500 | μΑ   | 1    |

|                                      | DDR3 SDRAM |                      |     | 1250 |      |      |

Table 14. Current Draw Characteristics for MV<sub>REF</sub> n

1. The voltage regulator for MV<sub>RFF</sub>n must be able to supply up to 1500 μA or 1250 uA current for DDR2 or DDR3, respectively.

### 6.2 DDR2 and DDR3 SDRAM Interface AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM controller interface. The DDR controller supports both DDR2 and DDR3 memories. Note that although the minimum data rate for most off-the-shelf DDR3 DIMMs available is 800 MHz, JEDEC specification does allow the DDR3 to run at the data rate as low as 606 MHz. Unless otherwise specified, the AC timing specifications described in this section for DDR3 is applicable for data rate between 606 MHz and 800 MHz, as long as the DC and AC specifications of the DDR3 memory to be used are compliant to both JEDEC specifications as well as the specifications and requirements described in this MPC8572E hardware specifications document.

### 6.2.1 DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

Table 15, Table 16, and Table 17 provide the input AC timing specifications for the DDR controller when interfacing to DDR2 and DDR3 SDRAM.

# Table 15. DDR2 SDRAM Interface Input AC Timing Specifications for 1.8-V Interface At recommended operating conditions with $GV_{DD}$ of 1.8 V ± 5%

| Paramet               | Parameter  |                   | Min                | Мах                | Unit | Notes |

|-----------------------|------------|-------------------|--------------------|--------------------|------|-------|

| AC input low voltage  | >=667 MHz  | V <sub>ILAC</sub> | —                  | $MV_{REF}n - 0.20$ | V    | _     |

|                       | <= 533 MHz |                   | —                  | $MV_{REF}n - 0.25$ |      |       |

| AC input high voltage | >=667 MHz  | V <sub>IHAC</sub> | $MV_{REF}n + 0.20$ | —                  | V    | —     |

| _                     | <= 533 MHz |                   | $MV_{REF}n + 0.25$ | _                  |      |       |

#### Table 16. DDR3 SDRAM Interface Input AC Timing Specifications for 1.5-V Interface

At recommended operating conditions with GV<sub>DD</sub> of 1.5 V ± 5%. DDR3 data rate is between 606 MHz and 800 MHz.

| Parameter             | Symbol            | Min                 | Мах                                | Unit | Notes |

|-----------------------|-------------------|---------------------|------------------------------------|------|-------|

| AC input low voltage  | V <sub>ILAC</sub> | _                   | MV <sub>REF</sub> <i>n</i> – 0.175 | V    | —     |

| AC input high voltage | V <sub>IHAC</sub> | $MV_{REF}n + 0.175$ | —                                  | V    | —     |

| Table 24, MIL GMIL | RMIL RGI | /III. TBI. RTB                          | I, and FIFO DC Electrica | Characteristics | (continued) |

|--------------------|----------|-----------------------------------------|--------------------------|-----------------|-------------|

|                    | ,,       | , , , , , , , , , , , , , , , , , , , , |                          |                 | ooninaca)   |

| Parameters                                                | Symbol          | Min | Мах | Unit | Notes  |

|-----------------------------------------------------------|-----------------|-----|-----|------|--------|

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$ | IIH             | _   | 10  | μΑ   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)              | Ι <sub>ΙL</sub> | -15 | _   | μΑ   | 3      |

Note:

<sup>1</sup>  $LV_{DD}$  supports eTSECs 1 and 2.

$^{2}$  TV<sub>DD</sub> supports eTSECs 3 and 4 or FEC.

$^3$  Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII and RTBI are presented in this section.

### 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, because they have similar performance and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back on the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source-synchronous timing reference. Typically, the clock edge that launched the data can be used, because the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is a relationship between the maximum FIFO speed and the platform (CCB) frequency. For more information see Section 4.5, "Platform to eTSEC FIFO Restrictions."

Table 25 and Table 26 summarize the FIFO AC specifications.

#### Table 25. FIFO Mode Transmit AC Timing Specification

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 2.5V ± 5%

| Parameter/Condition                       | Symbol                              | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK, GTX_CLK clock period <sup>1</sup> | t <sub>FIT</sub>                    | 5.3 | 8.0 | 100 | ns   |

| TX_CLK, GTX_CLK duty cycle                | t <sub>FITH</sub> /t <sub>FIT</sub> | 45  | 50  | 55  | %    |

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

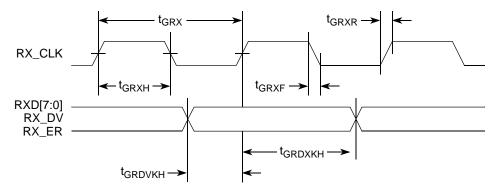

Figure 11 shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

### 8.2.3 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.3.1 MII Transmit AC Timing Specifications

Table 29 provides the MII transmit AC timing specifications.

#### Table 29. MII Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> <sup>2</sup>       | —   | 400 | _   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                    | —   | 40  | _   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                 | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise (20%-80%)                | t <sub>MTXR</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

| TX_CLK data clock fall (80%-20%)                | t <sub>MTXF</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

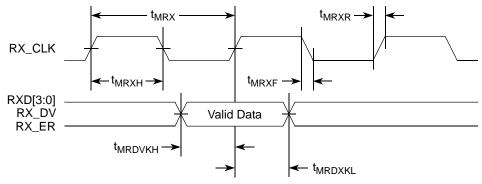

Figure 14 shows the MII receive AC timing diagram.

Figure 14. MII Receive AC Timing Diagram

### 8.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

### 8.2.4.1 TBI Transmit AC Timing Specifications

Table 31 provides the TBI transmit AC timing specifications.

#### Table 31. TBI Transmit AC Timing Specifications

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>            | Min | Тур | Мах | Unit |

|--------------------------------------------|--------------------------------|-----|-----|-----|------|

| TCG[9:0] setup time GTX_CLK going high     | t <sub>TTKHDV</sub>            | 2.0 | _   | _   | ns   |

| TCG[9:0] hold time from GTX_CLK going high | t <sub>TTKHDX</sub>            | 1.0 | _   | _   | ns   |

| GTX_CLK rise (20%-80%)                     | t <sub>TTXR</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

| GTX_CLK fall time (80%–20%)                | t <sub>TTXF</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

#### Local Bus Controller (eLBC)

Table 48 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 1.8 V$  DC.

| Parameter                                                              | Symbol           | Min                     | Мах                     | Unit |

|------------------------------------------------------------------------|------------------|-------------------------|-------------------------|------|

| Supply voltage 1.8V                                                    | BV <sub>DD</sub> | 1.71                    | 1.89                    | V    |

| High-level input voltage                                               | V <sub>IH</sub>  | 0.65 x BV <sub>DD</sub> | BV <sub>DD</sub> + 0.3  | V    |

| Low-level input voltage                                                | V <sub>IL</sub>  | -0.3                    | 0.35 x BV <sub>DD</sub> | V    |

| Input current<br>( $BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD}$ ) | I <sub>IN</sub>  | TBD                     | TBD                     | μA   |

| High-level output voltage<br>(I <sub>OH</sub> = −100 μA)               | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2  | _                       | V    |

| High-level output voltage $(I_{OH} = -2 \text{ mA})$                   | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.45 | _                       | V    |

| Low-level output voltage<br>(I <sub>OL</sub> = 100 μA)                 | V <sub>OL</sub>  | _                       | 0.2                     | V    |

| Low-level output voltage<br>(I <sub>OL</sub> = 2 mA)                   | V <sub>OL</sub>  | _                       | 0.45                    | V    |

Table 48. Local Bus DC Electrical Characteristics (1.8 V DC)

#### Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

### **10.2 Local Bus AC Electrical Specifications**

Table 49 describes the general timing parameters of the local bus interface at  $BV_{DD} = 3.3 \text{ V DC}$ .

Table 49. Local Bus General Timing Parameters ( $BV_{DD} = 3.3 V DC$ )—PLL EnabledAt recommended operating conditions with  $BV_{DD}$  of 3.3 V ± 5%.

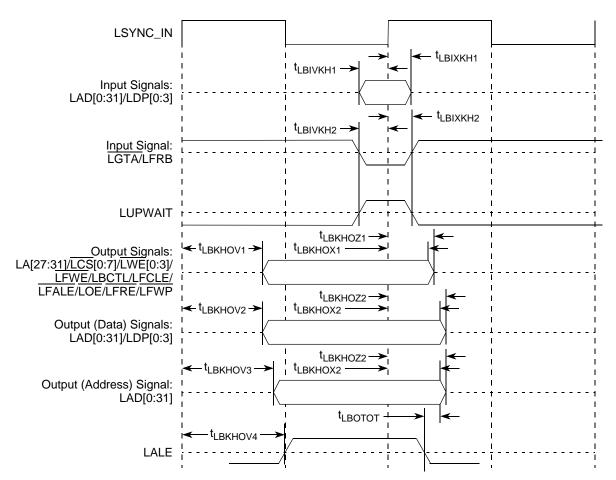

| Parameter                                                            | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|----------------------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                                 | t <sub>LBK</sub>                    | 6.67 | 12  | ns   | 2     |

| Local bus duty cycle                                                 | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                 | t <sub>LBKSKEW</sub>                | —    | 150 | ps   | 7,8   |

| Input setup to local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIVKH1</sub>                | 1.8  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                          | t <sub>LBIVKH2</sub>                | 1.7  | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                | t <sub>LBIXKH1</sub>                | 1.0  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKH2</sub>                | 1.0  | —   | ns   | 3, 4  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5  | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKHOV1</sub>                | —    | 2.3 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKHOV2</sub>                | —    | 2.4 | ns   | 3     |

| Local bus clock to address valid for LAD                             | t <sub>LBKHOV3</sub>                | —    | 2.3 | ns   | 3     |

#### Local Bus Controller (eLBC)

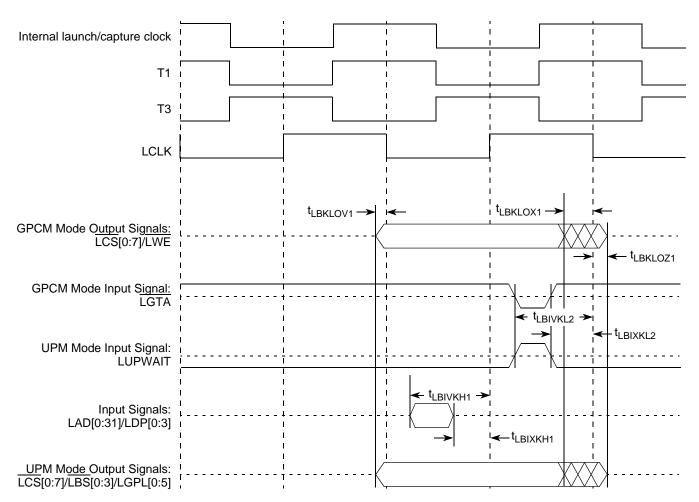

Figure 30 through Figure 35 show the local bus signals.

Figure 30. Local Bus Signals, Non-Special Signals Only (PLL Enabled)

Table 52 describes the general timing parameters of the local bus interface at  $BV_{DD} = 3.3 \text{ V DC}$  with PLL disabled.

#### Table 52. Local Bus General Timing Parameters—PLL Bypassed

At recommended operating conditions with  $BV_{DD}$  of 3.3 V ± 5%

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 12   | _   | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | —     |

| Internal launch/capture clock to LCLK delay           | t <sub>LBKHKT</sub>                 | 2.3  | 4.0 | ns   | —     |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 5.8  | —   | ns   | 4, 5  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKL2</sub>                | 5.7  | _   | ns   | 4, 5  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | -1.3 | —   | ns   | 4, 5  |

Local Bus Controller (eLBC)

Figure 33. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Bypass Mode)

GPIO

# 14 GPIO

This section describes the DC and AC electrical specifications for the GPIO interface of the MPC8572E.

### 14.1 GPIO DC Electrical Characteristics

Table 56 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 3.3 \text{ V DC}$ .

| Parameter                                                                      | Symbol           | Min                    | Max                    | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------------------------|------|

| Supply voltage 3.3V                                                            | BV <sub>DD</sub> | 3.13                   | 3.47                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 2                      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3                   | 0.8                    | V    |

| Input current<br>( $BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD}$ )         | I <sub>IN</sub>  | _                      | ±5                     | μΑ   |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | —                      | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  |                        | 0.2                    | V    |

Table 56. GPIO DC Electrical Characteristics (3.3 V DC)

Note:

1. Note that the symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

Table 57 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 2.5 \text{ V DC}$ .

Table 57. GPIO DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                      | Symbol           | Min       | Мах                    | Unit |

|--------------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5V                                                            | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 1.70      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3      | 0.7                    | V    |

| Input current                                                                  | I <sub>IH</sub>  | _         | 10                     | μΑ   |

| $(BV_{IN}^{1} = 0 \; V \; or \; BV_{IN} = BV_{DD})$                            | IIL              |           | -15                    |      |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -1 mA) | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> min, I <sub>OL</sub> = 1 mA)     | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

| Symbol                            | Parameter                                                                                                         | Min | Nominal | Max           | Units | Comments                                                                                                                                                                                                                                             |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|---------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TX-DC-CM</sub>             | The TX DC<br>Common Mode<br>Voltage                                                                               | 0   | _       | 3.6           | V     | The allowed DC Common Mode voltage under any conditions. See Note 6.                                                                                                                                                                                 |

| I <sub>TX-SHORT</sub>             | TX Short Circuit<br>Current Limit                                                                                 |     | —       | 90            | mA    | The total current the Transmitter can provide when shorted to its ground                                                                                                                                                                             |

| T <sub>TX-IDLE-MIN</sub>          | Minimum time<br>spent in<br>Electrical Idle                                                                       | 50  | _       | _             | UI    | Minimum time a Transmitter must be in Electrical<br>Idle Utilized by the Receiver to start looking for an<br>Electrical Idle Exit after successfully receiving an<br>Electrical Idle ordered set                                                     |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Maximum time to<br>transition to a<br>valid Electrical<br>idle after sending<br>an Electrical Idle<br>ordered set | _   |         | 20            | UI    | After sending an Electrical Idle ordered set, the<br>Transmitter must meet all Electrical Idle<br>Specifications within this time. This is considered a<br>debounce time for the Transmitter to meet Electrical<br>Idle after transitioning from L0. |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Maximum time to<br>transition to valid<br>TX specifications<br>after leaving an<br>Electrical idle<br>condition   | _   |         | 20            | UI    | Maximum time to meet all TX specifications when<br>transitioning from Electrical Idle to sending<br>differential data. This is considered a debounce<br>time for the TX to meet all TX specifications after<br>leaving Electrical Idle               |

| RL <sub>TX-DIFF</sub>             | Differential<br>Return Loss                                                                                       | 12  | —       | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                                         |

| RL <sub>TX-CM</sub>               | Common Mode<br>Return Loss                                                                                        | 6   | —       | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                                         |

| Z <sub>TX-DIFF-DC</sub>           | DC Differential<br>TX Impedance                                                                                   | 80  | 100     | 120           | Ω     | TX DC Differential mode Low Impedance                                                                                                                                                                                                                |

| Z <sub>TX-DC</sub>                | Transmitter DC<br>Impedance                                                                                       | 40  | _       | —             | Ω     | Required TX D+ as well as D- DC Impedance during all states                                                                                                                                                                                          |

| L <sub>TX-SKEW</sub>              | Lane-to-Lane<br>Output Skew                                                                                       |     | —       | 500 +<br>2 UI | ps    | Static skew between any two Transmitter Lanes within a single Link                                                                                                                                                                                   |

| C <sub>TX</sub>                   | AC Coupling<br>Capacitor                                                                                          | 75  | —       | 200           | nF    | All Transmitters shall be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See Note 8.                                                                                                   |

Table 62. Differential Transmitter (TX) Output Specifications (continued)

| Symbol                 | Parameter                   | Min | Nominal | Max | Units | Comments                                                                                                                                                          |

|------------------------|-----------------------------|-----|---------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>crosslink</sub> | Crosslink<br>Random Timeout | 0   |         | 1   |       | This random timeout helps resolve conflicts in<br>crosslink configuration by eventually resulting in<br>only one Downstream and one Upstream Port. See<br>Note 7. |

#### Notes:

- 1. No test load is necessarily associated with this value.

- Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 57 and measured over any 250 consecutive TX UIs. (Also refer to the transmitter compliance eye diagram shown in Figure 55.)

- 3. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the Transmitter collected over any 250 consecutive TX UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

- 4. The Transmitter input impedance shall result in a differential return loss greater than or equal to 12 dB and a common mode return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements is 50 ohms to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50 ohm probes—see Figure 57). Note that the series capacitors C<sub>TX</sub> is optional for the return loss measurement.

- 5. Measured between 20-80% at transmitter package pins into a test load as shown in Figure 57 for both V<sub>TX-D+</sub> and V<sub>TX-D-</sub>.

- 6. See Section 4.3.1.8 of the PCI Express Base Specifications Rev 1.0a.

- 7. See Section 4.2.6.3 of the PCI Express Base Specifications Rev 1.0a.

- 8. MPC8572E SerDes transmitter does not have C<sub>TX</sub> built-in. An external AC Coupling capacitor is required.

### 16.4.2 Transmitter Compliance Eye Diagrams

The TX eye diagram in Figure 55 is specified using the passive compliance/test measurement load (see Figure 57) in place of any real PCI Express interconnect + RX component.

There are two eye diagrams that must be met for the transmitter. Both eye diagrams must be aligned in time using the jitter median to locate the center of the eye diagram. The different eye diagrams differ in voltage depending whether it is a transition bit or a de-emphasized bit. The exact reduced voltage level of the de-emphasized bit is always relative to the transition bit.

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

#### NOTE

It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function (that is, least squares and median deviation fits).

PCI Express

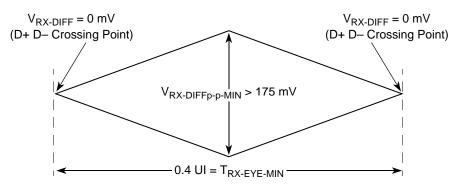

### 16.5 Receiver Compliance Eye Diagrams

The RX eye diagram in Figure 56 is specified using the passive compliance/test measurement load (see Figure 57) in place of any real PCI Express RX component.

Note: In general, the minimum Receiver eye diagram measured with the compliance/test measurement load (see Figure 57) is larger than the minimum Receiver eye diagram measured over a range of systems at the input Receiver of any real PCI Express component. The degraded eye diagram at the input Receiver is due to traces internal to the package as well as silicon parasitic characteristics which cause the real PCI Express component to vary in impedance from the compliance/test measurement load. The input Receiver eye diagram is implementation specific and is not specified. RX component designer should provide additional margin to adequately compensate for the degraded minimum Receiver eye diagram (shown in Figure 56) expected at the input Receiver based on some adequate combination of system simulations and the Return Loss measured looking into the RX package and silicon. The RX eye diagram must be aligned in time using the jitter median to locate the center of the eye diagram.

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

#### NOTE

The reference impedance for return loss measurements is 50. to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50. probes—see Figure 57). Note that the series capacitors, CTX, are optional for the return loss measurement.

Figure 56. Minimum Receiver Eye Timing and Voltage Compliance Specification

Serial RapidIO

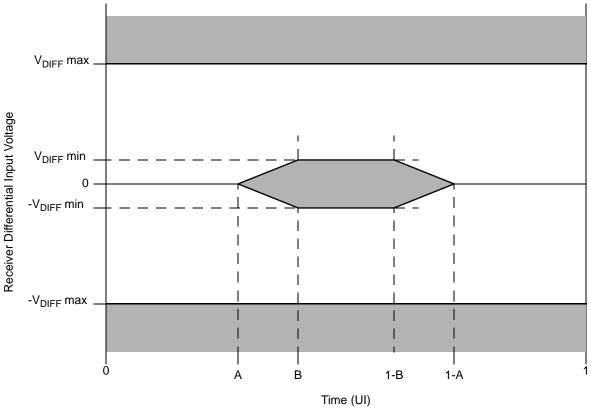

Figure 60. Receiver Input Compliance Mask

| Receiver Type | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|---------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud    | 100                        | 800                        | 0.275  | 0.400  |

| 2.5 GBaud     | 100                        | 800                        | 0.275  | 0.400  |

| 3.125 GBaud   | 100                        | 800                        | 0.275  | 0.400  |

### 17.8 Measurement and Test Requirements

Because the LP-Serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002, the measurement and test requirements defined here are similarly guided by Clause 47. Additionally, the CJPAT test pattern defined in Annex 48A of IEEE 802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter measurements. Annex 48B of IEEE 802.3ae-2002 is recommended as a reference for additional information on jitter test methods.

### 17.8.1 Eye Template Measurements

For the purpose of eye template measurements, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for template measurements is the Continuous Jitter Test Pattern (CJPAT) defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial

link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. The amount of data represented in the eye shall be adequate to ensure that the bit error ratio is less than  $10^{-12}$ . The eye pattern shall be measured with AC coupling and the compliance template centered at 0 Volts differential. The left and right edges of the template shall be aligned with the mean zero crossing points of the measured data eye. The load for this test shall be  $100 \Omega$  resistive +/- 5% differential to 2.5 GHz.

### 17.8.2 Jitter Test Measurements

For the purpose of jitter measurement, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for jitter measurements is the Continuous Jitter Test Pattern (CJPAT) pattern defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. Jitter shall be measured with AC coupling and at 0 Volts differential. Jitter measurement for the transmitter (or for calibration of a jitter tolerance setup) shall be performed with a test procedure resulting in a BER curve such as that described in Annex 48B of IEEE 802.3ae.

### 17.8.3 Transmit Jitter

Transmit jitter is measured at the driver output when terminated into a load of 100  $\Omega$  resistive +/- 5% differential to 2.5 GHz.

### 17.8.4 Jitter Tolerance

Jitter tolerance is measured at the receiver using a jitter tolerance test signal. This signal is obtained by first producing the sum of deterministic and random jitter defined in Section 17.6, "Receiver Specifications," and then adjusting the signal amplitude until the data eye contacts the 6 points of the minimum eye opening of the receive template shown in Figure 60 and Table 75. Note that for this to occur, the test signal must have vertical waveform symmetry about the average value and have horizontal symmetry (including jitter) about the mean zero crossing. Eye template measurement requirements are as defined above. Random jitter is calibrated using a high pass filter with a low frequency corner at 20 MHz and a 20 dB/decade roll-off below this. The required sinusoidal jitter specified in Section 17.6, "Receiver Specifications," is then added to the signal and the test load is replaced by the receiver being tested.

## **18 Package Description**

This section describes package parameters, pin assignments, and dimensions.

Package Description

#### Table 76. MPC8572E Pinout Listing (continued)

| Signal                                            | Signal Name         | Package Pin Number        | Pin Type | Power<br>Supply  | Notes   |

|---------------------------------------------------|---------------------|---------------------------|----------|------------------|---------|

| TSEC3_GTX_CLK                                     | Transmit Clock Out  | AE17                      | 0        | TV <sub>DD</sub> |         |

| TSEC3_RX_CLK/FEC_RX_CL<br>K/FIFO3_RX_CLK          | Receive Clock       | AF17                      | Ι        | TV <sub>DD</sub> | 1       |

| TSEC3_RX_DV/FEC_RX_DV/<br>FIFO3_RX_DV             | Receive Data Valid  | AG14                      | Ι        | TV <sub>DD</sub> | 1       |

| TSEC3_RX_ER/FEC_RX_ER/<br>FIFO3_RX_ER             | Receive Error       | AH15                      | I        | TV <sub>DD</sub> | 1       |

| TSEC3_TX_CLK/FEC_TX_CL<br>K/FIFO3_TX_CLK          | Transmit Clock In   | AF16                      | I        | TV <sub>DD</sub> | 1       |

| TSEC3_TX_EN/FEC_TX_EN/F<br>IFO3_TX_EN             | Transmit Enable     | AJ18                      | 0        | TV <sub>DD</sub> | 1, 22   |

|                                                   | Three-Speed Et      | hernet Controller 4       |          |                  |         |

| TSEC4_TXD[3:0]/TSEC3_TXD[<br>7:4]/FIFO3_TXD[7:4]  | Transmit Data       | AD15, AC16, AC14,<br>AB16 | 0        | TV <sub>DD</sub> | 1, 5, 9 |

| TSEC4_RXD[3:0]/TSEC3_RXD<br>[7:4]/FIFO3_RXD[7:4]  | Receive Data        | AE15, AF13, AE14,<br>AH14 | Ι        | TV <sub>DD</sub> | 1       |

| TSEC4_GTX_CLK                                     | Transmit Clock Out  | AB14                      | 0        | TV <sub>DD</sub> | _       |

| TSEC4_RX_CLK/TSEC3_COL/<br>FEC_COL/FIFO3_TX_FC    | Receive Clock       | AG13                      | Ι        | TV <sub>DD</sub> | 1       |

| TSEC4_RX_DV/TSEC3_CRS/<br>FEC_CRS/FIFO3_RX_FC     | Receive Data Valid  | AD13                      | I/O      | TV <sub>DD</sub> | 1, 23   |

| TSEC4_TX_EN/TSEC3_TX_E<br>R/FEC_TX_ER/FIFO3_TX_ER | Transmit Enable     | AB15                      | 0        | TV <sub>DD</sub> | 1, 22   |

|                                                   | DU                  | JART                      |          |                  |         |

| UART_CTS[0:1]                                     | Clear to Send       | W30, Y27                  | I        | OV <sub>DD</sub> | _       |

| UART_RTS[0:1]                                     | Ready to Send       | W31, Y30                  | 0        | OV <sub>DD</sub> | 5, 9    |

| UART_SIN[0:1]                                     | Receive Data        | Y26, W29                  | I        | OV <sub>DD</sub> | _       |

| UART_SOUT[0:1]                                    | Transmit Data       | Y25, W26                  | 0        | OV <sub>DD</sub> | 5, 9    |

|                                                   | l <sup>2</sup> C lı | nterface                  | -        |                  |         |

| IIC1_SCL                                          | Serial Clock        | AC30                      | I/O      | OV <sub>DD</sub> | 4, 20   |

| IIC1_SDA                                          | Serial Data         | AB30                      | I/O      | OV <sub>DD</sub> | 4, 20   |

| IIC2_SCL                                          | Serial Clock        | AD30                      | I/O      | OV <sub>DD</sub> | 4, 20   |

| IIC2_SDA                                          | Serial Data         | AD29                      | I/O      | OV <sub>DD</sub> | 4, 20   |

| -                                                 | SerDes (x1          | 0) PCIe, SRIO             |          |                  |         |

Clocking

# 19 Clocking

This section describes the PLL configuration of the MPC8572E. Note that the platform clock is identical to the core complex bus (CCB) clock.

### 19.1 Clock Ranges

Table 77 provides the clocking specifications for both processor cores.

|                               | Maximum Processor Core Frequency |      |          |      |          |      |          |      |      |       |

|-------------------------------|----------------------------------|------|----------|------|----------|------|----------|------|------|-------|

| Characteristic                | 1067 MHz                         |      | 1200 MHz |      | 1333 MHz |      | 1500 MHz |      | Unit | Notes |

|                               | Min                              | Max  | Min      | Max  | Min      | Max  | Min      | Max  |      |       |

| e500 core processor frequency | 800                              | 1067 | 800      | 1200 | 800      | 1333 | 800      | 1500 | MHz  | 1, 2  |

| CCB frequency                 | 400                              | 533  | 400      | 533  | 400      | 533  | 400      | 600  | MHz  |       |

| DDR Data Rate                 | 400                              | 667  | 400      | 667  | 400      | 667  | 400      | 800  | MHz  |       |

#### Table 77. MPC8572E Processor Core Clocking Specifications

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," Section 19.3, "e500 Core PLL Ratio," and Section 19.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

2. The processor core frequency speed bins listed also reflect the maximum platform (CCB) and DDR data rate frequency supported by production test. Running CCB and/or DDR data rate higher than the limit shown above, although logically possible via valid clock ratio setting in some condition, is not supported.

The DDR memory controller can run in either synchronous or asynchronous mode. When running in synchronous mode, the memory bus is clocked relative to the platform clock frequency. When running in asynchronous mode, the memory bus is clocked with its own dedicated PLL with clock provided on DDRCLK input pin. Table 78 provides the clocking specifications for the memory bus.

in the above equation refers to the negotiated link width as the result of PCI Express link training, which may or may not be the same as the link width POR selection.

For proper serial RapidIO operation, the CCB clock frequency must be greater than:

$\frac{2 \times (0.80) \times (\text{serial RapidIO interface frequency}) \times (\text{serial RapidIO link width})}{64}$

See Section 20.4, "1x/4x LP-Serial Signal Descriptions," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* for Serial RapidIO interface width and frequency details.

## 20 Thermal

This section describes the thermal specifications of the MPC8572E.

Table 84 shows the thermal characteristics for the package,  $1023 \ 33 \times 33 \ FC-PBGA$ .

The package uses a  $29.6 \times 29.6$  mm lid that attaches to the substrate. Recommended maximum heat sink force is 10 pounds force (45 Newton).

| Rating                                  | Board             | Symbol            | Value | Unit | Notes |

|-----------------------------------------|-------------------|-------------------|-------|------|-------|

| Junction to ambient, natural convection | Single-layer (1s) | $R_{\Theta J A}$  | 15    | °C/W | 1, 2  |

| Junction to ambient, natural convection | Four-layer (2s2p) | R <sub>ØJA</sub>  | 11    | °C/W | 1, 3  |

| Junction to ambient (at 200 ft./min.)   | Single-layer (1s) | R <sub>ØJMA</sub> | 11    | °C/W | 1, 3  |

| Junction to ambient (ar 200 ft./min.)   | Four-layer (2s2p) | R <sub>ØJMA</sub> | 8     | °C/W | 1, 3  |

| Junction to board                       | —                 | $R_{\Theta J B}$  | 4     | °C/W | 4     |

| Junction to case                        | _                 | $R_{\ThetaJC}$    | 0.5   | °C/W | 5     |

Table 84. Package Thermal Characteristics

Notes:

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance

- 2. Per JEDEC JESD51-2 with the single-layer board (JESD51-3) horizontal.

- 3. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883, Method 1012.1).

### 20.1 Temperature Diode

The MPC8572E has a temperature diode on the microprocessor that can be used in conjunction with other system temperature monitoring devices (such as Analog Devices, ADT7461<sup>TM</sup>). These devices use the negative temperature coefficient of a diode operated at a constant current to determine the temperature of the microprocessor and its environment. It is recommended that each MPC8572E device be calibrated.

The following are the specifications of the on-board temperature diode:

#### MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

NXP Semiconductors

System Design Information

### 21.10.3 SerDes 2 Interface (SGMII) Entirely Unused

If the high-speed SerDes 2 interface (SGMII) is not used at all, the unused pin should be terminated as described in this section.

The following pins must be left unconnected (float):

- SD2\_TX[3:0]

- <u>SD2\_TX[3:0]</u>

- Reserved pins: AF26, AF27

The following pins must be connected to XGND\_SRDS2:

- SD2\_RX[3:0]

- $\overline{\text{SD2}_RX}[3:0]$

- SD2\_REF\_CLK

- SD2\_REF\_CLK

The POR configuration pin cfg\_srds\_sgmii\_en on UART\_RTS[1] can be used to power down SerDes 2 block for power saving. Note that both SVDD\_SRDS2 and XVDD\_SRDS2 must remain powered.

### 21.10.4 SerDes 2 Interface (SGMII) Partly Unused

If only part of the high speed SerDes 2 interface (SGMII) pins are used, the remaining high-speed serial I/O pins should be terminated as described in this section.

The following pins must be left unconnected (float):

- SD2\_TX[3:0]

- <u>SD2\_TX[3:0]</u>

- Reserved pins: AF26, AF27

The following pins must be connected to XGND\_SRDS2:

- SD2\_RX[3:0]

- <u>SD2\_RX[3:0]</u>