#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                 |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                             |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                           |

| Speed                           | 1.2GHz                                                                   |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                    |

| RAM Controllers                 | DDR2, DDR3                                                               |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10/100/1000Mbps (4)                                                      |

| SATA                            | -                                                                        |

| USB                             | -                                                                        |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                   |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                    |

| Package / Case                  | 1023-BFBGA, FCBGA                                                        |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572eclpxatld |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

the upper and lower words of the 64-bit GPRs as they are defined by the SPE APU.

- Embedded vector and scalar single-precision floating-point APUs. Provide an instruction set for single-precision (32-bit) floating-point instructions.

- Double-precision floating-point APU. Provides an instruction set for double-precision (64-bit) floating-point instructions that use the 64-bit GPRs.

- 36-bit real addressing

- Memory management unit (MMU). Especially designed for embedded applications. Supports 4-Kbyte to 4-Gbyte page sizes.

- Enhanced hardware and software debug support

- Performance monitor facility that is similar to, but separate from, the MPC8572E performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operation.

- 1 Mbyte L2 cache/SRAM

- Shared by both cores.

- Flexible configuration and individually configurable per core.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- Per-way allocation of cache region to a given processor.

- SRAM features include the following:

- 1, 2, 4, or 8 ways can be configured as SRAM.

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- e500 coherency module (ECM) manages core and intrasystem transactions

- Address translation and mapping unit (ATMU)

- Twelve local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

Overview

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing.

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs.

- Interrupt summary registers allow fast identification of interrupt source.

- Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, SSL/TLS, SRTP, 802.16e, and 3GPP

- Four crypto-channels, each supporting multi-command descriptor chains

- Dynamic assignment of crypto-execution units through an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- PKEU—public key execution unit

- RSA and Diffie-Hellman; programmable field size up to 4096 bits

- Elliptic curve cryptography with F<sub>2</sub>m and F(p) modes and programmable field size up to 1023 bits

- DEU—Data Encryption Standard execution unit

- DES, 3DES

- Two key (K1, K2, K1) or three key (K1, K2, K3)

- ECB, CBC and OFB-64 modes for both DES and 3DES

- AESU—Advanced Encryption Standard unit

- Implements the Rijndael symmetric key cipher

- ECB, CBC, CTR, CCM, GCM, CMAC, OFB-128, CFB-128, and LRW modes

- 128-, 192-, and 256-bit key lengths

- AFEU—ARC four execution unit

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- MDEU—message digest execution unit

- SHA-1 with 160-bit message digest

- SHA-2 (SHA-256, SHA-384, SHA-512)

- MD5 with 128-bit message digest

- HMAC with all algorithms

- KEU—Kasumi execution unit

- Implements F8 algorithm for encryption and F9 algorithm for integrity checking

- Also supports A5/3 and GEA-3 algorithms

- RNG—random number generator

- XOR engine for parity checking in RAID storage applications

- CRC execution unit

- CRC-32 and CRC-32C

- Pattern Matching Engine with DEFLATE decompression

# NOTE

From a system standpoint, if any of the I/O power supplies ramp prior to the VDD core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-on reset, and extra current may be drawn by the device.

# **3** Power Characteristics

The estimated typical power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III devices with out the L in its part ordering is shown in Table 4.

| CCB Frequency | Core Frequency | Typical-65 <sup>2</sup> | Typical-105 <sup>3</sup> | Maximum <sup>4</sup> | Unit |

|---------------|----------------|-------------------------|--------------------------|----------------------|------|

| 533           | 1067           | 12.3                    | 17.8                     | 18.5                 | W    |

| 533           | 1200           | 12.3                    | 17.8                     | 18.5                 | W    |

| 533           | 1333           | 16.3                    | 22.8                     | 24.5                 | W    |

| 600           | 1500           | 17.3                    | 23.9                     | 25.9                 | W    |

| Table 4. MPC8572E | Power | Dissipation <sup>1</sup> | l |

|-------------------|-------|--------------------------|---|

|                   |       | Dissipation              |   |

Notes:

<sup>1</sup> This reflects the MPC8572E power dissipation excluding the power dissipation from B/G/L/O/T/XV<sub>DD</sub> rails.

$^2~$  Typical-65 is based on V\_DD = 1.1 V, T\_j = 65 °C, running Dhrystone.

<sup>3</sup> Typical-105 is based on  $V_{DD}$  = 1.1 V,  $T_i$  = 105 °C, running Dhrystone.

<sup>4</sup> Maximum is based on  $V_{DD}$  = 1.1 V,  $T_j$  = 105 °C, running a smoke test.

The estimated typical power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III devices with the L in its port ordering is shown in Table 5.

| CCB Frequency | Core Frequency | Typical-65 <sup>2</sup> | Typical-105 <sup>3</sup> | Maximum <sup>4</sup> | Unit |

|---------------|----------------|-------------------------|--------------------------|----------------------|------|

| 533           | 1067           | 12                      | 15                       | 15.8                 | W    |

| 533           | 1200           | 12                      | 15.5                     | 16.3                 | W    |

| 533           | 1333           | 12                      | 15.9                     | 16.9                 | W    |

| 600           | 1500           | 13                      | 18.7                     | 20.0                 | W    |

Table 5. MPC8572EL Power Dissipation <sup>1</sup>

Notes:

<sup>1</sup> This reflects the MPC8572E power dissipation excluding the power dissipation from B/G/L/O/T/XV<sub>DD</sub> rails.

<sup>2</sup> Typical-65 is based on  $V_{DD}$  = 1.1 V, T<sub>j</sub> = 65 °C, running Dhrystone.

<sup>3</sup> Typical-105 is based on V<sub>DD</sub> = 1.1 V,  $T_i$  = 105 °C, running Dhrystone.

$^4$  Maximum is based on V\_{DD} = 1.1 V, T\_j = 105 °C, running a smoke test.

# 4 Input Clocks

# 4.1 System Clock Timing

Table 6 provides the system clock (SYSCLK) AC timing specifications for the MPC8572E.

### Table 6. SYSCLK AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition       | Symbol                                | Min | Typical | Мах     | Unit | Notes   |

|---------------------------|---------------------------------------|-----|---------|---------|------|---------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 33  | —       | 133     | MHz  | 1       |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                   | 7.5 | —       | 30.3    | ns   | —       |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 1.2     | ns   | 2       |

| SYSCLK duty cycle         | t <sub>KHK</sub> /t <sub>SYSCLK</sub> | 40  | —       | 60      | %    | 3       |

| SYSCLK jitter             | —                                     | —   | —       | +/- 150 | ps   | 4, 5, 6 |

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies.Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on SYSCLK.

# 4.2 Real Time Clock Timing

The RTC input is sampled by the platform clock (CCB clock). The output of the sampling latch is then used as an input to the counters of the PIC and the TimeBase unit of the e500. There is no jitter specification. The minimum pulse width of the RTC signal should be greater than 2x the period of the CCB clock. That is, minimum clock high time is  $2 \times t_{CCB}$ , and minimum clock low time is  $2 \times t_{CCB}$ . There is no minimum RTC frequency; RTC may be grounded if not needed.

| PLL config input setup time with stable SYSCLK before HRESET negation                                           | 100 |   | μs      | — |

|-----------------------------------------------------------------------------------------------------------------|-----|---|---------|---|

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET                     | 4   | _ | SYSCLKs | 1 |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET                   | 2   | _ | SYSCLKs | 1 |

| Maximum valid-to-high imp <u>edance time</u> for actively driven POR configs with respect to negation of HRESET | _   | 5 | SYSCLKs | 1 |

Table 9. RESET Initialization Timing Specifications (continued)

#### Notes:

2. Reset assertion timing requirements for DDR3 DRAMs may differ.

### Table 10 provides the PLL lock times.

| Table | 10. | PLL | Lock | Times |

|-------|-----|-----|------|-------|

|-------|-----|-----|------|-------|

| Parameter/Condition | Symbol | Min | Typical | Max |

|---------------------|--------|-----|---------|-----|

| PLL lock times      | —      | 100 | μs      | _   |

| Local bus PLL       | —      | 50  | μs      |     |

# 6 DDR2 and DDR3 SDRAM Controller

This section describes the DC and AC electrical specifications for the DDR2 and DDR3 SDRAM controller interface of the MPC8572E. Note that the required  $GV_{DD}(typ)$  voltage is 1.8Vor 1.5 V when interfacing to DDR2 or DDR3 SDRAM, respectively.

# 6.1 DDR2 and DDR3 SDRAM Interface DC Electrical Characteristics

Table 11 provides the recommended operating conditions for the DDR SDRAM controller of the MPC8572E when interfacing to DDR2 SDRAM.

| Parameter/Condition                              | Symbol              | Min                  | Мах                         | Unit | Notes |

|--------------------------------------------------|---------------------|----------------------|-----------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>    | 1.71                 | 1.89                        | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> n | $0.49 	imes GV_{DD}$ | $0.51 	imes GV_{DD}$        | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>     | $MV_{REF}n - 0.04$   | $MV_{REF}n + 0.04$          | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>     | $MV_{REF}n + 0.125$  | GV <sub>DD</sub> + 0.3      | V    | _     |

| Input low voltage                                | V <sub>IL</sub>     | -0.3                 | MV <sub>REF</sub> n - 0.125 | V    | _     |

| Output leakage current                           | I <sub>OZ</sub>     | -50                  | 50                          | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>     | -13.4                | _                           | mA   | —     |

| Table 11 | DDR2 SDRAM | Interface DC | Electrical | Characteristics | for GV(tvn) | 1 = 18V |

|----------|------------|--------------|------------|-----------------|-------------|---------|

|          |            | menace DO    | Liccultur  | onaracteristics |             | / I.O V |

<sup>1.</sup> SYSCLK is the primary clock input for the MPC8572E.

#### DDR2 and DDR3 SDRAM Controller

### Table 11. DDR2 SDRAM Interface DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V (continued)

| Parameter/Condition                             | Symbol          | Min  | Мах | Unit | Notes |

|-------------------------------------------------|-----------------|------|-----|------|-------|

| Output low current (V <sub>OUT</sub> = 0.280 V) | I <sub>OL</sub> | 13.4 | _   | mA   | _     |

Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm GV}_{\rm DD}$  at all times.

- 2.  $MV_{REF}n$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}n$  may not exceed ±2% of the DC value.

- 3. V<sub>TT</sub> is not applied directly to the device. It is the supply to that far end signal termination is made and is expected to be equal to MV<sub>REF</sub>*n*. This rail should track variations in the DC level of MV<sub>REF</sub>*n*.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

Table 12 provides the recommended operating conditions for the DDR SDRAM controller of the MPC8572E when interfacing to DDR3 SDRAM.

| Parameter/Condition    | Symbol              | Min                  | Typical                            | Max | Unit |

|------------------------|---------------------|----------------------|------------------------------------|-----|------|

| I/O supply voltage     | GV <sub>DD</sub>    | 1.425                | 1.575                              | V   | 1    |

| I/O reference voltage  | MV <sub>REF</sub> n | $0.49 	imes GV_{DD}$ | $0.51 	imes GV_{DD}$               | V   | 2    |

| Input high voltage     | V <sub>IH</sub>     | $MV_{REF}n + 0.100$  | GV <sub>DD</sub>                   | V   | —    |

| Input low voltage      | V <sub>IL</sub>     | GND                  | MV <sub>REF</sub> <i>n</i> - 0.100 | V   | —    |

| Output leakage current | I <sub>OZ</sub>     | -50                  | 50                                 | μΑ  | 3    |

Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm GV}_{\rm DD}$  at all times.

2.  $MV_{REF}n$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}n$  may not exceed ±1% of the DC value.

3. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

#### Table 13 provides the DDR SDRAM controller interface capacitance for DDR2 and DDR3.

#### Table 13. DDR2 and DDR3 SDRAM Interface Capacitance for GV<sub>DD</sub>(typ)=1.8 V and 1.5 V

| Parameter/Condition                          | Symbol           | Min | Typical | Мах | Unit |

|----------------------------------------------|------------------|-----|---------|-----|------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8       | pF  | 1, 2 |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5     | pF  | 1, 2 |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 1.8 V ± 0.090 V (for DDR2), f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

2. This parameter is sampled.  $GV_{DD}$  = 1.5 V ± 0.075 V (for DDR3), f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.175 V.

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

The Fast Ethernet Controller (FEC) operates in MII mode only, and complies with the AC and DC electrical characteristics specified in this chapter for MII. Note that if FEC is used, eTSEC 3 and 4 are only available in SGMII mode.

# 8.1.1 eTSEC DC Electrical Characteristics

All MII, GMII, RMII, and TBI drivers and receivers comply with the DC parametric attributes specified in Table 23 and Table 24. All RGMII, RTBI and FIFO drivers and receivers comply with the DC parametric attributes specified in Table 24. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter                                                    | Symbol                               | Min  | Мах                     | Unit | Notes  |

|--------------------------------------------------------------|--------------------------------------|------|-------------------------|------|--------|

| Supply voltage 3.3 V                                         | LV <sub>DD</sub><br>TV <sub>DD</sub> | 3.13 | 3.47                    | V    | 1, 2   |

| Output high voltage $(LV_{DD}/TV_{DD} = Min, IOH = -4.0 mA)$ | VOH                                  | 2.40 | $LV_{DD}/TV_{DD} + 0.3$ | V    | —      |

| Output low voltage $(LV_{DD}/TV_{DD} = Min, IOL = 4.0 mA)$   | VOL                                  | GND  | 0.50                    | V    | —      |

| Input high voltage                                           | V <sub>IH</sub>                      | 2.0  | $LV_{DD}/TV_{DD} + 0.3$ | V    | —      |

| Input low voltage                                            | V <sub>IL</sub>                      | -0.3 | 0.90                    | V    | —      |

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$    | I <sub>IH</sub>                      | _    | 40                      | μΑ   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                 | I <sub>IL</sub>                      | -600 | —                       | μΑ   | 3      |

| Table 23. | GMII. MII                             | . RMII. a | and TBI DC | Electrical | Characteristics                         |

|-----------|---------------------------------------|-----------|------------|------------|-----------------------------------------|

|           | · · · · · · · · · · · · · · · · · · · | ,         |            |            | ••••••••••••••••••••••••••••••••••••••• |

#### Notes:

<sup>1</sup> LV<sub>DD</sub> supports eTSECs 1 and 2.

$^{2}$  TV<sub>DD</sub> supports eTSECs 3 and 4 or FEC.

$^{3}$  The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1.

### Table 24. MII, GMII, RMII, RGMII, TBI, RTBI, and FIFO DC Electrical Characteristics

| Parameters                                                    | Symbol                             | Min       | Мах                                      | Unit | Notes |

|---------------------------------------------------------------|------------------------------------|-----------|------------------------------------------|------|-------|

| Supply voltage 2.5 V                                          | LV <sub>DD/</sub> TV <sub>DD</sub> | 2.37      | 2.63                                     | V    | 1,2   |

| Output high voltage $(LV_{DD}/TV_{DD} = Min, IOH = -1.0 mA)$  | V <sub>OH</sub>                    | 2.00      | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | —     |

| Output low voltage $(LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA)$ | V <sub>OL</sub>                    | GND – 0.3 | 0.40                                     | V    | —     |

| Input high voltage                                            | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$                  | V    | —     |

| Input low voltage                                             | V <sub>IL</sub>                    | -0.3      | 0.70                                     | V    |       |

| Table 24, MIL GMIL | RMIL RGI | /III. TBI. RTB                          | I, and FIFO DC Electrica | Characteristics | (continued) |

|--------------------|----------|-----------------------------------------|--------------------------|-----------------|-------------|

|                    | ,,       | , , , , , , , , , , , , , , , , , , , , |                          |                 | ooninaca)   |

| Parameters                                                | Symbol          | Min | Мах | Unit | Notes  |

|-----------------------------------------------------------|-----------------|-----|-----|------|--------|

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$ | IIH             | _   | 10  | μA   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)              | Ι <sub>ΙL</sub> | -15 | _   | μΑ   | 3      |

Note:

<sup>1</sup>  $LV_{DD}$  supports eTSECs 1 and 2.

$^{2}$  TV<sub>DD</sub> supports eTSECs 3 and 4 or FEC.

$^3$  Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII and RTBI are presented in this section.

# 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, because they have similar performance and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back on the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source-synchronous timing reference. Typically, the clock edge that launched the data can be used, because the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is a relationship between the maximum FIFO speed and the platform (CCB) frequency. For more information see Section 4.5, "Platform to eTSEC FIFO Restrictions."

Table 25 and Table 26 summarize the FIFO AC specifications.

### Table 25. FIFO Mode Transmit AC Timing Specification

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 2.5V ± 5%

| Parameter/Condition                       | Symbol                              | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK, GTX_CLK clock period <sup>1</sup> | t <sub>FIT</sub>                    | 5.3 | 8.0 | 100 | ns   |

| TX_CLK, GTX_CLK duty cycle                | t <sub>FITH</sub> /t <sub>FIT</sub> | 45  | 50  | 55  | %    |

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

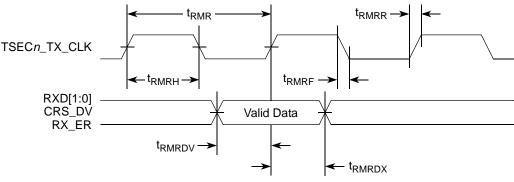

### Table 36. RMII Receive AC Timing Specifications (continued)

At recommended operating conditions with LV\_DD/TV\_DD of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                                              | Symbol <sup>1</sup> | Min | Тур | Мах | Unit |

|------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| RXD[1:0], CRS_DV, RX_ER hold time to<br>TSECn_TX_CLK rising edge | t <sub>RMRDX</sub>  | 2.0 | —   |     | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

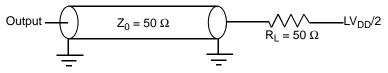

Figure 20 provides the AC test load for eTSEC.

Figure 20. eTSEC AC Test Load

Figure 21 shows the RMII receive AC timing diagram.

Figure 21. RMII Receive AC Timing Diagram

# 8.3 SGMII Interface Electrical Characteristics

Each SGMII port features a 4-wire AC-Coupled serial link from the dedicated SerDes 2 interface of MPC8572E as shown in Figure 22, where  $C_{TX}$  is the external (on board) AC-Coupled capacitor. Each output pin of the SerDes transmitter differential pair features 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to SGND\_SRDS2 (xcorevss). The reference circuit of the SerDes transmitter and receiver is shown in Figure 54.

When an eTSEC port is configured to operate in SGMII mode, the parallel interface's output signals of this eTSEC port can be left floating. The input signals should be terminated based on the guidelines

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 42. eTSEC IEEE 1588 AC Timing Specifications (continued)

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%

| Parameter/Condition           | Symbol                                                  | Min                         | Тур | Мах | Unit | Note |

|-------------------------------|---------------------------------------------------------|-----------------------------|-----|-----|------|------|

| TSEC_1588_CLK_OUT duty cycle  | t <sub>T1588</sub> CLKOTH<br>/t <sub>T1588</sub> CLKOUT | 30                          | 50  | 70  | %    | —    |

| TSEC_1588_PULSE_OUT           | t <sub>T1588OV</sub>                                    | 0.5                         | _   | 3.0 | ns   | —    |

| TSEC_1588_TRIG_IN pulse width | t <sub>T1588</sub> trigh                                | 2*t <sub>T1588CLK_MAX</sub> | _   | —   | ns   | 2    |

#### Note:

1.When TMR\_CTRL[CKSEL] is set as '00', the external TSEC\_1588\_CLK input is selected as the 1588 timer reference clock source, with the timing defined in Table 42, "eTSEC IEEE 1588 AC Timing Specifications." The maximum value of t<sub>T1588CLK</sub> is defined in terms of T<sub>TX\_CLK</sub>, that is the maximum clock cycle period of the equivalent interface speed that the eTSEC1 port is running at. When eTSEC1 is configured to operate in the parallel mode, the T<sub>TX\_CLK</sub> is the maximum clock period of the TSEC1\_TX\_CLK. When eTSEC1 operates in SGMII mode, the maximum value of t<sub>T1588CLK</sub> is defined in terms of the recovered clock from SGMII SerDes. For example, for SGMII 10/100/1000 Mbps modes, the maximum value of t<sub>T1588CLK</sub> is 3600, 360, 72 ns respectively. See the *MPC8572E PowerQUICC™ III Integrated Communications Processor Reference Manual* for detailed description of TMR\_CTRL registers.

2. It needs to be at least two times of the clock period of the clock selected by TMR\_CTRL[CKSEL].

# 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals ECn\_MDIO (management data input/output) and ECn\_MDC (management data clock). The electrical characteristics for GMII, SGMII, RGMII, RMII, TBI and RTBI are specified in "Section 8, "Ethernet: Enhanced Three-Speed Ethernet (eTSEC)."

# 9.1 MII Management DC Electrical Characteristics

The ECn\_MDC and ECn\_MDIO are defined to operate at a supply voltage of 3.3 V or 2.5 V. The DC electrical characteristics for ECn\_MDIO and ECn\_MDC are provided in Table 43 and Table 44.

| Parameter                                                                | Symbol            | Min  | Мах                    | Unit | Notes |

|--------------------------------------------------------------------------|-------------------|------|------------------------|------|-------|

| Supply voltage (3.3 V)                                                   | $LV_{DD}/TV_{DD}$ | 3.13 | 3.47                   | V    | 1, 2  |

| Output high voltage<br>( $LV_{DD}/TV_{DD} = Min, I_{OH} = -1.0 mA$ )     | V <sub>OH</sub>   | 2.10 | OV <sub>DD</sub> + 0.3 | V    | _     |

| Output low voltage $(LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA)$            | V <sub>OL</sub>   | GND  | 0.50                   | V    | _     |

| Input high voltage                                                       | V <sub>IH</sub>   | 2.0  | —                      | V    | _     |

| Input low voltage                                                        | V <sub>IL</sub>   | _    | 0.90                   | V    | _     |

| Input high current $(LV_{DD}/TV_{DD} = Max, V_{IN}^{3} = 2.1 \text{ V})$ | IIH               |      | 40                     | μA   | —     |

Table 43. MII Management DC Electrical Characteristics ( $LV_{DD}/TV_{DD}$ =3.3 V)

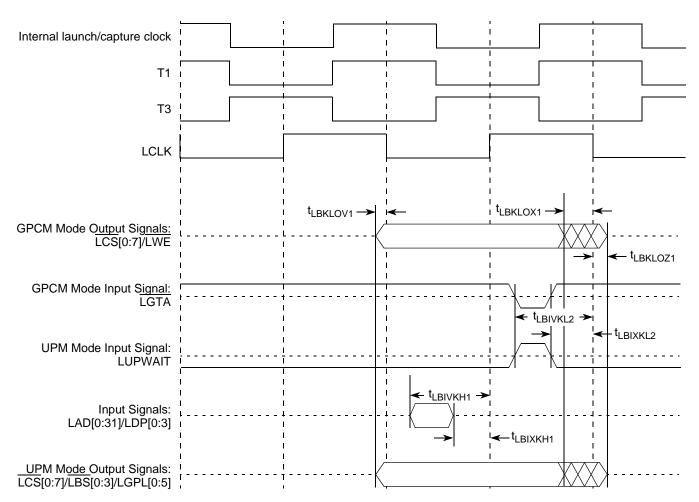

### Table 52. Local Bus General Timing Parameters—PLL Bypassed (continued)

At recommended operating conditions with  $BV_{DD}$  of 3.3 V ± 5%

| Parameter                                                            | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|----------------------------------------------------------------------|----------------------|------|------|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKL2</sub> | -1.3 | _    | ns   | 4, 5  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>lbotot</sub>  | 1.5  | _    | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKLOV1</sub> | _    | -0.3 | ns   |       |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKLOV2</sub> | —    | -0.1 | ns   | 4     |

| Local bus clock to address valid for LAD                             | t <sub>LBKLOV3</sub> | —    | 0.0  | ns   | 4     |

| Local bus clock to LALE assertion                                    | t <sub>LBKLOV4</sub> | —    | 0.0  | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)           | t <sub>LBKLOX1</sub> | -3.3 | _    | ns   | 4     |

| Output hold from local bus clock for LAD/LDP                         | t <sub>LBKLOX2</sub> | -3.3 | —    | ns   | 4     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)   | t <sub>LBKLOZ1</sub> | _    | 0.2  | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP                 | t <sub>lbkloz2</sub> | —    | 0.2  | ns   | 7     |

#### Notes:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to local bus clock for PLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which precedes LCLK by t<sub>LBKHKT</sub>.

- 3. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 4. All signals are measured from BVDD/2 of the rising edge of local bus clock for PLL bypass mode to 0.4 x BVDD of the signal in question for 3.3-V signaling levels.

- 5. Input timings are measured at the pin.

- t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

# NOTE

In PLL bypass mode, LCLK[n] is the inverted version of the internal clock with the delay of  $t_{LBKHKT}$ . In this mode, signals are launched at the rising edge of the internal clock and are captured at the falling edge of the internal clock with the exception of LGTA/LUPWAIT (which is captured on the rising edge of the internal clock).

Local Bus Controller (eLBC)

Figure 33. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Bypass Mode)

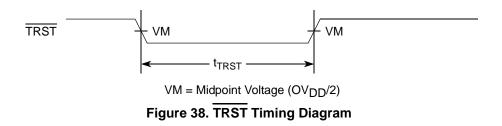

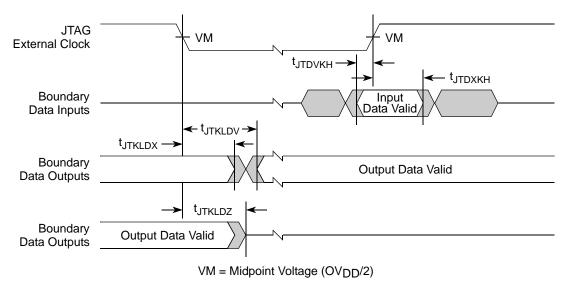

Figure 39 provides the boundary-scan timing diagram.

Figure 39. Boundary-Scan Timing Diagram

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the MPC8572E.

# 13.1 I<sup>2</sup>C DC Electrical Characteristics

Table 54 provides the DC electrical characteristics for the I<sup>2</sup>C interfaces.

| Parameter                                                                                                | Symbol              | Min                 | Мах                    | Unit | Notes |

|----------------------------------------------------------------------------------------------------------|---------------------|---------------------|------------------------|------|-------|

| Input high voltage level                                                                                 | V <sub>IH</sub>     | $0.7 	imes OV_{DD}$ | OV <sub>DD</sub> + 0.3 | V    | —     |

| Input low voltage level                                                                                  | V <sub>IL</sub>     | -0.3                | $0.3 	imes OV_{DD}$    | V    | _     |

| Low level output voltage                                                                                 | V <sub>OL</sub>     | 0                   | 0.4                    | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>I2KHKL</sub> | 0                   | 50                     | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | I                   | -10                 | 10                     | μA   | 3     |

High-Speed Serial Interfaces (HSSI)

# 15 High-Speed Serial Interfaces (HSSI)

The MPC8572E features two Serializer/Deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. The SerDes1 interface can be used for PCI Express and/or Serial RapidIO data transfers. The SerDes2 is dedicated for SGMII application.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 15.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 43 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SDn\_TX and SDn\_TX) or a receiver input (SDn\_RX and  $\overline{SDn_RX}$ ). Each signal swings between A Volts and B Volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

# 1. Single-Ended Swing

The transmitter output signals and the receiver input signals SDn\_TX, SDn\_TX, SDn\_RX and SDn\_RX each have a peak-to-peak swing of A - B Volts. This is also referred as each signal wire's Single-Ended Swing.

2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn_TX} - V_{\overline{SDn_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

3. Differential Input Voltage, V<sub>ID</sub> (or Differential Input Swing):

The Differential Input Voltage (or Swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{SDn_RX} - V_{\overline{SDn_RX}}$ . The  $V_{ID}$  value can be either positive or negative.

4. Differential Peak Voltage, V<sub>DIFFp</sub>

The peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak Voltage,  $V_{DIFFp} = |A - B|$  Volts.

# 5. Differential Peak-to-Peak, V<sub>DIFFp-p</sub>

Because the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) Volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak-to-Peak Voltage,  $V_{DIFFp-p} = 2*V_{DIFFp} = 2*|(A – B)|$  Volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2*|V_{OD}|$ .

### Table 66. Short Run Transmitter AC Timing Specifications—2.5 GBaud (continued)

| Characteristic       | Symbol          | Ra  | nge  | Unit | Notes                                                                  |

|----------------------|-----------------|-----|------|------|------------------------------------------------------------------------|

| Characteristic       | Symbol          | Min | Мах  | Onic | NOICS                                                                  |

| Multiple Output skew | S <sub>MO</sub> | _   | 1000 | -    | Skew at the transmitter output<br>between lanes of a multilane<br>link |

| Unit Interval        | UI              | 400 | 400  | ps   | +/- 100 ppm                                                            |

### Table 67. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                            |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|--|

|                             | Symbol              | Min   | Мах  | Onic   | NOICS                                                                            |  |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |  |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | —                                                                                |  |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                                |  |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                                |  |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |  |

| Unit Interval               | UI                  | 320   | 320  | ps     | +/- 100 ppm                                                                      |  |

# Table 68. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                            |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|--|

| Characteristic              | Symbol              | Min   | Мах  |        | NOLES                                                                            |  |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |  |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | —                                                                                |  |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                                |  |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                                |  |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |  |

| Unit Interval               | UI                  | 800   | 800  | ps     | +/- 100 ppm                                                                      |  |

|              |                              | ,                                                                                                                                                                                                                                                                                                                                 |          | Baura            |       |

|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| Signal       | Signal Name                  | Package Pin Number                                                                                                                                                                                                                                                                                                                | Pin Type | Power<br>Supply  | Notes |

| D1_MCAS      | Column Address Strobe        | AC9                                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> |       |

| D1_MRAS      | Row Address Strobe           | AB12                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> |       |

| D1_MCKE[0:3] | Clock Enable                 | M8, L9, T9, N8                                                                                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | 11    |

| D1_MCS[0:3]  | Chip Select                  | AB9, AF10, AB11,<br>AE11                                                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | _     |

| D1_MCK[0:5]  | Clock                        | V7, E13, AH11, Y9,<br>F14, AG10                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | _     |

| D1_MCK[0:5]  | Clock Complements            | Y10, E12, AH12, AA11,<br>F13, AG11                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub> |       |

| D1_MODT[0:3] | On Die Termination           | AD10, AF12, AC10,<br>AE12                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | _     |

| D1_MDIC[0:1] | Driver Impedance Calibration | E15, G14                                                                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | 25    |

|              | DDR SDRAM Mem                | ory Interface 2                                                                                                                                                                                                                                                                                                                   |          |                  |       |

| D2_MDQ[0:63] | Data                         | A6, B7, C5, D5, A7, C8,<br>D8, D6, C4, A3, D3,<br>D2, B4, A4, B1, C1, E3,<br>E1, G2, G6, D1, E4,<br>G5, G3, J4, J2, P4, R5,<br>H3, H1, N5, N3, Y6, Y4,<br>AC3, AD2, V5, W5,<br>AB2, AB3, AD5, AE3,<br>AF6, AG7, AC4, AD4,<br>AF4, AF7, AH5, AJ1,<br>AL2, AM3, AH3, AH6,<br>AM1, AL3, AK5, AL5,<br>AJ7, AK7, AK4, AM4,<br>AL6, AM7 | I/O      | GV <sub>DD</sub> |       |

| D2_MECC[0:7] | Error Correcting Code        | J5, H7, L7, N6, H4, H6,<br>M4, M5                                                                                                                                                                                                                                                                                                 | I/O      | GV <sub>DD</sub> |       |

| D2_MAPAR_ERR | Address Parity Error         | N1                                                                                                                                                                                                                                                                                                                                | I        | GV <sub>DD</sub> |       |

| D2_MAPAR_OUT | Address Parity Out           | W2                                                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub> | _     |

| D2_MDM[0:8]  | Data Mask                    | A5, B3, F4, J1, AA4,<br>AE5, AK1, AM5, K5                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> |       |

| D2_MDQS[0:8] | Data Strobe                  | B6, C2, F5, L4, AB5,<br>AF3, AL1, AM6, L6                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | —     |

| D2_MDQS[0:8] | Data Strobe                  | C7, A2, F2, K3, AA5,<br>AE6, AK2, AJ6, K6                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> |       |

| D2_MA[0:15]  | Address                      | W1, U4, U3, T1, T2, T3,<br>R1, R2, T5, R4, Y3, P1,<br>N2, AF1, M2, M1                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> |       |

# Table 76. MPC8572E Pinout Listing (continued)

| Table 76. MPC8572E Pinout Listing (continued) |

|-----------------------------------------------|

|-----------------------------------------------|

| Signal      | Signal Name                                                                      | Package Pin Number                        | Pin Type | Power<br>Supply            | Notes |

|-------------|----------------------------------------------------------------------------------|-------------------------------------------|----------|----------------------------|-------|

| SD1_RX[7:0] | Receive Data (positive)                                                          | P32, N30, M32, L30,<br>G30, F32, E30, D32 | I        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_RX[7:0] | Receive Data (negative)                                                          | P31, N29, M31, L29,<br>G29, F31, E29, D31 | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[7]   | PCIe1 Tx Data Lane 7 / SRIO or<br>PCIe2 Tx Data Lane 3 / PCIe3<br>TX Data Lane 1 | M26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 |       |

| SD1_TX[6]   | PCIe1 Tx Data Lane 6 / SRIO or<br>PCIe2 Tx Data Lane 2 / PCIe3<br>TX Data Lane 0 | L24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[5]   | PCIe1 Tx Data Lane 5 / SRIO or<br>PCIe2 Tx Data Lane 1                           | K26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[4]   | PCIe1 Tx Data Lane 4 / SRIO or<br>PCIe2 Tx Data Lane 0                           | J24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[3]   | PCIe1 Tx Data Lane 3                                                             | G24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[2]   | PCIe1 Tx Data Lane 2                                                             | F26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[1]   | PCIe1 Tx Data Lane 1]                                                            | E24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[0]   | PCIe1 Tx Data Lane 0                                                             | D26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[7:0] | Transmit Data (negative)                                                         | M27, L25, K27, J25,<br>G25, F27, E25, D27 | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_PLL_TPD | PLL Test Point Digital                                                           | J32                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | 17    |

| SD1_REF_CLK | PLL Reference Clock                                                              | H32                                       | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_REF_CLK | PLL Reference Clock<br>Complement                                                | H31                                       | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| Reserved    | -                                                                                | С29, К32                                  |          | —                          | 26    |

| Reserved    | -                                                                                | С30, К31                                  |          | —                          | 27    |

| Reserved    | -                                                                                | C24, C25, H26, H27                        | _        | —                          | 28    |

| Reserved    | _                                                                                | AL20, AL21                                |          |                            | 29    |

|             | SerDes (x4)                                                                      | SGMII                                     |          |                            |       |

| SD2_RX[3:0] | Receive Data (positive)                                                          | AK32, AJ30, AF30,<br>AE32                 | I        | XV <sub>DD_SR</sub><br>DS2 | _     |

Package Description

| Signal     | Signal Name                             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Type | Power<br>Supply | Notes |

|------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|-------|

|            | Power and Grou                          | und Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                 |       |

| GND        | Ground                                  | A18, A25, A29, C3, C6,<br>C9, C12, C15, C20,<br>C22, E5, E8, E11, E14,<br>F3, G7, G10, G13,<br>G16, H5, H21, J3, J9,<br>J12, J18, K7, L5, L13,<br>L15, L16, L21, M3, M9,<br>M12, M14, M16, M18,<br>N7, N13, N15, N17,<br>N19, N21, N23, P5,<br>P12, P14, P16, P20,<br>P22, R3, R9, R11, R13,<br>R15, R17, R19, R21,<br>R23, R26, T7, T12,<br>T14, T16, T18, T20,<br>T22, T30, U5, U11,<br>U13, U15, U16, U17,<br>U19, U21, U23, U25,<br>V3, V9, V12, V14, V16,<br>V18, V20, V22, W7,<br>W11, W13, W15, W17,<br>W19, W21, W27, W32,<br>Y5, Y12, Y14, Y16,<br>Y18, Y20, AA3, AA9,<br>AA13, AA15, AA17,<br>AA19, AA21, AA30,<br>AB7, AB26, AC5,<br>AC11, AC13, AD3,<br>AD9, AD14, AD17,<br>AD22, AE7, AE13,<br>AF5, AF11, AG3, AG9,<br>AG15, AG19, AH7,<br>AH13, AH22, AJ5,<br>AJ11, AJ17, AK3, AK9,<br>AK15, AK24, AL7,<br>AL13, AL19, AL26 |          |                 |       |

| XGND_SRDS1 | SerDes Transceiver Pad GND<br>(xpadvss) | C23, C27, D23, D25,<br>E23, E26, F23, F24,<br>G23, G27, H23, H25,<br>J23, J26, K23, K24,<br>L27, M25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —        |                 | —     |

| XGND_SRDS2 | SerDes Transceiver Pad GND<br>(xpadvss) | AD23, AD25, AE23,<br>AE27, AF23, AF24,<br>AG23, AG26, AH23,<br>AH25, AJ27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | _               |       |

# Table 76. MPC8572E Pinout Listing (continued)

Package Description

| Signal     | Signal Name                              | Package Pin Number                                                                                                                                                                                                                                                                                                        | Pin Type | Power<br>Supply     | Notes |

|------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|-------|

| VDD        | Core, L2, Logic Supply                   | L14, M13, M15, M17,<br>N12, N14, N16, N20,<br>N22, P11, P13, P15,<br>P17, P19, P21, P23,<br>R12, R14, R16, R18,<br>R20, R22, T13, T15,<br>T19, T21, T23, U12,<br>U14, U18, U20, U22,<br>V13, V15, V17, V19,<br>V21, W12, W14, W16,<br>W18, W20, W22, Y13,<br>Y15, Y17, Y19, Y21,<br>AA12, AA14, AA16,<br>AA18, AA20, AB13 | _        | VDD                 |       |

| SVDD_SRDS1 | SerDes Core 1 Logic Supply<br>(xcorevdd) | C31, D29, E28, E32,<br>F30, G28, G31, H29,<br>K30, L31, M29, N32,<br>P30                                                                                                                                                                                                                                                  | _        | _                   |       |

| SVDD_SRDS2 | SerDes Core 2 Logic Supply<br>(xcorevdd) | AD32, AF31, AG29,<br>AJ32, AK29, AK30                                                                                                                                                                                                                                                                                     | —        | —                   | _     |

| XVDD_SRDS1 | SerDes1 Transceiver Supply<br>(xpadvdd)  | C26, D24, E27, F25,<br>G26, H24, J27, K25,<br>L26, M24, N27                                                                                                                                                                                                                                                               | _        | _                   | _     |

| XVDD_SRDS2 | SerDes2 Transceiver Supply (xpadvdd)     | AD24, AD28, AE26,<br>AF25, AG27, AH24,<br>AJ26                                                                                                                                                                                                                                                                            | _        | -                   |       |

| AVDD_LBIU  | Local Bus PLL Supply                     | A19                                                                                                                                                                                                                                                                                                                       |          | —                   | 19    |

| AVDD_DDR   | DDR PLL Supply                           | AM20                                                                                                                                                                                                                                                                                                                      | —        | —                   | 19    |

| AVDD_CORE0 | CPU PLL Supply                           | B18                                                                                                                                                                                                                                                                                                                       | —        | —                   | 19    |

| AVDD_CORE1 | CPU PLL Supply                           | A17                                                                                                                                                                                                                                                                                                                       | —        | —                   | 19    |

| AVDD_PLAT  | Platform PLL Supply                      | AB32                                                                                                                                                                                                                                                                                                                      | _        |                     | 19    |

| AVDD_SRDS1 | SerDes1 PLL Supply                       | J29                                                                                                                                                                                                                                                                                                                       | _        | _                   | 19    |

| AVDD_SRDS2 | SerDes2 PLL Supply                       | AH29                                                                                                                                                                                                                                                                                                                      | _        | —                   | 19    |

| SENSEVDD   | VDD Sensing Pin                          | N18                                                                                                                                                                                                                                                                                                                       | _        | _                   | 13    |

| SENSEVSS   | GND Sensing Pin                          | P18                                                                                                                                                                                                                                                                                                                       | _        |                     | 13    |

|            | Analog S                                 | ignals                                                                                                                                                                                                                                                                                                                    |          |                     |       |

| MVREF1     | SSTL_1.8 Reference Voltage               | C16                                                                                                                                                                                                                                                                                                                       | I        | GV <sub>DD</sub> /2 | _     |

| MVREF2     | SSTL_1.8 Reference Voltage               | AM19                                                                                                                                                                                                                                                                                                                      | I        | GV <sub>DD</sub> /2 | _     |

|            | 1                                        | 1                                                                                                                                                                                                                                                                                                                         |          |                     |       |

# Table 76. MPC8572E Pinout Listing (continued)

System Design Information

#### Notes:

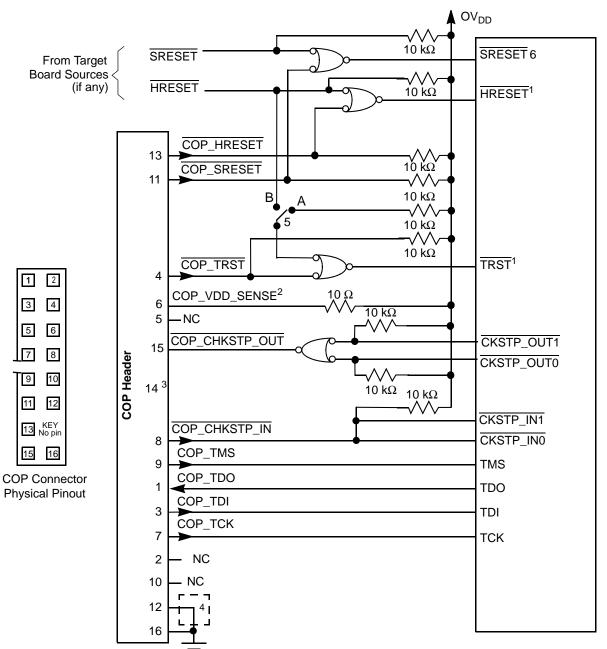

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor to fully control the processor as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- 5. This switch is included as a precaution for BSDL testing. The switch should be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed to position B.

- 6. Asserting SRESET causes a machine check interrupt to the e500 cores.