Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| ore Processor Pow<br>Jumber of Cores/Bus Width 2 Coreed 1.06<br>p-Processors/DSP Sign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | solete  werPC e500  Core, 32-Bit  67GHz  nal Processing; SPE, Security; SEC  R2, DDR3 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| ore Processor  Pow  Jumber of Cores/Bus Width  2 Co  Jumper of Cores/Bus Width  3 Co  Jumper of Cores/Bus Width  4 Co  Jumper of Cores/Bus Width  4 Co  Jumper of Cores/Bus Width  5 Co  Jumper of Cores/Bus Width  5 Co  Jumper of Cores/Bus Width  6 Co  Jumper of Cores/Bus Width  6 Co  Jumper of Cores/Bus Width  6 Co  Jumper of Cores/Bus Width  7 Co  Jumper of Cores/Bus Width  7 Co  Jumper of Cores/Bus Width  8 Co  Jumper of Co  Jumper of Cores/Bus Width  9 Co  Jumper of | werPC e500 Core, 32-Bit 167GHz nal Processing; SPE, Security; SEC R2, DDR3            |

| umber of Cores/Bus Width 2 Coreed 1.06 p-Processors/DSP Sign AM Controllers DDF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Core, 32-Bit 167GHz nal Processing; SPE, Security; SEC R2, DDR3                       |

| peed 1.06 p-Processors/DSP Sign AM Controllers DDF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nal Processing; SPE, Security; SEC                                                    |

| p-Processors/DSP Sign<br>AM Controllers DDF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nal Processing; SPE, Security; SEC<br>R2, DDR3                                        |

| AM Controllers DDF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R2, DDR3                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·                                                                                     |

| aphics Acceleration No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                       |

| splay & Interface Controllers -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |

| hernet 10/3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (100/1000Mbps (4)                                                                     |

| TA -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |

| SB -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |

| oltage - I/O 1.5\                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V, 1.8V, 2.5V, 3.3V                                                                   |

| perating Temperature -40°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | °C ~ 105°C (TA)                                                                       |

| curity Features Cryp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ptography, Random Number Generator                                                    |

| ckage / Case 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23-BBGA, FCBGA                                                                        |

| pplier Device Package 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23-FCPBGA (33x33)                                                                     |

| rchase URL http                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ps://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572ecvjarle                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Electrical Characteristics**

# 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values shown are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

**Table 2. Recommended Operating Conditions**

| Characteristic                                                                                                    |                                                                   | Symbol                                   | Recommended Value                                  | Unit | Notes |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------|----------------------------------------------------|------|-------|

| Core supply voltage                                                                                               |                                                                   | V <sub>DD</sub>                          | 1.1 V ± 55 mV                                      | V    | _     |

| PLL supply voltage                                                                                                |                                                                   | AV <sub>DD</sub>                         | 1.1 V ± 55 mV                                      | V    | 1     |

| Core power supply for SerDes transceivers                                                                         |                                                                   | SV <sub>DD</sub>                         | 1.1 V ± 55 mV                                      | V    | _     |

| Pad power supply fo                                                                                               | r SerDes transceivers                                             | $XV_{DD}$                                | 1.1 V ± 55 mV                                      | V    | _     |

| DDR SDRAM DDR2 SDRAM Interface                                                                                    |                                                                   | GV <sub>DD</sub>                         | 1.8 V ± 90 mV                                      | V    | _     |

| Controller I/O supply voltage                                                                                     | DDR3 SDRAM Interface                                              |                                          | 1.5 V ± 75 mV                                      |      | _     |

| Three-speed Ethernet I/O voltage                                                                                  |                                                                   | LV <sub>DD</sub>                         | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | 4     |

|                                                                                                                   |                                                                   | TV <sub>DD</sub>                         | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   |      | 4     |

| DUART, system con                                                                                                 | trol and power management, I <sup>2</sup> C, and JTAG I/O voltage | OV <sub>DD</sub>                         | 3.3 V ± 165 mV                                     | V    | 3     |

| Local bus and GPIO I/O voltage                                                                                    |                                                                   | BV <sub>DD</sub>                         | 3.3 V ± 165 mV<br>2.5 V ± 125 mV<br>1.8 V ± 90 mV  | V    | _     |

| Input voltage                                                                                                     | DDR2 and DDR3 SDRAM Interface signals                             | MV <sub>IN</sub>                         | GND to GV <sub>DD</sub>                            | V    | 2     |

|                                                                                                                   | DDR2 and DDR3 SDRAM Interface reference                           | MV <sub>REF</sub> n                      | GV <sub>DD</sub> /2 ± 1%                           | V    | _     |

| Three-speed Ethernet signals                                                                                      |                                                                   | LV <sub>IN</sub><br>TV <sub>IN</sub>     | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V    | 4     |

| Local bus and GPIO signals                                                                                        |                                                                   | BV <sub>IN</sub> GND to BV <sub>DD</sub> |                                                    | V    | _     |

| Local bus, DUART, SYSCLK, Serial RapidIO, system control and power management, I <sup>2</sup> C, and JTAG signals |                                                                   | OV <sub>IN</sub>                         | GND to OV <sub>DD</sub>                            | V    | 3     |

| Junction temperature                                                                                              | e range                                                           | TJ                                       | 0 to 105                                           | °C   | _     |

### Notes:

- 1. This voltage is the input to the filter discussed in Section 21.2.1, "PLL Power Supply Filtering," and not necessarily the voltage at the AV<sub>DD</sub> pin, that may be reduced from V<sub>DD</sub> by the filter.

- 2. **Caution:**  $MV_{IN}$  must not exceed  $GV_{DD}$  by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. Caution:  $OV_{IN}$  must not exceed  $OV_{DD}$  by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- Caution: L/TV<sub>IN</sub> must not exceed L/TV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

**Electrical Characteristics**

# 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths.

**Table 3. Output Drive Capability**

| Driver Type                           | Programmable Output Impedance $(\Omega)$ | Supply<br>Voltage                                                                   | Notes |

|---------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>35                                 | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V                                | 1     |

|                                       | 45(default)<br>45(default)<br>125        | $BV_{DD} = 3.3 \text{ V}$<br>$BV_{DD} = 2.5 \text{ V}$<br>$BV_{DD} = 1.8 \text{ V}$ |       |

| DDR2 signal                           | 18<br>36 (half strength mode)            | GV <sub>DD</sub> = 1.8 V                                                            | 2     |

| DDR3 signal                           | 20<br>40 (half strength mode)            | GV <sub>DD</sub> = 1.5 V                                                            | 2     |

| eTSEC/10/100 signals                  | 45                                       | L/TV <sub>DD</sub> = 2.5/3.3 V                                                      | _     |

| DUART, system control, JTAG           | 45                                       | OV <sub>DD</sub> = 3.3 V                                                            | _     |

| I2C                                   | 150                                      | OV <sub>DD</sub> = 3.3 V                                                            | _     |

#### Notes:

# 2.2 Power Sequencing

The MPC8572E requires its power rails to be applied in a specific sequence to ensure proper device operation. These requirements are as follows for power up:

- 1.  $V_{DD}$ ,  $AV_{DD\_n}$ ,  $BV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ ,  $SV_{DD\_SRDS1}$  and  $SV_{DD\_SRDS2}$ ,  $TV_{DD}$ ,  $XV_{DD\_SRDS1}$  and  $XV_{DD\_SRDS2}$

- $2. \text{ GV}_{DD}$

All supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

To guarantee MCKE low during power-on reset, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-on reset, then the sequencing for  $GV_{DD}$  is not required.

<sup>1.</sup> The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

<sup>2.</sup> The drive strength of the DDR2 or DDR3 interface in half-strength mode is at  $T_i = 105$ °C and at  $GV_{DD}$  (min).

### **DDR2 and DDR3 SDRAM Controller**

### Table 17. DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                         | Symbol  | Min  | Max | Unit | Notes |

|-----------------------------------|---------|------|-----|------|-------|

| Controller Skew for MDQS—MDQ/MECC | tciskew | _    | _   | ps   | 1, 2  |

| 800 MHz                           | _       | -200 | 200 | _    | _     |

| 667 MHz                           | _       | -240 | 240 | _    | _     |

| 533 MHz                           | _       | -300 | 300 | _    | _     |

| 400 MHz                           | _       | -365 | 365 | _    | _     |

#### Note:

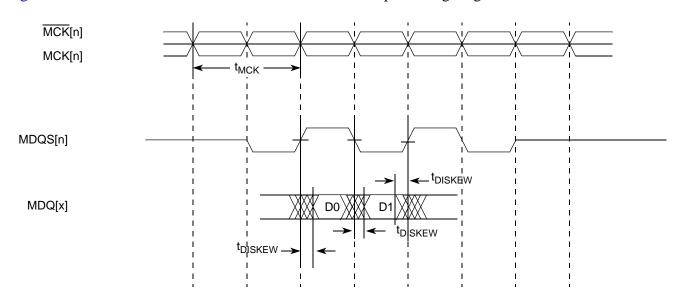

- 1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

- 2. The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called tDISKEW. This can be determined by the following equation: tDISKEW =+/-(T/4 abs(tCISKEW)) where T is the clock period and abs(tCISKEW) is the absolute value of tCISKEW.

Figure 3 shows the DDR2 and DDR3 SDRAM interface input timing diagram.

Figure 3. DDR2 and DDR3 SDRAM Interface Input Timing Diagram

# 6.2.2 DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications

Table 18 contains the output AC timing targets for the DDR2 and DDR3 SDRAM interface.

## Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                                 | Symbol <sup>1</sup> | Min | Max | Unit | Notes |

|-------------------------------------------|---------------------|-----|-----|------|-------|

| MCK[n] cycle time                         | t <sub>MCK</sub>    | 2.5 | 5   | ns   | 2     |

| ADDR/CMD output setup with respect to MCK | t <sub>DDKHAS</sub> |     |     | ns   | 3     |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

Table 20 provides the differential specifications for the MPC8572E differential signals MDQS/MDQS and  $MCK/\overline{MCK}$  when in DDR3 mode.

**Table 20. DDR3 SDRAM Differential Electrical Characteristics**

| Parameter/Condition                 | Symbol            | Min | Max | Unit | Notes |

|-------------------------------------|-------------------|-----|-----|------|-------|

| DC Input Signal Voltage             | V <sub>IN</sub>   | _   | _   | mV   | _     |

| DC Differential Input Voltage       | V <sub>ID</sub>   | _   | _   | mV   | _     |

| AC Differential Input Voltage       | V <sub>IDAC</sub> | _   | _   | mV   | _     |

| DC Differential Output Voltage      | V <sub>OH</sub>   | _   | _   | mV   | _     |

| AC Differential Output Voltage      | V <sub>OHAC</sub> | _   | _   | mV   | _     |

| AC Differential Cross-point Voltage | V <sub>IXAC</sub> | _   | _   | mV   | _     |

| Input Midpoint Voltage              | $V_{MP}$          |     | _   | mV   | _     |

# **DUART**

This section describes the DC and AC electrical specifications for the DUART interface of the MPC8572E.

#### **DUART DC Electrical Characteristics** 7.1

Table 21 provides the DC electrical characteristics for the DUART interface.

**Table 21. DUART DC Electrical Characteristics**

| Parameter                                                                                | Symbol           | Min  | Max                    | Unit |

|------------------------------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage (3.3 V)                                                                   | OV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| High-level input voltage                                                                 | V <sub>IH</sub>  | 2    | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                  | V <sub>IL</sub>  | -0.3 | 0.8                    | V    |

| Input current (V <sub>IN</sub> <sup>1</sup> = 0 V or V <sub>IN</sub> = V <sub>DD</sub> ) | I <sub>IN</sub>  | _    | ±5                     | μΑ   |

| High-level output voltage (OV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA)              | V <sub>OH</sub>  | 2.4  | _                      | ٧    |

| Low-level output voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)                | V <sub>OL</sub>  | _    | 0.4                    | ٧    |

## Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1.

**NXP Semiconductors** 27

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

The Fast Ethernet Controller (FEC) operates in MII mode only, and complies with the AC and DC electrical characteristics specified in this chapter for MII. Note that if FEC is used, eTSEC 3 and 4 are only available in SGMII mode.

## 8.1.1 eTSEC DC Electrical Characteristics

All MII, GMII, RMII, and TBI drivers and receivers comply with the DC parametric attributes specified in Table 23 and Table 24. All RGMII, RTBI and FIFO drivers and receivers comply with the DC parametric attributes specified in Table 24. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

**Parameter** Symbol Unit Min Max **Notes** 1, 2 Supply voltage 3.3 V 3.47 V  $LV_{DD}$ 3.13  $TV_{DD}$ Output high voltage VOH  $LV_{DD}/TV_{DD} + 0.3$ ٧ 2.40  $(LV_{DD}/TV_{DD} = Min, IOH = -4.0 mA)$ Output low voltage VOL **GND** 0.50 ٧  $(LV_{DD}/TV_{DD} = Min, IOL = 4.0 mA)$ Input high voltage  $LV_{DD}/TV_{DD} + 0.3$ 2.0  $V_{IH}$ Input low voltage  $V_{IL}$ -0.3 0.90 ٧ Input high current 40 1, 2,3 μΑ  $I_{IH}$  $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$ 3 Input low current  $I_{IL}$ -600μΑ  $(V_{IN} = GND)$

Table 23. GMII, MII, RMII, and TBI DC Electrical Characteristics

### Notes:

Table 24. MII, GMII, RMII, RGMII, TBI, RTBI, and FIFO DC Electrical Characteristics

| Parameters                                                                                 | Symbol                             | Min       | Max                     | Unit | Notes |

|--------------------------------------------------------------------------------------------|------------------------------------|-----------|-------------------------|------|-------|

| Supply voltage 2.5 V                                                                       | LV <sub>DD/</sub> TV <sub>DD</sub> | 2.37      | 2.63                    | V    | 1,2   |

| Output high voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, IOH = -1.0 mA)           | V <sub>OH</sub>                    | 2.00      | $LV_{DD}/TV_{DD} + 0.3$ | V    | _     |

| Output low voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>                    | GND - 0.3 | 0.40                    | V    | _     |

| Input high voltage                                                                         | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$ | V    | _     |

| Input low voltage                                                                          | V <sub>IL</sub>                    | -0.3      | 0.70                    | V    | _     |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

<sup>&</sup>lt;sup>1</sup> LV<sub>DD</sub> supports eTSECs 1 and 2.

<sup>&</sup>lt;sup>2</sup> TV<sub>DD</sub> supports eTSECs 3 and 4 or FEC.

$<sup>^3</sup>$  The symbol  $V_{IN}$ , in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1.

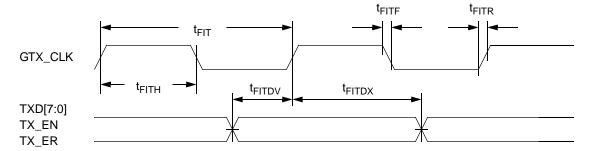

## **Table 25. FIFO Mode Transmit AC Timing Specification (continued)**

At recommended operating conditions with LV  $_{DD}/TV_{DD}$  of 2.5V  $\pm\,5\%$

| Parameter/Condition                                    | Symbol             | Min | Тур | Max  | Unit |

|--------------------------------------------------------|--------------------|-----|-----|------|------|

| TX_CLK, GTX_CLK peak-to-peak jitter                    | t <sub>FITJ</sub>  | _   | _   | 250  | ps   |

| Rise time TX_CLK (20%–80%)                             | t <sub>FITR</sub>  | _   | _   | 0.75 | ns   |

| Fall time TX_CLK (80%–20%)                             | t <sub>FITF</sub>  | _   | _   | 0.75 | ns   |

| FIFO data TXD[7:0], TX_ER, TX_EN setup time to GTX_CLK | t <sub>FITDV</sub> | 2.0 | _   | _    | ns   |

| GTX_CLK to FIFO data TXD[7:0], TX_ER, TX_EN hold time  | t <sub>FITDX</sub> | 0.5 | _   | 3.0  | ns   |

#### Notes:

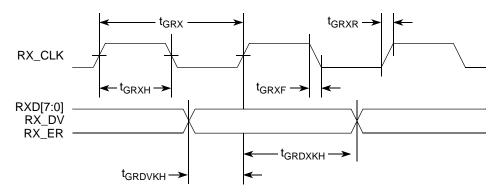

### Table 26. FIFO Mode Receive AC Timing Specification

At recommended operating conditions with LV  $_{DD}/TV_{DD}$  of 2.5V  $\pm\,5\%$

| Parameter/Condition                         | Symbol                              | Min | Тур | Max  | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|------|------|

| RX_CLK clock period <sup>1</sup>            | t <sub>FIR</sub>                    | 5.3 | 8.0 | 100  | ns   |

| RX_CLK duty cycle                           | t <sub>FIRH</sub> /t <sub>FIR</sub> | 45  | 50  | 55   | %    |

| RX_CLK peak-to-peak jitter                  | t <sub>FIRJ</sub>                   | _   | _   | 250  | ps   |

| Rise time RX_CLK (20%–80%)                  | t <sub>FIRR</sub>                   | _   | _   | 0.75 | ns   |

| Fall time RX_CLK (80%–20%)                  | t <sub>FIRF</sub>                   | _   | _   | 0.75 | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>FIRDV</sub>                  | 1.5 | _   | _    | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>FIRDX</sub>                  | 0.5 | _   | _    | ns   |

<sup>1.</sup> The minimum cycle period (or maximum frequency) of the RX\_CLK is dependent on the maximum platform frequency of the speed bins the part belongs to as well as the FIFO mode under operation. Refer to Section 4.5, "Platform to eTSEC FIFO Restrictions," for more detailed description.

Figure 7 and Figure 8 show the FIFO timing diagrams.

Figure 7. FIFO Transmit AC Timing Diagram

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

<sup>1.</sup> The minimum cycle period (or maximum frequency) of the TX\_CLK is dependent on the maximum platform frequency of the speed bins the part belongs to as well as the FIFO mode under operation. Refer to Section 4.5, "Platform to eTSEC FIFO Restrictions," for more detailed description.

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

Figure 11 shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

# 8.2.3 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

# 8.2.3.1 MII Transmit AC Timing Specifications

Table 29 provides the MII transmit AC timing specifications.

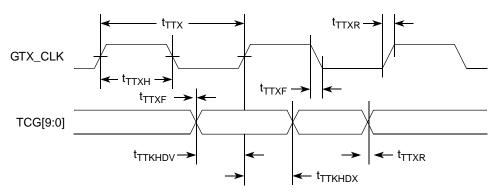

## **Table 29. MII Transmit AC Timing Specifications**

At recommended operating conditions with LV  $_{DD}/TV_{DD}$  of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> <sup>2</sup>       | _   | 400 | _   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                    | _   | 40  | _   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                 | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise (20%-80%)                | t <sub>MTXR</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

| TX_CLK data clock fall (80%-20%)                | t <sub>MTXF</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

### Notes:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)</sub>(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

Figure 15 shows the TBI transmit AC timing diagram.

Figure 15. TBI Transmit AC Timing Diagram

## 8.2.4.2 TBI Receive AC Timing Specifications

Table 32 provides the TBI receive AC timing specifications.

## **Table 32. TBI Receive AC Timing Specifications**

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition <sup>3</sup>                             | Symbol <sup>1</sup>                 | Min | Тур  | Max | Unit |

|--------------------------------------------------------------|-------------------------------------|-----|------|-----|------|

| Clock period for TBI Receive Clock 0, 1                      | t <sub>TRX</sub>                    | _   | 16.0 | _   | ns   |

| Skew for TBI Receive Clock 0, 1                              | t <sub>SKTRX</sub>                  | 7.5 | _    | 8.5 | ns   |

| Duty cycle for TBI Receive Clock 0, 1                        | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  | _    | 60  | %    |

| RCG[9:0] setup time to rising edge of TBI Receive Clock 0, 1 | t <sub>TRDVKH</sub>                 | 2.5 | _    | _   | ns   |

| RCG[9:0] hold time to rising edge of TBI Receive Clock 0, 1  | t <sub>TRDXKH</sub>                 | 1.5 | _    | _   | ns   |

| Clock rise time (20%-80%) for TBI Receive Clock 0, 1         | t <sub>TRXR</sub> <sup>2</sup>      | 0.7 | _    | 2.4 | ns   |

| Clock fall time (80%-20%) for TBI Receive Clock 0, 1         | t <sub>TRXF</sub> <sup>2</sup>      | 0.7 | _    | 2.4 | ns   |

### Notes:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)</sub>(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).

- 2. Guaranteed by design.

- 3. The signals "TBI Receive Clock 0" and "TBI Receive Clock 1" refer to TSECn\_RX\_CLK and TSECn\_TX\_CLK pins respectively. These two clock signals are also referred as PMA\_RX\_CLK[0:1].

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

### Local Bus Controller (eLBC)

Table 48 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 1.8 \text{ V}$  DC.

Table 48. Local Bus DC Electrical Characteristics (1.8 V DC)

| Parameter                                                                                   | Symbol           | Min                     | Max                     | Unit |

|---------------------------------------------------------------------------------------------|------------------|-------------------------|-------------------------|------|

| Supply voltage 1.8V                                                                         | BV <sub>DD</sub> | 1.71                    | 1.89                    | V    |

| High-level input voltage                                                                    | V <sub>IH</sub>  | 0.65 x BV <sub>DD</sub> | BV <sub>DD</sub> + 0.3  | V    |

| Low-level input voltage                                                                     | V <sub>IL</sub>  | -0.3                    | 0.35 x BV <sub>DD</sub> | V    |

| Input current (BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IN</sub>  | TBD                     | TBD                     | μΑ   |

| High-level output voltage $(I_{OH} = -100 \mu A)$                                           | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2  | _                       | V    |

| High-level output voltage (I <sub>OH</sub> = -2 mA)                                         | V <sub>OH</sub>  | BV <sub>DD</sub> - 0.45 | _                       | V    |

| Low-level output voltage (I <sub>OL</sub> = 100 μA)                                         | V <sub>OL</sub>  | _                       | 0.2                     | V    |

| Low-level output voltage (I <sub>OL</sub> = 2 mA)                                           | V <sub>OL</sub>  | _                       | 0.45                    | V    |

### Note:

# 10.2 Local Bus AC Electrical Specifications

Table 49 describes the general timing parameters of the local bus interface at  $BV_{DD} = 3.3 \text{ V DC}$ .

Table 49. Local Bus General Timing Parameters (BV $_{DD}$  = 3.3 V DC)—PLL Enabled At recommended operating conditions with BV $_{DD}$  of 3.3 V  $\pm$  5%.

| Parameter                                                            | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|----------------------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                                 | t <sub>LBK</sub>                    | 6.67 | 12  | ns   | 2     |

| Local bus duty cycle                                                 | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43   | 57  | %    | _     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                 | t <sub>LBKSKEW</sub>                | _    | 150 | ps   | 7,8   |

| Input setup to local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIVKH1</sub>                | 1.8  | _   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                          | t <sub>LBIVKH2</sub>                | 1.7  | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                | t <sub>LBIXKH1</sub>                | 1.0  | _   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKH2</sub>                | 1.0  | _   | ns   | 3, 4  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5  | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKHOV1</sub>                | _    | 2.3 | ns   | _     |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKHOV2</sub>                | _    | 2.4 | ns   | 3     |

| Local bus clock to address valid for LAD                             | t <sub>LBKHOV3</sub>                | —    | 2.3 | ns   | 3     |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

<sup>1.</sup> The symbol  ${\rm BV_{IN}}$ , in this case, represents the  ${\rm BV_{IN}}$  symbol referenced in Table 1.

Figure 32. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Enabled)

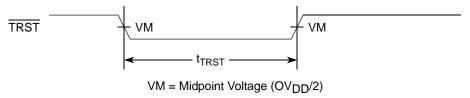

Figure 38. TRST Timing Diagram

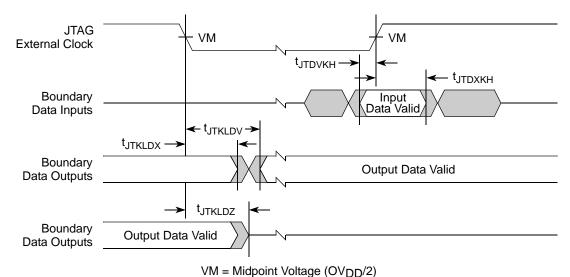

Figure 39 provides the boundary-scan timing diagram.

Figure 39. Boundary-Scan Timing Diagram

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the MPC8572E.

# 13.1 I<sup>2</sup>C DC Electrical Characteristics

Table 54 provides the DC electrical characteristics for the I<sup>2</sup>C interfaces.

**Parameter Symbol** Min Max Unit **Notes**  $\mathsf{V}_{\mathsf{IH}}$  $OV_{DD} + 0.3$ Input high voltage level  $0.7 \times OV_{DD}$ ٧  $V_{IL}$ ٧ Input low voltage level -0.3 $0.3 \times OV_{DD}$ ٧ Low level output voltage  $V_{OL}$ 0 0.4 1 Pulse width of spikes which must be suppressed by the 0 50 2 ns t<sub>12KHKL</sub> input filter Input current each I/O pin (input voltage is between I<sub>I</sub> -10 10 μΑ 3  $0.1 \times OV_{DD}$  and  $0.9 \times OV_{DD}$ (max)

Table 54. I<sup>2</sup>C DC Electrical Characteristics

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

I<sup>2</sup>C

# Table 54. I<sup>2</sup>C DC Electrical Characteristics (continued)

| Capacitance for each I/O pin | C <sub>I</sub> | _ | 10 | pF | _ | Ī |

|------------------------------|----------------|---|----|----|---|---|

|------------------------------|----------------|---|----|----|---|---|

#### Notes:

- 1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2. Refer to the MPC8572E PowerQUICC™ III Integrated Host Processor Family Reference Manual for information on the digital filter used.

- 3. I/O pins will obstruct the SDA and SCL lines if  $\mbox{OV}_{\mbox{\scriptsize DD}}$  is switched off.

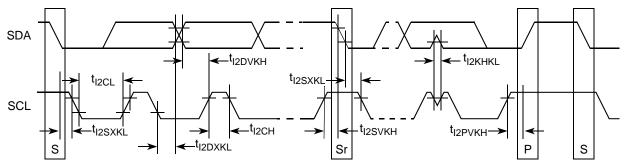

# 13.2 I<sup>2</sup>C AC Electrical Specifications

Table 55 provides the AC timing parameters for the  $I^2C$  interfaces.

## Table 55. I<sup>2</sup>C AC Electrical Specifications

At recommended operating conditions with OV<sub>DD</sub> of 3.3 V  $\pm$  5%. All values refer to V<sub>IH</sub> (min) and V<sub>IL</sub> (max) levels (see Table 2).

| Parameter                                                                                    | Symbol <sup>1</sup> | Min                                | Max              | Unit             |

|----------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------|------------------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0                                  | 400              | kHz <sup>4</sup> |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3                                | _                | μs               |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6                                | _                | μs               |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6                                | _                | μs               |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6                                | _                | μs               |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100                                | _                | ns               |

| Data input hold time:  CBUS compatible masters  I <sup>2</sup> C bus devices                 | t <sub>l2DXKL</sub> | <del>-</del> 0 <sup>2</sup>        | _                | μs               |

| Data output delay time                                                                       | t <sub>I2OVKL</sub> | _                                  | 0.9 <sup>3</sup> | μs               |

| Setup time for STOP condition                                                                | t <sub>I2PVKH</sub> | 0.6                                | _                | μs               |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub> | 1.3                                | _                | μs               |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>     | $0.1 \times \text{OV}_{\text{DD}}$ | _                | V                |

| Noise margin at the HIGH level for each connected device (including hysteresis)              | $V_{NH}$            | $0.2 \times \text{OV}_{\text{DD}}$ | _                | V                |

## Table 55. I<sup>2</sup>C AC Electrical Specifications (continued)

At recommended operating conditions with OV<sub>DD</sub> of 3.3 V ± 5%. All values refer to V<sub>IH</sub> (min) and V<sub>IL</sub> (max) levels (see Table 2).

| Parameter                         | Symbol <sup>1</sup> | Min | Max | Unit |

|-----------------------------------|---------------------|-----|-----|------|

| Capacitive load for each bus line | Cb                  | _   | 400 | pF   |

#### Notes:

- 1.The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)</sub>(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>I2DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>I2SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the START condition (S) went invalid (X) relative to the t<sub>I2C</sub> clock reference (K) going to the low (L) state or hold time. Also, t<sub>I2PVKH</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the STOP condition (P) reaching the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time.