#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XFI

| Product Status                  | Obsolete                                                     |

|---------------------------------|--------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                 |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                               |

| Speed                           | 1.333GHz                                                     |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                        |

| RAM Controllers                 | DDR2, DDR3                                                   |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers |                                                              |

| Ethernet                        | 10/100/1000Mbps (4)                                          |

| SATA                            | -                                                            |

| USB                             |                                                              |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography, Random Number Generator                        |

| Package / Case                  | 1023-BFBGA, FCBGA                                            |

| Supplier Device Package         | 1023-FCBGA (33x33)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8572ecvtauld |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

the upper and lower words of the 64-bit GPRs as they are defined by the SPE APU.

- Embedded vector and scalar single-precision floating-point APUs. Provide an instruction set for single-precision (32-bit) floating-point instructions.

- Double-precision floating-point APU. Provides an instruction set for double-precision (64-bit) floating-point instructions that use the 64-bit GPRs.

- 36-bit real addressing

- Memory management unit (MMU). Especially designed for embedded applications. Supports 4-Kbyte to 4-Gbyte page sizes.

- Enhanced hardware and software debug support

- Performance monitor facility that is similar to, but separate from, the MPC8572E performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operation.

- 1 Mbyte L2 cache/SRAM

- Shared by both cores.

- Flexible configuration and individually configurable per core.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- Per-way allocation of cache region to a given processor.

- SRAM features include the following:

- 1, 2, 4, or 8 ways can be configured as SRAM.

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- e500 coherency module (ECM) manages core and intrasystem transactions

- Address translation and mapping unit (ATMU)

- Twelve local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

Overview

- Multiplexed 32-bit address and data bus operating at up to 150 MHz

- Eight chip selects support eight external slaves

- Up to 8-beat burst transfers

- The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller.

- Three protocol engines available on a per-chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- NAND Flash control machine (FCM)

- Parity support

- Default boot ROM chip select with configurable bus width (8, 16, or 32 bits)

- Four enhanced three-speed Ethernet controllers (eTSECs)

- Three-speed support (10/100/1000 Mbps)

- Four IEEE Std 802.3®, 802.3u, 802.3x, 802.3z, 802.3ac, 802.3ab-compatible controllers

- Support for various Ethernet physical interfaces:

- 1000 Mbps full-duplex IEEE 802.3 GMII, IEEE 802.3z TBI, RTBI, RGMII, and SGMII

- 10/100 Mbps full and half-duplex IEEE 802.3 MII, IEEE 802.3 RGMII, and RMII

- Flexible configuration for multiple PHY interface configurations

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (Q-in-Q) VLAN, 802.2, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Supported in all FIFO modes

- Quality of service support:

- Transmission from up to eight physical queues

- Reception to up to eight physical queues

- Full- and half-duplex Ethernet support (1000 Mbps supports only full duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE Std 802.1<sup>TM</sup> virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- Three PCI Express controllers

- PCI Express 1.0a compatible

- Supports x8, x4, x2, and x1 link widths (see following bullet for specific width configuration options)

- Auto-detection of number of connected lanes

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 256-byte maximum payload size

- Virtual channel 0 only

- Full 64-bit decode with 36-bit wide windows

- Pin multiplexing for the high-speed I/O interfaces supports one of the following configurations:

- Single x8/x4/x2/x1 PCI Express

- Dual x4/x2/x1 PCI Express

- Single x4/x2/x1 PCI Express and dual x2/x1 PCI Express

- Single 1x/4x Serial RapidIO and single x4/x2/x1 PCI Express

- Power management

- Supports power saving modes: doze, nap, and sleep

- Employs dynamic power management, that automatically minimizes power consumption of blocks when they are idle

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the eight counters

- Supports duration and quantity threshold counting

- Permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- IEEE Std 1149.1<sup>™</sup> compatible, JTAG boundary scan

- 1023 FC-PBGA package

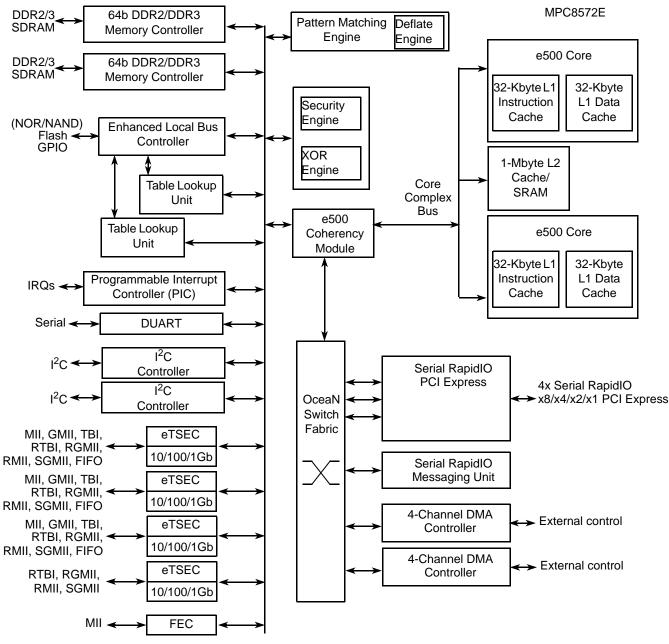

Figure 1 shows the MPC8572E block diagram.

# 2 **Electrical Characteristics**

This section provides the AC and DC electrical specifications for the MPC8572E. The MPC8572E is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 4 Input Clocks

# 4.1 System Clock Timing

Table 6 provides the system clock (SYSCLK) AC timing specifications for the MPC8572E.

#### Table 6. SYSCLK AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition       | Symbol                                | Min | Typical | Мах     | Unit | Notes   |

|---------------------------|---------------------------------------|-----|---------|---------|------|---------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 33  | —       | 133     | MHz  | 1       |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                   | 7.5 | —       | 30.3    | ns   | —       |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 1.2     | ns   | 2       |

| SYSCLK duty cycle         | t <sub>KHK</sub> /t <sub>SYSCLK</sub> | 40  | —       | 60      | %    | 3       |

| SYSCLK jitter             | —                                     | —   | —       | +/- 150 | ps   | 4, 5, 6 |

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies.Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on SYSCLK.

# 4.2 Real Time Clock Timing

The RTC input is sampled by the platform clock (CCB clock). The output of the sampling latch is then used as an input to the counters of the PIC and the TimeBase unit of the e500. There is no jitter specification. The minimum pulse width of the RTC signal should be greater than 2x the period of the CCB clock. That is, minimum clock high time is  $2 \times t_{CCB}$ , and minimum clock low time is  $2 \times t_{CCB}$ . There is no minimum RTC frequency; RTC may be grounded if not needed.

**RESET** Initialization

Table 8. DDRCLK AC Timing Specifications (continued)

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition | Symbol | Min | Typical | Max     | Unit | Notes   |

|---------------------|--------|-----|---------|---------|------|---------|

| DDRCLK jitter       | _      |     |         | +/- 150 | ps   | 4, 5, 6 |

Notes:

- 1. **Caution:** The DDR complex clock to DDRCLK ratio settings must be chosen such that the resulting DDR complex clock frequency does not exceed the maximum or minimum operating frequencies. Refer to Section 19.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

- 2. Rise and fall times for DDRCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The DDRCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track DDRCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on DDRCLK.

# 4.5 Platform to eTSEC FIFO Restrictions

Note the following eTSEC FIFO mode maximum speed restrictions based on platform (CCB) frequency.

For FIFO GMII modes (both 8 and 16 bit) and 16-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/4.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 127 MHz.

For 8-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/3.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz.

# 4.6 Other Input Clocks

For information on the input clocks of other functional blocks of the platform, such as SerDes and eTSEC, see the respective sections of this document.

# 5 **RESET** Initialization

Table 9 describes the AC electrical specifications for the RESET initialization timing.

#### **Table 9. RESET Initialization Timing Specifications**

| Parameter/Condition               |     | Мах | Unit    | Notes |

|-----------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET | 100 | —   | μs      | 2     |

| Minimum assertion time for SRESET | 3   | —   | SYSCLKs | 1     |

Table 14 provides the current draw characteristics for  $MV_{REF}n$ .

| Parameter / Condition                |            | Symbol               | Min | Max  | Unit | Note |

|--------------------------------------|------------|----------------------|-----|------|------|------|

| Current draw for MV <sub>REF</sub> n | DDR2 SDRAM | I <sub>MVREF</sub> n | —   | 1500 | μΑ   | 1    |

|                                      | DDR3 SDRAM |                      |     | 1250 |      |      |

Table 14. Current Draw Characteristics for MV<sub>REF</sub> n

1. The voltage regulator for MV<sub>RFF</sub>n must be able to supply up to 1500 μA or 1250 uA current for DDR2 or DDR3, respectively.

# 6.2 DDR2 and DDR3 SDRAM Interface AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM controller interface. The DDR controller supports both DDR2 and DDR3 memories. Note that although the minimum data rate for most off-the-shelf DDR3 DIMMs available is 800 MHz, JEDEC specification does allow the DDR3 to run at the data rate as low as 606 MHz. Unless otherwise specified, the AC timing specifications described in this section for DDR3 is applicable for data rate between 606 MHz and 800 MHz, as long as the DC and AC specifications of the DDR3 memory to be used are compliant to both JEDEC specifications as well as the specifications and requirements described in this MPC8572E hardware specifications document.

## 6.2.1 DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

Table 15, Table 16, and Table 17 provide the input AC timing specifications for the DDR controller when interfacing to DDR2 and DDR3 SDRAM.

# Table 15. DDR2 SDRAM Interface Input AC Timing Specifications for 1.8-V Interface At recommended operating conditions with $GV_{DD}$ of 1.8 V ± 5%

| Paramet               | Parameter  |                   | Min                | Мах                | Unit | Notes |

|-----------------------|------------|-------------------|--------------------|--------------------|------|-------|

| AC input low voltage  | >=667 MHz  | V <sub>ILAC</sub> | —                  | $MV_{REF}n - 0.20$ | V    | _     |

|                       | <= 533 MHz |                   | —                  | $MV_{REF}n - 0.25$ |      |       |

| AC input high voltage | >=667 MHz  | V <sub>IHAC</sub> | $MV_{REF}n + 0.20$ | —                  | V    | —     |

| _                     | <= 533 MHz |                   | $MV_{REF}n + 0.25$ | _                  |      |       |

#### Table 16. DDR3 SDRAM Interface Input AC Timing Specifications for 1.5-V Interface

At recommended operating conditions with GV<sub>DD</sub> of 1.5 V ± 5%. DDR3 data rate is between 606 MHz and 800 MHz.

| Parameter             | Symbol            | Min                 | Мах                                | Unit | Notes |

|-----------------------|-------------------|---------------------|------------------------------------|------|-------|

| AC input low voltage  | V <sub>ILAC</sub> | _                   | MV <sub>REF</sub> <i>n</i> – 0.175 | V    | —     |

| AC input high voltage | V <sub>IHAC</sub> | $MV_{REF}n + 0.175$ | —                                  | V    | —     |

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

### 8.3.3 SGMII Transmitter and Receiver DC Electrical Characteristics

Table 38 and Table 39 describe the SGMII SerDes transmitter and receiver AC-Coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs (SD2\_TX[n] and SD2\_TX[n]) as depicted in Figure 23.

| Parameter                                      | Symbol            | Min                                                                      | Тур | Max                                                                      | Unit | Notes                       |

|------------------------------------------------|-------------------|--------------------------------------------------------------------------|-----|--------------------------------------------------------------------------|------|-----------------------------|

| Supply Voltage                                 | $XV_{DD\_SRDS2}$  | 1.045                                                                    | 1.1 | 1.155                                                                    | V    | —                           |

| Output high voltage                            | VOH               | —                                                                        | _   | XV <sub>DD_SRDS2-Typ</sub> /2<br>+  V <sub>OD</sub>   <sub>-max</sub> /2 | mV   | 1                           |

| Output low voltage                             | VOL               | XV <sub>DD_SRDS2-Typ</sub> /2<br>-  V <sub>OD</sub>   <sub>-max</sub> /2 | _   | _                                                                        | mV   | 1                           |

| Output ringing                                 | V <sub>RING</sub> | —                                                                        | _   | 10                                                                       | %    | —                           |

|                                                |                   | 359                                                                      | 550 | 791                                                                      |      | Equalization setting: 1.0x  |

|                                                |                   | 329                                                                      | 505 | 725                                                                      |      | Equalization setting: 1.09x |

| Output differential voltage <sup>2, 3, 5</sup> | V <sub>OD</sub>   | 299                                                                      | 458 | 659                                                                      |      | Equalization setting: 1.2x  |

| Ouput unrerentiar voltage                      |                   | 270                                                                      | 414 | 594                                                                      | mV   | Equalization setting: 1.33x |

|                                                |                   | 239                                                                      | 367 | 527                                                                      |      | Equalization setting: 1.5x  |

|                                                |                   | 210                                                                      | 322 | 462                                                                      |      | Equalization setting: 1.71x |

|                                                |                   | 180                                                                      | 275 | 395                                                                      |      | Equalization setting: 2.0x  |

| Output offset voltage                          | V <sub>OS</sub>   | 473                                                                      | 550 | 628                                                                      | mV   | 1, 4                        |

| Output impedance (single-ended)                | R <sub>O</sub>    | 40                                                                       | _   | 60                                                                       | Ω    | —                           |

| Mismatch in a pair                             | $\Delta R_{O}$    | —                                                                        | _   | 10                                                                       | %    | —                           |

| Change in $V_{OD}$ between "0" and "1"         | $\Delta  V_{OD} $ | _                                                                        |     | 25                                                                       | mV   | —                           |

#### Table 38. SGMII DC Transmitter Electrical Characteristics

# NP

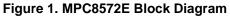

#### Local Bus Controller (eLBC)

Table 50. Local Bus General Timing Parameters ( $BV_{DD} = 2.5 V DC$ )—PLL Enabled (continued)At recommended operating conditions with  $BV_{DD}$  of 2.5 V ± 5% (continued)

| Parameter                                                          | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output valid (except LAD/LDP and LALE)          | t <sub>LBKHOV1</sub> | —   | 2.4 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                          | t <sub>LBKHOV2</sub> | —   | 2.5 | ns   | 3     |

| Local bus clock to address valid for LAD                           | t <sub>LBKHOV3</sub> | —   | 2.4 | ns   | 3     |

| Local bus clock to LALE assertion                                  | t <sub>LBKHOV4</sub> | —   | 2.4 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)         | t <sub>LBKHOX1</sub> | 0.8 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKHOX2</sub> | 0.8 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKHOZ1</sub> | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKHOZ2</sub> | —   | 2.6 | ns   | 5     |

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 2.5-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

Table 51 describes the general timing parameters of the local bus interface at  $BV_{DD} = 1.8 \text{ V DC}$

Table 51. Local Bus General Timing Parameters ( $BV_{DD} = 1.8 \text{ V DC}$ )—PLL Enabled At recommended operating conditions with  $BV_{DD}$  of 1.8 V ± 5%

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 6.67 | 12  | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43   | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                  | t <sub>LBKSKEW</sub>                | _    | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 2.4  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKH2</sub>                | 1.9  | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | 1.1  | —   | ns   | 3, 4  |

Local Bus Controller (eLBC)

Figure 35. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

JTAG

#### Table 53. JTAG AC Timing Specifications (Independent of SYSCLK) <sup>1</sup> (continued)

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 5%.

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min    | Max     | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|--------|---------|------|-------|

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 3<br>3 | 19<br>9 | ns   | 5, 6  |

Notes:

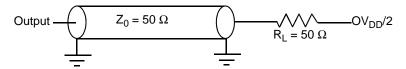

All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 36). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to  $t_{TCLK}$ .

- 6. Guaranteed by design.

Figure 36 provides the AC test load for TDO and the boundary-scan outputs.

Figure 36. AC Test Load for the JTAG Interface

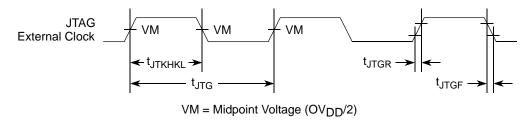

Figure 37 provides the JTAG clock input timing diagram.

Figure 37. JTAG Clock Input Timing Diagram

Figure 38 provides the  $\overline{\text{TRST}}$  timing diagram.

Table 58 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 1.8 \text{ V DC}$ . Table 58. GPIO DC Electrical Characteristics (1.8 V DC)

|                                                                   | · · ·            |                         |                         |      |  |  |  |  |

|-------------------------------------------------------------------|------------------|-------------------------|-------------------------|------|--|--|--|--|

| Parameter                                                         | Symbol           | Min                     | Мах                     | Unit |  |  |  |  |

| Supply voltage 1.8V                                               | BV <sub>DD</sub> | 1.71                    | 1.89                    | V    |  |  |  |  |

| High-level input voltage                                          | V <sub>IH</sub>  | 0.65 x BV <sub>DD</sub> | BV <sub>DD</sub> + 0.3  | V    |  |  |  |  |

| Low-level input voltage                                           | V <sub>IL</sub>  | -0.3                    | 0.35 x BV <sub>DD</sub> | V    |  |  |  |  |

| Input current $(BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD})$ | I <sub>IN</sub>  | TBD                     | TBD                     | μΑ   |  |  |  |  |

| High-level output voltage $(I_{OH} = -100 \ \mu A)$               | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2  | —                       | V    |  |  |  |  |

| High-level output voltage<br>(I <sub>OH</sub> = -2 mA)            | V <sub>OH</sub>  | BV <sub>DD</sub> - 0.45 | _                       | V    |  |  |  |  |

| Low-level output voltage $(I_{OL} = 100 \ \mu A)$                 | V <sub>OL</sub>  | _                       | 0.2                     | V    |  |  |  |  |

| Low-level output voltage<br>(I <sub>OL</sub> = 2 mA)              | V <sub>OL</sub>  | _                       | 0.45                    | V    |  |  |  |  |

#### Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

# 14.2 GPIO AC Electrical Specifications

Table 59 provides the GPIO input and output AC timing specifications.

#### Table 59. GPIO Input AC Timing Specifications<sup>1</sup>

| Parameter                       | Symbol             | Тур | Unit | Notes |

|---------------------------------|--------------------|-----|------|-------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub> | 20  | ns   | 2     |

Notes:

- 1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYSCLK. Timings are measured at the pin.

- 2. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

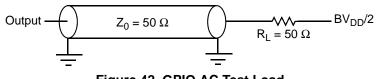

#### Figure 42 provides the AC test load for the GPIO.

Figure 42. GPIO AC Test Load

# 15.2.3 Interfacing With Other Differential Signaling Levels

- With on-chip termination to SGND\_SRDS*n* (xcorevss), the differential reference clocks inputs are HCSL (High-Speed Current Steering Logic) compatible DC-coupled.

- Many other low voltage differential type outputs like LVDS (Low Voltage Differential Signaling) can be used but may need to be AC-coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

- LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, additionally to AC-coupling.

#### NOTE

Figure 48 to Figure 51 below are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the MPC8572E SerDes reference clock receiver requirement provided in this document.

PCI Express

| Symbol                                       | Parameter                                                                                    | Min   | Nominal | Max | Units | Comments                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------|----------------------------------------------------------------------------------------------|-------|---------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>RX-EYE-MEDIAN-to-MAX</sub><br>-JITTER | Maximum time<br>between the jitter<br>median and<br>maximum<br>deviation from<br>the median. |       | _       | 0.3 | UI    | Jitter is defined as the measurement<br>variation of the crossing points ( $V_{RX-DIFFp-p}$<br>= 0 V) in relation to a recovered TX UI. A<br>recovered TX UI is calculated over 3500<br>consecutive unit intervals of sample data.<br>Jitter is measured using all edges of the<br>250 consecutive UI in the center of the<br>3500 UI used for calculating the TX UI. See<br>Notes 2, 3 and 7. |

| V <sub>RX-CM-ACp</sub>                       | AC Peak<br>Common Mode<br>Input Voltage                                                      | _     |         | 150 | mV    | $V_{RX-CM-ACp} =  V_{RXD+} + V_{RXD-} /2 - V_{RX-CM-DC} = DC_{(avg)} \text{ of }  V_{RX-D+} + V_{RX-D-} /2$<br>See Note 2                                                                                                                                                                                                                                                                      |

| RL <sub>RX-DIFF</sub>                        | Differential<br>Return Loss                                                                  | 15    |         | _   | dB    | Measured over 50 MHz to 1.25 GHz with<br>the D+ and D- lines biased at +300 mV and<br>-300 mV, respectively.<br>See Note 4                                                                                                                                                                                                                                                                     |

| RL <sub>RX-CM</sub>                          | Common Mode<br>Return Loss                                                                   | 6     | _       | _   | dB    | Measured over 50 MHz to 1.25 GHz with<br>the D+ and D- lines biased at 0 V. See Note<br>4                                                                                                                                                                                                                                                                                                      |

| Z <sub>RX-DIFF-DC</sub>                      | DC Differential<br>Input Impedance                                                           | 80    | 100     | 120 | Ω     | RX DC Differential mode impedance. See Note 5                                                                                                                                                                                                                                                                                                                                                  |

| Z <sub>RX-DC</sub>                           | DC Input<br>Impedance                                                                        | 40    | 50      | 60  | Ω     | Required RX D+ as well as D- DC<br>Impedance (50 $\pm$ 20% tolerance). See<br>Notes 2 and 5.                                                                                                                                                                                                                                                                                                   |

| Z <sub>RX-HIGH-IMP-DC</sub>                  | Powered Down<br>DC Input<br>Impedance                                                        | 200 k | _       | _   | Ω     | Required RX D+ as well as D- DC<br>Impedance when the Receiver terminations<br>do not have power. See Note 6.                                                                                                                                                                                                                                                                                  |

| V <sub>RX-IDLE</sub> -DET-DIFFp-p            | Electrical Idle<br>Detect Threshold                                                          | 65    | _       | 175 | mV    | $V_{RX-IDLE-DET-DIFF_{P}} = 2^*  V_{RX-D+} - V_{RX-D-} $<br>Measured at the package pins of the<br>Receiver                                                                                                                                                                                                                                                                                    |

| T <sub>RX-IDLE-DET-DIFF-</sub><br>ENTERTIME  | Unexpected<br>Electrical Idle<br>Enter Detect<br>Threshold<br>Integration Time               |       |         | 10  | ms    | An unexpected Electrical Idle ( $V_{RX-DIFFp-p} < V_{RX-IDLE-DET-DIFFp-p}$ ) must be recognized<br>no longer than $T_{RX-IDLE-DET-DIFF-ENTERING}$ to signal an unexpected idle condition.                                                                                                                                                                                                      |

#### Table 63. Differential Receiver (RX) Input Specifications (continued)

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

| Unaracteristic              | Gymbol              | Min   | Мах  | Onic   | notes                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | _                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | _                                                                                |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | _                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 400   | 400  | ps     | +/- 100 ppm                                                                      |

#### Table 69. Long Run Transmitter AC Timing Specifications—2.5 GBaud

#### Table 70. Long Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | R     | ange | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit   | Notes                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | —                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                                |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | -     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 320   | 320  | ps     | +/- 100 ppm                                                                      |

For each baud rate at which an LP-Serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the transmitter output compliance mask shown in Figure 58 with the parameters specified in Figure 71 when measured at the output pins of the device and the device is driving a 100  $\Omega$  +/-5% differential resistive load. The output eye pattern of an LP-Serial transmitter that implements pre-emphasis (to equalize the link and reduce inter-symbol interference) need only comply with the Transmitter Output Compliance Mask when pre-emphasis is disabled or minimized.

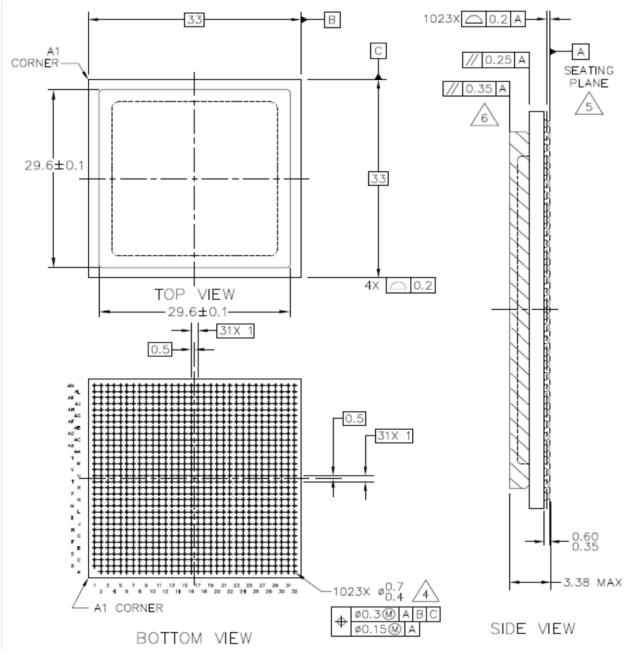

## 18.2 Mechanical Dimensions of the MPC8572E FC-PBGA

Figure 61 shows the mechanical dimensions of the MPC8572E FC-PBGA package with full lid.

Figure 61. Mechanical Dimensions of the MPC8572E FC-PBGA with Full Lid

#### NOTES:

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

- 4. Maximum solder ball diameter measured parallel to datum A.

Clocking

# 19 Clocking

This section describes the PLL configuration of the MPC8572E. Note that the platform clock is identical to the core complex bus (CCB) clock.

# 19.1 Clock Ranges

Table 77 provides the clocking specifications for both processor cores.

|                               | Maximum Processor Core Frequency |      |          |      |          |      |          |      |      |       |

|-------------------------------|----------------------------------|------|----------|------|----------|------|----------|------|------|-------|

| Characteristic                | 1067 MHz                         |      | 1200 MHz |      | 1333 MHz |      | 1500 MHz |      | Unit | Notes |

|                               | Min                              | Max  | Min      | Max  | Min      | Max  | Min      | Max  |      |       |

| e500 core processor frequency | 800                              | 1067 | 800      | 1200 | 800      | 1333 | 800      | 1500 | MHz  | 1, 2  |

| CCB frequency                 | 400                              | 533  | 400      | 533  | 400      | 533  | 400      | 600  | MHz  |       |

| DDR Data Rate                 | 400                              | 667  | 400      | 667  | 400      | 667  | 400      | 800  | MHz  |       |

#### Table 77. MPC8572E Processor Core Clocking Specifications

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," Section 19.3, "e500 Core PLL Ratio," and Section 19.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

2. The processor core frequency speed bins listed also reflect the maximum platform (CCB) and DDR data rate frequency supported by production test. Running CCB and/or DDR data rate higher than the limit shown above, although logically possible via valid clock ratio setting in some condition, is not supported.

The DDR memory controller can run in either synchronous or asynchronous mode. When running in synchronous mode, the memory bus is clocked relative to the platform clock frequency. When running in asynchronous mode, the memory bus is clocked with its own dedicated PLL with clock provided on DDRCLK input pin. Table 78 provides the clocking specifications for the memory bus.

Clocking

| Binary Value of LA[29:31] Signals | CCB:SYSCLK Ratio |

|-----------------------------------|------------------|

| 000                               | 4:1              |

| 001                               | 5:1              |

| 010                               | 6:1              |

| 011                               | 8:1              |

| 100                               | 10:1             |

| 101                               | 12:1             |

| 110                               | Reserved         |

| 111                               | Reserved         |

#### Table 79. CCB Clock Ratio

# 19.3 e500 Core PLL Ratio

The clock speed for each e500 core can be configured differently, determined by the values of various signals at power up.

Table 80 describes the clock ratio between e500 Core0 and the e500 core complex bus (CCB). This ratio is determined by the binary value of LBCTL, LALE and LGPL2/LOE/LFRE at power up, as shown in Table 80.

| Binary Value of<br>LBCT <u>L, LALE,</u><br>LGPL2/LOE/LFRE<br>Signals | e500 Core0:CCB Clock Ratio | Binary Value of<br>LBCT <u>L, LALE,</u><br>LGPL2/LOE/LFRE<br>Signals | e500 Core0:CCB Clock Ratio |

|----------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------|----------------------------|

| 000                                                                  | Reserved                   | 100                                                                  | 2:1                        |

| 001                                                                  | Reserved                   | 101                                                                  | 5:2 (2.5:1)                |

| 010                                                                  | Reserved                   | 110                                                                  | 3:1                        |

| 011                                                                  | 3:2 (1.5:1)                | 111                                                                  | 7:2 (3.5:1)                |

#### Table 80. e500 Core0 to CCB Clock Ratio

| Binary Value of<br>TSEC_1588_CLK_OUT,<br>TSEC_1588_PULSE_OUT1,<br>TSEC_1588_PULSE_OUT2 Signals | DDR:DDRCLK Ratio |  |  |  |

|------------------------------------------------------------------------------------------------|------------------|--|--|--|

| 101                                                                                            | 12:1             |  |  |  |

| 110                                                                                            | 14:1             |  |  |  |

| 111                                                                                            | Synchronous mode |  |  |  |

Table 82. DDR Clock Ratio (continued)

# **19.5 Frequency Options**

## **19.5.1** Platform to Sysclk Frequency Options

Table 83 shows the expected frequency values for the platform frequency when using the specified CCB clock to SYSCLK ratio.

| CCB to<br>SYSCLK Ratio |       | SYSCLK (MHz)                  |     |       |     |     |     |        |  |  |

|------------------------|-------|-------------------------------|-----|-------|-----|-----|-----|--------|--|--|

|                        | 33.33 | 41.66                         | 50  | 66.66 | 83  | 100 | 111 | 133.33 |  |  |

|                        |       | Platform /CCB Frequency (MHz) |     |       |     |     |     |        |  |  |

| 4                      |       |                               |     |       |     | 400 | 444 | 533    |  |  |

| 5                      |       |                               |     |       | 415 | 500 | 555 |        |  |  |

| 6                      |       |                               |     | 400   | 498 | 600 |     |        |  |  |

| 8                      |       |                               | 400 | 533   |     |     | -   |        |  |  |

| 10                     |       | 417                           | 500 |       | -   |     |     |        |  |  |

| 12                     | 400   | 500                           | 600 | ]     |     |     |     |        |  |  |

Table 83. Frequency Options for Platform Frequency

## 19.5.2 Minimum Platform Frequency Requirements for High-Speed Interfaces

Section 4.4.3.6, "I/O Port Selection," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* describes various high-speed interface configuration options. Note that the CCB clock frequency must be considered for proper operation of such interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than or equal to:

See Section 21.1.3.2, "Link Width," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* for PCI Express interface width details. Note that the "PCI Express link width"

**Ordering Information**

| MPC                          | nnnn               | е                                       | t                                      | Ι                              | рр                                                     | ffm                                                                                                                                                                                                                                  | r                                                                                                                     |

|------------------------------|--------------------|-----------------------------------------|----------------------------------------|--------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Product<br>Code <sup>1</sup> | Part<br>Identifier | Security<br>Engine                      | Temperature                            | Power                          | Package<br>Sphere Type <sup>2</sup>                    | Processor Frequency/<br>DDR Data Rate <sup>3</sup>                                                                                                                                                                                   | Silicon<br>Revision                                                                                                   |

| MPC<br>PPC                   | 8572               | E = Included<br>Blank = Not<br>included | Blank = 0 to 105°C<br>C = −40 to 105°C | Blank =<br>Standard<br>L = Low | PX =<br>Leaded,<br>FC-PBGA<br>VT = Pb-free,<br>FC-PBGA | AVN =<br>150- MHz processor;<br>800 MT/s DDR data rate<br>AUL =<br>1333-MHz processor;<br>667 MT/s DDR data rate<br>ATL =<br>1200-MHz processor;<br>667 MT/s DDR data rate<br>ARL =<br>1067-MHz processor;<br>667 MT/s DDR data rate | D= Ver. 2.1<br>(SVR =<br>0x80E8_0021)<br>SEC included<br>D= Ver. 2.1<br>(SVR =<br>0x80E0_0021)<br>SEC not<br>included |

#### Table 87. Part Numbering Nomenclature—Rev 2.1

#### Notes:

<sup>1</sup> MPC stands for "Qualified."

PPC stands for "Prototype"

<sup>2</sup> See Section 18, "Package Description," for more information on the available package types.

<sup>3</sup> Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

#### Table 88. Part Numbering Nomenclature—Rev 1.1.1

| MPC                          | nnnn               | е                                       | t                                   | рр                                  | ffm                                                                                                                                                                                                                                  | r                                                                                                                        |

|------------------------------|--------------------|-----------------------------------------|-------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Product<br>Code <sup>1</sup> | Part<br>Identifier | Security Engine                         | Temperature                         | Package Sphere<br>Type <sup>2</sup> | Processor Frequency/<br>DDR Data Rate <sup>3</sup>                                                                                                                                                                                   | Silicon<br>Revision                                                                                                      |

| MPC<br>PPC                   | 8572               | E = Included<br>Blank = Not<br>included | Blank=0 to 105°C<br>C= −40 to 105°C | ,                                   | AVN =<br>1500-MHz processor;<br>800 MT/s DDR data rate<br>AUL =<br>1333-MHz process or;<br>667 MT/s DDR datarate<br>ATL =<br>1200-MHz processor;<br>667 MT/s DDR data rate<br>ARL =<br>1067-MHz processor;<br>667 MT/s DDR data rate | B = Ver. 1.1.1<br>(SVR =<br>0x80E8_0011)<br>SEC included<br>B = Ver. 1.1.1<br>(SVR =<br>0x80E0_0011)<br>SEC not included |

#### Notes:

<sup>1</sup> MPC stands for "Qualified."

PPC stands for "Prototype"

<sup>2</sup> See Section 18, "Package Description," for more information on the available package types.