#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.333GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                   |

| RAM Controllers                 | DDR2, DDR3                                                              |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers |                                                                         |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             |                                                                         |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                  |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                   |

| Package / Case                  | 1023-BFBGA, FCBGA                                                       |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572ecvtaule |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- CRC generation and verification of inbound/outbound frames

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- Two MII management interfaces for control and status

- Ability to force allocation of header information and buffer descriptors into L2 cache

- 10/100 Fast Ethernet controller (FEC) management interface

- 10/100 Mbps full and half-duplex IEEE 802.3 MII for system management

- Note: When enabled, the FEC occupies eTSEC3 and eTSEC4 parallel interface signals. In such a mode, eTSEC3 and eTSEC4 are only available through SGMII interfaces.

- OCeaN switch fabric

- Full crossbar packet switch

- Reorders packets from a source based on priorities

- Reorders packets to bypass blocked packets

- Implements starvation avoidance algorithms

- Supports packets with payloads of up to 256 bytes

- Two integrated DMA controllers

- Four DMA channels per controller

- All channels accessible by the local masters

- Extended DMA functions (advanced chaining and striding capability)

- Misaligned transfer capability

- Interrupt on completed segment, link, list, and error

- Supports transfers to or from any local memory or I/O port

- Selectable hardware-enforced coherency (snoop/no snoop)

- Ability to start and flow control up to 4 (both Channel 0 and 1 for each DMA Controller) of the 8 total DMA channels from external 3-pin interface by the remote masters

- The Channel 2 of DMA Controller 2 is only allowed to initiate and start a DMA transfer by the remote master, because only one of the 3-external pins (DMA2\_DREQ[2]) is made available

| PLL config input setup time with stable SYSCLK before HRESET negation                                           | 100 |   | μs      | — |

|-----------------------------------------------------------------------------------------------------------------|-----|---|---------|---|

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET                     | 4   | _ | SYSCLKs | 1 |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET                   | 2   | _ | SYSCLKs | 1 |

| Maximum valid-to-high imp <u>edance time</u> for actively driven POR configs with respect to negation of HRESET | _   | 5 | SYSCLKs | 1 |

Table 9. RESET Initialization Timing Specifications (continued)

#### Notes:

2. Reset assertion timing requirements for DDR3 DRAMs may differ.

#### Table 10 provides the PLL lock times.

| Table | 10. | PLL | Lock | Times |

|-------|-----|-----|------|-------|

|-------|-----|-----|------|-------|

| Parameter/Condition | Symbol | Min | Typical | Max |

|---------------------|--------|-----|---------|-----|

| PLL lock times      | —      | 100 | μs      | _   |

| Local bus PLL       | —      | 50  | μs      |     |

# 6 DDR2 and DDR3 SDRAM Controller

This section describes the DC and AC electrical specifications for the DDR2 and DDR3 SDRAM controller interface of the MPC8572E. Note that the required  $GV_{DD}(typ)$  voltage is 1.8Vor 1.5 V when interfacing to DDR2 or DDR3 SDRAM, respectively.

## 6.1 DDR2 and DDR3 SDRAM Interface DC Electrical Characteristics

Table 11 provides the recommended operating conditions for the DDR SDRAM controller of the MPC8572E when interfacing to DDR2 SDRAM.

| Parameter/Condition                              | Symbol              | Min                  | Мах                         | Unit | Notes |

|--------------------------------------------------|---------------------|----------------------|-----------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>    | 1.71                 | 1.89                        | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> n | $0.49 	imes GV_{DD}$ | $0.51 	imes GV_{DD}$        | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>     | $MV_{REF}n - 0.04$   | $MV_{REF}n + 0.04$          | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>     | $MV_{REF}n + 0.125$  | GV <sub>DD</sub> + 0.3      | V    | _     |

| Input low voltage                                | V <sub>IL</sub>     | -0.3                 | MV <sub>REF</sub> n - 0.125 | V    | _     |

| Output leakage current                           | I <sub>OZ</sub>     | -50                  | 50                          | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>     | -13.4                | _                           | mA   | —     |

| Table 11 | DDR2 SDRAM | Interface DC | Electrical | Characteristics | for GV(tvn) | 1 = 18V |

|----------|------------|--------------|------------|-----------------|-------------|---------|

|          |            | menace DO    | Liccultur  | onaracteristics |             | / I.O V |

<sup>1.</sup> SYSCLK is the primary clock input for the MPC8572E.

Table 14 provides the current draw characteristics for  $MV_{REF}n$ .

| Parameter / Condition                |            | Symbol               | Min | Max  | Unit | Note |

|--------------------------------------|------------|----------------------|-----|------|------|------|

| Current draw for MV <sub>REF</sub> n | DDR2 SDRAM | I <sub>MVREF</sub> n | —   | 1500 | μΑ   | 1    |

|                                      | DDR3 SDRAM |                      |     | 1250 |      |      |

Table 14. Current Draw Characteristics for MV<sub>REF</sub> n

1. The voltage regulator for MV<sub>RFF</sub>n must be able to supply up to 1500 μA or 1250 uA current for DDR2 or DDR3, respectively.

## 6.2 DDR2 and DDR3 SDRAM Interface AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM controller interface. The DDR controller supports both DDR2 and DDR3 memories. Note that although the minimum data rate for most off-the-shelf DDR3 DIMMs available is 800 MHz, JEDEC specification does allow the DDR3 to run at the data rate as low as 606 MHz. Unless otherwise specified, the AC timing specifications described in this section for DDR3 is applicable for data rate between 606 MHz and 800 MHz, as long as the DC and AC specifications of the DDR3 memory to be used are compliant to both JEDEC specifications as well as the specifications and requirements described in this MPC8572E hardware specifications document.

## 6.2.1 DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

Table 15, Table 16, and Table 17 provide the input AC timing specifications for the DDR controller when interfacing to DDR2 and DDR3 SDRAM.

# Table 15. DDR2 SDRAM Interface Input AC Timing Specifications for 1.8-V Interface At recommended operating conditions with $GV_{DD}$ of 1.8 V ± 5%

| Parameter             |            | Symbol            | Min                | Мах                | Unit | Notes |

|-----------------------|------------|-------------------|--------------------|--------------------|------|-------|

| AC input low voltage  | >=667 MHz  | V <sub>ILAC</sub> | —                  | $MV_{REF}n - 0.20$ | V    | _     |

|                       | <= 533 MHz |                   | —                  | $MV_{REF}n - 0.25$ |      |       |

| AC input high voltage | >=667 MHz  | V <sub>IHAC</sub> | $MV_{REF}n + 0.20$ | —                  | V    | —     |

| _                     | <= 533 MHz |                   | $MV_{REF}n + 0.25$ | _                  |      |       |

#### Table 16. DDR3 SDRAM Interface Input AC Timing Specifications for 1.5-V Interface

At recommended operating conditions with GV<sub>DD</sub> of 1.5 V ± 5%. DDR3 data rate is between 606 MHz and 800 MHz.

| Parameter             | Symbol            | Min                 | Мах                                | Unit | Notes |

|-----------------------|-------------------|---------------------|------------------------------------|------|-------|

| AC input low voltage  | V <sub>ILAC</sub> | _                   | MV <sub>REF</sub> <i>n</i> – 0.175 | V    | —     |

| AC input high voltage | V <sub>IHAC</sub> | $MV_{REF}n + 0.175$ | —                                  | V    | —     |

#### DDR2 and DDR3 SDRAM Controller

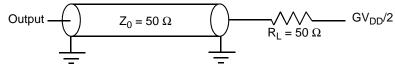

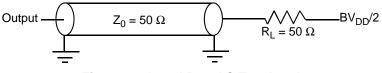

Figure 6 provides the AC test load for the DDR2 and DDR3 Controller bus.

Figure 6. DDR2 and DDR3 Controller bus AC Test Load

## 6.2.3 DDR2 and DDR3 SDRAM Differential Timing Specifications

This section describes the DC and AC differential electrical specifications for the DDR2 and DDR3 SDRAM controller interface of the MPC8572E.

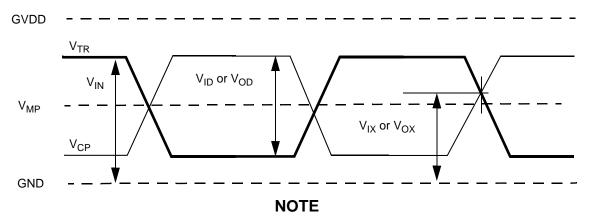

VID specifies the input differential voltage |VTR - VCP| required for switching, where VTR is the true input signal (such as MCK or MDQS) and VCP is the complementary input signal (such as MCK or MDQS).

Table 19 provides the differential specifications for the MPC8572E differential signals MDQS/ $\overline{MDQS}$  and MCK/ $\overline{MCK}$  when in DDR2 mode.

| Parameter/Condition                 | Symbol            | Min        | Мах                           | Unit | Notes |

|-------------------------------------|-------------------|------------|-------------------------------|------|-------|

| DC Input Signal Voltage             | V <sub>IN</sub>   | -0.3       | GV <sub>DD</sub> + 0.3        | V    | —     |

| DC Differential Input Voltage       | V <sub>ID</sub>   |            | —                             | mV   | —     |

| AC Differential Input Voltage       | V <sub>IDAC</sub> |            | —                             | mV   | —     |

| DC Differential Output Voltage      | V <sub>OH</sub>   | _          | _                             | mV   | —     |

| AC Differential Output Voltage      | V <sub>OHAC</sub> | JEDEC: 0.5 | JEDEC: GV <sub>DD</sub> + 0.6 | V    | —     |

| AC Differential Cross-point Voltage | V <sub>IXAC</sub> | _          | _                             | mV   | —     |

| Input Midpoint Voltage              | V <sub>MP</sub>   | _          | —                             | mV   | —     |

Table 19. DDR2 SDRAM Differential Electrical Characteristics

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

# 7.2 DUART AC Electrical Specifications

Table 22 provides the AC timing parameters for the DUART interface.

#### Table 22. DUART AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter         | Value                       | Unit | Notes   |

|-------------------|-----------------------------|------|---------|

| Minimum baud rate | f <sub>CCB</sub> /1,048,576 | baud | 1, 2    |

| Maximum baud rate | f <sub>CCB</sub> /16        | baud | 1, 2, 3 |

| Oversample rate   | 16                          | _    | 1, 4    |

#### Notes:

1. Guaranteed by design

- 2. f<sub>CCB</sub> refers to the internal platform clock frequency.

- 3. Actual attainable baud rate is limited by the latency of interrupt processing.

- 4. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

# 8 Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

This section provides the AC and DC electrical characteristics for the enhanced three-speed Ethernet controller.

## 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics

The electrical characteristics specified here apply to all FIFO mode, gigabit media independent interface (GMII), media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), and reduced media independent interface (RMII) signals except management data input/output (MDIO) and management data clock (MDC), and serial gigabit media independent interface (SGMII). The RGMII, RTBI and FIFO mode interfaces are defined for 2.5 V, while the GMII, MII, RMII, and TBI interfaces can operate at both 2.5 V and 3.3V.

The GMII, MII, or TBI interface timing is compliant with IEEE 802.3. The RGMII and RTBI interfaces follow the Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3 (12/10/2000). The RMII interface follows the RMII Consortium RMII Specification Version 1.2 (3/20/1998).

The electrical characteristics for MDIO and MDC are specified in Section 9, "Ethernet Management Interface Electrical Characteristics."

The electrical characteristics for SGMII is specified in Section 8.3, "SGMII Interface Electrical Characteristics." The SGMII interface conforms (with exceptions) to the Serial-GMII Specification Version 1.8.

| Table 24, MIL GMIL | RMIL RGI | /III. TBI. RTB                          | I, and FIFO DC Electrica | Characteristics | (continued) |

|--------------------|----------|-----------------------------------------|--------------------------|-----------------|-------------|

|                    | ,,       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                          |                 | ooninaca)   |

| Parameters                                                | Symbol          | Min | Мах | Unit | Notes  |

|-----------------------------------------------------------|-----------------|-----|-----|------|--------|

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$ | IIH             | _   | 10  | μA   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)              | Ι <sub>ΙL</sub> | -15 | _   | μΑ   | 3      |

Note:

<sup>1</sup>  $LV_{DD}$  supports eTSECs 1 and 2.

$^{2}$  TV<sub>DD</sub> supports eTSECs 3 and 4 or FEC.

$^3$  Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII and RTBI are presented in this section.

## 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, because they have similar performance and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back on the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source-synchronous timing reference. Typically, the clock edge that launched the data can be used, because the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is a relationship between the maximum FIFO speed and the platform (CCB) frequency. For more information see Section 4.5, "Platform to eTSEC FIFO Restrictions."

Table 25 and Table 26 summarize the FIFO AC specifications.

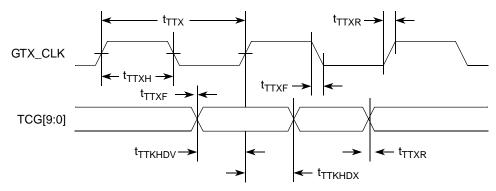

#### Table 25. FIFO Mode Transmit AC Timing Specification

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 2.5V ± 5%

| Parameter/Condition                       | Symbol                              | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK, GTX_CLK clock period <sup>1</sup> | t <sub>FIT</sub>                    | 5.3 | 8.0 | 100 | ns   |

| TX_CLK, GTX_CLK duty cycle                | t <sub>FITH</sub> /t <sub>FIT</sub> | 45  | 50  | 55  | %    |

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

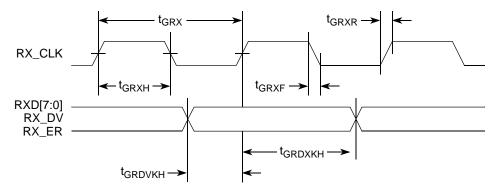

Figure 11 shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

## 8.2.3 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

## 8.2.3.1 MII Transmit AC Timing Specifications

Table 29 provides the MII transmit AC timing specifications.

#### Table 29. MII Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> <sup>2</sup>       | —   | 400 | _   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                    | —   | 40  | _   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                 | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise (20%-80%)                | t <sub>MTXR</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

| TX_CLK data clock fall (80%-20%)                | t <sub>MTXF</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

Figure 15 shows the TBI transmit AC timing diagram.

Figure 15. TBI Transmit AC Timing Diagram

## 8.2.4.2 TBI Receive AC Timing Specifications

Table 32 provides the TBI receive AC timing specifications.

#### Table 32. TBI Receive AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition <sup>3</sup>                             | Symbol <sup>1</sup>                 | Min | Тур  | Мах | Unit |

|--------------------------------------------------------------|-------------------------------------|-----|------|-----|------|

| Clock period for TBI Receive Clock 0, 1                      | t <sub>TRX</sub>                    | _   | 16.0 | —   | ns   |

| Skew for TBI Receive Clock 0, 1                              | t <sub>SKTRX</sub>                  | 7.5 | —    | 8.5 | ns   |

| Duty cycle for TBI Receive Clock 0, 1                        | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  | —    | 60  | %    |

| RCG[9:0] setup time to rising edge of TBI Receive Clock 0, 1 | t <sub>TRDVKH</sub>                 | 2.5 | —    | —   | ns   |

| RCG[9:0] hold time to rising edge of TBI Receive Clock 0, 1  | t <sub>TRDXKH</sub>                 | 1.5 | —    | —   | ns   |

| Clock rise time (20%-80%) for TBI Receive Clock 0, 1         | t <sub>TRXR</sub> <sup>2</sup>      | 0.7 | —    | 2.4 | ns   |

| Clock fall time (80%-20%) for TBI Receive Clock 0, 1         | t <sub>TRXF</sub> <sup>2</sup>      | 0.7 | —    | 2.4 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).</sub>

2. Guaranteed by design.

3. The signals "TBI Receive Clock 0" and "TBI Receive Clock 1" refer to TSECn\_RX\_CLK and TSECn\_TX\_CLK pins respectively. These two clock signals are also referred as PMA\_RX\_CLK[0:1].

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

Table 39 lists the SGMII DC receiver electrical characteristics.

| Parameter                        |           | Symbol                  | Min   | Тур                   | Max   | Unit | Notes |

|----------------------------------|-----------|-------------------------|-------|-----------------------|-------|------|-------|

| Supply Voltage                   |           | XV <sub>DD_SRDS2</sub>  | 1.045 | 1.1                   | 1.155 | V    |       |

| DC Input voltage range           |           | —                       |       | N/A                   |       | _    | 1     |

| Input differential voltage       | LSTS = 0  | V <sub>RX_DIFFp-p</sub> | 100   | —                     | 1200  | mV   | 2, 4  |

|                                  | LSTS = 1  |                         | 175   | —                     |       |      |       |

| Loss of signal threshold         | LSTS = 0  | VLOS                    | 30    | —                     | 100   | mV   | 3, 4  |

|                                  | LSTS = 1  |                         | 65    | —                     | 175   |      |       |

| Input AC common mode v           | voltage   | V <sub>CM_ACp-p</sub>   |       | —                     | 100   | mV   | 5     |

| Receiver differential input      | impedance | Z <sub>RX_DIFF</sub>    | 80    | 100                   | 120   | Ω    |       |

| Receiver common mode i impedance | nput      | Z <sub>RX_CM</sub>      | 20    | —                     | 35    | Ω    | _     |

| Common mode input volta          | age       | V <sub>CM</sub>         | —     | V <sub>xcorevss</sub> |       | V    | 6     |

Table 39. SGMII DC Receiver Electrical Characteristics

#### Note:

1. Input must be externally AC-coupled.

2. V<sub>RX DIFFp-p</sub> is also referred to as peak to peak input differential voltage

3. The concept of this parameter is equivalent to the Electrical Idle Detect Threshold parameter in PCI Express. Refer to PCI Express Differential Receiver (RX) Input Specifications section for further explanation.

4. The LSTS shown in the table refers to the LSTSAB or LSTSEF bit field of MPC8572E's SerDes 2 Control Register.

5.  $V_{\mbox{CM}\_\mbox{ACp-p}}$  is also referred to as peak to peak AC common mode voltage.

6. On-chip termination to SGND\_SRDS2 (xcorevss).

## 8.3.4 SGMII AC Timing Specifications

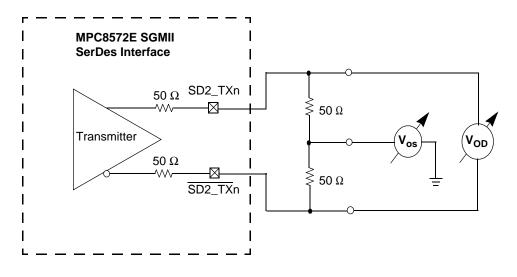

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs ( $SD2_TX[n]$  and  $\overline{SD2_TX[n]}$ ) or at the receiver inputs ( $SD2_RX[n]$  and  $\overline{SD2_RX[n]}$ ) as depicted in Figure 25, respectively.

## 8.3.4.1 SGMII Transmit AC Timing Specifications

Table 40 provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### Table 40. SGMII Transmit AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2}$  = 1.1V ± 5%.

| Parameter                           | Symbol            | Min    | Тур | Max    | Unit   | Notes |

|-------------------------------------|-------------------|--------|-----|--------|--------|-------|

| Deterministic Jitter                | JD                | —      | _   | 0.17   | UI p-p | _     |

| Total Jitter                        | JT                | —      | _   | 0.35   | UI p-p | _     |

| Unit Interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1     |

| V <sub>OD</sub> fall time (80%-20%) | tfall             | 50     | _   | 120    | ps     | _     |

| V <sub>OD</sub> rise time (20%-80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     | _     |

Notes:

1. Each UI is 800 ps  $\pm$  100 ppm.

## 8.3.4.2 SGMII Receive AC Timing Specifications

Table 41 provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 24 shows the SGMII receiver input compliance mask eye diagram.

#### Table 41. SGMII Receive AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2} = 1.1V \pm 5\%$ .

| Parameter                                          | Symbol          | Min    | Тур | Max               | Unit   | Notes |

|----------------------------------------------------|-----------------|--------|-----|-------------------|--------|-------|

| Deterministic Jitter Tolerance                     | JD              | 0.37   | —   | —                 | UI p-p | 1     |

| Combined Deterministic and Random Jitter Tolerance | JDR             | 0.55   | —   | _                 | UI p-p | 1     |

| Sinusoidal Jitter Tolerance                        | JSIN            | 0.1    | —   | —                 | UI p-p | 1     |

| Total Jitter Tolerance                             | JT              | 0.65   |     | _                 | UI p-p | 1     |

| Bit Error Ratio                                    | BER             | _      | —   | 10 <sup>-12</sup> |        | _     |

| Unit Interval                                      | UI              | 799.92 | 800 | 800.08            | ps     | 2     |

| AC Coupling Capacitor                              | C <sub>TX</sub> | 5      | —   | 200               | nF     | 3     |

Notes:

1. Measured at receiver.

2. Each UI is 800 ps  $\pm$  100 ppm.

3. The external AC coupling capacitor is required. It is recommended to be placed near the device transmitter outputs.

4. See RapidIO 1x/4x LP Serial Physical Layer Specification for interpretation of jitter specifications.

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 42. eTSEC IEEE 1588 AC Timing Specifications (continued)

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%

| Parameter/Condition           | Symbol                                                  | Min                         | Тур | Мах | Unit | Note |

|-------------------------------|---------------------------------------------------------|-----------------------------|-----|-----|------|------|

| TSEC_1588_CLK_OUT duty cycle  | t <sub>T1588</sub> CLKOTH<br>/t <sub>T1588</sub> CLKOUT | 30                          | 50  | 70  | %    | —    |

| TSEC_1588_PULSE_OUT           | t <sub>T1588OV</sub>                                    | 0.5                         | _   | 3.0 | ns   | —    |

| TSEC_1588_TRIG_IN pulse width | t <sub>T1588</sub> trigh                                | 2*t <sub>T1588CLK_MAX</sub> | _   | —   | ns   | 2    |

#### Note:

1.When TMR\_CTRL[CKSEL] is set as '00', the external TSEC\_1588\_CLK input is selected as the 1588 timer reference clock source, with the timing defined in Table 42, "eTSEC IEEE 1588 AC Timing Specifications." The maximum value of t<sub>T1588CLK</sub> is defined in terms of T<sub>TX\_CLK</sub>, that is the maximum clock cycle period of the equivalent interface speed that the eTSEC1 port is running at. When eTSEC1 is configured to operate in the parallel mode, the T<sub>TX\_CLK</sub> is the maximum clock period of the TSEC1\_TX\_CLK. When eTSEC1 operates in SGMII mode, the maximum value of t<sub>T1588CLK</sub> is defined in terms of the recovered clock from SGMII SerDes. For example, for SGMII 10/100/1000 Mbps modes, the maximum value of t<sub>T1588CLK</sub> is 3600, 360, 72 ns respectively. See the *MPC8572E PowerQUICC™ III Integrated Communications Processor Reference Manual* for detailed description of TMR\_CTRL registers.

2. It needs to be at least two times of the clock period of the clock selected by TMR\_CTRL[CKSEL].

# 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals ECn\_MDIO (management data input/output) and ECn\_MDC (management data clock). The electrical characteristics for GMII, SGMII, RGMII, RMII, TBI and RTBI are specified in "Section 8, "Ethernet: Enhanced Three-Speed Ethernet (eTSEC)."

## 9.1 MII Management DC Electrical Characteristics

The ECn\_MDC and ECn\_MDIO are defined to operate at a supply voltage of 3.3 V or 2.5 V. The DC electrical characteristics for ECn\_MDIO and ECn\_MDC are provided in Table 43 and Table 44.

| Parameter                                                                | Symbol            | Min  | Мах                    | Unit | Notes |

|--------------------------------------------------------------------------|-------------------|------|------------------------|------|-------|

| Supply voltage (3.3 V)                                                   | $LV_{DD}/TV_{DD}$ | 3.13 | 3.47                   | V    | 1, 2  |

| Output high voltage<br>( $LV_{DD}/TV_{DD} = Min, I_{OH} = -1.0 mA$ )     | V <sub>OH</sub>   | 2.10 | OV <sub>DD</sub> + 0.3 | V    | _     |

| Output low voltage $(LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA)$            | V <sub>OL</sub>   | GND  | 0.50                   | V    | _     |

| Input high voltage                                                       | V <sub>IH</sub>   | 2.0  | —                      | V    | _     |

| Input low voltage                                                        | V <sub>IL</sub>   | _    | 0.90                   | V    | _     |

| Input high current $(LV_{DD}/TV_{DD} = Max, V_{IN}^{3} = 2.1 \text{ V})$ | IIH               |      | 40                     | μA   | —     |

Table 43. MII Management DC Electrical Characteristics ( $LV_{DD}/TV_{DD}$ =3.3 V)

**Ethernet Management Interface Electrical Characteristics**

Table 43. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=3.3 V) (continued)

| Parameter                                                                             | Symbol          | Min  | Мах | Unit | Notes |

|---------------------------------------------------------------------------------------|-----------------|------|-----|------|-------|

| Input low current (LV <sub>DD</sub> /TV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V) | I <sub>IL</sub> | -600 | _   | μΑ   | _     |

Note:

1. EC1\_MDC and EC1\_MDIO operate on LV<sub>DD</sub>.

2. EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

3. Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  and  $TV_{IN}$  symbol referenced in Table 1.

#### Table 44. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=2.5 V)

| Parameters                                                         | Symbol                             | Min       | Мах                                      | Unit | Notes  |

|--------------------------------------------------------------------|------------------------------------|-----------|------------------------------------------|------|--------|

| Supply voltage 2.5 V                                               | LV <sub>DD/</sub> TV <sub>DD</sub> | 2.37      | 2.63                                     | V    | 1,2    |

| Output high voltage<br>( $LV_{DD}/TV_{DD} = Min, IOH = -1.0 mA$ )  | V <sub>OH</sub>                    | 2.00      | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _      |

| Output low voltage<br>( $LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA$ ) | V <sub>OL</sub>                    | GND – 0.3 | 0.40                                     | V    | _      |

| Input high voltage                                                 | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$                  | V    | _      |

| Input low voltage                                                  | V <sub>IL</sub>                    | -0.3      | 0.70                                     | V    | _      |

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$          | IIH                                | _         | 10                                       | μΑ   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                       | IIL                                | -15       | _                                        | μA   | 3      |

#### Note:

$^1\,$  EC1\_MDC and EC1\_MDIO operate on LV\_DD.

<sup>2</sup> EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

$^3\,$  Note that the symbol V\_{IN}, in this case, represents the LV\_{IN} and TV\_{IN} symbols referenced in Table 1.

## 9.2 MII Management AC Electrical Specifications

Table 45 provides the MII management AC timing specifications. There are three sets of Ethernet management signals (EC1\_MDC and EC1\_MDIO, EC3\_MDC and EC3\_MDIO, EC5\_MDC and EC5\_MDIO). These are not explicitly shown in the table or in the figure following.

#### Table 45. MII Management AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%.

| Parameter/Condition            | Symbol <sup>1</sup> | Min   | Тур | Мах                     | Unit | Notes |

|--------------------------------|---------------------|-------|-----|-------------------------|------|-------|

| ECn_MDC frequency              | f <sub>MDC</sub>    | 0.9   | 2.5 | 9.3                     | MHz  | 2, 3  |

| ECn_MDC period                 | t <sub>MDC</sub>    | 107.5 | _   | 1120                    | ns   | —     |

| ECn_MDC clock pulse width high | t <sub>MDCH</sub>   | 32    | _   | _                       | ns   | —     |

| ECn_MDC to ECn_MDIO delay      | t <sub>MDKHDX</sub> | 10    | _   | 16*t <sub>plb_clk</sub> | ns   | 5     |

# NP

#### Local Bus Controller (eLBC)

Table 50. Local Bus General Timing Parameters ( $BV_{DD} = 2.5 V DC$ )—PLL Enabled (continued)At recommended operating conditions with  $BV_{DD}$  of 2.5 V ± 5% (continued)

| Parameter                                                          | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output valid (except LAD/LDP and LALE)          | t <sub>LBKHOV1</sub> | —   | 2.4 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                          | t <sub>LBKHOV2</sub> | —   | 2.5 | ns   | 3     |

| Local bus clock to address valid for LAD                           | t <sub>LBKHOV3</sub> | —   | 2.4 | ns   | 3     |

| Local bus clock to LALE assertion                                  | t <sub>LBKHOV4</sub> | —   | 2.4 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)         | t <sub>LBKHOX1</sub> | 0.8 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKHOX2</sub> | 0.8 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKHOZ1</sub> | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKHOZ2</sub> | —   | 2.6 | ns   | 5     |

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 2.5-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

Table 51 describes the general timing parameters of the local bus interface at  $BV_{DD} = 1.8 \text{ V DC}$

Table 51. Local Bus General Timing Parameters ( $BV_{DD} = 1.8 \text{ V DC}$ )—PLL Enabled At recommended operating conditions with  $BV_{DD}$  of 1.8 V ± 5%

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 6.67 | 12  | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43   | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                  | t <sub>LBKSKEW</sub>                | _    | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 2.4  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKH2</sub>                | 1.9  | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | 1.1  | —   | ns   | 3, 4  |

Table 51. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)—PLL Enabled (continued)

At recommended operating conditions with  $\mathsf{BV}_{\mathsf{DD}}$  of 1.8 V ± 5% (continued)

| Parameter                                                            | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|----------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKH2</sub> | 1.1 | —   | ns   | 3, 4  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>lbotot</sub>  | 1.2 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKHOV1</sub> | _   | 3.2 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKHOV2</sub> | _   | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                             | t <sub>LBKHOV3</sub> | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                    | t <sub>LBKHOV4</sub> | _   | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)           | t <sub>LBKHOX1</sub> | 0.9 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                         | t <sub>LBKHOX2</sub> | 0.9 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)   | t <sub>LBKHOZ1</sub> | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                 | t <sub>LBKHOZ2</sub> |     | 2.6 | ns   | 5     |

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from BV<sub>DD</sub>/2 of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 1.8-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

Figure 29 provides the AC test load for the local bus.

Figure 29. Local Bus AC Test Load

GPIO

# 14 GPIO

This section describes the DC and AC electrical specifications for the GPIO interface of the MPC8572E.

# 14.1 GPIO DC Electrical Characteristics

Table 56 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 3.3 \text{ V DC}$ .

| Parameter                                                                      | Symbol           | Min                    | Мах                    | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------------------------|------|

| Supply voltage 3.3V                                                            | BV <sub>DD</sub> | 3.13                   | 3.47                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 2                      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3                   | 0.8                    | V    |

| Input current<br>( $BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD}$ )         | I <sub>IN</sub>  | _                      | ±5                     | μΑ   |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | —                      | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  |                        | 0.2                    | V    |

Table 56. GPIO DC Electrical Characteristics (3.3 V DC)

Note:

1. Note that the symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

Table 57 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 2.5 \text{ V DC}$ .

Table 57. GPIO DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                      | Symbol           | Min       | Мах                    | Unit |

|--------------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5V                                                            | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 1.70      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3      | 0.7                    | V    |

|                                                                                | IIH              | _         | 10                     | μΑ   |

| $(BV_{IN}^{1} = 0 \; V \; or \; BV_{IN} = BV_{DD})$                            | I <sub>IL</sub>  |           | -15                    |      |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -1 mA) | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> min, I <sub>OL</sub> = 1 mA)     | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

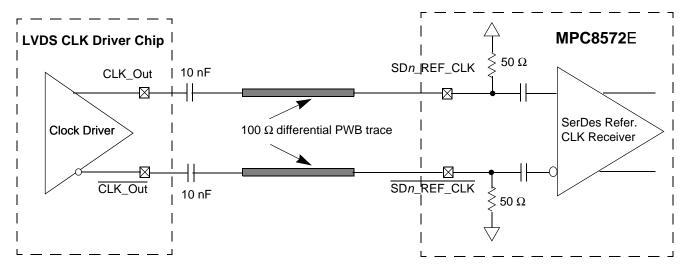

Figure 49 shows the SerDes reference clock connection reference circuits for LVDS type clock driver. Because LVDS clock driver's common mode voltage is higher than the MPC8572E SerDes reference clock input's allowed range (100 to 400mV), AC-coupled connection scheme must be used. It assumes the LVDS output driver features  $50-\Omega$  termination resistor. It also assumes that the LVDS transmitter establishes its own common mode level without relying on the receiver or other external component.

Figure 49. AC-Coupled Differential Connection with LVDS Clock Driver (Reference Only)

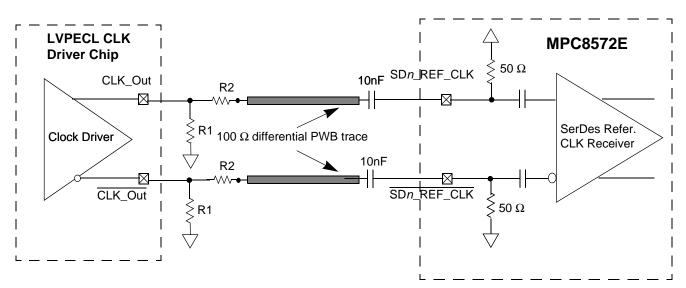

Figure 50 shows the SerDes reference clock connection reference circuits for LVPECL type clock driver. Because LVPECL driver's DC levels (both common mode voltages and output swing) are incompatible with MPC8572E SerDes reference clock input's DC requirement, AC-coupling must be used. Figure 50 assumes that the LVPECL clock driver's output impedance is  $50\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from  $140\Omega$  to  $240\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's  $50-\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8572E SerDes reference clock's differential input amplitude requirement (between 200mV and 800mV differential peak). For example, if the LVPECL output's differential peak is 900mV and the desired SerDes reference clock input amplitude is selected as 600mV, the attenuation factor is 0.67, which requires R2 =  $25\Omega$ . Consult

#### High-Speed Serial Interfaces (HSSI)

clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 50. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

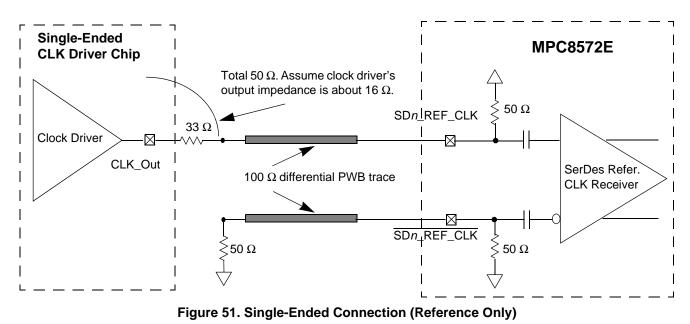

Figure 51 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with MPC8572E SerDes reference clock input's DC requirement.

# 15.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100KHz can be tracked by the PLL and data recovery loops and

Serial RapidIO

# 17.1 <u>DC Requirements</u> for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK

For more information, see Section 15.2, "SerDes Reference Clocks."

# 17.2 <u>AC Requirements</u> for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK

Figure 64lists the AC requirements.

| Table 64. SDn_ | _REF_CLK an | d SD <i>n</i> _REF | _CLK AC Requirements |

|----------------|-------------|--------------------|----------------------|

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Comments                                                         |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|------------------------------------------------------------------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 10(8)   | —   | ns    | 8 ns applies only to serial RapidIO with 125-MHz reference clock |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | —       | 80  | ps    | _                                                                |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -40 | _       | 40  | ps    | _                                                                |

# 17.3 Equalization

With the use of high speed serial links, the interconnect media causes degradation of the signal at the receiver. Effects such as Inter-Symbol Interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are as follows:

- A passive high pass filter network placed at the receiver. This is often referred to as passive equalization.

- The use of active circuits in the receiver. This is often referred to as adaptive equalization.

# 17.4 Explanatory Note on Transmitter and Receiver Specifications

AC electrical specifications are given for transmitter and receiver. Long run and short run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to serial RapidIO, as described in Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." The goal of this standard is that electrical designs for Serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

Package Description

### Table 76. MPC8572E Pinout Listing (continued)

| Signal                                            | Signal Name         | Package Pin Number        | Pin Type | Power<br>Supply  | Notes   |

|---------------------------------------------------|---------------------|---------------------------|----------|------------------|---------|

| TSEC3_GTX_CLK                                     | Transmit Clock Out  | AE17                      | 0        | TV <sub>DD</sub> |         |

| TSEC3_RX_CLK/FEC_RX_CL<br>K/FIFO3_RX_CLK          | Receive Clock       | AF17                      | Ι        | TV <sub>DD</sub> | 1       |

| TSEC3_RX_DV/FEC_RX_DV/<br>FIFO3_RX_DV             | Receive Data Valid  | AG14                      | Ι        | TV <sub>DD</sub> | 1       |

| TSEC3_RX_ER/FEC_RX_ER/<br>FIFO3_RX_ER             | Receive Error       | AH15                      | Ι        | TV <sub>DD</sub> | 1       |

| TSEC3_TX_CLK/FEC_TX_CL<br>K/FIFO3_TX_CLK          | Transmit Clock In   | AF16                      | I        | TV <sub>DD</sub> | 1       |

| TSEC3_TX_EN/FEC_TX_EN/F<br>IFO3_TX_EN             | Transmit Enable     | AJ18                      | 0        | TV <sub>DD</sub> | 1, 22   |

|                                                   | Three-Speed Et      | hernet Controller 4       |          |                  |         |

| TSEC4_TXD[3:0]/TSEC3_TXD[<br>7:4]/FIFO3_TXD[7:4]  | Transmit Data       | AD15, AC16, AC14,<br>AB16 | 0        | TV <sub>DD</sub> | 1, 5, 9 |

| TSEC4_RXD[3:0]/TSEC3_RXD<br>[7:4]/FIFO3_RXD[7:4]  | Receive Data        | AE15, AF13, AE14,<br>AH14 | Ι        | TV <sub>DD</sub> | 1       |

| TSEC4_GTX_CLK                                     | Transmit Clock Out  | AB14                      | 0        | TV <sub>DD</sub> | _       |

| TSEC4_RX_CLK/TSEC3_COL/<br>FEC_COL/FIFO3_TX_FC    | Receive Clock       | AG13                      | Ι        | TV <sub>DD</sub> | 1       |

| TSEC4_RX_DV/TSEC3_CRS/<br>FEC_CRS/FIFO3_RX_FC     | Receive Data Valid  | AD13                      | AD13 I/O |                  | 1, 23   |

| TSEC4_TX_EN/TSEC3_TX_E<br>R/FEC_TX_ER/FIFO3_TX_ER | Transmit Enable     | AB15                      | AB15 O   |                  | 1, 22   |

|                                                   | DL                  | JART                      |          |                  |         |

| UART_CTS[0:1]                                     | Clear to Send       | W30, Y27                  | I        | OV <sub>DD</sub> | _       |

| UART_RTS[0:1]                                     | Ready to Send       | W31, Y30                  | 0        | OV <sub>DD</sub> | 5, 9    |

| UART_SIN[0:1]                                     | Receive Data        | Y26, W29                  | I        | OV <sub>DD</sub> | _       |

| UART_SOUT[0:1]                                    | Transmit Data       | Y25, W26                  | 0        | OV <sub>DD</sub> | 5, 9    |

|                                                   | l <sup>2</sup> C lı | nterface                  | -        |                  |         |

| IIC1_SCL                                          | Serial Clock        | AC30                      | I/O      | OV <sub>DD</sub> | 4, 20   |

| IIC1_SDA                                          | Serial Data         | AB30                      | I/O      | OV <sub>DD</sub> | 4, 20   |

| IIC2_SCL                                          | Serial Clock        | AD30                      | I/O      | OV <sub>DD</sub> | 4, 20   |

| IIC2_SDA                                          | Serial Data         | AD29                      | I/O      | OV <sub>DD</sub> | 4, 20   |

| -                                                 | SerDes (x1          | 0) PCIe, SRIO             |          |                  |         |

# 21 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8572E.

# 21.1 System Clocking

The platform PLL generates the platform clock from the externally supplied SYSCLK input. The frequency ratio between the platform and SYSCLK is selected using the platform PLL ratio configuration bits as described in Section 19.2, "CCB/SYSCLK PLL Ratio." The MPC8572E includes seven PLLs, with the following functions:

- Two core PLLs have ratios that are individually configurable. Each e500 core PLL generates the core clock as a slave to the platform clock. The frequency ratio between the e500 core clock and the platform clock is selected using the e500 PLL ratio configuration bits as described in Section 19.3, "e500 Core PLL Ratio."

- The DDR complex PLL generates the clocking for the DDR controllers.

- The local bus PLL generates the clock for the local bus.

- The PLL for the SerDes1 module is used for PCI Express and Serial Rapid IO interfaces.

- The PLL for the SerDes2 module is used for the SGMII interface.

# 21.2 Power Supply Design

## 21.2.1 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins  $(AV_{DD}PLAT, AV_{DD}CORE0, AV_{DD}CORE1, AV_{DD}DDR, AV_{DD}LBIU, AV_{DD}SRDS1 and AV_{DD}SRDS2 respectively).$  The AV<sub>DD</sub> level should always be equivalent to V<sub>DD</sub>, and preferably these voltages are derived directly from V<sub>DD</sub> through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide independent filter circuits per PLL power supply as illustrated in Figure 62, one to each of the  $AV_{DD}$  pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of the 1023 FC-PBGA footprint, without the inductance of vias.