#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XFI

| Product Status                  | Active                                                       |

|---------------------------------|--------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                 |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                               |

| Speed                           | 1.5GHz                                                       |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                        |

| RAM Controllers                 | DDR2, DDR3                                                   |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10/100/1000Mbps (4)                                          |

| SATA                            | -                                                            |

| USB                             | -                                                            |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography, Random Number Generator                        |

| Package / Case                  | 1023-BFBGA, FCBGA                                            |

| Supplier Device Package         | 1023-FCPBGA (33x33)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8572ecvtavne |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

the upper and lower words of the 64-bit GPRs as they are defined by the SPE APU.

- Embedded vector and scalar single-precision floating-point APUs. Provide an instruction set for single-precision (32-bit) floating-point instructions.

- Double-precision floating-point APU. Provides an instruction set for double-precision (64-bit) floating-point instructions that use the 64-bit GPRs.

- 36-bit real addressing

- Memory management unit (MMU). Especially designed for embedded applications. Supports 4-Kbyte to 4-Gbyte page sizes.

- Enhanced hardware and software debug support

- Performance monitor facility that is similar to, but separate from, the MPC8572E performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operation.

- 1 Mbyte L2 cache/SRAM

- Shared by both cores.

- Flexible configuration and individually configurable per core.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- Per-way allocation of cache region to a given processor.

- SRAM features include the following:

- 1, 2, 4, or 8 ways can be configured as SRAM.

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- e500 coherency module (ECM) manages core and intrasystem transactions

- Address translation and mapping unit (ATMU)

- Twelve local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

Overview

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing.

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs.

- Interrupt summary registers allow fast identification of interrupt source.

- Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, SSL/TLS, SRTP, 802.16e, and 3GPP

- Four crypto-channels, each supporting multi-command descriptor chains

- Dynamic assignment of crypto-execution units through an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- PKEU—public key execution unit

- RSA and Diffie-Hellman; programmable field size up to 4096 bits

- Elliptic curve cryptography with F<sub>2</sub>m and F(p) modes and programmable field size up to 1023 bits

- DEU—Data Encryption Standard execution unit

- DES, 3DES

- Two key (K1, K2, K1) or three key (K1, K2, K3)

- ECB, CBC and OFB-64 modes for both DES and 3DES

- AESU—Advanced Encryption Standard unit

- Implements the Rijndael symmetric key cipher

- ECB, CBC, CTR, CCM, GCM, CMAC, OFB-128, CFB-128, and LRW modes

- 128-, 192-, and 256-bit key lengths

- AFEU—ARC four execution unit

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- MDEU—message digest execution unit

- SHA-1 with 160-bit message digest

- SHA-2 (SHA-256, SHA-384, SHA-512)

- MD5 with 128-bit message digest

- HMAC with all algorithms

- KEU—Kasumi execution unit

- Implements F8 algorithm for encryption and F9 algorithm for integrity checking

- Also supports A5/3 and GEA-3 algorithms

- RNG—random number generator

- XOR engine for parity checking in RAID storage applications

- CRC execution unit

- CRC-32 and CRC-32C

- Pattern Matching Engine with DEFLATE decompression

- Regular expression (regex) pattern matching

- Built-in case insensitivity, wildcard support, no pattern explosion

- Cross-packet pattern detection

- Fast pattern database compilation and fast incremental updates

- 16000 patterns, each up to 128 bytes in length

- Patterns can be split into 256 sets, each of which can contain 16 subsets

- Stateful rule engine enables hardware execution of state-aware logic when a pattern is found

- Useful for contextual searches, multi-pattern signatures, or for performing additional checks after a pattern is found

- Capable of capturing and utilizing data from the data stream (such as LENGTH field) and using that information in subsequent pattern searches (for example, positive match only if pattern is detected within the number of bytes specified in the LENGTH field)

- 8192 stateful rules

- Deflate engine

- Supports decompression of DEFLATE compression format including zlib and gzip

- Can work independently or in conjunction with the Pattern Matching Engine (that is decompressed data can be passed directly to the Pattern Matching Engine without further software involvement or memory copying)

- Two Table Lookup Units (TLU)

- Hardware-based lookup engine offloads table searches from e500 cores

- Longest prefix match, exact match, chained hash, and flat data table formats

- Up to 32 tables, with each table up to 16M entries

- 32-, 64-, 96-, or 128-bit keys

- Two I<sup>2</sup>C controllers

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset the I<sup>2</sup>C interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- DUART

- Two 4-wire interfaces (SIN, SOUT,  $\overline{\text{RTS}}$ ,  $\overline{\text{CTS}}$ )

- Programming model compatible with the original 16450 UART and the PC16550D

- Enhanced local bus controller (eLBC)

**RESET** Initialization

Table 8. DDRCLK AC Timing Specifications (continued)

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition | Symbol | Min | Typical | Max     | Unit | Notes   |

|---------------------|--------|-----|---------|---------|------|---------|

| DDRCLK jitter       | _      |     |         | +/- 150 | ps   | 4, 5, 6 |

Notes:

- 1. **Caution:** The DDR complex clock to DDRCLK ratio settings must be chosen such that the resulting DDR complex clock frequency does not exceed the maximum or minimum operating frequencies. Refer to Section 19.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

- 2. Rise and fall times for DDRCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The DDRCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track DDRCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on DDRCLK.

## 4.5 Platform to eTSEC FIFO Restrictions

Note the following eTSEC FIFO mode maximum speed restrictions based on platform (CCB) frequency.

For FIFO GMII modes (both 8 and 16 bit) and 16-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/4.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 127 MHz.

For 8-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/3.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz.

## 4.6 Other Input Clocks

For information on the input clocks of other functional blocks of the platform, such as SerDes and eTSEC, see the respective sections of this document.

## 5 **RESET** Initialization

Table 9 describes the AC electrical specifications for the RESET initialization timing.

#### **Table 9. RESET Initialization Timing Specifications**

| Parameter/Condition               | Min | Мах | Unit    | Notes |

|-----------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET | 100 | —   | μs      | 2     |

| Minimum assertion time for SRESET | 3   | —   | SYSCLKs | 1     |

| PLL config input setup time with stable SYSCLK before HRESET negation                                           | 100 |   | μs      | — |

|-----------------------------------------------------------------------------------------------------------------|-----|---|---------|---|

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET                     | 4   | _ | SYSCLKs | 1 |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET                   | 2   | _ | SYSCLKs | 1 |

| Maximum valid-to-high imp <u>edance time</u> for actively driven POR configs with respect to negation of HRESET | _   | 5 | SYSCLKs | 1 |

Table 9. RESET Initialization Timing Specifications (continued)

#### Notes:

2. Reset assertion timing requirements for DDR3 DRAMs may differ.

#### Table 10 provides the PLL lock times.

| Table | 10. | PLL | Lock | Times |

|-------|-----|-----|------|-------|

|-------|-----|-----|------|-------|

| Parameter/Condition | Symbol | Min | Typical | Max |

|---------------------|--------|-----|---------|-----|

| PLL lock times      | —      | 100 | μs      | _   |

| Local bus PLL       | —      | 50  | μs      |     |

## 6 DDR2 and DDR3 SDRAM Controller

This section describes the DC and AC electrical specifications for the DDR2 and DDR3 SDRAM controller interface of the MPC8572E. Note that the required  $GV_{DD}(typ)$  voltage is 1.8Vor 1.5 V when interfacing to DDR2 or DDR3 SDRAM, respectively.

## 6.1 DDR2 and DDR3 SDRAM Interface DC Electrical Characteristics

Table 11 provides the recommended operating conditions for the DDR SDRAM controller of the MPC8572E when interfacing to DDR2 SDRAM.

| Parameter/Condition                              | Symbol              | Min                  | Мах                         | Unit | Notes |

|--------------------------------------------------|---------------------|----------------------|-----------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>    | 1.71                 | 1.89                        | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> n | $0.49 	imes GV_{DD}$ | $0.51 	imes GV_{DD}$        | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>     | $MV_{REF}n - 0.04$   | $MV_{REF}n + 0.04$          | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>     | $MV_{REF}n + 0.125$  | GV <sub>DD</sub> + 0.3      | V    | _     |

| Input low voltage                                | V <sub>IL</sub>     | -0.3                 | MV <sub>REF</sub> n - 0.125 | V    | _     |

| Output leakage current                           | I <sub>OZ</sub>     | -50                  | 50                          | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>     | -13.4                | _                           | mA   | —     |

| Table 11 | DDR2 SDRAM | Interface DC | Electrical | Characteristics | for GV(tvn) | 1 = 18V |

|----------|------------|--------------|------------|-----------------|-------------|---------|

|          |            | menace DO    | Liccultur  | onaracteristics |             | / I.O V |

<sup>1.</sup> SYSCLK is the primary clock input for the MPC8572E.

#### DDR2 and DDR3 SDRAM Controller

#### Table 17. DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                         | Symbol              | Min  | Max | Unit | Notes |

|-----------------------------------|---------------------|------|-----|------|-------|

| Controller Skew for MDQS—MDQ/MECC | t <sub>CISKEW</sub> | —    | _   | ps   | 1, 2  |

| 800 MHz                           | _                   | -200 | 200 | —    | —     |

| 667 MHz                           | _                   | -240 | 240 | —    | —     |

| 533 MHz                           | _                   | -300 | 300 | —    | —     |

| 400 MHz                           | _                   | -365 | 365 |      | —     |

Note:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

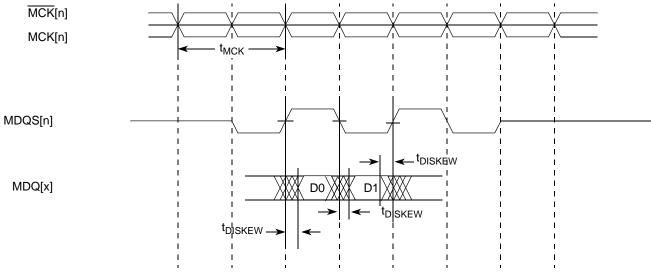

The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called tDISKEW. This can be determined by the following equation: tDISKEW =+/-(T/4 – abs(tCISKEW)) where T is the clock period and abs(tCISKEW) is the absolute value of tCISKEW.

Figure 3 shows the DDR2 and DDR3 SDRAM interface input timing diagram.

Figure 3. DDR2 and DDR3 SDRAM Interface Input Timing Diagram

## 6.2.2 DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications

Table 18 contains the output AC timing targets for the DDR2 and DDR3 SDRAM interface.

#### Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                                 | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|-------------------------------------------|---------------------|-----|-----|------|-------|

| MCK[n] cycle time                         | t <sub>MCK</sub>    | 2.5 | 5   | ns   | 2     |

| ADDR/CMD output setup with respect to MCK | t <sub>DDKHAS</sub> |     |     | ns   | 3     |

# Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications (continued)At recommended operating conditions with $GV_{DD}$ of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                                      | Symbol <sup>1</sup>                         | Min    | Мах   | Unit | Notes |

|------------------------------------------------|---------------------------------------------|--------|-------|------|-------|

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | —     |      |       |

| 533 MHz                                        |                                             | 1.48   | —     |      |       |

| 400 MHz                                        |                                             | 1.95   | —     |      |       |

| ADDR/CMD output hold with respect to MCK       | t <sub>DDKHAX</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | —     |      |       |

| 667 MHz                                        |                                             | 1.10   | —     |      |       |

| 533 MHz                                        |                                             | 1.48   | —     |      |       |

| 400 MHz                                        |                                             | 1.95   | —     |      |       |

| MCS[n] output setup with respect to MCK        | t <sub>DDKHCS</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   |       |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        | t <sub>DDKHCS</sub>                         | 1.95   |       | ns   | 3     |

| MCS[n] output hold with respect to MCK         | t <sub>DDKHCX</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | —     |      |       |

| 667 MHz                                        |                                             | 1.10   | —     |      |       |

| 533 MHz                                        |                                             | 1.48   | —     |      |       |

| 400 MHz                                        |                                             | 1.95   | —     |      |       |

| MCK to MDQS Skew                               | t <sub>DDKHMH</sub>                         |        |       | ns   | 4     |

| 800 MHz                                        |                                             | -0.375 | 0.375 |      |       |

| <= 667 MHz                                     |                                             | -0.6   | 0.6   |      |       |

| MDQ/MECC/MDM output setup with respect to MDQS | t <sub>DDKHDS,</sub><br>t <sub>DDKLDS</sub> |        |       | ps   | 5     |

| 800 MHz                                        |                                             | 375    | —     |      |       |

| 667 MHz                                        |                                             | 450    | _     |      |       |

| 533 MHz                                        |                                             | 538    | —     |      |       |

| 400 MHz                                        |                                             | 700    | —     |      |       |

| MDQ/MECC/MDM output hold with respect to MDQS  | t <sub>DDKHDX,</sub><br>t <sub>DDKLDX</sub> |        |       | ps   | 5     |

| 800 MHz                                        |                                             | 375    | —     |      |       |

| 667 MHz                                        |                                             | 450    | _     |      |       |

| Parameter                                     | Symbol                            | Min | Тур | Мах | Unit | Notes |

|-----------------------------------------------|-----------------------------------|-----|-----|-----|------|-------|

| Change in $V_{\mbox{OS}}$ between "0" and "1" | $\Delta V_{OS}$                   | _   | _   | 25  | mV   | —     |

| Output current on short to GND                | I <sub>SA</sub> , I <sub>SB</sub> | _   | _   | 40  | mA   | _     |

Table 38. SGMII DC Transmitter Electrical Characteristics (continued)

Note:

1. This will not align to DC-coupled SGMII.  $XV_{DD\_SRDS2-Typ}$ =1.1 V.

2. |V<sub>OD</sub>| = |V<sub>SD2\_TXn</sub> - V<sub>SD2\_TXn</sub>|. |V<sub>OD</sub>| is also referred as output differential peak voltage. V<sub>TX-DIFFp-p</sub> = 2\*|V<sub>OD</sub>|.

3. The |V<sub>OD</sub>| value shown in the table assumes the following transmit equalization setting in the XMITEQAB (for SerDes 2 lanes A & B) or XMITEQEF (for SerDes 2 lanes E & E) bit field of MPC8572E's SerDes 2 Control Register:

•The MSbit (bit 0) of the above bit field is set to zero (selecting the full V<sub>DD-DIFF-p-p</sub> amplitude - power up default);

•The LSbits (bit [1:3]) of the above bit field is set based on the equalization setting shown in table.

4. V<sub>OS</sub> is also referred to as output common mode voltage.

5.The |V<sub>OD</sub>| value shown in the Typ column is based on the condition of XV<sub>DD\_SRDS2-Typ</sub>=1.1V, no common mode offset variation (V<sub>OS</sub> =550mV), SerDes2 transmitter is terminated with 100-Ω differential load between SD2\_TX[n] and SD2\_TX[n].

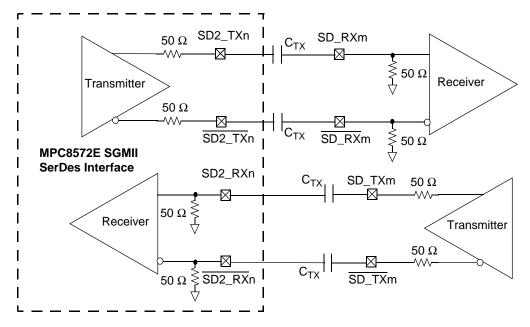

Figure 22. 4-Wire AC-Coupled SGMII Serial Link Connection Example

## 8.3.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs ( $SD2_TX[n]$  and  $\overline{SD2_TX[n]}$ ) or at the receiver inputs ( $SD2_RX[n]$  and  $\overline{SD2_RX[n]}$ ) as depicted in Figure 25, respectively.

## 8.3.4.1 SGMII Transmit AC Timing Specifications

Table 40 provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### Table 40. SGMII Transmit AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2}$  = 1.1V ± 5%.

| Parameter                           | Symbol            | Min    | Тур | Max    | Unit   | Notes |

|-------------------------------------|-------------------|--------|-----|--------|--------|-------|

| Deterministic Jitter                | JD                | —      | _   | 0.17   | UI p-p | _     |

| Total Jitter                        | JT                | —      | _   | 0.35   | UI p-p | _     |

| Unit Interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1     |

| V <sub>OD</sub> fall time (80%-20%) | tfall             | 50     | _   | 120    | ps     | _     |

| V <sub>OD</sub> rise time (20%-80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     | _     |

Notes:

1. Each UI is 800 ps  $\pm$  100 ppm.

### 8.3.4.2 SGMII Receive AC Timing Specifications

Table 41 provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 24 shows the SGMII receiver input compliance mask eye diagram.

#### Table 41. SGMII Receive AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2} = 1.1V \pm 5\%$ .

| Parameter                                          | Symbol          | Min    | Тур | Max               | Unit   | Notes |

|----------------------------------------------------|-----------------|--------|-----|-------------------|--------|-------|

| Deterministic Jitter Tolerance                     | JD              | 0.37   | —   | —                 | UI p-p | 1     |

| Combined Deterministic and Random Jitter Tolerance | JDR             | 0.55   | —   | _                 | UI p-p | 1     |

| Sinusoidal Jitter Tolerance                        | JSIN            | 0.1    | —   | —                 | UI p-p | 1     |

| Total Jitter Tolerance                             | JT              | 0.65   |     | _                 | UI p-p | 1     |

| Bit Error Ratio                                    | BER             | _      | —   | 10 <sup>-12</sup> |        | _     |

| Unit Interval                                      | UI              | 799.92 | 800 | 800.08            | ps     | 2     |

| AC Coupling Capacitor                              | C <sub>TX</sub> | 5      | —   | 200               | nF     | 3     |

Notes:

1. Measured at receiver.

2. Each UI is 800 ps  $\pm$  100 ppm.

3. The external AC coupling capacitor is required. It is recommended to be placed near the device transmitter outputs.

4. See RapidIO 1x/4x LP Serial Physical Layer Specification for interpretation of jitter specifications.

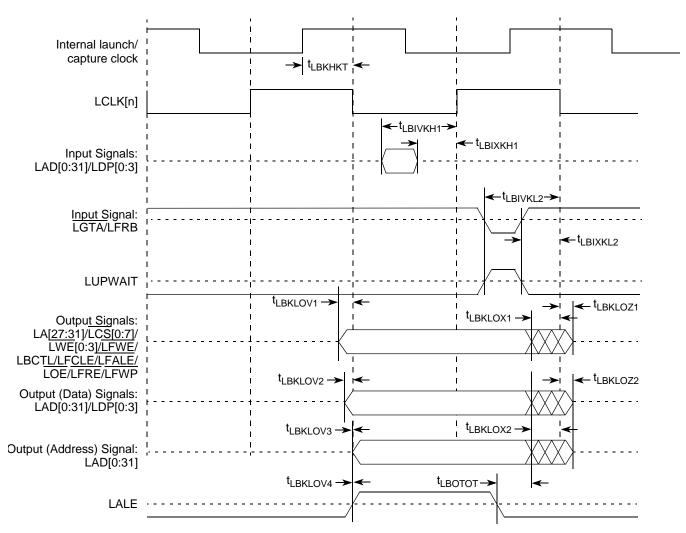

Local Bus Controller (eLBC)

Figure 31. Local Bus Signals (PLL Bypass Mode)

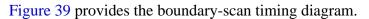

Figure 39. Boundary-Scan Timing Diagram

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the MPC8572E.

## 13.1 I<sup>2</sup>C DC Electrical Characteristics

Table 54 provides the DC electrical characteristics for the  $I^2C$  interfaces.

| Table 54. I <sup>2</sup> C DC Electrical Characteristic | ;S |

|---------------------------------------------------------|----|

|---------------------------------------------------------|----|

| Parameter                                                                                                | Symbol              | Min                                | Мах                    | Unit | Notes |

|----------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------|------|-------|

| Input high voltage level                                                                                 | V <sub>IH</sub>     | $0.7 \times \text{OV}_{\text{DD}}$ | OV <sub>DD</sub> + 0.3 | V    | —     |

| Input low voltage level                                                                                  | V <sub>IL</sub>     | -0.3                               | $0.3 	imes OV_{DD}$    | V    | —     |

| Low level output voltage                                                                                 | V <sub>OL</sub>     | 0                                  | 0.4                    | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>I2KHKL</sub> | 0                                  | 50                     | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | Ι <sub>Ι</sub>      | -10                                | 10                     | μA   | 3     |

| Symbol               | Parameter  | Min | Nominal | Max | Units | Comments                                                                                                                                                                                                                                 |

|----------------------|------------|-----|---------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L <sub>RX-SKEW</sub> | Total Skew |     |         | 20  | ns    | Skew across all lanes on a Link. This<br>includes variation in the length of SKP<br>ordered set (for example, COM and one to<br>five SKP Symbols) at the RX as well as any<br>delay differences arising from the<br>interconnect itself. |

#### Notes:

- 1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 57 should be used as the RX device when taking measurements (also refer to the Receiver compliance eye diagram shown in Figure 56). If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

- 3. A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the Transmitter and interconnect collected any 250 consecutive UIs. The T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as the reference for the eye diagram.

- 4. The Receiver input impedance shall result in a differential return loss greater than or equal to 15 dB with the D+ line biased to 300 mV and the D- line biased to -300 mV and a common mode return loss greater than or equal to 6 dB (no bias required) over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements for is 50 ohms to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50 ohm probes see Figure 57). Note: that the series capacitors CTX is optional for the return loss measurement.

- 5. Impedance during all LTSSM states. When transitioning from a Fundamental Reset to Detect (the initial state of the LTSSM) there is a 5 ms transition time before Receiver termination values must be met on all un-configured Lanes of a Port.

- 6. The RX DC Common Mode Impedance that exists when no power is present or Fundamental Reset is asserted. This helps ensure that the Receiver Detect circuit does not falsely assume a Receiver is powered on when it is not. This term must be measured at 300 mV above the RX ground.

- 7. It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function. Least squares and median deviation fits have worked well with experimental and simulated data.

Package Description

### Table 76. MPC8572E Pinout Listing (continued)

| Signal                            | Signal Name                   | Package Pin Number                                   | Pin Type | Power<br>Supply  | Notes   |

|-----------------------------------|-------------------------------|------------------------------------------------------|----------|------------------|---------|

| IRQ_OUT                           | Interrupt Output              | U24                                                  | 0        | OV <sub>DD</sub> | 2, 4    |

|                                   | 1588                          | 3                                                    |          |                  |         |

| TSEC_1588_CLK                     | Clock In                      | AM22                                                 | I        | LV <sub>DD</sub> |         |

| TSEC_1588_TRIG_IN                 | Trigger In                    | AM23                                                 | I        | LV <sub>DD</sub> | _       |

| TSEC_1588_TRIG_OUT                | Trigger Out                   | AA23                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| TSEC_1588_CLK_OUT                 | Clock Out                     | AC23                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| TSEC_1588_PULSE_OUT1              | Pulse Out1                    | AA22                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| TSEC_1588_PULSE_OUT2              | Pulse Out2                    | AB23                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

|                                   | Ethernet Managem              | ent Interface 1                                      |          |                  |         |

| EC1_MDC                           | Management Data Clock         | AL30                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| EC1_MDIO                          | Management Data In/Out        | AM25                                                 | I/O      | LV <sub>DD</sub> |         |

|                                   | Ethernet Managem              | ent Interface 3                                      |          |                  |         |

| EC3_MDC                           | Management Data Clock         | AF19                                                 | 0        | TV <sub>DD</sub> | 5, 9    |

| EC3_MDIO                          | Management Data In/Out        | AF18                                                 | I/O      | TV <sub>DD</sub> |         |

|                                   | Ethernet Managem              | ent Interface 5                                      |          |                  |         |

| EC5_MDC                           | Management Data Clock         | AF14                                                 | 0        | TV <sub>DD</sub> | 21      |

| EC5_MDIO                          | Management Data In/Out        | AF15                                                 | I/O      | TV <sub>DD</sub> |         |

|                                   | Gigabit Ethernet R            | eference Clock                                       |          |                  |         |

| EC_GTX_CLK125                     | Reference Clock               | AM24                                                 | Ι        | LV <sub>DD</sub> | 32      |

|                                   | Three-Speed Ether             | net Controller 1                                     |          |                  |         |

| TSEC1_RXD[7:0]/FIFO1_RXD[<br>7:0] | Receive Data                  | AM28, AL28, AM26,<br>AK23, AM27, AK26,<br>AL29, AM30 | I        | LV <sub>DD</sub> | 1       |

| TSEC1_TXD[7:0]/FIFO1_TXD[<br>7:0] | Transmit Data                 | AC20, AD20, AE22,<br>AB22, AC22, AD21,<br>AB21, AE21 | 0        | LV <sub>DD</sub> | 1, 5, 9 |

| TSEC1_COL/FIFO1_TX_FC             | Collision Detect/Flow Control | AJ23                                                 | Ι        | LV <sub>DD</sub> | 1       |

| TSEC1_CRS/FIFO1_RX_FC             | Carrier Sense/Flow Control    | AM31                                                 | I/O      | LV <sub>DD</sub> | 1, 16   |

| TSEC1_GTX_CLK                     | Transmit Clock Out            | AK27                                                 | 0        | LV <sub>DD</sub> |         |

| TSEC1_RX_CLK/FIFO1_RX_C<br>LK     | Receive Clock                 | AL25                                                 | I        | LV <sub>DD</sub> | 1       |

Package Description

| Signal Name                                 | Package Pin Number                                                                                                                                                                                          | Pin Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power<br>Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Receive Data (negative)                     | AK31, AJ29, AF29,<br>AE31                                                                                                                                                                                   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| SGMII Tx Data eTSEC4                        | AH26                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| SGMII Tx Data eTSEC3                        | AG24                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| SGMII Tx Data eTSEC2                        | AE24                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| SGMII Tx Data eTSEC1                        | AD26                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Transmit Data (negative)                    | AH27, AG25, AE25,<br>AD27                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| PLL Test Point Digital                      | AH32                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| PLL Reference Clock                         | AG32                                                                                                                                                                                                        | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| PLL Reference Clock<br>Complement           | AG31                                                                                                                                                                                                        | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| —                                           | AF26, AF27                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| General-Purpose                             | Input/Output                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| General Purpose Input / Output              | B27, A28, B31, A32,<br>B30, A31, B28, B29                                                                                                                                                                   | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| System Co                                   | ontrol                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Hard Reset                                  | AC31                                                                                                                                                                                                        | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Hard Reset Request                          | L23                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| Soft Reset                                  | P24                                                                                                                                                                                                         | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Checkstop In Processor 0                    | N26                                                                                                                                                                                                         | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |