# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.067GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                   |

| RAM Controllers                 | DDR2, DDR3                                                              |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                  |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | Cryptography, Random Number Generator                                   |

| Package / Case                  | 1023-BFBGA, FCBGA                                                       |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572elvtarle |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Three inbound windows plus a configuration window on PCI Express

- Four inbound windows plus a default window on Serial RapidIO®

- Four outbound windows plus default translation for PCI Express

- Eight outbound windows plus default translation for Serial RapidIO with segmentation and sub-segmentation support

- Two 64-bit DDR2/DDR3 memory controllers

- Programmable timing supporting DDR2 and DDR3 SDRAM

- 64-bit data interface per controller

- Four banks of memory supported, each up to 4 Gbytes, for a maximum of 16 Gbytes per controller

- DRAM chip configurations from 64 Mbits to 4 Gbits with x8/x16 data ports

- Full ECC support

- Page mode support

- Up to 32 simultaneous open pages for DDR2 or DDR3

- Contiguous or discontiguous memory mapping

- Cache line, page, bank, and super-bank interleaving between memory controllers

- Read-modify-write support for RapidIO atomic increment, decrement, set, and clear transactions

- Sleep mode support for self-refresh SDRAM

- On-die termination support when using DDR2 or DDR3

- Supports auto refreshing

- On-the-fly power management using CKE signal

- Registered DIMM support

- Fast memory access through JTAG port

- 1.8-V SSTL\_1.8 compatible I/O

- Support 1.5-V operation for DDR3. The detail is TBD pending on official release of appropriate industry specifications.

- Support for battery-backed main memory

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture.

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts

- Supports 4 message interrupts per processor with 32-bit messages

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high resolution timers/counters per processor that can generate interrupts

- Supports a variety of other internal interrupt sources

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

# 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| Table 1. Absolute Maximum Ratings | 1 |

|-----------------------------------|---|

|-----------------------------------|---|

|                                       | Characteristic                                                                         | Symbol                                        | Range                                                                | Unit | Notes |

|---------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------|------|-------|

| Core supply voltag                    | e                                                                                      | V <sub>DD</sub>                               | -0.3 to 1.21                                                         | V    |       |

| PLL supply voltage                    | 3                                                                                      | AV <sub>DD</sub>                              | V <sub>DD</sub> -0.3 to 1.21 V                                       |      | _     |

| Core power supply                     | ofor SerDes transceivers                                                               | SV <sub>DD</sub>                              | -0.3 to 1.21                                                         | V    | _     |

| Pad power supply                      | for SerDes transceivers                                                                | XV <sub>DD</sub>                              | -0.3 to 1.21                                                         | V    | _     |

| DDR SDRAM                             | DDR2 SDRAM Interface                                                                   | GV <sub>DD</sub>                              | -0.3 to 1.98                                                         | V    | _     |

| Controller I/O<br>supply voltage      | DDR3 SDRAM Interface                                                                   | _                                             | -0.3 to 1.65                                                         |      | —     |

| Three-speed Ether<br>management volta | rnet I/O, FEC management interface, MII<br>ge                                          | LV <sub>DD</sub> (for eTSEC1 and eTSEC2)      | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | 2     |

|                                       |                                                                                        | TV <sub>DD</sub> (for eTSEC3 and eTSEC4, FEC) | -0.3 to 3.63<br>-0.3 to 2.75                                         | —    | 2     |

| DUART, system co<br>I/O voltage       | ontrol and power management, I <sup>2</sup> C, and JTAG                                | OV <sub>DD</sub>                              | -0.3 to 3.63                                                         | V    | —     |

| Local bus and GPI                     | O I/O voltage                                                                          | BV <sub>DD</sub>                              | -0.3 to 3.63<br>-0.3 to 2.75<br>-0.3 to 1.98                         | V    | _     |

| Input voltage                         | DDR2 and DDR3 SDRAM interface signals                                                  | MV <sub>IN</sub>                              | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 3     |

|                                       | DDR2 and DDR3 SDRAM interface reference                                                | MV <sub>REF</sub> n                           | -0.3 to (GV <sub>DD</sub> /2 + 0.3)                                  | V    | —     |

|                                       | Three-speed Ethernet signals                                                           | LV <sub>IN</sub><br>TV <sub>IN</sub>          | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 3     |

|                                       | Local bus and GPIO signals                                                             | BV <sub>IN</sub>                              | –0.3 to (BV <sub>DD</sub> + 0.3)                                     | —    | —     |

|                                       | DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                              | –0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 3     |

| Storage temperatu                     | re range                                                                               | T <sub>STG</sub>                              | –55 to 150                                                           | °C   | —     |

Notes:

1. Functional operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

The 3.63V maximum is only supported when the port is configured in GMII, MII, RMII or TBI modes; otherwise the 2.75V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

3. (M,L,O)V<sub>IN</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

#### DDR2 and DDR3 SDRAM Controller

## Table 11. DDR2 SDRAM Interface DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V (continued)

| Parameter/Condition                             | Symbol          | Min  | Мах | Unit | Notes |

|-------------------------------------------------|-----------------|------|-----|------|-------|

| Output low current (V <sub>OUT</sub> = 0.280 V) | I <sub>OL</sub> | 13.4 | _   | mA   | _     |

Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm GV}_{\rm DD}$  at all times.

- 2.  $MV_{REF}n$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}n$  may not exceed ±2% of the DC value.

- 3. V<sub>TT</sub> is not applied directly to the device. It is the supply to that far end signal termination is made and is expected to be equal to MV<sub>REF</sub>*n*. This rail should track variations in the DC level of MV<sub>REF</sub>*n*.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

Table 12 provides the recommended operating conditions for the DDR SDRAM controller of the MPC8572E when interfacing to DDR3 SDRAM.

| Parameter/Condition    | Symbol              | Min                  | Typical                            | Max | Unit |

|------------------------|---------------------|----------------------|------------------------------------|-----|------|

| I/O supply voltage     | GV <sub>DD</sub>    | 1.425                | 1.575                              | V   | 1    |

| I/O reference voltage  | MV <sub>REF</sub> n | $0.49 	imes GV_{DD}$ | $0.51 	imes GV_{DD}$               | V   | 2    |

| Input high voltage     | V <sub>IH</sub>     | $MV_{REF}n + 0.100$  | GV <sub>DD</sub>                   | V   | —    |

| Input low voltage      | V <sub>IL</sub>     | GND                  | MV <sub>REF</sub> <i>n</i> - 0.100 | V   | —    |

| Output leakage current | I <sub>OZ</sub>     | -50                  | 50                                 | μΑ  | 3    |

Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm GV}_{\rm DD}$  at all times.

2.  $MV_{REF}n$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}n$  may not exceed ±1% of the DC value.

3. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

## Table 13 provides the DDR SDRAM controller interface capacitance for DDR2 and DDR3.

## Table 13. DDR2 and DDR3 SDRAM Interface Capacitance for GV<sub>DD</sub>(typ)=1.8 V and 1.5 V

| Parameter/Condition                          | Symbol           | Min | Typical | Мах | Unit |

|----------------------------------------------|------------------|-----|---------|-----|------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8       | pF  | 1, 2 |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5     | pF  | 1, 2 |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 1.8 V ± 0.090 V (for DDR2), f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

2. This parameter is sampled.  $GV_{DD}$  = 1.5 V ± 0.075 V (for DDR3), f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.175 V.

# Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications (continued)At recommended operating conditions with $GV_{DD}$ of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                                      | Symbol <sup>1</sup>                         | Min    | Мах   | Unit | Notes |

|------------------------------------------------|---------------------------------------------|--------|-------|------|-------|

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | —     |      |       |

| 400 MHz                                        |                                             | 1.95   | —     |      |       |

| ADDR/CMD output hold with respect to MCK       | t <sub>DDKHAX</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | —     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        |                                             | 1.95   | _     |      |       |

| MCS[n] output setup with respect to MCK        | t <sub>DDKHCS</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   |       |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        | t <sub>DDKHCS</sub>                         | 1.95   |       | ns   | 3     |

| MCS[n] output hold with respect to MCK         | t <sub>DDKHCX</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | —     |      |       |

| 667 MHz                                        |                                             | 1.10   | —     |      |       |

| 533 MHz                                        |                                             | 1.48   | —     |      |       |

| 400 MHz                                        |                                             | 1.95   | —     |      |       |

| MCK to MDQS Skew                               | t <sub>DDKHMH</sub>                         |        |       | ns   | 4     |

| 800 MHz                                        |                                             | -0.375 | 0.375 |      |       |

| <= 667 MHz                                     |                                             | -0.6   | 0.6   |      |       |

| MDQ/MECC/MDM output setup with respect to MDQS | t <sub>DDKHDS,</sub><br>t <sub>DDKLDS</sub> |        |       | ps   | 5     |

| 800 MHz                                        |                                             | 375    | —     |      |       |

| 667 MHz                                        |                                             | 450    | _     |      |       |

| 533 MHz                                        |                                             | 538    | —     |      |       |

| 400 MHz                                        |                                             | 700    | —     |      |       |

| MDQ/MECC/MDM output hold with respect to MDQS  | t <sub>DDKHDX,</sub><br>t <sub>DDKLDX</sub> |        |       | ps   | 5     |

| 800 MHz                                        |                                             | 375    | —     |      |       |

| 667 MHz                                        |                                             | 450    | _     |      |       |

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

# 7.2 DUART AC Electrical Specifications

Table 22 provides the AC timing parameters for the DUART interface.

# Table 22. DUART AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter         | Value                       | Unit | Notes   |

|-------------------|-----------------------------|------|---------|

| Minimum baud rate | f <sub>CCB</sub> /1,048,576 | baud | 1, 2    |

| Maximum baud rate | f <sub>CCB</sub> /16        | baud | 1, 2, 3 |

| Oversample rate   | 16                          | _    | 1, 4    |

## Notes:

1. Guaranteed by design

- 2. f<sub>CCB</sub> refers to the internal platform clock frequency.

- 3. Actual attainable baud rate is limited by the latency of interrupt processing.

- 4. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

# 8 Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

This section provides the AC and DC electrical characteristics for the enhanced three-speed Ethernet controller.

# 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics

The electrical characteristics specified here apply to all FIFO mode, gigabit media independent interface (GMII), media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), and reduced media independent interface (RMII) signals except management data input/output (MDIO) and management data clock (MDC), and serial gigabit media independent interface (SGMII). The RGMII, RTBI and FIFO mode interfaces are defined for 2.5 V, while the GMII, MII, RMII, and TBI interfaces can operate at both 2.5 V and 3.3V.

The GMII, MII, or TBI interface timing is compliant with IEEE 802.3. The RGMII and RTBI interfaces follow the Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3 (12/10/2000). The RMII interface follows the RMII Consortium RMII Specification Version 1.2 (3/20/1998).

The electrical characteristics for MDIO and MDC are specified in Section 9, "Ethernet Management Interface Electrical Characteristics."

The electrical characteristics for SGMII is specified in Section 8.3, "SGMII Interface Electrical Characteristics." The SGMII interface conforms (with exceptions) to the Serial-GMII Specification Version 1.8.

| Table 24, MIL GMIL | RMIL RGI | /III. TBI. RTB                          | I, and FIFO DC Electrica | Characteristics | (continued) |

|--------------------|----------|-----------------------------------------|--------------------------|-----------------|-------------|

|                    | ,,       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                          |                 | ooninaca)   |

| Parameters                                                | Symbol          | Min | Мах | Unit | Notes  |

|-----------------------------------------------------------|-----------------|-----|-----|------|--------|

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$ | IIH             | _   | 10  | μΑ   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)              | Ι <sub>ΙL</sub> | -15 | _   | μΑ   | 3      |

Note:

<sup>1</sup>  $LV_{DD}$  supports eTSECs 1 and 2.

$^{2}$  TV<sub>DD</sub> supports eTSECs 3 and 4 or FEC.

$^3$  Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII and RTBI are presented in this section.

# 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, because they have similar performance and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back on the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source-synchronous timing reference. Typically, the clock edge that launched the data can be used, because the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is a relationship between the maximum FIFO speed and the platform (CCB) frequency. For more information see Section 4.5, "Platform to eTSEC FIFO Restrictions."

Table 25 and Table 26 summarize the FIFO AC specifications.

# Table 25. FIFO Mode Transmit AC Timing Specification

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 2.5V ± 5%

| Parameter/Condition                       | Symbol                              | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK, GTX_CLK clock period <sup>1</sup> | t <sub>FIT</sub>                    | 5.3 | 8.0 | 100 | ns   |

| TX_CLK, GTX_CLK duty cycle                | t <sub>FITH</sub> /t <sub>FIT</sub> | 45  | 50  | 55  | %    |

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

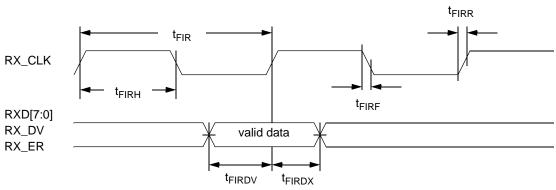

Figure 8. FIFO Receive AC Timing Diagram

# 8.2.2 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

# 8.2.2.1 GMII Transmit AC Timing Specifications

Table 27 provides the GMII transmit AC timing specifications.

## Table 27. GMII Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 2.5/ 3.3 V ± 5%.

| Parameter/Condition                               | Symbol <sup>1</sup> | Min | Тур | Max | Unit |

|---------------------------------------------------|---------------------|-----|-----|-----|------|

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | t <sub>GTKHDV</sub> | 2.5 | _   | _   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | <sup>t</sup> GTKHDX | 0.5 | _   | 5.0 | ns   |

| GTX_CLK data clock rise time (20%-80%)            | t <sub>GTXR</sub> 2 | _   | _   | 1.0 | ns   |

| GTX_CLK data clock fall time (80%-20%)            | $t_{GTXF}^2$        |     | 1   | 1.0 | ns   |

#### Notes:

1. The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

described in Section 21.5, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

When operating in SGMII mode, the eTSEC EC\_GTX\_CLK125 clock is not required for this port. Instead, SerDes reference clock is required on SD2\_REF\_CLK and SD2\_REF\_CLK pins.

# 8.3.1 DC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 15, "High-Speed Serial Interfaces (HSSI)."

# 8.3.2 AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

Table 37 lists the SGMII SerDes reference clock AC requirements. Note that SD2\_REF\_CLK and SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | _   | 10 (8)  |     | ns    | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles |     |         | 100 | ps    | —     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | —       | 50  | ps    | —     |

# Table 37. SD2\_REF\_CLK and SD2\_REF\_CLK AC Requirements

Note:

1.8 ns applies only when 125 MHz SerDes2 reference clock frequency is selected through cfg\_srds\_sgmii\_refclk during POR.

# 10 Local Bus Controller (eLBC)

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8572E.

# **10.1** Local Bus DC Electrical Characteristics

Table 46 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 3.3 \text{ V}$  DC.

| Parameter                                                                      | Symbol           | Min                    | Мах                    | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------------------------|------|

| Supply voltage 3.3V                                                            | BV <sub>DD</sub> | 3.13                   | 3.47                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 2                      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3                   | 0.8                    | V    |

| Input current<br>( $BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD}$ )         | I <sub>IN</sub>  | —                      | ±5                     | μΑ   |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = −2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  | —                      | 0.2                    | V    |

Table 46. Local Bus DC Electrical Characteristics (3.3 V DC)

#### Note:

1. Note that the symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

Table 47 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 2.5 V DC$ .

Table 47. Local Bus DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                    | Symbol           | Min       | Мах                    | Unit |

|------------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5V                                                          | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level input voltage                                                     | V <sub>IH</sub>  | 1.70      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                      | V <sub>IL</sub>  | -0.3      | 0.7                    | V    |

| Input current                                                                | I <sub>IH</sub>  | _         | 10                     | μΑ   |

| $(BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD})$                          | ۱ <sub>IL</sub>  |           | -15                    |      |

| High-level output voltage<br>( $BV_{DD} = min, I_{OH} = -1 mA$ )             | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 1 mA) | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

JTAG

# Table 53. JTAG AC Timing Specifications (Independent of SYSCLK) <sup>1</sup> (continued)

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 5%.

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min    | Max     | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|--------|---------|------|-------|

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 3<br>3 | 19<br>9 | ns   | 5, 6  |

Notes:

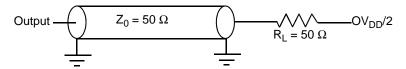

All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 36). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to  $t_{TCLK}$ .

- 6. Guaranteed by design.

Figure 36 provides the AC test load for TDO and the boundary-scan outputs.

Figure 36. AC Test Load for the JTAG Interface

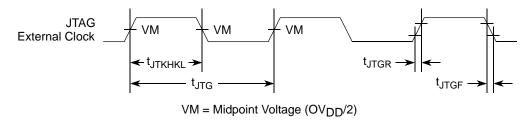

Figure 37 provides the JTAG clock input timing diagram.

Figure 37. JTAG Clock Input Timing Diagram

Figure 38 provides the  $\overline{\text{TRST}}$  timing diagram.

#### High-Speed Serial Interfaces (HSSI)

clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

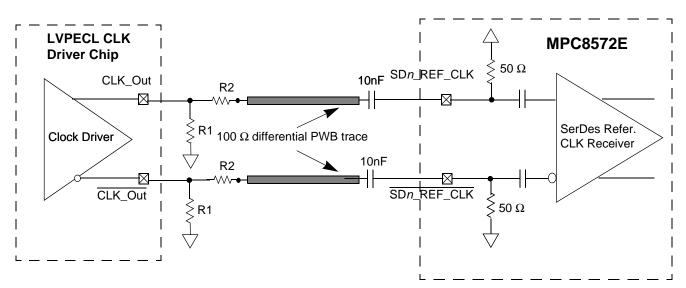

Figure 50. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

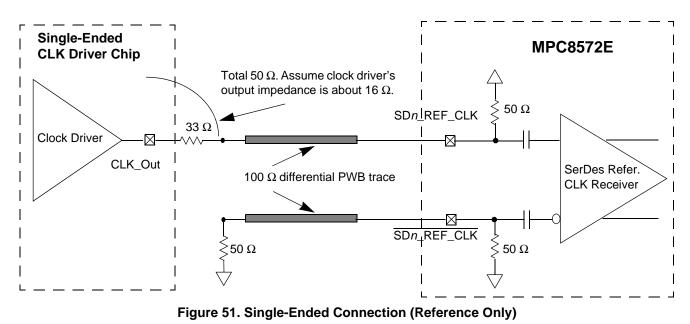

Figure 51 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with MPC8572E SerDes reference clock input's DC requirement.

# 15.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100KHz can be tracked by the PLL and data recovery loops and

## Table 66. Short Run Transmitter AC Timing Specifications—2.5 GBaud (continued)

| Characteristic       | Symbol          | Ra  | nge  | Unit | Notes                                                                  |

|----------------------|-----------------|-----|------|------|------------------------------------------------------------------------|

| Characteristic       | Symbol          | Min | Мах  | Onic | NOICS                                                                  |

| Multiple Output skew | S <sub>MO</sub> | _   | 1000 | -    | Skew at the transmitter output<br>between lanes of a multilane<br>link |

| Unit Interval        | UI              | 400 | 400  | ps   | +/- 100 ppm                                                            |

# Table 67. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

|                             | Symbol              | Min   | Мах  | Onic   | NOICS                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | —                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | —                                                                                |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | _                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 320   | 320  | ps     | +/– 100 ppm                                                                      |

# Table 68. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Мах  |        | NOLES                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | —                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                                |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 800   | 800  | ps     | +/- 100 ppm                                                                      |

Package Description

# Table 76. MPC8572E Pinout Listing (continued)

| Signal                            | Signal Name                   | Package Pin Number                                   | Pin Type | Power<br>Supply  | Notes   |

|-----------------------------------|-------------------------------|------------------------------------------------------|----------|------------------|---------|

| IRQ_OUT                           | Interrupt Output              | U24                                                  | 0        | OV <sub>DD</sub> | 2, 4    |

|                                   | 1588                          | 3                                                    |          |                  |         |

| TSEC_1588_CLK                     | Clock In                      | AM22                                                 | I        | LV <sub>DD</sub> |         |

| TSEC_1588_TRIG_IN                 | Trigger In                    | AM23                                                 | I        | LV <sub>DD</sub> | _       |

| TSEC_1588_TRIG_OUT                | Trigger Out                   | AA23                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| TSEC_1588_CLK_OUT                 | Clock Out                     | AC23                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| TSEC_1588_PULSE_OUT1              | Pulse Out1                    | AA22                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| TSEC_1588_PULSE_OUT2              | Pulse Out2                    | AB23                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

|                                   | Ethernet Managem              | ent Interface 1                                      |          |                  |         |

| EC1_MDC                           | Management Data Clock         | AL30                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| EC1_MDIO                          | Management Data In/Out        | AM25                                                 | I/O      | LV <sub>DD</sub> |         |

|                                   | Ethernet Managem              | ent Interface 3                                      |          |                  |         |

| EC3_MDC                           | Management Data Clock         | AF19                                                 | 0        | TV <sub>DD</sub> | 5, 9    |

| EC3_MDIO                          | Management Data In/Out        | AF18                                                 | I/O      | TV <sub>DD</sub> |         |

|                                   | Ethernet Managem              | ent Interface 5                                      |          |                  |         |

| EC5_MDC                           | Management Data Clock         | AF14                                                 | 0        | TV <sub>DD</sub> | 21      |

| EC5_MDIO                          | Management Data In/Out        | AF15                                                 | I/O      | TV <sub>DD</sub> |         |

|                                   | Gigabit Ethernet R            | eference Clock                                       |          |                  |         |

| EC_GTX_CLK125                     | Reference Clock               | AM24                                                 | Ι        | LV <sub>DD</sub> | 32      |

|                                   | Three-Speed Ether             | net Controller 1                                     |          |                  |         |

| TSEC1_RXD[7:0]/FIFO1_RXD[<br>7:0] | Receive Data                  | AM28, AL28, AM26,<br>AK23, AM27, AK26,<br>AL29, AM30 | I        | LV <sub>DD</sub> | 1       |

| TSEC1_TXD[7:0]/FIFO1_TXD[<br>7:0] | Transmit Data                 | AC20, AD20, AE22,<br>AB22, AC22, AD21,<br>AB21, AE21 | 0        | LV <sub>DD</sub> | 1, 5, 9 |

| TSEC1_COL/FIFO1_TX_FC             | Collision Detect/Flow Control | AJ23                                                 | Ι        | LV <sub>DD</sub> | 1       |

| TSEC1_CRS/FIFO1_RX_FC             | Carrier Sense/Flow Control    | AM31                                                 | I/O      | LV <sub>DD</sub> | 1, 16   |

| TSEC1_GTX_CLK                     | Transmit Clock Out            | AK27                                                 | 0        | LV <sub>DD</sub> |         |

| TSEC1_RX_CLK/FIFO1_RX_C<br>LK     | Receive Clock                 | AL25                                                 | I        | LV <sub>DD</sub> | 1       |

|                                                   |                               |                                                      |          | Power            |             |

|---------------------------------------------------|-------------------------------|------------------------------------------------------|----------|------------------|-------------|

| Signal                                            | Signal Name                   | Package Pin Number                                   | Pin Type | Supply           | Notes       |

| TSEC1_RX_DV/FIFO1_RX_D<br>V/FIFO1_RXC[0]          | Receive Data Valid            | AL24                                                 | I        | LV <sub>DD</sub> | 1           |

| TSEC1_RX_ER/FIFO1_RX_E<br>R/FIFO1_RXC[1]          | Receive Data Error            | AM29                                                 | I        | LV <sub>DD</sub> | 1           |

| TSEC1_TX_CLK/FIFO1_TX_C<br>LK                     | Transmit Clock In             | AB20                                                 | I        | LV <sub>DD</sub> | 1           |

| TSEC1_TX_EN/FIFO1_TX_EN<br>/FIFO1_TXC[0]          | Transmit Enable               | AJ24                                                 | 0        | LV <sub>DD</sub> | 1, 22       |

| TSEC1_TX_ER/FIFO1_TX_ER<br>R/FIFO1_TXC[1]         | Transmit Error                | AK25                                                 | 0        | LV <sub>DD</sub> | 1, 5, 9     |

|                                                   | Three-Speed Ether             | net Controller 2                                     |          |                  |             |

| TSEC2_RXD[7:0]/FIFO2_RXD[<br>7:0]/FIFO1_RXD[15:8] | Receive Data                  | AG22, AH20, AL22,<br>AG20, AK21, AK22,<br>AJ21, AK20 | I        | LV <sub>DD</sub> | 1           |

| TSEC2_TXD[7:0]/FIFO2_TXD[<br>7:0]/FIFO1_TXD[15:8] | Transmit Data                 | AH21, AF20, AC17,<br>AF21, AD18, AF22,<br>AE20, AB18 | 0        | LV <sub>DD</sub> | 1, 5, 9, 24 |

| TSEC2_COL/FIFO2_TX_FC                             | Collision Detect/Flow Control | AE19                                                 | Ι        | LV <sub>DD</sub> | 1           |

| TSEC2_CRS/FIFO2_RX_FC                             | Carrier Sense/Flow Control    | AJ20                                                 | I/O      | LV <sub>DD</sub> | 1, 16       |

| TSEC2_GTX_CLK                                     | Transmit Clock Out            | AE18                                                 | 0        | LV <sub>DD</sub> | —           |

| TSEC2_RX_CLK/FIFO2_RX_C<br>LK                     | Receive Clock                 | AL23                                                 | I        | LV <sub>DD</sub> | 1           |

| TSEC2_RX_DV/FIFO2_RX_D<br>V/FIFO1_RXC[2]          | Receive Data Valid            | AJ22                                                 | I        | LV <sub>DD</sub> | 1           |

| TSEC2_RX_ER/FIFO2_RX_E<br>R                       | Receive Data Error            | AD19                                                 | I        | LV <sub>DD</sub> | 1           |

| TSEC2_TX_CLK/FIFO2_TX_C<br>LK                     | Transmit Clock In             | AC19                                                 | I        | LV <sub>DD</sub> | 1           |

| TSEC2_TX_EN/FIFO2_TX_EN<br>/FIFO1_TXC[2]          | Transmit Enable               | AB19                                                 | 0        | LV <sub>DD</sub> | 1, 22       |

| TSEC2_TX_ER/FIFO2_TX_ER<br>R                      | Transmit Error                | AB17                                                 | 0        | LV <sub>DD</sub> | 1, 5, 9     |

|                                                   | Three-Speed Ethern            | net Controller 3                                     |          |                  |             |

| TSEC3_TXD[3:0]/FEC_TXD[3:<br>0]/FIFO3_TXD[3:0]    | Transmit Data                 | AG18, AG17, AH17,<br>AH19                            | 0        | TV <sub>DD</sub> | 1, 5, 9     |

| TSEC3_RXD[3:0]/FEC_RXD[3:<br>0]/FIFO3_RXD[3:0]    | Receive Data                  | AG16, AK19, AD16,<br>AJ19                            | Ι        | TV <sub>DD</sub> | 1           |

| Table 76. MPC8572E Pinout Listing (continued) |

|-----------------------------------------------|

|-----------------------------------------------|

| Signal           | Signal Name                 | Package Pin Number | Pin Type | Power<br>Supply  | Notes     |  |  |

|------------------|-----------------------------|--------------------|----------|------------------|-----------|--|--|

| MSRCID[0:1]      | Memory Debug Source Port ID | U27, T29           | 0        | OV <sub>DD</sub> | 5, 9, 30  |  |  |

| MSRCID[2:4]      | Memory Debug Source Port ID | U28, W24, W28      | 0        | OV <sub>DD</sub> | 21        |  |  |

| MDVAL            | Memory Debug Data Valid     | V26                | 0        | OV <sub>DD</sub> | 2, 21     |  |  |

| CLK_OUT          | Clock Out                   | U32                | 0        | OV <sub>DD</sub> | 11        |  |  |

|                  | Clock                       | κ                  |          |                  |           |  |  |

| RTC              | Real Time Clock             | V25                | I        | OV <sub>DD</sub> | —         |  |  |

| SYSCLK           | System Clock                | Y32                | I        | OV <sub>DD</sub> | —         |  |  |

| DDRCLK           | DDR Clock                   | AA29               | I        | OV <sub>DD</sub> | 31        |  |  |

| JTAG             |                             |                    |          |                  |           |  |  |

| тск              | Test Clock                  | T28                | I        | OV <sub>DD</sub> |           |  |  |

| TDI              | Test Data In                | T27                | I        | OV <sub>DD</sub> | 12        |  |  |

| TDO              | Test Data Out               | T26                | 0        | OV <sub>DD</sub> | —         |  |  |

| TMS              | Test Mode Select            | U26                | I        | OV <sub>DD</sub> | 12        |  |  |

| TRST             | Test Reset                  | AA32               | I        | OV <sub>DD</sub> | 12        |  |  |

| DFT              |                             |                    |          |                  |           |  |  |

| L1_TSTCLK        | L1 Test Clock               | V32                | I        | OV <sub>DD</sub> | 18        |  |  |

| L2_TSTCLK        | L2 Test Clock               | V31                | I        | OV <sub>DD</sub> | 18        |  |  |

| LSSD_MODE        | LSSD Mode                   | N24                | I        | OV <sub>DD</sub> | 18        |  |  |

| TEST_SEL         | Test Select 0               | K28                | I        | OV <sub>DD</sub> | 18        |  |  |

| Power Management |                             |                    |          |                  |           |  |  |

| ASLEEP           | Asleep                      | P28                | 0        | OV <sub>DD</sub> | 9, 15, 21 |  |  |

Package Description

| Signal     | Signal Name                             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Type | Power<br>Supply | Notes |  |  |

|------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|-------|--|--|

|            | Power and Ground Signals                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                 |       |  |  |

| GND        | Ground                                  | A18, A25, A29, C3, C6,<br>C9, C12, C15, C20,<br>C22, E5, E8, E11, E14,<br>F3, G7, G10, G13,<br>G16, H5, H21, J3, J9,<br>J12, J18, K7, L5, L13,<br>L15, L16, L21, M3, M9,<br>M12, M14, M16, M18,<br>N7, N13, N15, N17,<br>N19, N21, N23, P5,<br>P12, P14, P16, P20,<br>P22, R3, R9, R11, R13,<br>R15, R17, R19, R21,<br>R23, R26, T7, T12,<br>T14, T16, T18, T20,<br>T22, T30, U5, U11,<br>U13, U15, U16, U17,<br>U19, U21, U23, U25,<br>V3, V9, V12, V14, V16,<br>V18, V20, V22, W7,<br>W11, W13, W15, W17,<br>W19, W21, W27, W32,<br>Y5, Y12, Y14, Y16,<br>Y18, Y20, AA3, AA9,<br>AA13, AA15, AA17,<br>AA19, AA21, AA30,<br>AB7, AB26, AC5,<br>AC11, AC13, AD3,<br>AD9, AD14, AD17,<br>AD22, AE7, AE13,<br>AF5, AF11, AG3, AG9,<br>AG15, AG19, AH7,<br>AH13, AH22, AJ5,<br>AJ11, AJ17, AK3, AK9,<br>AK15, AK24, AL7,<br>AL13, AL19, AL26 |          |                 |       |  |  |

| XGND_SRDS1 | SerDes Transceiver Pad GND<br>(xpadvss) | C23, C27, D23, D25,<br>E23, E26, F23, F24,<br>G23, G27, H23, H25,<br>J23, J26, K23, K24,<br>L27, M25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —        |                 | —     |  |  |

| XGND_SRDS2 | SerDes Transceiver Pad GND<br>(xpadvss) | AD23, AD25, AE23,<br>AE27, AF23, AF24,<br>AG23, AG26, AH23,<br>AH25, AJ27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | _               |       |  |  |

# Table 76. MPC8572E Pinout Listing (continued)

| Signal     | Signal Name                                     | Package Pin Number                                                                                                                                                                                                                                                                                                                                            | Pin Type | Power<br>Supply | Notes |

|------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|-------|

| SGND_SRDS1 | SerDes Transceiver Core Logic<br>GND (xcorevss) | C28, C32, D30, E31,<br>F28, F29, G32, H28,<br>H30, J28, K29, L32,<br>M30, N31, P29, R32                                                                                                                                                                                                                                                                       | _        | _               | _     |

| SGND_SRDS2 | SerDes Transceiver Core Logic<br>GND (xcorevss) | AE28, AE30, AF28,<br>AF32, AG28, AG30,<br>AH28, AJ28, AJ31,<br>AL32                                                                                                                                                                                                                                                                                           | _        | _               |       |

| AGND_SRDS1 | SerDes PLL GND                                  | J31                                                                                                                                                                                                                                                                                                                                                           | —        | —               | _     |

| AGND_SRDS2 | SerDes PLL GND                                  | AH31                                                                                                                                                                                                                                                                                                                                                          | —        | —               | _     |

| OVDD       | General I/O Supply                              | U31, V24, V28, Y31,<br>AA27, AB25, AB29                                                                                                                                                                                                                                                                                                                       | —        | OVDD            | _     |

| LVDD       | TSEC 1&2 I/O Supply                             | AC18, AC21, AG21,<br>AL27                                                                                                                                                                                                                                                                                                                                     | —        | LVDD            | _     |

| TVDD       | TSEC 3&4 I/O Supply                             | AC15, AE16, AH18                                                                                                                                                                                                                                                                                                                                              | —        | TVDD            | _     |

| GVDD       | SSTL_1.8 DDR Supply                             | B2, B5, B8, B11, B14,<br>D4, D7, D10, D13, E2,<br>F6, F9, F12, G4, H2,<br>H8, H11, H14, J6, K4,<br>K10, K13, L2, L8, M6,<br>N4, N10, P2, P8, R6,<br>T4, T10, U2, U8, V6,<br>W4, W10, Y2, Y8, AA6,<br>AB4, AB10, AC2, AC8,<br>AD6, AD12, AE4,<br>AE10, AF2, AF8, AG6,<br>AG12, AH4, AH10,<br>AH16, AJ2, AJ8, AJ14,<br>AK6, AK12, AK18, AL4,<br>AL10, AL16, AM2 |          | GVDD            | _     |

| BVDD       | Local Bus and GPIO Supply                       | A26, A30, B21, D16,<br>D21, F18, G20, H17,<br>J22, K15, K20                                                                                                                                                                                                                                                                                                   | —        | BVDD            | _     |

Clocking

| Binary Value of LA[29:31] Signals | CCB:SYSCLK Ratio |  |  |

|-----------------------------------|------------------|--|--|

| 000                               | 4:1              |  |  |

| 001                               | 5:1              |  |  |

| 010                               | 6:1              |  |  |

| 011                               | 8:1              |  |  |

| 100                               | 10:1             |  |  |

| 101                               | 12:1             |  |  |

| 110                               | Reserved         |  |  |

| 111                               | Reserved         |  |  |

## Table 79. CCB Clock Ratio

# 19.3 e500 Core PLL Ratio

The clock speed for each e500 core can be configured differently, determined by the values of various signals at power up.

Table 80 describes the clock ratio between e500 Core0 and the e500 core complex bus (CCB). This ratio is determined by the binary value of LBCTL, LALE and LGPL2/LOE/LFRE at power up, as shown in Table 80.

| Binary Value of<br>LBCT <u>L, LALE,</u><br>LGPL2/LOE/LFRE<br>Signals | e500 Core0:CCB Clock Ratio | Binary Value of<br>LBCT <u>L, LALE,</u><br>LGPL2/LOE/LFRE<br>Signals | e500 Core0:CCB Clock Ratio |

|----------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------|----------------------------|

| 000                                                                  | Reserved                   | 100                                                                  | 2:1                        |

| 001                                                                  | Reserved                   | 101                                                                  | 5:2 (2.5:1)                |

| 010                                                                  | Reserved                   | 110                                                                  | 3:1                        |

| 011                                                                  | 3:2 (1.5:1)                | 111                                                                  | 7:2 (3.5:1)                |

## Table 80. e500 Core0 to CCB Clock Ratio

System Design Information

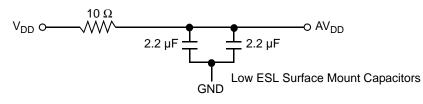

Figure 62 shows the PLL power supply filter circuits.

Figure 62. PLL Power Supply Filter Circuit

# NOTE

It is recommended to have the minimum number of vias in the  $AV_{DD}$  trace for board layout. For example, zero vias might be possible if the  $AV_{DD}$  filter is placed on the component side. One via might be possible if it is placed on the opposite of the component side. Additionally, all traces for  $AV_{DD}$  and the filter components should be low impedance, 10 to 15 mils wide and short. This includes traces going to GND and the supply rails they are filtering.

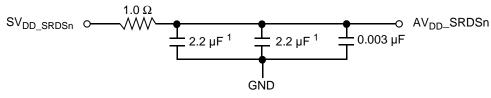

The AV<sub>DD</sub>\_SRDSn signal provides power for the analog portions of the SerDesn PLL. To ensure stability of the internal clock, the power supplied to the PLL is filtered using a circuit similar to the one shown in following figure. For maximum effectiveness, the filter circuit is placed as closely as possible to the AV<sub>DD</sub>\_SRDSn ball to ensure it filters out as much noise as possible. The ground connection should be near the AV<sub>DD</sub>\_SRDSn ball. The 0.003- $\mu$ F capacitor is closest to the ball, followed by the two 2.2  $\mu$ F capacitors, and finally the 1  $\Omega$  resistor to the board supply plane. The capacitors are connected from AV<sub>DD</sub>\_SRDSn to the ground plane. Use ceramic chip capacitors with the highest possible self-resonant frequency. All traces should be kept short, wide and direct.

1. An 0805 sized capacitor is recommended for system initial bring-up.

Figure 63. SerDes PLL Power Supply Filter

# NOTE

AV<sub>DD</sub>\_SRDSn should be a filtered version of SV<sub>DD</sub>\_SRDSn.

# NOTE

Signals on the SerDesn interface are fed from the  $XV_{DD}$ -SRDS*n* power plane.

# 21.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads.

System Design Information

#### Notes:

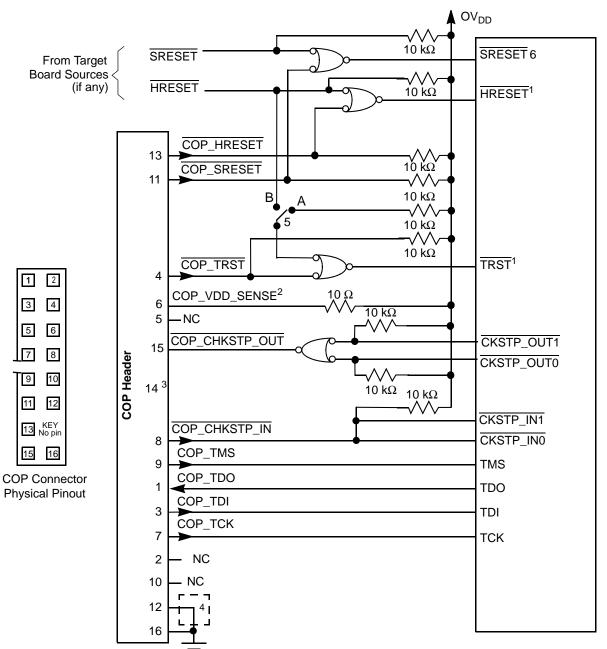

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor to fully control the processor as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- 5. This switch is included as a precaution for BSDL testing. The switch should be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed to position B.

- 6. Asserting SRESET causes a machine check interrupt to the e500 cores.