# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.333GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                   |

| RAM Controllers                 | DDR2, DDR3                                                              |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                  |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | Cryptography, Random Number Generator                                   |

| Package / Case                  | 1023-BFBGA, FCBGA                                                       |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572elvtaule |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

- Ability to launch DMA from single write transaction

- Serial RapidIO interface unit

- Supports RapidIO Interconnect Specification, Revision 1.2

- Both 1x and 4x LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto-detection of 1x- and 4x-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO–compliant message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

- Single inbound doorbell message structure

- Facility to accept port-write messages

# 4 Input Clocks

## 4.1 System Clock Timing

Table 6 provides the system clock (SYSCLK) AC timing specifications for the MPC8572E.

### Table 6. SYSCLK AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition       | Symbol                                | Min | Typical | Мах     | Unit | Notes   |

|---------------------------|---------------------------------------|-----|---------|---------|------|---------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 33  | —       | 133     | MHz  | 1       |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                   | 7.5 | —       | 30.3    | ns   | —       |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 1.2     | ns   | 2       |

| SYSCLK duty cycle         | t <sub>KHK</sub> /t <sub>SYSCLK</sub> | 40  | —       | 60      | %    | 3       |

| SYSCLK jitter             | —                                     | —   | —       | +/- 150 | ps   | 4, 5, 6 |

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies.Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on SYSCLK.

## 4.2 Real Time Clock Timing

The RTC input is sampled by the platform clock (CCB clock). The output of the sampling latch is then used as an input to the counters of the PIC and the TimeBase unit of the e500. There is no jitter specification. The minimum pulse width of the RTC signal should be greater than 2x the period of the CCB clock. That is, minimum clock high time is  $2 \times t_{CCB}$ , and minimum clock low time is  $2 \times t_{CCB}$ . There is no minimum RTC frequency; RTC may be grounded if not needed.

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

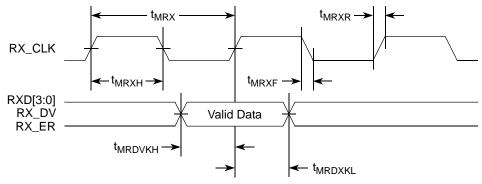

Figure 14 shows the MII receive AC timing diagram.

Figure 14. MII Receive AC Timing Diagram

## 8.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

## 8.2.4.1 TBI Transmit AC Timing Specifications

Table 31 provides the TBI transmit AC timing specifications.

### Table 31. TBI Transmit AC Timing Specifications

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>            | Min | Тур | Мах | Unit |

|--------------------------------------------|--------------------------------|-----|-----|-----|------|

| TCG[9:0] setup time GTX_CLK going high     | t <sub>TTKHDV</sub>            | 2.0 | _   | _   | ns   |

| TCG[9:0] hold time from GTX_CLK going high | t <sub>TTKHDX</sub>            | 1.0 | _   | _   | ns   |

| GTX_CLK rise (20%-80%)                     | t <sub>TTXR</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

| GTX_CLK fall time (80%–20%)                | t <sub>TTXF</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

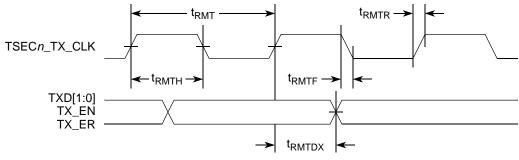

### Table 35. RMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup> | Min | Тур | Мах  | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|------|

| TSECn_TX_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 1.0 |     | 10.0 | ns   |

Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

Figure 19 shows the RMII transmit AC timing diagram.

Figure 19. RMII Transmit AC Timing Diagram

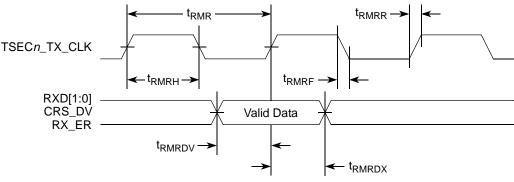

## 8.2.7.2 RMII Receive AC Timing Specifications

Table 36 shows the RMII receive AC timing specifications.

### Table 36. RMII Receive AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                                               | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period                                         | t <sub>RMR</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_TX_CLK duty cycle                                           | t <sub>RMRH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter                                  | t <sub>RMRJ</sub>   | —    | —    | 250  | ps   |

| Rise time TSECn_TX_CLK (20%-80%)                                  | t <sub>RMRR</sub>   | 1.0  | —    | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%–20%)                                  | t <sub>RMRF</sub>   | 1.0  | —    | 2.0  | ns   |

| RXD[1:0], CRS_DV, RX_ER setup time to<br>TSECn_TX_CLK rising edge | t <sub>RMRDV</sub>  | 4.0  | -    | —    | ns   |

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

### Table 36. RMII Receive AC Timing Specifications (continued)

At recommended operating conditions with LV\_DD/TV\_DD of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                                              | Symbol <sup>1</sup> | Min | Тур | Мах | Unit |

|------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| RXD[1:0], CRS_DV, RX_ER hold time to<br>TSECn_TX_CLK rising edge | t <sub>RMRDX</sub>  | 2.0 | —   |     | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

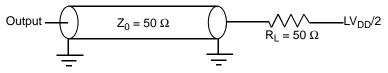

Figure 20 provides the AC test load for eTSEC.

Figure 20. eTSEC AC Test Load

Figure 21 shows the RMII receive AC timing diagram.

Figure 21. RMII Receive AC Timing Diagram

## 8.3 SGMII Interface Electrical Characteristics

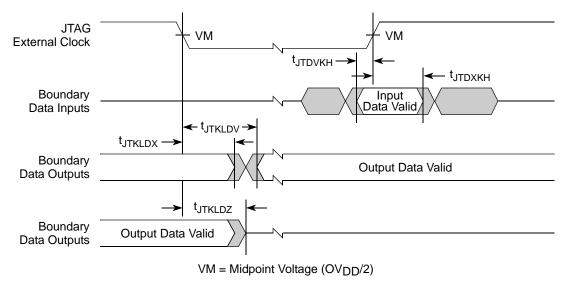

Each SGMII port features a 4-wire AC-Coupled serial link from the dedicated SerDes 2 interface of MPC8572E as shown in Figure 22, where  $C_{TX}$  is the external (on board) AC-Coupled capacitor. Each output pin of the SerDes transmitter differential pair features 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to SGND\_SRDS2 (xcorevss). The reference circuit of the SerDes transmitter and receiver is shown in Figure 54.

When an eTSEC port is configured to operate in SGMII mode, the parallel interface's output signals of this eTSEC port can be left floating. The input signals should be terminated based on the guidelines

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

## 8.3.3 SGMII Transmitter and Receiver DC Electrical Characteristics

Table 38 and Table 39 describe the SGMII SerDes transmitter and receiver AC-Coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs (SD2\_TX[n] and SD2\_TX[n]) as depicted in Figure 23.

| Parameter                                                 | Symbol            | Min                                                                      | Тур | Max                                                                      | Unit | Notes                       |

|-----------------------------------------------------------|-------------------|--------------------------------------------------------------------------|-----|--------------------------------------------------------------------------|------|-----------------------------|

| Supply Voltage                                            | $XV_{DD\_SRDS2}$  | 1.045                                                                    | 1.1 | 1.155                                                                    | V    | —                           |

| Output high voltage                                       | VOH               | —                                                                        | _   | XV <sub>DD_SRDS2-Typ</sub> /2<br>+  V <sub>OD</sub>   <sub>-max</sub> /2 | mV   | 1                           |

| Output low voltage                                        | VOL               | XV <sub>DD_SRDS2-Typ</sub> /2<br>-  V <sub>OD</sub>   <sub>-max</sub> /2 | _   | _                                                                        | mV   | 1                           |

| Output ringing                                            | V <sub>RING</sub> | —                                                                        | _   | 10                                                                       | %    | —                           |

|                                                           |                   | 359                                                                      | 550 | 791                                                                      |      | Equalization setting: 1.0x  |

|                                                           |                   | 329                                                                      | 505 | 725                                                                      |      | Equalization setting: 1.09x |

| 235                                                       | V <sub>OD</sub>   | 299                                                                      | 458 | 659                                                                      | mV   | Equalization setting: 1.2x  |

| Output differential voltage <sup>2, 3, 5</sup>            |                   | 270                                                                      | 414 | 594                                                                      |      | Equalization setting: 1.33x |

|                                                           |                   | 239                                                                      | 367 | 527                                                                      |      | Equalization setting: 1.5x  |

|                                                           |                   | 210                                                                      | 322 | 462                                                                      |      | Equalization setting: 1.71x |

|                                                           |                   | 180                                                                      | 275 | 395                                                                      |      | Equalization setting: 2.0x  |

| Output offset voltage                                     | V <sub>OS</sub>   | 473                                                                      | 550 | 628                                                                      | mV   | 1, 4                        |

| Output impedance (single-ended)                           | R <sub>O</sub>    | 40                                                                       | _   | 60                                                                       | Ω    | —                           |

| Mismatch in a pair                                        | $\Delta R_{O}$    | —                                                                        | _   | 10                                                                       | %    | —                           |

| Change in $V_{\mbox{\scriptsize OD}}$ between "0" and "1" | $\Delta  V_{OD} $ | _                                                                        |     | 25                                                                       | mV   | —                           |

### Table 38. SGMII DC Transmitter Electrical Characteristics

## 8.3.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs ( $SD2_TX[n]$  and  $\overline{SD2_TX[n]}$ ) or at the receiver inputs ( $SD2_RX[n]$  and  $\overline{SD2_RX[n]}$ ) as depicted in Figure 25, respectively.

## 8.3.4.1 SGMII Transmit AC Timing Specifications

Table 40 provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

### Table 40. SGMII Transmit AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2}$  = 1.1V ± 5%.

| Parameter                           | Symbol            | Min    | Тур | Max    | Unit   | Notes |

|-------------------------------------|-------------------|--------|-----|--------|--------|-------|

| Deterministic Jitter                | JD                | —      | _   | 0.17   | UI p-p | _     |

| Total Jitter                        | JT                | —      | _   | 0.35   | UI p-p | _     |

| Unit Interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1     |

| V <sub>OD</sub> fall time (80%-20%) | tfall             | 50     | _   | 120    | ps     | _     |

| V <sub>OD</sub> rise time (20%-80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     | _     |

Notes:

1. Each UI is 800 ps  $\pm$  100 ppm.

## 8.3.4.2 SGMII Receive AC Timing Specifications

Table 41 provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 24 shows the SGMII receiver input compliance mask eye diagram.

### Table 41. SGMII Receive AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2} = 1.1V \pm 5\%$ .

| Parameter                                          | Symbol          | Min    | Тур | Max               | Unit   | Notes |

|----------------------------------------------------|-----------------|--------|-----|-------------------|--------|-------|

| Deterministic Jitter Tolerance                     | JD              | 0.37   | —   | —                 | UI p-p | 1     |

| Combined Deterministic and Random Jitter Tolerance | JDR             | 0.55   | —   | _                 | UI p-p | 1     |

| Sinusoidal Jitter Tolerance                        | JSIN            | 0.1    | —   | —                 | UI p-p | 1     |

| Total Jitter Tolerance                             | JT              | 0.65   |     | _                 | UI p-p | 1     |

| Bit Error Ratio                                    | BER             | _      | —   | 10 <sup>-12</sup> |        | _     |

| Unit Interval                                      | UI              | 799.92 | 800 | 800.08            | ps     | 2     |

| AC Coupling Capacitor                              | C <sub>TX</sub> | 5      | —   | 200               | nF     | 3     |

Notes:

1. Measured at receiver.

2. Each UI is 800 ps  $\pm$  100 ppm.

3. The external AC coupling capacitor is required. It is recommended to be placed near the device transmitter outputs.

4. See RapidIO 1x/4x LP Serial Physical Layer Specification for interpretation of jitter specifications.

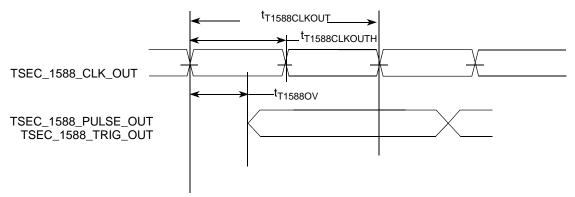

## 8.4 eTSEC IEEE Std 1588<sup>™</sup> AC Specifications

Figure 26 shows the data and command output timing diagram.

Figure 26. eTSEC IEEE 1588 Output AC Timing

<sup>1</sup> The output delay is count starting rising edge if t<sub>T1588CLKOUT</sub> is non-inverting. Otherwise, it is count starting falling edge.

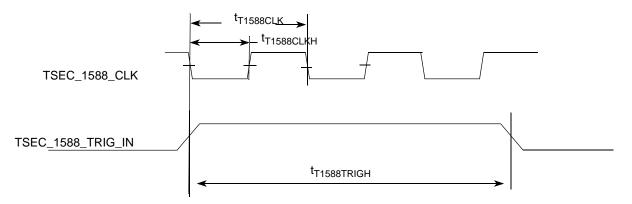

Figure 27 shows the data and command input timing diagram.

## Table 42 provides the IEEE 1588 AC timing specifications.

## Table 42. eTSEC IEEE 1588 AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%

| Parameter/Condition                | Symbol                                             | Min                     | Тур | Max                    | Unit | Note |

|------------------------------------|----------------------------------------------------|-------------------------|-----|------------------------|------|------|

| TSEC_1588_CLK clock period         | t <sub>T1588CLK</sub>                              | 3.3                     | —   | T <sub>TX_CLK</sub> *9 | ns   | 1    |

| TSEC_1588_CLK duty cycle           | t <sub>T1588</sub> CLKH<br>/t <sub>T1588</sub> CLK | 40                      | 50  | 60                     | %    | —    |

| TSEC_1588_CLK peak-to-peak jitter  | t <sub>T1588CLKINJ</sub>                           | —                       | —   | 250                    | ps   | —    |

| Rise time eTSEC_1588_CLK (20%-80%) | t <sub>T1588CLKINR</sub>                           | 1.0                     | —   | 2.0                    | ns   | —    |

| Fall time eTSEC_1588_CLK (80%-20%) | t <sub>T1588CLKINF</sub>                           | 1.0                     | —   | 2.0                    | ns   | —    |

| TSEC_1588_CLK_OUT clock period     | t <sub>T1588CLKOUT</sub>                           | 2*t <sub>T1588CLK</sub> | —   | _                      | ns   | —    |

### MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

NXP Semiconductors

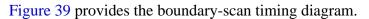

Figure 39. Boundary-Scan Timing Diagram

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the MPC8572E.

## 13.1 I<sup>2</sup>C DC Electrical Characteristics

Table 54 provides the DC electrical characteristics for the  $I^2C$  interfaces.

| Table 54. I <sup>2</sup> C DC Electrical Characteristic | ;S |

|---------------------------------------------------------|----|

|---------------------------------------------------------|----|

| Parameter                                                                                                | Symbol              | Min                                | Мах                    | Unit | Notes |

|----------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------|------|-------|

| Input high voltage level                                                                                 | V <sub>IH</sub>     | $0.7 \times \text{OV}_{\text{DD}}$ | OV <sub>DD</sub> + 0.3 | V    | —     |

| Input low voltage level                                                                                  | V <sub>IL</sub>     | -0.3                               | $0.3 	imes OV_{DD}$    | V    | —     |

| Low level output voltage                                                                                 | V <sub>OL</sub>     | 0                                  | 0.4                    | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>I2KHKL</sub> | 0                                  | 50                     | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | Ι <sub>Ι</sub>      | -10                                | 10                     | μA   | 3     |

High-Speed Serial Interfaces (HSSI)

# 15 High-Speed Serial Interfaces (HSSI)

The MPC8572E features two Serializer/Deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. The SerDes1 interface can be used for PCI Express and/or Serial RapidIO data transfers. The SerDes2 is dedicated for SGMII application.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

## 15.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 43 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SDn\_TX and SDn\_TX) or a receiver input (SDn\_RX and  $\overline{SDn_RX}$ ). Each signal swings between A Volts and B Volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

## 1. Single-Ended Swing

The transmitter output signals and the receiver input signals SDn\_TX, SDn\_TX, SDn\_RX and SDn\_RX each have a peak-to-peak swing of A - B Volts. This is also referred as each signal wire's Single-Ended Swing.

2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn_TX} - V_{\overline{SDn_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

3. Differential Input Voltage, V<sub>ID</sub> (or Differential Input Swing):

The Differential Input Voltage (or Swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{SDn_RX} - V_{\overline{SDn_RX}}$ . The  $V_{ID}$  value can be either positive or negative.

4. Differential Peak Voltage, V<sub>DIFFp</sub>

The peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak Voltage,  $V_{DIFFp} = |A - B|$  Volts.

## 5. Differential Peak-to-Peak, V<sub>DIFFp-p</sub>

Because the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) Volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak-to-Peak Voltage,  $V_{DIFFp-p} = 2*V_{DIFFp} = 2*|(A – B)|$  Volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2*|V_{OD}|$ .

High-Speed Serial Interfaces (HSSI)

SD1\_REF\_CLK for PCI Express and Serial RapidIO, or SD2\_REF\_CLK and SD2\_REF\_CLK for the SGMII interface respectively.

The following sections describe the SerDes reference clock requirements and some application information.

## **15.2.1** SerDes Reference Clock Receiver Characteristics

Figure 44 shows a receiver reference diagram of the SerDes reference clocks. Characteristics are as follows:

- The supply voltage requirements for  $XV_{DD SRDS2}$  are specified in Table 1 and Table 2.

- SerDes Reference Clock Receiver Reference Circuit Structure

- The SDn\_REF\_CLK and SDn\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 44. Each differential clock input (SDn\_REF\_CLK or SDn\_REF\_CLK) has on-chip 50-Ω termination to SGND\_SRDSn (xcorevss) followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. Refer to the Differential Mode and Single-ended Mode description below for further detailed requirements.

- The maximum average current requirement that also determines the common mode voltage range

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA (refer to the following bullet for more detail), because the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V/50 = 8 mA) while the minimum common mode input level is 0.1 V above SGND\_SRDS*n* (xcorevss). For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 mA to 16 mA (0-0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SD*n*\_REF\_CLK and  $\overline{\text{SD}n_\text{REF}\text{-}\text{CLK}}$  inputs cannot drive 50  $\Omega$  to SGND\_SRDS*n* (xcorevss) DC, or it exceeds the maximum input current limitations, then it must be AC-coupled off-chip.

- The input amplitude requirement

- This requirement is described in detail in the following sections.

## 15.2.3 Interfacing With Other Differential Signaling Levels

- With on-chip termination to SGND\_SRDS*n* (xcorevss), the differential reference clocks inputs are HCSL (High-Speed Current Steering Logic) compatible DC-coupled.

- Many other low voltage differential type outputs like LVDS (Low Voltage Differential Signaling) can be used but may need to be AC-coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

- LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, additionally to AC-coupling.

### NOTE

Figure 48 to Figure 51 below are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the MPC8572E SerDes reference clock receiver requirement provided in this document.

PCI Express

| Symbol                                       | Parameter                                                                                    | Min   | Nominal | Max | Units | Comments                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------|----------------------------------------------------------------------------------------------|-------|---------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>RX-EYE-MEDIAN-to-MAX</sub><br>-JITTER | Maximum time<br>between the jitter<br>median and<br>maximum<br>deviation from<br>the median. |       | _       | 0.3 | UI    | Jitter is defined as the measurement<br>variation of the crossing points ( $V_{RX-DIFFp-p}$<br>= 0 V) in relation to a recovered TX UI. A<br>recovered TX UI is calculated over 3500<br>consecutive unit intervals of sample data.<br>Jitter is measured using all edges of the<br>250 consecutive UI in the center of the<br>3500 UI used for calculating the TX UI. See<br>Notes 2, 3 and 7. |

| V <sub>RX-CM-ACp</sub>                       | AC Peak<br>Common Mode<br>Input Voltage                                                      | _     |         | 150 | mV    | $V_{RX-CM-ACp} =  V_{RXD+} + V_{RXD-} /2 - V_{RX-CM-DC} = DC_{(avg)} \text{ of }  V_{RX-D+} + V_{RX-D-} /2$<br>See Note 2                                                                                                                                                                                                                                                                      |

| RL <sub>RX-DIFF</sub>                        | Differential<br>Return Loss                                                                  | 15    |         | _   | dB    | Measured over 50 MHz to 1.25 GHz with<br>the D+ and D- lines biased at +300 mV and<br>-300 mV, respectively.<br>See Note 4                                                                                                                                                                                                                                                                     |

| RL <sub>RX-CM</sub>                          | Common Mode<br>Return Loss                                                                   | 6     | _       | _   | dB    | Measured over 50 MHz to 1.25 GHz with<br>the D+ and D- lines biased at 0 V. See Note<br>4                                                                                                                                                                                                                                                                                                      |

| Z <sub>RX-DIFF-DC</sub>                      | DC Differential<br>Input Impedance                                                           | 80    | 100     | 120 | Ω     | RX DC Differential mode impedance. See Note 5                                                                                                                                                                                                                                                                                                                                                  |

| Z <sub>RX-DC</sub>                           | DC Input<br>Impedance                                                                        | 40    | 50      | 60  | Ω     | Required RX D+ as well as D- DC<br>Impedance (50 $\pm$ 20% tolerance). See<br>Notes 2 and 5.                                                                                                                                                                                                                                                                                                   |

| Z <sub>RX-HIGH-IMP-DC</sub>                  | Powered Down<br>DC Input<br>Impedance                                                        | 200 k | _       | _   | Ω     | Required RX D+ as well as D- DC<br>Impedance when the Receiver terminations<br>do not have power. See Note 6.                                                                                                                                                                                                                                                                                  |

| V <sub>RX-IDLE</sub> -DET-DIFFp-p            | Electrical Idle<br>Detect Threshold                                                          | 65    | _       | 175 | mV    | $V_{RX-IDLE-DET-DIFF_{P}} = 2^*  V_{RX-D+} - V_{RX-D-} $<br>Measured at the package pins of the<br>Receiver                                                                                                                                                                                                                                                                                    |

| T <sub>RX-IDLE-DET-DIFF-</sub><br>ENTERTIME  | Unexpected<br>Electrical Idle<br>Enter Detect<br>Threshold<br>Integration Time               |       |         | 10  | ms    | An unexpected Electrical Idle ( $V_{RX-DIFFp-p} < V_{RX-IDLE-DET-DIFFp-p}$ ) must be recognized<br>no longer than $T_{RX-IDLE-DET-DIFF-ENTERING}$ to signal an unexpected idle condition.                                                                                                                                                                                                      |

## Table 63. Differential Receiver (RX) Input Specifications (continued)

## 16.5.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 57.

## NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

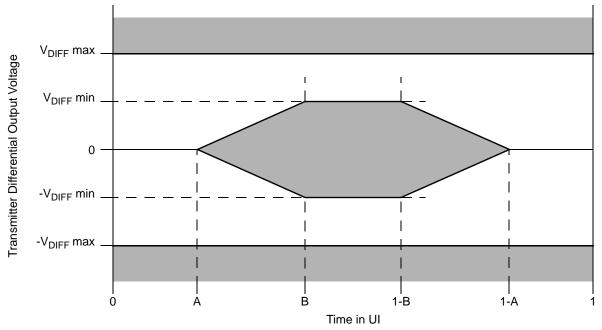

Figure 57. Compliance Test/Measurement Load

## 17 Serial RapidIO

This section describes the DC and AC electrical specifications for the RapidIO interface of the MPC8572E for the LP-Serial physical layer. The electrical specifications cover both single and multiple-lane links. Two transmitters (short run and long run) and a single receiver are specified for each of three baud rates, 1.25, 2.50, and 3.125 GBaud.

Two transmitter specifications allow for solutions ranging from simple board-to-board interconnect to driving two connectors across a backplane. A single receiver specification is given that accepts signals from both the short run and long run transmitter specifications.

The short run transmitter should be used mainly for chip-to-chip connections on either the same printed circuit board or across a single connector. This covers the case where connections are made to a mezzanine (daughter) card. The minimum swings of the short run specification reduce the overall power used by the transceivers.

The long run transmitter specifications use larger voltage swings that are capable of driving signals across backplanes. This allows a user to drive signals across two connectors and a backplane. The specifications allow a distance of at least 50 cm at all baud rates.

All unit intervals are specified with a tolerance of +/-100 ppm. The worst case frequency difference between any transmit and receive clock is 200 ppm.

To ensure interoperability between drivers and receivers of different vendors and technologies, AC coupling at the receiver input must be used.

Serial RapidIO

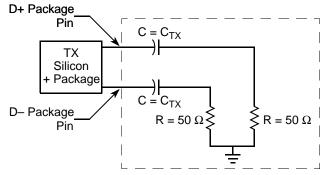

Figure 58. Transmitter Output Compliance Mask

| Transmitter Type        | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|-------------------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud short range  | 250                        | 500                        | 0.175  | 0.39   |

| 1.25 GBaud long range   | 400                        | 800                        | 0.175  | 0.39   |

| 2.5 GBaud short range   | 250                        | 500                        | 0.175  | 0.39   |

| 2.5 GBaud long range    | 400                        | 800                        | 0.175  | 0.39   |

| 3.125 GBaud short range | 250                        | 500                        | 0.175  | 0.39   |

| 3.125 GBaud long range  | 400                        | 800                        | 0.175  | 0.39   |

Table 71. Transmitter Differential Output Eye Diagram Parameters

## 17.6 Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance shall result in a differential return loss better that 10 dB and a common mode return loss better than 6 dB from 100 MHz to  $(0.8) \times$  (Baud Frequency). This includes contributions from on-chip circuitry, the chip package and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100 Ohm resistive for differential return loss and 25- $\Omega$  resistive for common mode.

Package Description

| Signal               | Signal Name                  | Package Pin Number                                                                                                                                                                  | Pin Type | Power<br>Supply  | Notes   |

|----------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| D2_MBA[0:2]          | Bank Select                  | Y1, W3, P3                                                                                                                                                                          | 0        | GV <sub>DD</sub> |         |

| D2_MWE               | Write Enable                 | AA2                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MCAS              | Column Address Strobe        | AD1                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MRAS              | Row Address Strobe           | AA1                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MCKE[0:3]         | Clock Enable                 | L3, L1, K1, K2                                                                                                                                                                      | 0        | GV <sub>DD</sub> | 11      |

| D2_MCS[0:3]          | Chip Select                  | AB1, AG2, AC1, AH2                                                                                                                                                                  | 0        | GV <sub>DD</sub> | _       |

| D2_MCK[0:5]          | Clock                        | V4, F7, AJ3, V2, E7,<br>AG4                                                                                                                                                         | 0        | GV <sub>DD</sub> | —       |

| D2_MCK[0:5]          | Clock Complements            | V1, F8, AJ4, U1, E6,<br>AG5                                                                                                                                                         | 0        | GV <sub>DD</sub> | —       |

| D2_MODT[0:3]         | On Die Termination           | AE1, AG1, AE2, AH1                                                                                                                                                                  | 0        | GV <sub>DD</sub> | —       |

| D2_MDIC[0:1]         | Driver Impedance Calibration | F1, G1                                                                                                                                                                              | I/O      | GV <sub>DD</sub> | 25      |

|                      | Local Bus Contr              | oller Interface                                                                                                                                                                     |          |                  |         |

| LAD[0:31]            | Muxed Data/Address           | M22, L22, F22, G22,<br>F21, G21, E20, H22,<br>K22, K21, H19, J20,<br>J19, L20, M20, M19,<br>E22, E21, L19, K19,<br>G19, H18, E18, G18,<br>J17, K17, K14, J15,<br>H16, J14, H15, G15 | I/O      | BV <sub>DD</sub> | 34      |

| LDP[0:3]             | Data Parity                  | M21, D22, A24, E17                                                                                                                                                                  | I/O      | BV <sub>DD</sub> | _       |

| LA[27]               | Burst Address                | J21                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LA[28:31]            | Port Address                 | F20, K18, H20, G17                                                                                                                                                                  | 0        | BV <sub>DD</sub> | 5, 7, 9 |

| LCS[0:4]             | Chip Selects                 | B23, E16, D20, B25,<br>A22                                                                                                                                                          | 0        | BV <sub>DD</sub> | 10      |

| LCS[5]/DMA2_DREQ[1]  | Chip Selects / DMA Request   | D19                                                                                                                                                                                 | I/O      | BV <sub>DD</sub> | 1, 10   |

| LCS[6]/DMA2_DACK[1]  | Chip Selects / DMA Ack       | E19                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 1, 10   |

| LCS[7]/DMA2_DDONE[1] | Chip Selects / DMA Done      | C21                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 1, 10   |

| LWE[0]/LBS[0]/LFWE   | Write Enable / Byte Select   | D17                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[1]/LBS[1]        | Write Enable / Byte Select   | F15                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[2]/LBS[2]        | Write Enable / Byte Select   | B24                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[3]/LBS[3]        | Write Enable / Byte Select   | D18                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LALE                 | Address Latch Enable         | F19                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                | Buffer Control               | L18                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| Table 76. MPC8572E Pinout Listing (continued) |                                                                                              |                                                                     |          |                  |         |  |  |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------|------------------|---------|--|--|--|

| Signal                                        | Signal Name                                                                                  | Package Pin Number                                                  | Pin Type | Power<br>Supply  | Notes   |  |  |  |

| LGPL0/LFCLE                                   | UPM General Purpose Line 0 /<br>Flash Command Latch Enable                                   | J13                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |

| LGPL1/LFALE                                   | UPM General Purpose Line 1/<br>Flash Address Latch Enable                                    | J16                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |

| LGPL2/LOE/LFRE                                | UPM General Purpose Line 2 /<br>Output Enable / Flash Read<br>Enable                         | A27                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |  |  |  |

| LGPL3/LFWP                                    | UPM General Purpose Line 3 /<br>Flash Write Protect                                          | K16                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |

| LGPL4/LGTA/LUPWAIT/LPBSE<br>/LFRB             | UPM General Purpose Line 4 /<br>Target Ack / Wait / Parity Byte<br>Select / Flash Ready-Busy | L17                                                                 | I/O      | BV <sub>DD</sub> |         |  |  |  |

| LGPL5                                         | UPM General Purpose Line 5 /<br>Amux                                                         | B26                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |

| LCLK[0:2]                                     | Local Bus Clock                                                                              | F17, F16, A23                                                       | 0        | BV <sub>DD</sub> | _       |  |  |  |

| LSYNC_IN                                      | Local Bus DLL Synchronization                                                                | B22                                                                 | Ι        | BV <sub>DD</sub> | _       |  |  |  |

| LSYNC_OUT                                     | Local Bus DLL Synchronization                                                                | A21                                                                 | 0        | BV <sub>DD</sub> | —       |  |  |  |

|                                               | DMA                                                                                          |                                                                     |          |                  |         |  |  |  |

| DMA1_DACK[0:1]                                | DMA Acknowledge                                                                              | W25, U30                                                            | 0        | OV <sub>DD</sub> | 21      |  |  |  |

| DMA2_DACK[0]                                  | DMA Acknowledge                                                                              | AA26                                                                | 0        | OV <sub>DD</sub> | 5, 9    |  |  |  |

| DMA1_DREQ[0:1]                                | DMA Request                                                                                  | Y29, V27                                                            | I        | OV <sub>DD</sub> | —       |  |  |  |

| DMA2_DREQ[0]                                  | DMA Request                                                                                  | V29                                                                 | Ι        | OV <sub>DD</sub> | —       |  |  |  |

| DMA1_DDONE[0:1]                               | DMA Done                                                                                     | Y28, V30                                                            | 0        | OV <sub>DD</sub> | 5, 9    |  |  |  |

| DMA2_DDONE[0]                                 | DMA Done                                                                                     | AA28                                                                | 0        | OV <sub>DD</sub> | 5, 9    |  |  |  |

| DMA2_DREQ[2]                                  | DMA Request                                                                                  | M23                                                                 | Ι        | BV <sub>DD</sub> | —       |  |  |  |

|                                               | Programmable Inter                                                                           | rupt Controller                                                     |          |                  |         |  |  |  |

| UDE0                                          | Unconditional Debug Event<br>Processor 0                                                     | AC25                                                                | I        | OV <sub>DD</sub> | _       |  |  |  |

| UDE1                                          | Unconditional Debug Event<br>Processor 1                                                     | AA25                                                                | Ι        | OV <sub>DD</sub> | —       |  |  |  |

| MCP0                                          | Machine Check Processor 0                                                                    | M28                                                                 | Ι        | OV <sub>DD</sub> | _       |  |  |  |

| MCP1                                          | Machine Check Processor 1                                                                    | L28                                                                 | I        | OV <sub>DD</sub> | _       |  |  |  |

| IRQ[0:11]                                     | External Interrupts                                                                          | T24, R24, R25, R27,<br>R28, AB27, AB28, P27,<br>R30, AC28, R29, T31 | Ι        | OV <sub>DD</sub> | _       |  |  |  |

### Table 76. MPC8572E Pinout Listing (continued)

| Table 76. MPC8572E Pinout Listing (continued) |

|-----------------------------------------------|

|-----------------------------------------------|

| Signal           | Signal Signal Name          |               | Pin Type | Power<br>Supply  | Notes     |  |  |  |

|------------------|-----------------------------|---------------|----------|------------------|-----------|--|--|--|

| MSRCID[0:1]      | Memory Debug Source Port ID | U27, T29      | 0        | OV <sub>DD</sub> | 5, 9, 30  |  |  |  |

| MSRCID[2:4]      | Memory Debug Source Port ID | U28, W24, W28 | 0        | OV <sub>DD</sub> | 21        |  |  |  |

| MDVAL            | Memory Debug Data Valid     | V26           | 0        | OV <sub>DD</sub> | 2, 21     |  |  |  |

| CLK_OUT          | Clock Out                   | U32           | 0        | OV <sub>DD</sub> | 11        |  |  |  |

|                  | Clock                       | κ             |          |                  |           |  |  |  |

| RTC              | Real Time Clock             | V25           | I        | OV <sub>DD</sub> | —         |  |  |  |

| SYSCLK           | System Clock                | Y32           | I        | OV <sub>DD</sub> | —         |  |  |  |

| DDRCLK           | DDR Clock                   | AA29          | I        | OV <sub>DD</sub> | 31        |  |  |  |

| JTAG             |                             |               |          |                  |           |  |  |  |

| тск              | Test Clock                  | T28           | I        | OV <sub>DD</sub> |           |  |  |  |

| TDI              | Test Data In                | T27           | I        | OV <sub>DD</sub> | 12        |  |  |  |

| TDO              | Test Data Out               | T26           | 0        | OV <sub>DD</sub> | —         |  |  |  |

| TMS              | Test Mode Select            | U26           | I        | OV <sub>DD</sub> | 12        |  |  |  |

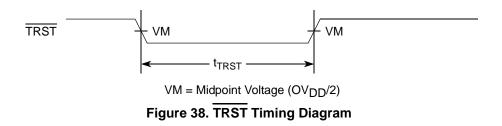

| TRST             | Test Reset                  | AA32          | I        | OV <sub>DD</sub> | 12        |  |  |  |

| DFT              |                             |               |          |                  |           |  |  |  |

| L1_TSTCLK        | L1 Test Clock               | V32           | I        | OV <sub>DD</sub> | 18        |  |  |  |

| L2_TSTCLK        | L2 Test Clock               | V31           | I        | OV <sub>DD</sub> | 18        |  |  |  |

| LSSD_MODE        | LSSD Mode                   | N24           | I        | OV <sub>DD</sub> | 18        |  |  |  |

| TEST_SEL         | Test Select 0               | K28           | I        | OV <sub>DD</sub> | 18        |  |  |  |

| Power Management |                             |               |          |                  |           |  |  |  |

| ASLEEP           | Asleep                      | P28           | 0        | OV <sub>DD</sub> | 9, 15, 21 |  |  |  |

System Design Information

#### Notes:

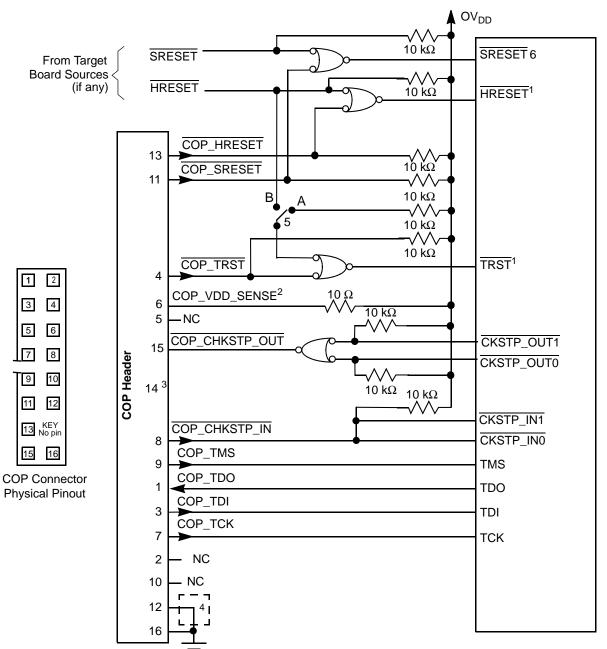

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor to fully control the processor as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- 5. This switch is included as a precaution for BSDL testing. The switch should be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed to position B.

- 6. Asserting SRESET causes a machine check interrupt to the e500 cores.

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. ,ÅúTypical,Åù parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including ,Åútypicals,,Åù must be validated for each customer application by customer,Åôs technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE,

JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. . Oracle and

Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2008-2011, 2014, 2016 NXP B.V.

Document Number: MPC8572EEC Rev. 7 03/2016