# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                  |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | -                                                                       |

| Number of Cores/Bus Width       | -                                                                       |

| Speed                           | -                                                                       |

| Co-Processors/DSP               | -                                                                       |

| RAM Controllers                 | -                                                                       |

| Graphics Acceleration           | -                                                                       |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | -                                                                       |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | -                                                                       |

| Operating Temperature           | -                                                                       |

| Security Features               | -                                                                       |

| Package / Case                  | -                                                                       |

| Supplier Device Package         | -                                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572elvtavne |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

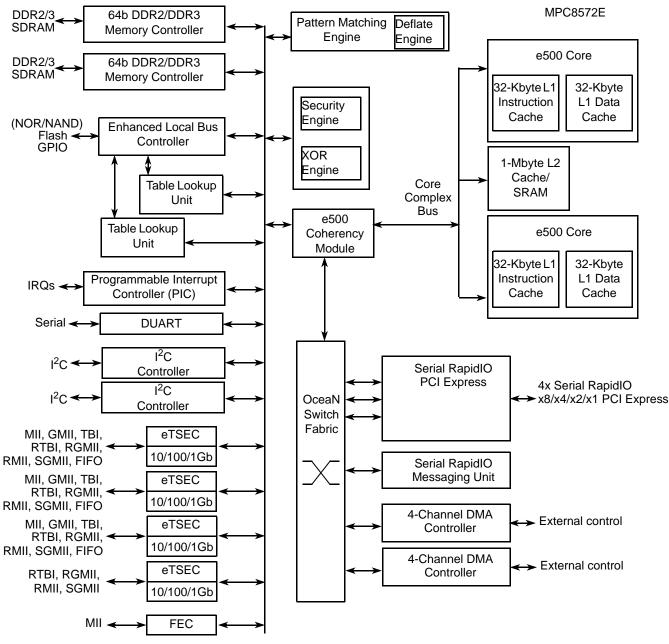

Figure 1 shows the MPC8572E block diagram.

## 2 **Electrical Characteristics**

This section provides the AC and DC electrical specifications for the MPC8572E. The MPC8572E is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

## 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

### 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| Table 1. Absolute Maximum Ratings | 1 |

|-----------------------------------|---|

|-----------------------------------|---|

|                                       | Characteristic                                                                         | Symbol                                        | Range                                                                | Unit | Notes |

|---------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------|------|-------|

| Core supply voltag                    | e                                                                                      | V <sub>DD</sub>                               | -0.3 to 1.21                                                         | V    |       |

| PLL supply voltage                    | 3                                                                                      | AV <sub>DD</sub>                              | -0.3 to 1.21                                                         | V    | _     |

| Core power supply                     | ofor SerDes transceivers                                                               | SV <sub>DD</sub>                              | -0.3 to 1.21                                                         | V    | _     |

| Pad power supply                      | for SerDes transceivers                                                                | XV <sub>DD</sub>                              | -0.3 to 1.21                                                         | V    | _     |

| DDR SDRAM                             | DDR2 SDRAM Interface                                                                   | GV <sub>DD</sub>                              | -0.3 to 1.98                                                         | V    | _     |

| Controller I/O<br>supply voltage      | DDR3 SDRAM Interface                                                                   | _                                             | -0.3 to 1.65                                                         |      | —     |

| Three-speed Ether<br>management volta | rnet I/O, FEC management interface, MII<br>ge                                          | LV <sub>DD</sub> (for eTSEC1 and eTSEC2)      | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | 2     |

|                                       |                                                                                        | TV <sub>DD</sub> (for eTSEC3 and eTSEC4, FEC) | -0.3 to 3.63<br>-0.3 to 2.75                                         | —    | 2     |

| DUART, system co<br>I/O voltage       | ontrol and power management, I <sup>2</sup> C, and JTAG                                | OV <sub>DD</sub>                              | -0.3 to 3.63                                                         | V    | —     |

| Local bus and GPI                     | O I/O voltage                                                                          | BV <sub>DD</sub>                              | -0.3 to 3.63<br>-0.3 to 2.75<br>-0.3 to 1.98                         | V    | _     |

| Input voltage                         | DDR2 and DDR3 SDRAM interface signals                                                  | MV <sub>IN</sub>                              | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 3     |

|                                       | DDR2 and DDR3 SDRAM interface reference                                                | MV <sub>REF</sub> n                           | -0.3 to (GV <sub>DD</sub> /2 + 0.3)                                  | V    | —     |

|                                       | Three-speed Ethernet signals                                                           | LV <sub>IN</sub><br>TV <sub>IN</sub>          | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 3     |

|                                       | Local bus and GPIO signals                                                             | BV <sub>IN</sub>                              | –0.3 to (BV <sub>DD</sub> + 0.3)                                     | —    | —     |

|                                       | DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                              | –0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 3     |

| Storage temperatu                     | re range                                                                               | T <sub>STG</sub>                              | –55 to 150                                                           | °C   | —     |

Notes:

1. Functional operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

The 3.63V maximum is only supported when the port is configured in GMII, MII, RMII or TBI modes; otherwise the 2.75V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

3. (M,L,O)V<sub>IN</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

Electrical Characteristics

### 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values shown are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

|                                  | Characteristic                                                                                                    | Symbol                               | Recommended Value                                  | Unit | Notes |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|------|-------|

| Core supply voltage              |                                                                                                                   | V <sub>DD</sub>                      | 1.1 V ± 55 mV                                      | V    |       |

| PLL supply voltage               |                                                                                                                   | AV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | 1     |

| Core power supply for            | or SerDes transceivers                                                                                            | SV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    |       |

| Pad power supply fo              | r SerDes transceivers                                                                                             | XV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    |       |

| DDR SDRAM                        | DDR2 SDRAM Interface                                                                                              | GV <sub>DD</sub>                     | 1.8 V ± 90 mV                                      | V    |       |

| Controller I/O<br>supply voltage | DDR3 SDRAM Interface                                                                                              |                                      | 1.5 V ± 75 mV                                      |      |       |

| Three-speed Etherne              | et I/O voltage                                                                                                    | LV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | 4     |

|                                  |                                                                                                                   | TV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   |      | 4     |

| DUART, system con                | trol and power management, $I^2C$ , and JTAG I/O voltage                                                          | OV <sub>DD</sub>                     | 3.3 V ± 165 mV                                     | V    | 3     |

| Local bus and GPIO               | I/O voltage                                                                                                       | BV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV<br>1.8 V ± 90 mV  | V    | _     |

| Input voltage                    | DDR2 and DDR3 SDRAM Interface signals                                                                             | MV <sub>IN</sub>                     | GND to GV <sub>DD</sub>                            | V    | 2     |

|                                  | DDR2 and DDR3 SDRAM Interface reference                                                                           | MV <sub>REF</sub> n                  | GV <sub>DD</sub> /2 ± 1%                           | V    | _     |

|                                  | Three-speed Ethernet signals                                                                                      | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V    | 4     |

|                                  | Local bus and GPIO signals                                                                                        | BVIN                                 | GND to BV <sub>DD</sub>                            | V    |       |

|                                  | Local bus, DUART, SYSCLK, Serial RapidIO, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                     | GND to OV <sub>DD</sub>                            | V    | 3     |

| Junction temperature             | e range                                                                                                           | TJ                                   | 0 to 105                                           | °C   | _     |

#### **Table 2. Recommended Operating Conditions**

#### Notes:

- 1. This voltage is the input to the filter discussed in Section 21.2.1, "PLL Power Supply Filtering," and not necessarily the voltage at the AV<sub>DD</sub> pin, that may be reduced from V<sub>DD</sub> by the filter.

- 2. Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. Caution: L/TV<sub>IN</sub> must not exceed L/TV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

## 4 Input Clocks

## 4.1 System Clock Timing

Table 6 provides the system clock (SYSCLK) AC timing specifications for the MPC8572E.

#### Table 6. SYSCLK AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition       | Symbol                                | Min | Typical | Мах     | Unit | Notes   |

|---------------------------|---------------------------------------|-----|---------|---------|------|---------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 33  | —       | 133     | MHz  | 1       |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                   | 7.5 | —       | 30.3    | ns   | —       |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 1.2     | ns   | 2       |

| SYSCLK duty cycle         | t <sub>KHK</sub> /t <sub>SYSCLK</sub> | 40  | —       | 60      | %    | 3       |

| SYSCLK jitter             | —                                     | —   | —       | +/- 150 | ps   | 4, 5, 6 |

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies.Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on SYSCLK.

## 4.2 Real Time Clock Timing

The RTC input is sampled by the platform clock (CCB clock). The output of the sampling latch is then used as an input to the counters of the PIC and the TimeBase unit of the e500. There is no jitter specification. The minimum pulse width of the RTC signal should be greater than 2x the period of the CCB clock. That is, minimum clock high time is  $2 \times t_{CCB}$ , and minimum clock low time is  $2 \times t_{CCB}$ . There is no minimum RTC frequency; RTC may be grounded if not needed.

#### DDR2 and DDR3 SDRAM Controller

#### Table 17. DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                         | Symbol              | Min  | Max | Unit | Notes |

|-----------------------------------|---------------------|------|-----|------|-------|

| Controller Skew for MDQS—MDQ/MECC | t <sub>CISKEW</sub> | —    | _   | ps   | 1, 2  |

| 800 MHz                           | _                   | -200 | 200 | —    | —     |

| 667 MHz                           | _                   | -240 | 240 | —    | —     |

| 533 MHz                           | _                   | -300 | 300 | —    | —     |

| 400 MHz                           | _                   | -365 | 365 |      | —     |

Note:

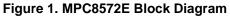

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called tDISKEW. This can be determined by the following equation: tDISKEW =+/-(T/4 – abs(tCISKEW)) where T is the clock period and abs(tCISKEW) is the absolute value of tCISKEW.

Figure 3 shows the DDR2 and DDR3 SDRAM interface input timing diagram.

Figure 3. DDR2 and DDR3 SDRAM Interface Input Timing Diagram

### 6.2.2 DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications

Table 18 contains the output AC timing targets for the DDR2 and DDR3 SDRAM interface.

#### Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                                 | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|-------------------------------------------|---------------------|-----|-----|------|-------|

| MCK[n] cycle time                         | t <sub>MCK</sub>    | 2.5 | 5   | ns   | 2     |

| ADDR/CMD output setup with respect to MCK | t <sub>DDKHAS</sub> |     |     | ns   | 3     |

#### DDR2 and DDR3 SDRAM Controller

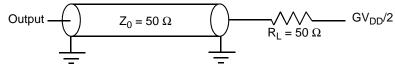

Figure 6 provides the AC test load for the DDR2 and DDR3 Controller bus.

Figure 6. DDR2 and DDR3 Controller bus AC Test Load

### 6.2.3 DDR2 and DDR3 SDRAM Differential Timing Specifications

This section describes the DC and AC differential electrical specifications for the DDR2 and DDR3 SDRAM controller interface of the MPC8572E.

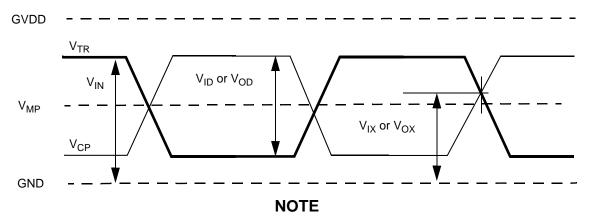

VID specifies the input differential voltage |VTR - VCP| required for switching, where VTR is the true input signal (such as MCK or MDQS) and VCP is the complementary input signal (such as MCK or MDQS).

Table 19 provides the differential specifications for the MPC8572E differential signals MDQS/ $\overline{MDQS}$  and MCK/ $\overline{MCK}$  when in DDR2 mode.

| Parameter/Condition                 | Symbol            | Min        | Мах                           | Unit | Notes |

|-------------------------------------|-------------------|------------|-------------------------------|------|-------|

| DC Input Signal Voltage             | V <sub>IN</sub>   | -0.3       | GV <sub>DD</sub> + 0.3        | V    | —     |

| DC Differential Input Voltage       | V <sub>ID</sub>   |            | —                             | mV   | —     |

| AC Differential Input Voltage       | V <sub>IDAC</sub> |            | —                             | mV   | —     |

| DC Differential Output Voltage      | V <sub>OH</sub>   | _          | _                             | mV   | —     |

| AC Differential Output Voltage      | V <sub>OHAC</sub> | JEDEC: 0.5 | JEDEC: GV <sub>DD</sub> + 0.6 | V    | —     |

| AC Differential Cross-point Voltage | V <sub>IXAC</sub> | _          | _                             | mV   | —     |

| Input Midpoint Voltage              | V <sub>MP</sub>   | _          | —                             | mV   | —     |

Table 19. DDR2 SDRAM Differential Electrical Characteristics

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

## 7.2 DUART AC Electrical Specifications

Table 22 provides the AC timing parameters for the DUART interface.

#### Table 22. DUART AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter         | Value                       | Unit | Notes   |

|-------------------|-----------------------------|------|---------|

| Minimum baud rate | f <sub>CCB</sub> /1,048,576 | baud | 1, 2    |

| Maximum baud rate | f <sub>CCB</sub> /16        | baud | 1, 2, 3 |

| Oversample rate   | 16                          | _    | 1, 4    |

#### Notes:

1. Guaranteed by design

- 2. f<sub>CCB</sub> refers to the internal platform clock frequency.

- 3. Actual attainable baud rate is limited by the latency of interrupt processing.

- 4. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

## 8 Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

This section provides the AC and DC electrical characteristics for the enhanced three-speed Ethernet controller.

### 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics

The electrical characteristics specified here apply to all FIFO mode, gigabit media independent interface (GMII), media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), and reduced media independent interface (RMII) signals except management data input/output (MDIO) and management data clock (MDC), and serial gigabit media independent interface (SGMII). The RGMII, RTBI and FIFO mode interfaces are defined for 2.5 V, while the GMII, MII, RMII, and TBI interfaces can operate at both 2.5 V and 3.3V.

The GMII, MII, or TBI interface timing is compliant with IEEE 802.3. The RGMII and RTBI interfaces follow the Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3 (12/10/2000). The RMII interface follows the RMII Consortium RMII Specification Version 1.2 (3/20/1998).

The electrical characteristics for MDIO and MDC are specified in Section 9, "Ethernet Management Interface Electrical Characteristics."

The electrical characteristics for SGMII is specified in Section 8.3, "SGMII Interface Electrical Characteristics." The SGMII interface conforms (with exceptions) to the Serial-GMII Specification Version 1.8.

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

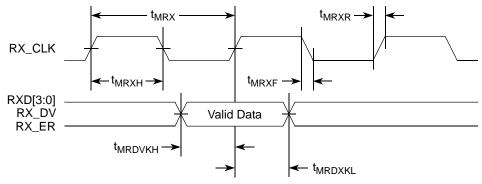

Figure 14 shows the MII receive AC timing diagram.

Figure 14. MII Receive AC Timing Diagram

### 8.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

### 8.2.4.1 TBI Transmit AC Timing Specifications

Table 31 provides the TBI transmit AC timing specifications.

#### Table 31. TBI Transmit AC Timing Specifications

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>            | Min | Тур | Мах | Unit |

|--------------------------------------------|--------------------------------|-----|-----|-----|------|

| TCG[9:0] setup time GTX_CLK going high     | t <sub>TTKHDV</sub>            | 2.0 | _   | _   | ns   |

| TCG[9:0] hold time from GTX_CLK going high | t <sub>TTKHDX</sub>            | 1.0 | _   | _   | ns   |

| GTX_CLK rise (20%-80%)                     | t <sub>TTXR</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

| GTX_CLK fall time (80%–20%)                | t <sub>TTXF</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

#### Table 35. RMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup> | Min | Тур | Мах  | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|------|

| TSECn_TX_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 1.0 |     | 10.0 | ns   |

Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

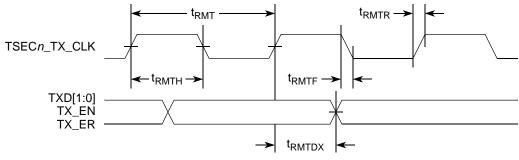

Figure 19 shows the RMII transmit AC timing diagram.

Figure 19. RMII Transmit AC Timing Diagram

### 8.2.7.2 RMII Receive AC Timing Specifications

Table 36 shows the RMII receive AC timing specifications.

#### Table 36. RMII Receive AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                                               | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period                                         | t <sub>RMR</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_TX_CLK duty cycle                                           | t <sub>RMRH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter                                  | t <sub>RMRJ</sub>   | —    | —    | 250  | ps   |

| Rise time TSECn_TX_CLK (20%-80%)                                  | t <sub>RMRR</sub>   | 1.0  | —    | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%–20%)                                  | t <sub>RMRF</sub>   | 1.0  | —    | 2.0  | ns   |

| RXD[1:0], CRS_DV, RX_ER setup time to<br>TSECn_TX_CLK rising edge | t <sub>RMRDV</sub>  | 4.0  | -    | —    | ns   |

described in Section 21.5, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

When operating in SGMII mode, the eTSEC EC\_GTX\_CLK125 clock is not required for this port. Instead, SerDes reference clock is required on SD2\_REF\_CLK and SD2\_REF\_CLK pins.

## 8.3.1 DC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 15, "High-Speed Serial Interfaces (HSSI)."

## 8.3.2 AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

Table 37 lists the SGMII SerDes reference clock AC requirements. Note that SD2\_REF\_CLK and SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

| Symbol             | Parameter Description                                                                    |     | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | _   | 10 (8)  |     | ns    | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles |     |         | 100 | ps    | —     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | —       | 50  | ps    | —     |

#### Table 37. SD2\_REF\_CLK and SD2\_REF\_CLK AC Requirements

Note:

1.8 ns applies only when 125 MHz SerDes2 reference clock frequency is selected through cfg\_srds\_sgmii\_refclk during POR.

### 8.3.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs ( $SD2_TX[n]$  and  $\overline{SD2_TX[n]}$ ) or at the receiver inputs ( $SD2_RX[n]$  and  $\overline{SD2_RX[n]}$ ) as depicted in Figure 25, respectively.

### 8.3.4.1 SGMII Transmit AC Timing Specifications

Table 40 provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### Table 40. SGMII Transmit AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2}$  = 1.1V ± 5%.

| Parameter                           | Symbol            | Min    | Тур | Max    | Unit   | Notes |

|-------------------------------------|-------------------|--------|-----|--------|--------|-------|

| Deterministic Jitter                | JD                | —      | _   | 0.17   | UI p-p | _     |

| Total Jitter                        | JT                | —      | _   | 0.35   | UI p-p | _     |

| Unit Interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1     |

| V <sub>OD</sub> fall time (80%-20%) | tfall             | 50     | _   | 120    | ps     | _     |

| V <sub>OD</sub> rise time (20%-80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     | _     |

Notes:

1. Each UI is 800 ps  $\pm$  100 ppm.

### 8.3.4.2 SGMII Receive AC Timing Specifications

Table 41 provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 24 shows the SGMII receiver input compliance mask eye diagram.

#### Table 41. SGMII Receive AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2} = 1.1V \pm 5\%$ .

| Parameter                                          | Symbol          | Min    | Тур | Max               | Unit   | Notes |

|----------------------------------------------------|-----------------|--------|-----|-------------------|--------|-------|

| Deterministic Jitter Tolerance                     | JD              | 0.37   | —   | —                 | UI p-p | 1     |

| Combined Deterministic and Random Jitter Tolerance | JDR             | 0.55   | —   | _                 | UI p-p | 1     |

| Sinusoidal Jitter Tolerance                        | JSIN            | 0.1    | —   | —                 | UI p-p | 1     |

| Total Jitter Tolerance                             | JT              | 0.65   |     | _                 | UI p-p | 1     |

| Bit Error Ratio                                    | BER             | _      | —   | 10 <sup>-12</sup> |        | _     |

| Unit Interval                                      | UI              | 799.92 | 800 | 800.08            | ps     | 2     |

| AC Coupling Capacitor                              | C <sub>TX</sub> | 5      | —   | 200               | nF     | 3     |

Notes:

1. Measured at receiver.

2. Each UI is 800 ps  $\pm$  100 ppm.

3. The external AC coupling capacitor is required. It is recommended to be placed near the device transmitter outputs.

4. See RapidIO 1x/4x LP Serial Physical Layer Specification for interpretation of jitter specifications.

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 42. eTSEC IEEE 1588 AC Timing Specifications (continued)

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%

| Parameter/Condition           | Symbol                                                  | Min                         | Тур | Мах | Unit | Note |

|-------------------------------|---------------------------------------------------------|-----------------------------|-----|-----|------|------|

| TSEC_1588_CLK_OUT duty cycle  | t <sub>T1588</sub> CLKOTH<br>/t <sub>T1588</sub> CLKOUT | 30                          | 50  | 70  | %    | —    |

| TSEC_1588_PULSE_OUT           | t <sub>T1588OV</sub>                                    | 0.5                         | _   | 3.0 | ns   | —    |

| TSEC_1588_TRIG_IN pulse width | t <sub>T1588</sub> TRIGH                                | 2*t <sub>T1588CLK_MAX</sub> | _   | —   | ns   | 2    |

#### Note:

1.When TMR\_CTRL[CKSEL] is set as '00', the external TSEC\_1588\_CLK input is selected as the 1588 timer reference clock source, with the timing defined in Table 42, "eTSEC IEEE 1588 AC Timing Specifications." The maximum value of t<sub>T1588CLK</sub> is defined in terms of T<sub>TX\_CLK</sub>, that is the maximum clock cycle period of the equivalent interface speed that the eTSEC1 port is running at. When eTSEC1 is configured to operate in the parallel mode, the T<sub>TX\_CLK</sub> is the maximum clock period of the TSEC1\_TX\_CLK. When eTSEC1 operates in SGMII mode, the maximum value of t<sub>T1588CLK</sub> is defined in terms of the recovered clock from SGMII SerDes. For example, for SGMII 10/100/1000 Mbps modes, the maximum value of t<sub>T1588CLK</sub> is 3600, 360, 72 ns respectively. See the *MPC8572E PowerQUICC™ III Integrated Communications Processor Reference Manual* for detailed description of TMR\_CTRL registers.

2. It needs to be at least two times of the clock period of the clock selected by TMR\_CTRL[CKSEL].

## 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals ECn\_MDIO (management data input/output) and ECn\_MDC (management data clock). The electrical characteristics for GMII, SGMII, RGMII, RMII, TBI and RTBI are specified in "Section 8, "Ethernet: Enhanced Three-Speed Ethernet (eTSEC)."

### 9.1 MII Management DC Electrical Characteristics

The ECn\_MDC and ECn\_MDIO are defined to operate at a supply voltage of 3.3 V or 2.5 V. The DC electrical characteristics for ECn\_MDIO and ECn\_MDC are provided in Table 43 and Table 44.

| Parameter                                                                | Symbol            | Min  | Мах                    | Unit | Notes |

|--------------------------------------------------------------------------|-------------------|------|------------------------|------|-------|

| Supply voltage (3.3 V)                                                   | $LV_{DD}/TV_{DD}$ | 3.13 | 3.47                   | V    | 1, 2  |

| Output high voltage<br>( $LV_{DD}/TV_{DD} = Min, I_{OH} = -1.0 mA$ )     | V <sub>OH</sub>   | 2.10 | OV <sub>DD</sub> + 0.3 | V    | _     |

| Output low voltage $(LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA)$            | V <sub>OL</sub>   | GND  | 0.50                   | V    | _     |

| Input high voltage                                                       | V <sub>IH</sub>   | 2.0  | —                      | V    | _     |

| Input low voltage                                                        | V <sub>IL</sub>   | _    | 0.90                   | V    | _     |

| Input high current $(LV_{DD}/TV_{DD} = Max, V_{IN}^{3} = 2.1 \text{ V})$ | IIH               |      | 40                     | μA   | —     |

Table 43. MII Management DC Electrical Characteristics ( $LV_{DD}/TV_{DD}$ =3.3 V)

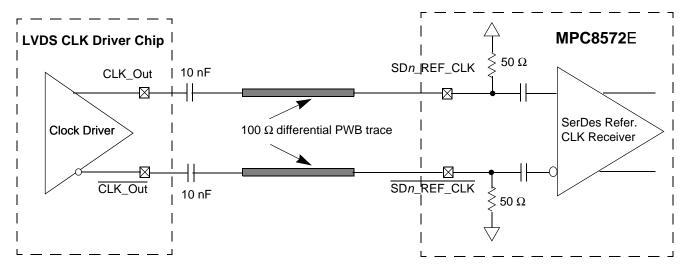

Figure 49 shows the SerDes reference clock connection reference circuits for LVDS type clock driver. Because LVDS clock driver's common mode voltage is higher than the MPC8572E SerDes reference clock input's allowed range (100 to 400mV), AC-coupled connection scheme must be used. It assumes the LVDS output driver features  $50-\Omega$  termination resistor. It also assumes that the LVDS transmitter establishes its own common mode level without relying on the receiver or other external component.

Figure 49. AC-Coupled Differential Connection with LVDS Clock Driver (Reference Only)

Figure 50 shows the SerDes reference clock connection reference circuits for LVPECL type clock driver. Because LVPECL driver's DC levels (both common mode voltages and output swing) are incompatible with MPC8572E SerDes reference clock input's DC requirement, AC-coupling must be used. Figure 50 assumes that the LVPECL clock driver's output impedance is  $50\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from  $140\Omega$  to  $240\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's  $50-\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8572E SerDes reference clock's differential input amplitude requirement (between 200mV and 800mV differential peak). For example, if the LVPECL output's differential peak is 900mV and the desired SerDes reference clock input amplitude is selected as 600mV, the attenuation factor is 0.67, which requires R2 =  $25\Omega$ . Consult

PCI Express

| Symbol                                       | Parameter                                                                                    | Min    | Nominal | Max    | Units | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|----------------------------------------------------------------------------------------------|--------|---------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                           | Unit Interval                                                                                | 399.88 | 400     | 400.12 | ps    | Each UI is 400 ps ± 300 ppm. UI does not account<br>for Spread Spectrum Clock dictated variations. See<br>Note 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>TX-DIFFp-p</sub>                      | Differential<br>Peak-to-Peak<br>Output Voltage                                               | 0.8    | —       | 1.2    | V     | $V_{TX-DIFFp-p} = 2^*  V_{TX-D+} - V_{TX-D-} $ See Note 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>TX-DE-RATIO</sub>                     | De- Emphasized<br>Differential<br>Output Voltage<br>(Ratio)                                  | -3.0   | -3.5    | -4.0   | dB    | Ratio of the $V_{TX-DIFFp-p}$ of the second and following bits after a transition divided by the $V_{TX-DIFFp-p}$ of the first bit after a transition. See Note 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| T <sub>TX-EYE</sub>                          | Minimum TX Eye<br>Width                                                                      | 0.70   | _       | —      | UI    | The maximum Transmitter jitter can be derived as $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.3$ UI.<br>See Notes 2 and 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| T <sub>TX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time<br>between the jitter<br>median and<br>maximum<br>deviation from<br>the median. |        | _       | 0.15   | UI    | Jitter is defined as the measurement variation of the crossing points ( $V_{TX-DIFFp-p} = 0$ V) in relation to a recovered TX UI. A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI. See Notes 2 and 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| T <sub>TX-RISE</sub> , T <sub>TX-FALL</sub>  | D+/D- TX Output<br>Rise/Fall Time                                                            | 0.125  | —       | —      | UI    | See Notes 2 and 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>TX-CM-ACp</sub>                       | RMS AC Peak<br>Common Mode<br>Output Voltage                                                 | —      | —       | 20     | mV    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VTX-CM-DC-ACTIVE-<br>IDLE-DELTA              | Absolute Delta of<br>DC Common<br>Mode Voltage<br>During L0 and<br>Electrical Idle           | 0      |         | 100    | mV    | $eq:logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_logical_lo$ |

| V <sub>TX-CM</sub> -DC-LINE-DELTA            | Absolute Delta of<br>DC Common<br>Mode between<br>D+ and D–                                  | 0      | —       | 25     | mV    | $\begin{split}  V_{\text{TX-CM-DC-D+}} - V_{\text{TX-CM-DC-D-}}  &<= 25 \text{ mV} \\ V_{\text{TX-CM-DC-D+}} = DC_{(\text{avg})} \text{ of }  V_{\text{TX-D+}}  \\ V_{\text{TX-CM-DC-D-}} = DC_{(\text{avg})} \text{ of }  V_{\text{TX-D-}}  \\ \text{See Note 2.} \end{split}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>TX-IDLE</sub> -DIFFp                  | Electrical Idle<br>differential Peak<br>Output Voltage                                       | 0      | —       | 20     | mV    | $V_{TX-IDLE-DIFFp} =  V_{TX-IDLE-D+} - V_{TX-IDLE-D-}  \le 20$<br>mV<br>See Note 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>TX-RCV-DETECT</sub>                   | The amount of<br>voltage change<br>allowed during<br>Receiver<br>Detection                   |        | _       | 600    | mV    | The total amount of voltage change that a transmitter can apply to sense whether a low impedance Receiver is present. See Note 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Serial RapidIO

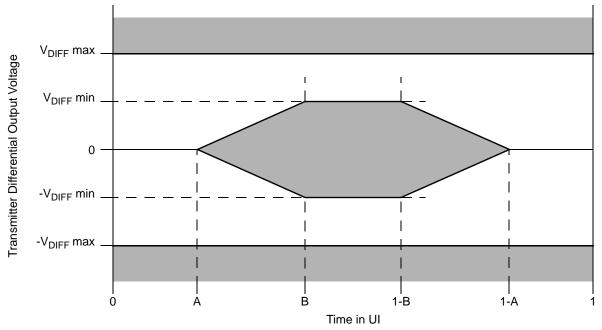

Figure 58. Transmitter Output Compliance Mask

| Transmitter Type        | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|-------------------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud short range  | 250                        | 500                        | 0.175  | 0.39   |

| 1.25 GBaud long range   | 400                        | 800                        | 0.175  | 0.39   |

| 2.5 GBaud short range   | 250                        | 500                        | 0.175  | 0.39   |

| 2.5 GBaud long range    | 400                        | 800                        | 0.175  | 0.39   |

| 3.125 GBaud short range | 250                        | 500                        | 0.175  | 0.39   |

| 3.125 GBaud long range  | 400                        | 800                        | 0.175  | 0.39   |

Table 71. Transmitter Differential Output Eye Diagram Parameters

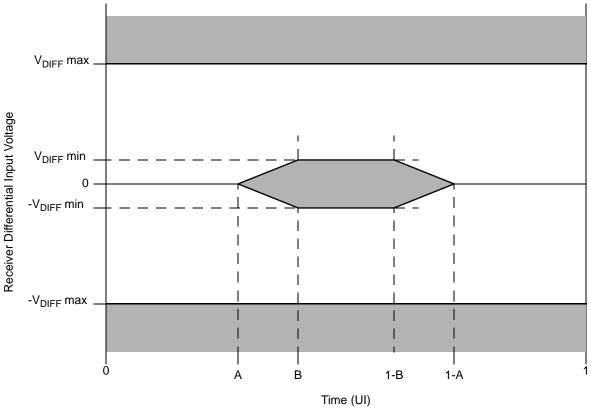

## 17.6 Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance shall result in a differential return loss better that 10 dB and a common mode return loss better than 6 dB from 100 MHz to  $(0.8) \times$  (Baud Frequency). This includes contributions from on-chip circuitry, the chip package and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100 Ohm resistive for differential return loss and 25- $\Omega$  resistive for common mode.

Serial RapidIO

Figure 60. Receiver Input Compliance Mask

| Receiver Type | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|---------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud    | 100                        | 800                        | 0.275  | 0.400  |

| 2.5 GBaud     | 100                        | 800                        | 0.275  | 0.400  |

| 3.125 GBaud   | 100                        | 800                        | 0.275  | 0.400  |

## 17.8 Measurement and Test Requirements

Because the LP-Serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002, the measurement and test requirements defined here are similarly guided by Clause 47. Additionally, the CJPAT test pattern defined in Annex 48A of IEEE 802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter measurements. Annex 48B of IEEE 802.3ae-2002 is recommended as a reference for additional information on jitter test methods.

## 17.8.1 Eye Template Measurements

For the purpose of eye template measurements, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for template measurements is the Continuous Jitter Test Pattern (CJPAT) defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial

Thermal

$V_f > 0.40$  V  $V_f < 0.90$  V  $Operating \ range \ 2-300 \ \mu A$   $Diode \ leakage < 10 \ nA \ @ \ 125^{\circ}C$

An approximate value of the ideality may be obtained by calibrating the device near the expected operating temperature.

Ideality factor is defined as the deviation from the ideal diode equation:

$$I_{fw} = I_s \left[ e^{\frac{qV_f}{nKT}} - 1 \right]$$

Another useful equation is:

$$\mathbf{V}_{H} - \mathbf{V}_{L} = \mathbf{n} \frac{\mathrm{KT}}{\mathrm{q}} \left[ \mathbf{I} \mathbf{n} \frac{\mathrm{I}_{H}}{\mathrm{I}_{L}} \right]$$

Where:

$I_{fw} = Forward current$   $I_s = Saturation current$   $V_d = Voltage at diode$   $V_f = Voltage forward biased$   $V_H = Diode voltage while I_H is flowing$   $V_L = Diode voltage while I_L is flowing$   $I_H = Larger diode bias current$   $I_L = Smaller diode bias current$   $q = Charge of electron (1.6 \times 10^{-19} \text{ C})$  n = Ideality factor (normally 1.0)  $K = Boltzman's constant (1.38 \times 10^{-23} \text{ Joules/K})$  T = Temperature (Kelvins)

The ratio of  $I_H$  to  $I_L$  is usually selected to be 10:1. The above simplifies to the following:

$V_{\text{H}} - V_{\text{L}} = ~1.986 \times 10^{-4} \times nT$

Solving for T, the equation becomes:

$$\mathbf{nT} = \frac{\mathbf{V}_{\mathsf{H}} - \mathbf{V}_{\mathsf{L}}}{1.986 \times 10^{-4}}$$

System Design Information

## 21.6 Pull-Up and Pull-Down Resistor Requirements

The MPC8572E requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and MPIC interrupt pins.

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 66. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

The following pins must NOT be pulled down during power-on reset: DMA\_DACK[0:1], EC5\_MDC, HRESET\_REQ, TRIG\_OUT/READY\_P0/QUIESCE, MSRCID[2:4], MDVAL, and ASLEEP. The TEST\_SEL pin must be set to a proper state during POR configuration. For more details, refer to the pinlist table of the individual device.

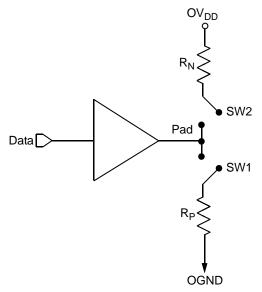

## 21.7 Output Buffer DC Impedance

The MPC8572E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 64). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

Figure 64. Driver Impedance Measurement

#### System Design Information

logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert TRST during the power-on reset flow. Simply tying TRST to HRESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 66 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

The COP interface has a standard header, shown in Figure 65, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; so emulator vendors have issued many different pin numbering schemes. Some COP headers are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom. Still others number the pins counter-clockwise from pin 1 (as with an IC). Regardless of the numbering scheme, the signal placement recommended in Figure 65 is common to all known emulators.

### 21.9.1 Termination of Unused Signals

If the JTAG interface and COP header is not used, Freescale recommends the following connections:

- TRST should be tied to HRESET through a 0 k $\Omega$  isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 66. If this is not possible, the isolation resistor allows future access to TRST in case a JTAG interface may need to be wired onto the system in future debug situations.

- No pull-up/pull-down is required for TDI, TMS, TDO or TCK.

**Document Revision History**