# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                         |

| Speed                           | 1.5GHz                                                                 |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                  |

| RAM Controllers                 | DDR2, DDR3                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                 |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                  |

| Package / Case                  | 1023-BFBGA, FCBGA                                                      |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572epxavnb |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

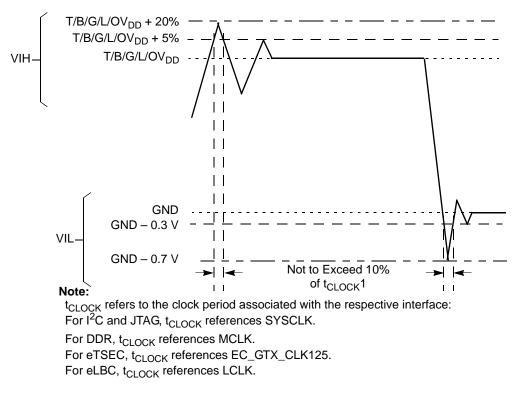

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8572E.

#### Figure 2. Overshoot/Undershoot Voltage for TV<sub>DD</sub>/BV<sub>DD</sub>/GV<sub>DD</sub>/LV<sub>DD</sub>/OV<sub>DD</sub>

The core voltage must always be provided at nominal 1.1 V. (See Table 2 for actual recommended core voltage.) Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ , and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR2 and DDR3 SDRAM interface uses differential receivers referenced by the externally supplied  $MV_{REF}n$  signal (nominally set to  $GV_{DD}/2$ ) as is appropriate for the SSTL\_1.8 electrical signaling standard for DDR2 or 1.5-V electrical signaling for DDR3. The DDR DQS receivers cannot be operated in single-ended fashion. The complement signal must be properly driven and cannot be grounded.

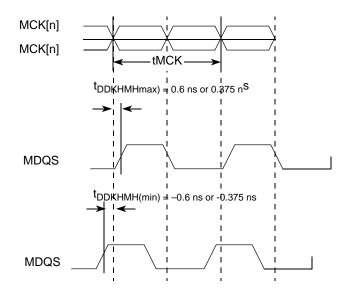

Figure 4 shows the DDR2 and DDR3 SDRAM Interface output timing for the MCK to MDQS skew measurement (tDDKHMH).

Figure 4. Timing Diagram for tDDKHMH

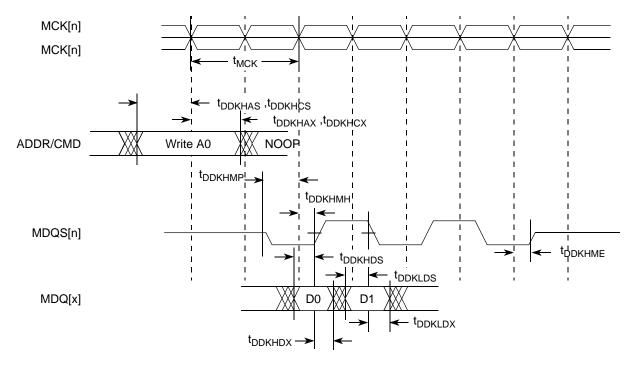

Figure 5 shows the DDR2 and DDR3 SDRAM Interface output timing diagram.

Figure 5. DDR2 and DDR3 SDRAM Interface Output Timing Diagram

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

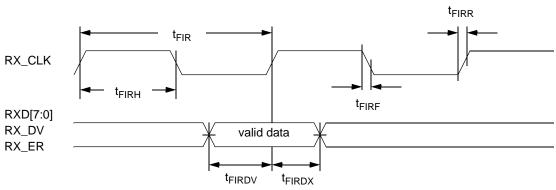

Figure 8. FIFO Receive AC Timing Diagram

# 8.2.2 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

### 8.2.2.1 GMII Transmit AC Timing Specifications

Table 27 provides the GMII transmit AC timing specifications.

#### Table 27. GMII Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 2.5/ 3.3 V ± 5%.

| Parameter/Condition                               | Symbol <sup>1</sup> | Min | Тур | Max | Unit |

|---------------------------------------------------|---------------------|-----|-----|-----|------|

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | t <sub>GTKHDV</sub> | 2.5 | _   | _   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | <sup>t</sup> GTKHDX | 0.5 | _   | 5.0 | ns   |

| GTX_CLK data clock rise time (20%-80%)            | t <sub>GTXR</sub> 2 | _   | _   | 1.0 | ns   |

| GTX_CLK data clock fall time (80%-20%)            | $t_{GTXF}^2$        |     | 1   | 1.0 | ns   |

#### Notes:

1. The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

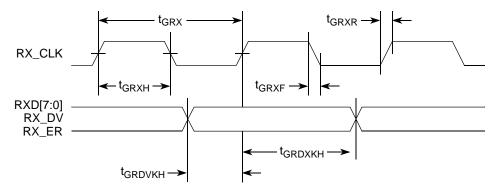

Figure 11 shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

### 8.2.3 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.3.1 MII Transmit AC Timing Specifications

Table 29 provides the MII transmit AC timing specifications.

#### Table 29. MII Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> <sup>2</sup>       | —   | 400 | _   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                    | —   | 40  | _   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                 | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise (20%-80%)                | t <sub>MTXR</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

| TX_CLK data clock fall (80%-20%)                | t <sub>MTXF</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

# 8.3.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs ( $SD2_TX[n]$  and  $\overline{SD2_TX[n]}$ ) or at the receiver inputs ( $SD2_RX[n]$  and  $\overline{SD2_RX[n]}$ ) as depicted in Figure 25, respectively.

## 8.3.4.1 SGMII Transmit AC Timing Specifications

Table 40 provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### Table 40. SGMII Transmit AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2}$  = 1.1V ± 5%.

| Parameter                           | Symbol            | Min    | Тур | Max    | Unit   | Notes |

|-------------------------------------|-------------------|--------|-----|--------|--------|-------|

| Deterministic Jitter                | JD                | —      | _   | 0.17   | UI p-p | _     |

| Total Jitter                        | JT                | —      | _   | 0.35   | UI p-p | _     |

| Unit Interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1     |

| V <sub>OD</sub> fall time (80%-20%) | tfall             | 50     | _   | 120    | ps     | _     |

| V <sub>OD</sub> rise time (20%-80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     | _     |

Notes:

1. Each UI is 800 ps  $\pm$  100 ppm.

### 8.3.4.2 SGMII Receive AC Timing Specifications

Table 41 provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 24 shows the SGMII receiver input compliance mask eye diagram.

#### Table 41. SGMII Receive AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2} = 1.1V \pm 5\%$ .

| Parameter                                          | Symbol          | Min    | Тур | Max               | Unit   | Notes |

|----------------------------------------------------|-----------------|--------|-----|-------------------|--------|-------|

| Deterministic Jitter Tolerance                     | JD              | 0.37   | —   | —                 | UI p-p | 1     |

| Combined Deterministic and Random Jitter Tolerance | JDR             | 0.55   | —   | _                 | UI p-p | 1     |

| Sinusoidal Jitter Tolerance                        | JSIN            | 0.1    | —   | —                 | UI p-p | 1     |

| Total Jitter Tolerance                             | JT              | 0.65   |     | _                 | UI p-p | 1     |

| Bit Error Ratio                                    | BER             | _      | —   | 10 <sup>-12</sup> |        | _     |

| Unit Interval                                      | UI              | 799.92 | 800 | 800.08            | ps     | 2     |

| AC Coupling Capacitor                              | C <sub>TX</sub> | 5      | —   | 200               | nF     | 3     |

Notes:

1. Measured at receiver.

2. Each UI is 800 ps  $\pm$  100 ppm.

3. The external AC coupling capacitor is required. It is recommended to be placed near the device transmitter outputs.

4. See RapidIO 1x/4x LP Serial Physical Layer Specification for interpretation of jitter specifications.

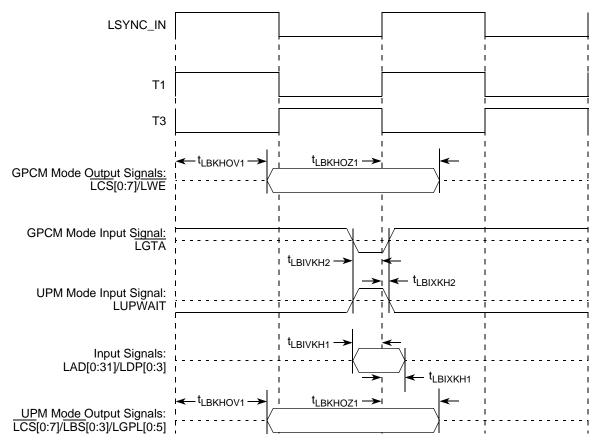

Local Bus Controller (eLBC)

Figure 32. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Enabled)

GPIO

# 14 GPIO

This section describes the DC and AC electrical specifications for the GPIO interface of the MPC8572E.

# 14.1 GPIO DC Electrical Characteristics

Table 56 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 3.3 \text{ V DC}$ .

| Parameter                                                                      | Symbol           | Min                    | Max                    | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------------------------|------|

| Supply voltage 3.3V                                                            | BV <sub>DD</sub> | 3.13                   | 3.47                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 2                      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3                   | 0.8                    | V    |

| Input current<br>( $BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD}$ )         | I <sub>IN</sub>  | _                      | ±5                     | μΑ   |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | —                      | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  |                        | 0.2                    | V    |

Table 56. GPIO DC Electrical Characteristics (3.3 V DC)

Note:

1. Note that the symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

Table 57 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 2.5 \text{ V DC}$ .

Table 57. GPIO DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                      | Symbol           | Min       | Мах                    | Unit |

|--------------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5V                                                            | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 1.70      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3      | 0.7                    | V    |

|                                                                                | I <sub>IH</sub>  | _         | 10                     | μΑ   |

| $(BV_{IN}^{1} = 0 \; V \; or \; BV_{IN} = BV_{DD})$                            | IIL              |           | -15                    |      |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -1 mA) | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> min, I <sub>OL</sub> = 1 mA)     | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

Table 58 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 1.8 \text{ V DC}$ . Table 58. GPIO DC Electrical Characteristics (1.8 V DC)

| Parameter                                                         | Symbol           | Min                     | Мах                     | Unit |

|-------------------------------------------------------------------|------------------|-------------------------|-------------------------|------|

| Supply voltage 1.8V                                               | BV <sub>DD</sub> | 1.71                    | 1.89                    | V    |

| High-level input voltage                                          | V <sub>IH</sub>  | 0.65 x BV <sub>DD</sub> | BV <sub>DD</sub> + 0.3  | V    |

| Low-level input voltage                                           | V <sub>IL</sub>  | -0.3                    | 0.35 x BV <sub>DD</sub> | V    |

| Input current $(BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD})$ | I <sub>IN</sub>  | TBD                     | TBD                     | μΑ   |

| High-level output voltage $(I_{OH} = -100 \ \mu A)$               | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2  | —                       | V    |

| High-level output voltage<br>(I <sub>OH</sub> = -2 mA)            | V <sub>OH</sub>  | BV <sub>DD</sub> - 0.45 | _                       | V    |

| Low-level output voltage $(I_{OL} = 100 \ \mu A)$                 | V <sub>OL</sub>  | _                       | 0.2                     | V    |

| Low-level output voltage<br>(I <sub>OL</sub> = 2 mA)              | V <sub>OL</sub>  | _                       | 0.45                    | V    |

#### Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

# 14.2 GPIO AC Electrical Specifications

Table 59 provides the GPIO input and output AC timing specifications.

#### Table 59. GPIO Input AC Timing Specifications<sup>1</sup>

| Parameter                       | Symbol             | Тур | Unit | Notes |

|---------------------------------|--------------------|-----|------|-------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub> | 20  | ns   | 2     |

Notes:

- 1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYSCLK. Timings are measured at the pin.

- 2. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

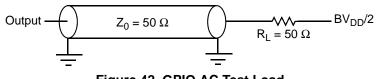

#### Figure 42 provides the AC test load for the GPIO.

Figure 42. GPIO AC Test Load

High-Speed Serial Interfaces (HSSI)

# 15 High-Speed Serial Interfaces (HSSI)

The MPC8572E features two Serializer/Deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. The SerDes1 interface can be used for PCI Express and/or Serial RapidIO data transfers. The SerDes2 is dedicated for SGMII application.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 15.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 43 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SDn\_TX and SDn\_TX) or a receiver input (SDn\_RX and  $\overline{SDn_RX}$ ). Each signal swings between A Volts and B Volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

### 1. Single-Ended Swing

The transmitter output signals and the receiver input signals SDn\_TX, SDn\_TX, SDn\_RX and SDn\_RX each have a peak-to-peak swing of A - B Volts. This is also referred as each signal wire's Single-Ended Swing.

2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn_TX} - V_{\overline{SDn_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

3. Differential Input Voltage, V<sub>ID</sub> (or Differential Input Swing):

The Differential Input Voltage (or Swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{SDn_RX} - V_{\overline{SDn_RX}}$ . The  $V_{ID}$  value can be either positive or negative.

4. Differential Peak Voltage, V<sub>DIFFp</sub>

The peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak Voltage,  $V_{DIFFp} = |A - B|$  Volts.

### 5. Differential Peak-to-Peak, V<sub>DIFFp-p</sub>

Because the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) Volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak-to-Peak Voltage,  $V_{DIFFp-p} = 2*V_{DIFFp} = 2*|(A – B)|$  Volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2*|V_{OD}|$ .

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

| Unaracteristic              | Gymbol              | Min   | Мах  | Onic   | notes                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | _                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | _                                                                                |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | _                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 400   | 400  | ps     | +/- 100 ppm                                                                      |

#### Table 69. Long Run Transmitter AC Timing Specifications—2.5 GBaud

#### Table 70. Long Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | R     | ange | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onit   | Notes                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | —                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | —                                                                                |

| Total Jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | —                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 320   | 320  | ps     | +/- 100 ppm                                                                      |

For each baud rate at which an LP-Serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the transmitter output compliance mask shown in Figure 58 with the parameters specified in Figure 71 when measured at the output pins of the device and the device is driving a 100  $\Omega$  +/-5% differential resistive load. The output eye pattern of an LP-Serial transmitter that implements pre-emphasis (to equalize the link and reduce inter-symbol interference) need only comply with the Transmitter Output Compliance Mask when pre-emphasis is disabled or minimized.

| Characteristic                                     | Symbol          | Ra   | nge               | Unit   | Notes                                                              |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------------|

| Gharacteristic                                     | Symbol          | Min  | Max               | Unit   | NOLES                                                              |

| Differential Input Voltage                         | V <sub>IN</sub> | 200  | 1600              | mV p-p | Measured at receiver                                               |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37 | _                 | UI p-p | Measured at receiver                                               |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55 | _                 | UI p-p | Measured at receiver                                               |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | _                 | UI p-p | Measured at receiver                                               |

| Multiple Input Skew                                | S <sub>MI</sub> | —    | 24                | ns     | Skew at the receiver input<br>between lanes of a multilane<br>link |

| Bit Error Rate                                     | BER             | —    | 10 <sup>-12</sup> | —      | _                                                                  |

| Unit Interval                                      | UI              | 800  | 800               | ps     | +/- 100 ppm                                                        |

#### Table 72. Receiver AC Timing Specifications—1.25 GBaud

Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 59. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

| Characteristic                                     |                 |      | nge               | Unit   | Notes                                                              |  |  |  |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------------|--|--|--|

| Characteristic                                     | Symbol          | Min  | Мах               | Unit   | Notes                                                              |  |  |  |

| Differential Input Voltage                         | V <sub>IN</sub> | 200  | 1600              | mV p-p | Measured at receiver                                               |  |  |  |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37 | —                 | UI p-p | Measured at receiver                                               |  |  |  |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55 | —                 | UI p-p | Measured at receiver                                               |  |  |  |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | —                 | UI p-p | Measured at receiver                                               |  |  |  |

| Multiple Input Skew                                | S <sub>MI</sub> | _    | 24                | ns     | Skew at the receiver input<br>between lanes of a multilane<br>link |  |  |  |

| Bit Error Rate                                     | BER             | —    | 10 <sup>-12</sup> | —      | —                                                                  |  |  |  |

| Unit Interval                                      | UI              | 400  | 400               | ps     | +/– 100 ppm                                                        |  |  |  |

#### Table 73. Receiver AC Timing Specifications—2.5 GBaud

Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 59. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

| Table 76. MPC8572E Pinout Listing (continued) |                                                                                              |                                                                     |          |                  |         |  |  |  |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------|------------------|---------|--|--|--|--|

| Signal                                        | Signal Name                                                                                  | Package Pin Number                                                  | Pin Type | Power<br>Supply  | Notes   |  |  |  |  |

| LGPL0/LFCLE                                   | UPM General Purpose Line 0 /<br>Flash Command Latch Enable                                   | J13                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |  |

| LGPL1/LFALE                                   | UPM General Purpose Line 1/<br>Flash Address Latch Enable                                    | J16                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |  |

| LGPL2/LOE/LFRE                                | GPL2/LOE/LFRE UPM General Purpose Line 2 /<br>Output Enable / Flash Read<br>Enable           |                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |  |  |  |  |

| LGPL3/LFWP                                    | UPM General Purpose Line 3 /<br>Flash Write Protect                                          | K16                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |  |

| LGPL4/LGTA/LUPWAIT/LPBSE<br>/LFRB             | UPM General Purpose Line 4 /<br>Target Ack / Wait / Parity Byte<br>Select / Flash Ready-Busy | L17                                                                 | I/O      | BV <sub>DD</sub> |         |  |  |  |  |

| LGPL5                                         | UPM General Purpose Line 5 /<br>Amux                                                         | B26                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |  |

| LCLK[0:2]                                     | Local Bus Clock                                                                              | F17, F16, A23                                                       | 0        | BV <sub>DD</sub> | _       |  |  |  |  |

| LSYNC_IN                                      | Local Bus DLL Synchronization                                                                | B22                                                                 | Ι        | BV <sub>DD</sub> | —       |  |  |  |  |

| LSYNC_OUT                                     | Local Bus DLL Synchronization                                                                | A21                                                                 | 0        | BV <sub>DD</sub> | —       |  |  |  |  |

|                                               | DMA                                                                                          |                                                                     |          |                  |         |  |  |  |  |

| DMA1_DACK[0:1]                                | DMA Acknowledge                                                                              | W25, U30                                                            | 0        | OV <sub>DD</sub> | 21      |  |  |  |  |

| DMA2_DACK[0]                                  | DMA Acknowledge                                                                              | AA26                                                                | 0        | OV <sub>DD</sub> | 5, 9    |  |  |  |  |

| DMA1_DREQ[0:1]                                | DMA Request                                                                                  | Y29, V27                                                            | Ι        | OV <sub>DD</sub> | —       |  |  |  |  |

| DMA2_DREQ[0]                                  | DMA Request                                                                                  | V29                                                                 | Ι        | OV <sub>DD</sub> | —       |  |  |  |  |

| DMA1_DDONE[0:1]                               | DMA Done                                                                                     | Y28, V30                                                            | 0        | OV <sub>DD</sub> | 5, 9    |  |  |  |  |

| DMA2_DDONE[0]                                 | DMA Done                                                                                     | AA28                                                                | 0        | OV <sub>DD</sub> | 5, 9    |  |  |  |  |

| DMA2_DREQ[2]                                  | DMA Request                                                                                  | M23                                                                 | Ι        | BV <sub>DD</sub> | —       |  |  |  |  |

|                                               | Programmable Inter                                                                           | rupt Controller                                                     |          |                  |         |  |  |  |  |

| UDE0                                          | Unconditional Debug Event<br>Processor 0                                                     | AC25                                                                | Ι        | OV <sub>DD</sub> | _       |  |  |  |  |

| UDE1                                          | Unconditional Debug Event<br>Processor 1                                                     | AA25                                                                | Ι        | OV <sub>DD</sub> | —       |  |  |  |  |

| MCP0                                          | Machine Check Processor 0                                                                    | M28                                                                 | Ι        | OV <sub>DD</sub> | _       |  |  |  |  |

| MCP1                                          | Machine Check Processor 1                                                                    | L28                                                                 | I        | OV <sub>DD</sub> | _       |  |  |  |  |

| IRQ[0:11]                                     | External Interrupts                                                                          | T24, R24, R25, R27,<br>R28, AB27, AB28, P27,<br>R30, AC28, R29, T31 | Ι        | OV <sub>DD</sub> | _       |  |  |  |  |

#### Table 76. MPC8572E Pinout Listing (continued)

Package Description

| Signal     | Signal Name                              | Package Pin Number                                                                                                                                                                                                                                                                                                        | Pin Type | Power<br>Supply     | Notes |

|------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|-------|

| VDD        | Core, L2, Logic Supply                   | L14, M13, M15, M17,<br>N12, N14, N16, N20,<br>N22, P11, P13, P15,<br>P17, P19, P21, P23,<br>R12, R14, R16, R18,<br>R20, R22, T13, T15,<br>T19, T21, T23, U12,<br>U14, U18, U20, U22,<br>V13, V15, V17, V19,<br>V21, W12, W14, W16,<br>W18, W20, W22, Y13,<br>Y15, Y17, Y19, Y21,<br>AA12, AA14, AA16,<br>AA18, AA20, AB13 |          | VDD                 |       |

| SVDD_SRDS1 | SerDes Core 1 Logic Supply<br>(xcorevdd) | C31, D29, E28, E32,<br>F30, G28, G31, H29,<br>K30, L31, M29, N32,<br>P30                                                                                                                                                                                                                                                  | _        | _                   |       |

| SVDD_SRDS2 | SerDes Core 2 Logic Supply<br>(xcorevdd) | AD32, AF31, AG29,<br>AJ32, AK29, AK30                                                                                                                                                                                                                                                                                     | _        | —                   | _     |

| XVDD_SRDS1 | SerDes1 Transceiver Supply<br>(xpadvdd)  | C26, D24, E27, F25,<br>G26, H24, J27, K25,<br>L26, M24, N27                                                                                                                                                                                                                                                               | _        | —                   | _     |

| XVDD_SRDS2 | SerDes2 Transceiver Supply<br>(xpadvdd)  | AD24, AD28, AE26,<br>AF25, AG27, AH24,<br>AJ26                                                                                                                                                                                                                                                                            | _        | —                   | _     |

| AVDD_LBIU  | Local Bus PLL Supply                     | A19                                                                                                                                                                                                                                                                                                                       | _        | —                   | 19    |

| AVDD_DDR   | DDR PLL Supply                           | AM20                                                                                                                                                                                                                                                                                                                      | _        | —                   | 19    |

| AVDD_CORE0 | CPU PLL Supply                           | B18                                                                                                                                                                                                                                                                                                                       | _        | —                   | 19    |

| AVDD_CORE1 | CPU PLL Supply                           | A17                                                                                                                                                                                                                                                                                                                       | _        | —                   | 19    |

| AVDD_PLAT  | Platform PLL Supply                      | AB32                                                                                                                                                                                                                                                                                                                      | _        | —                   | 19    |

| AVDD_SRDS1 | SerDes1 PLL Supply                       | J29                                                                                                                                                                                                                                                                                                                       | _        | _                   | 19    |

| AVDD_SRDS2 | SerDes2 PLL Supply                       | AH29                                                                                                                                                                                                                                                                                                                      | _        | —                   | 19    |

| SENSEVDD   | VDD Sensing Pin                          | N18                                                                                                                                                                                                                                                                                                                       | _        | _                   | 13    |

| SENSEVSS   | GND Sensing Pin                          | P18                                                                                                                                                                                                                                                                                                                       |          |                     | 13    |

|            | Analog S                                 | ignals                                                                                                                                                                                                                                                                                                                    |          |                     |       |

| MVREF1     | SSTL_1.8 Reference Voltage               | C16                                                                                                                                                                                                                                                                                                                       | I        | GV <sub>DD</sub> /2 | _     |

| MVREF2     | SSTL_1.8 Reference Voltage               | AM19                                                                                                                                                                                                                                                                                                                      | I        | GV <sub>DD</sub> /2 | _     |

|            |                                          | 1                                                                                                                                                                                                                                                                                                                         |          |                     |       |

### Table 76. MPC8572E Pinout Listing (continued)

| Signal             | Signal Name                         | Package Pin Number | Pin Type | Power<br>Supply         | Notes |

|--------------------|-------------------------------------|--------------------|----------|-------------------------|-------|

| SD1_IMP_CAL_RX     | SerDes1 Rx Impedance<br>Calibration | B32                | I        | 200Ω<br>(±1%) to<br>GND | _     |

| SD1_IMP_CAL_TX     | SerDes1 Tx Impedance<br>Calibration | T32                | I        | 100Ω<br>(±1%) to<br>GND | _     |

| SD1_PLL_TPA        | SerDes1 PLL Test Point Analog       | J30                | 0        | AVDD_S<br>RDS<br>analog | 17    |

| SD2_IMP_CAL_RX     | SerDes2 Rx Impedance<br>Calibration | AC32               | I        | 200Ω<br>(±1%) to<br>GND | —     |

| SD2_IMP_CAL_TX     | SerDes2 Tx Impedance<br>Calibration | AM32               | I        | 100Ω<br>(±1%) to<br>GND | —     |

| SD2_PLL_TPA        | SerDes2 PLL Test Point Analog       | AH30               | 0        | AVDD_S<br>RDS<br>analog | 17    |

| TEMP_ANODE         | Temperature Diode Anode             | AA31               | _        | internal<br>diode       | 14    |

| TEMP_CATHODE       | Temperature Diode Cathode           | AB31               |          | internal<br>diode       | 14    |

| No Connection Pins |                                     | 1                  |          | 11                      |       |

#### Table 76. MPC8572E Pinout Listing (continued)

#### Table 78. Memory Bus Clocking Specifications

| Characteristic             | Min | Мах | Unit | Notes      |

|----------------------------|-----|-----|------|------------|

| Memory bus clock frequency | 200 | 400 | MHz  | 1, 2, 3, 4 |

Notes:

- 1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," Section 19.3, "e500 Core PLL Ratio," and Section 19.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

- 2. The Memory bus clock refers to the MPC8572E memory controllers' Dn\_MCK[0:5] and Dn\_MCK[0:5] output clocks, running at half of the DDR data rate.

- 3. In synchronous mode, the memory bus clock speed is half the platform clock frequency. In other words, the DDR data rate is the same as the platform (CCB) frequency. If the desired DDR data rate is higher than the platform (CCB) frequency, asynchronous mode must be used.

- 4. In asynchronous mode, the memory bus clock speed is dictated by its own PLL. Refer to Section 19.4, "DDR/DDRCLK PLL Ratio." The memory bus clock speed must be less than or equal to the CCB clock rate which in turn must be less than the DDR data rate.

As a general guideline when selecting the DDR data rate or platform (CCB) frequency, the following procedures can be used:

- Start with the processor core frequency selection;

- After the processor core frequency is determined, select the platform (CCB) frequency from the limited options listed in Table 80 and Table 81;

- Check the CCB to SYSCLK ratio to verify a valid ratio can be choose from Table 79;

- If the desired DDR data rate can be same as the CCB frequency, use the synchronous DDR mode; Otherwise, if a higher DDR data rate is desired, use asynchronous mode by selecting a valid DDR data rate to DDRCLK ratio from Table 82. Note that in asynchronous mode, the DDR data rate must be greater than the platform (CCB) frequency. In other words, running DDR data rate lower than the platform (CCB) frequency in asynchronous mode is not supported by MPC8572E.

- Verify all clock ratios to ensure that there is no violation to any clock and/or ratio specification.

# 19.2 CCB/SYSCLK PLL Ratio

The CCB clock is the clock that drives the e500 core complex bus (CCB), and is also called the platform clock. The frequency of the CCB is set using the following reset signals, as shown in Table 79:

- SYSCLK input signal

- Binary value on LA[29:31] at power up

Note that there is no default for this PLL ratio; these signals must be pulled to the desired values. Also note that, in synchronous mode, the DDR data rate is the determining factor in selecting the CCB bus frequency, because the CCB frequency must equal the DDR data rate. In asynchronous mode, the memory bus clock frequency is decoupled from the CCB bus frequency.

Table 81 describes the clock ratio between e500 Core1 and the e500 core complex bus (CCB). This ratio is determined by the binary value of LWE[0]/LBS[0]/LFWE, UART\_SOUT[1], and READY\_P1 signals at power up, as shown in Table 81.

| <u>Bina</u> ry <u>Value</u> of<br><u>L</u> WE[0]/LBS[0]/<br>LFWE, UART_SOUT[1],<br>READY_P1 Signals | e500 Core1:CCB Clock Ratio | <u>Bina</u> ry <u>Value</u> of<br><u>L</u> WE[0]/LBS[0]/<br>LFWE, UART_SOUT[1],<br>READY_P1 Signals | e500 Core1:CCB Clock Ratio |

|-----------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|----------------------------|

| 000                                                                                                 | Reserved                   | 100                                                                                                 | 2:1                        |

| 001                                                                                                 | Reserved                   | 101                                                                                                 | 5:2 (2.5:1)                |

| 010                                                                                                 | Reserved                   | 110                                                                                                 | 3:1                        |

| 011                                                                                                 | 3:2 (1.5:1)                | 111                                                                                                 | 7:2 (3.5:1)                |

| Table 81. | e500 | Core1 | to | ССВ | <b>Clock Ratio</b> | ) |

|-----------|------|-------|----|-----|--------------------|---|

|           |      |       |    |     | ••••••             |   |

# 19.4 DDR/DDRCLK PLL Ratio

The dual DDR memory controller complexes can be synchronous with, or asynchronous to, the CCB, depending on configuration.

Table 82 describes the clock ratio between the DDR memory controller complexes and the DDR PLL reference clock, DDRCLK, which is not the memory bus clock. The DDR memory controller complexes clock frequency is equal to the DDR data rate.

When synchronous mode is selected, the memory buses are clocked at half the CCB clock rate. The default mode of operation is for the DDR data rate for both DDR controllers to be equal to the CCB clock rate in synchronous mode, or the resulting DDR PLL rate in asynchronous mode.

In asynchronous mode, the DDR PLL rate to DDRCLK ratios listed in Table 82 reflects the DDR data rate to DDRCLK ratio, because the DDR PLL rate in asynchronous mode means the DDR data rate resulting from DDR PLL output.

Note that the DDR PLL reference clock input, DDRCLK, is only required in asynchronous mode. MPC8572E does not support running one DDR controller in synchronous mode and the other in asynchronous mode.

| Binary Value of<br>TSEC_1588_CLK_OUT,<br>TSEC_1588_PULSE_OUT1,<br>TSEC_1588_PULSE_OUT2 Signals | DDR:DDRCLK Ratio |

|------------------------------------------------------------------------------------------------|------------------|

| 000                                                                                            | 3:1              |

| 001                                                                                            | 4:1              |

| 010                                                                                            | 6:1              |

| 011                                                                                            | 8:1              |

| 100                                                                                            | 10:1             |

#### Table 82. DDR Clock Ratio

| Binary Value of<br>TSEC_1588_CLK_OUT,<br>TSEC_1588_PULSE_OUT1,<br>TSEC_1588_PULSE_OUT2 Signals | DDR:DDRCLK Ratio |

|------------------------------------------------------------------------------------------------|------------------|

| 101                                                                                            | 12:1             |

| 110                                                                                            | 14:1             |

| 111                                                                                            | Synchronous mode |

Table 82. DDR Clock Ratio (continued)

# **19.5 Frequency Options**

# **19.5.1** Platform to Sysclk Frequency Options

Table 83 shows the expected frequency values for the platform frequency when using the specified CCB clock to SYSCLK ratio.

| CCB to<br>SYSCLK Ratio |       | SYSCLK (MHz)                  |     |       |     |     |     |        |  |

|------------------------|-------|-------------------------------|-----|-------|-----|-----|-----|--------|--|

|                        | 33.33 | 41.66                         | 50  | 66.66 | 83  | 100 | 111 | 133.33 |  |

|                        |       | Platform /CCB Frequency (MHz) |     |       |     |     |     |        |  |

| 4                      |       |                               |     |       |     | 400 | 444 | 533    |  |

| 5                      |       |                               |     |       | 415 | 500 | 555 |        |  |

| 6                      |       |                               |     | 400   | 498 | 600 |     |        |  |

| 8                      |       |                               | 400 | 533   |     |     | -   |        |  |

| 10                     |       | 417                           | 500 |       | -   |     |     |        |  |

| 12                     | 400   | 500                           | 600 | ]     |     |     |     |        |  |

Table 83. Frequency Options for Platform Frequency

## 19.5.2 Minimum Platform Frequency Requirements for High-Speed Interfaces

Section 4.4.3.6, "I/O Port Selection," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* describes various high-speed interface configuration options. Note that the CCB clock frequency must be considered for proper operation of such interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than or equal to:

See Section 21.1.3.2, "Link Width," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* for PCI Express interface width details. Note that the "PCI Express link width"

# 21 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8572E.

# 21.1 System Clocking

The platform PLL generates the platform clock from the externally supplied SYSCLK input. The frequency ratio between the platform and SYSCLK is selected using the platform PLL ratio configuration bits as described in Section 19.2, "CCB/SYSCLK PLL Ratio." The MPC8572E includes seven PLLs, with the following functions:

- Two core PLLs have ratios that are individually configurable. Each e500 core PLL generates the core clock as a slave to the platform clock. The frequency ratio between the e500 core clock and the platform clock is selected using the e500 PLL ratio configuration bits as described in Section 19.3, "e500 Core PLL Ratio."

- The DDR complex PLL generates the clocking for the DDR controllers.

- The local bus PLL generates the clock for the local bus.

- The PLL for the SerDes1 module is used for PCI Express and Serial Rapid IO interfaces.

- The PLL for the SerDes2 module is used for the SGMII interface.

# 21.2 Power Supply Design

# 21.2.1 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins  $(AV_{DD}PLAT, AV_{DD}CORE0, AV_{DD}CORE1, AV_{DD}DDR, AV_{DD}LBIU, AV_{DD}SRDS1 and AV_{DD}SRDS2 respectively).$  The AV<sub>DD</sub> level should always be equivalent to V<sub>DD</sub>, and preferably these voltages are derived directly from V<sub>DD</sub> through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide independent filter circuits per PLL power supply as illustrated in Figure 62, one to each of the  $AV_{DD}$  pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of the 1023 FC-PBGA footprint, without the inductance of vias.

# 22 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 22.1, "Part Numbers Fully Addressed by this Document."

# 22.1 Part Numbers Fully Addressed by this Document

Table 86 through Table 88 provide the Freescale part numbering nomenclature for the MPC8572E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC                          | nnnn               | е                                       | t                                      | Ι                              | рр                                                                                                                   | ffm                                                                                                                                                                                                                                  | r                                                                                                                           |

|------------------------------|--------------------|-----------------------------------------|----------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Product<br>Code <sup>1</sup> | Part<br>Identifier | Security<br>Engine                      | Temperature                            | Power                          | Package<br>Sphere<br>Type <sup>2</sup>                                                                               | Processor Frequency/<br>DDR Data Rate <sup>3</sup>                                                                                                                                                                                   | Silicon<br>Revision                                                                                                         |

| MPC<br>PPC                   | 8572               | E = Included<br>Blank = Not<br>included | Blank = 0 to 105°C<br>C = −40 to 105°C | Blank =<br>Standard<br>L = Low | PX =<br>Leaded,<br>FC-PBGA<br>VT = Pb-free,<br>FC-PBGA <sup>4</sup><br>VJ = Fully<br>Pb-free<br>FC-PBGA <sup>5</sup> | AVN =<br>1500-MHz processor;<br>800 MT/s DDR data rate<br>AUL =<br>1333-MHz processor;<br>667 MT/s DDR data rate<br>ATL =<br>1200-MHz processor;<br>667 MT/s DDR data rate<br>ARL =<br>1067-MHz processor;<br>667 MT/s DDR data rate | E = Ver. 2.2.1<br>(SVR =<br>0x80E8_0022)<br>SEC included<br>E = Ver. 2.2.1<br>(SVR =<br>0x80E0_0022)<br>SEC not<br>included |

Notes:

- <sup>1</sup> MPC stands for "Qualified."

- PPC stands for "Prototype"

- <sup>2</sup> See Section 18, "Package Description," for more information on the available package types.

- <sup>3</sup> Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

- 4. The VT part number is ROHS-compliant with the permitted exception of the C4 die bumps.

- 5. The VJ part number is entirely lead-free. This includes the C4 die bumps.

**Document Revision History**

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6              | 06/2014 | <ul> <li>Updated Table 76, "MPC8572E Pinout Listing," TDO signal is not driven during HRSET* assertion.</li> <li>In Table 86, "Part Numbering Nomenclature—Rev 2.2.1," added full Pb-free part code.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5              | 01/2011 | <ul> <li>Editorial changes throughout</li> <li>Updated Table 4, "MPC8572E Power Dissipation," to include low power product.</li> <li>In Section 22.1, "Part Numbers Fully Addressed by this Document," defined PPC as "Prototype" and changed table headings to say "Package Sphere Type".</li> <li>Added Table 86, "Part Numbering Nomenclature—Rev 2.2.1."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4              | 06/2010 | <ul> <li>In Section 18.3, "Pinout Listings," updated Table 76 showing GPINOUT power rail as BVDD.</li> <li>Updated Section 14.1, "GPIO DC Electrical Characteristics."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3              | 03/2010 | <ul> <li>In Section 2.1, "Overall DC Electrical Characteristics," changed GPIO power from OVDD to BVDD.</li> <li>In Section 22.1, "Part Numbers Fully Addressed by this Document," added Table 87 for Rev 2.1 silicon.</li> <li>In Section 22.1, "Part Numbers Fully Addressed by this Document," updated Table 88 for Rev 1.1.1 silicon.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2              | 06/2009 | <ul> <li>In Section 3, "Power Characteristics," updated CCB Max to 533MHz for 1200MHz core device in Table 5, "MPC8572EL Power Dissipation."</li> <li>In Section 4.4, "DDR Clock Timing," changed DDRCLK Max to 100MHz. This change was announced in Product Bulletin #13572.</li> <li>Clarified restrictions in Section 4.5, "Platform to eTSEC FIFO Restrictions."</li> <li>In Table 9, "RESET Initialization Timing Specifications," added note 2.</li> <li>Added Section 14, "GPIO."</li> <li>In Section 18.1, "Package Parameters for the MPC8572E FC-PBGA," updated material composition to 63% Sn, 37% Pb.</li> <li>In Section 18.2, "Mechanical Dimensions of the MPC8572E FC-PBGA, updated Figure 61 to correct the package thickness and top view.</li> <li>In Section 19.1, "Clock Ranges," updated CCB Max to 533MHz for 1200MHz core device in Table 77, "MPC8572E Processor Core Clocking Specifications."</li> <li>In Section 19.5.2, "Minimum Platform Frequency Requirements for High-Speed Interfaces," changed minimum CCB clock frequency for proper PCI Express operation.</li> <li>Added LPBSE to description of LGPL4/LGTA/LUPWAIT/LPBSE/LFRB signal in Table 76, "MPC8572E Pinout Listing."</li> <li>Corrected supply voltage for GPIO pins in Table 76, "MPC8572E Pinout Listing."</li> <li>Applied note regarding MDIC in Table 76, "MPC8572E Pinout Listing."</li> <li>Added note for LAD pins in Table 76, "MPC8572E Pinout Listing."</li> <li>Updated Table 88, ",Part Numbering Nomenclature—Rev 1.1.1" with Rev 2.0 and Rev 2.1 part number information. Added note indicating that silicon version 2.0 is available for prototype purposes only and will not be available as a qualified device.</li> </ul> |

| 1              | 08/2008 | • In Section 22.1, "Part Numbers Fully Addressed by this Document," added SVR information in,<br>Table 88 "Part Numbering Nomenclature—Rev 1.1.1," for devices without Security Engine feature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0              | 07/2008 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |