#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Obsolete                                                    |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                              |

| Speed                           | 1.5GHz                                                      |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                       |

| RAM Controllers                 | DDR2, DDR3                                                  |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (4)                                         |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | Cryptography, Random Number Generator                       |

| Package / Case                  | 1023-BFBGA, FCBGA                                           |

| Supplier Device Package         | 1023-FCBGA (33x33)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8572epxavnd |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Regular expression (regex) pattern matching

- Built-in case insensitivity, wildcard support, no pattern explosion

- Cross-packet pattern detection

- Fast pattern database compilation and fast incremental updates

- 16000 patterns, each up to 128 bytes in length

- Patterns can be split into 256 sets, each of which can contain 16 subsets

- Stateful rule engine enables hardware execution of state-aware logic when a pattern is found

- Useful for contextual searches, multi-pattern signatures, or for performing additional checks after a pattern is found

- Capable of capturing and utilizing data from the data stream (such as LENGTH field) and using that information in subsequent pattern searches (for example, positive match only if pattern is detected within the number of bytes specified in the LENGTH field)

- 8192 stateful rules

- Deflate engine

- Supports decompression of DEFLATE compression format including zlib and gzip

- Can work independently or in conjunction with the Pattern Matching Engine (that is decompressed data can be passed directly to the Pattern Matching Engine without further software involvement or memory copying)

- Two Table Lookup Units (TLU)

- Hardware-based lookup engine offloads table searches from e500 cores

- Longest prefix match, exact match, chained hash, and flat data table formats

- Up to 32 tables, with each table up to 16M entries

- 32-, 64-, 96-, or 128-bit keys

- Two I<sup>2</sup>C controllers

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset the I<sup>2</sup>C interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- DUART

- Two 4-wire interfaces (SIN, SOUT,  $\overline{\text{RTS}}$ ,  $\overline{\text{CTS}}$ )

- Programming model compatible with the original 16450 UART and the PC16550D

- Enhanced local bus controller (eLBC)

## 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

## 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| Table 1. Absolute Maximum Ratings | 1 |

|-----------------------------------|---|

|-----------------------------------|---|

|                                       | Characteristic                                                                         | Symbol                                                                                                                                                                                                         | Range                                                                | Unit | Notes |

|---------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------|-------|

| Core supply voltag                    | e                                                                                      | V <sub>DD</sub>                                                                                                                                                                                                | -0.3 to 1.21                                                         | V    |       |

| PLL supply voltage                    | 3                                                                                      | AV <sub>DD</sub>                                                                                                                                                                                               | -0.3 to 1.21                                                         | V    | _     |

| Core power supply                     | ofor SerDes transceivers                                                               | SV <sub>DD</sub>                                                                                                                                                                                               | -0.3 to 1.21                                                         | V    | _     |

| Pad power supply                      | for SerDes transceivers                                                                | XV <sub>DD</sub>                                                                                                                                                                                               | -0.3 to 1.21                                                         | V    | _     |

| DDR SDRAM                             | DDR2 SDRAM Interface                                                                   | GV <sub>DD</sub>                                                                                                                                                                                               | -0.3 to 1.98                                                         | V    | _     |

| Controller I/O<br>supply voltage      | DDR3 SDRAM Interface                                                                   | RAM Interface -0.3 to 1.65   C management interface, MII LV <sub>DD</sub> (for eTSEC1 and eTSEC2) -0.3 to 3.63 -0.3 to 2.75   TV <sub>DD</sub> (for eTSEC3 -0.3 to 3.63 -0.3 to 3.63 -0.3 to 3.63 -0.3 to 3.63 |                                                                      | —    |       |

| Three-speed Ether<br>management volta | rnet I/O, FEC management interface, MII<br>ge                                          |                                                                                                                                                                                                                |                                                                      | V    | 2     |

|                                       |                                                                                        | TV <sub>DD</sub> (for eTSEC3 and eTSEC4, FEC)                                                                                                                                                                  | -0.3 to 3.63<br>-0.3 to 2.75                                         | —    | 2     |

| DUART, system co<br>I/O voltage       | ontrol and power management, I <sup>2</sup> C, and JTAG                                | OV <sub>DD</sub>                                                                                                                                                                                               | -0.3 to 3.63                                                         | V    | —     |

| Local bus and GPI                     | O I/O voltage                                                                          | BV <sub>DD</sub>                                                                                                                                                                                               | -0.3 to 3.63<br>-0.3 to 2.75<br>-0.3 to 1.98                         | V    | _     |

| Input voltage                         | DDR2 and DDR3 SDRAM interface signals                                                  | MV <sub>IN</sub>                                                                                                                                                                                               | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 3     |

|                                       | DDR2 and DDR3 SDRAM interface reference                                                | MV <sub>REF</sub> n                                                                                                                                                                                            | -0.3 to (GV <sub>DD</sub> /2 + 0.3)                                  | V    | —     |

|                                       | Three-speed Ethernet signals                                                           | LV <sub>IN</sub><br>TV <sub>IN</sub>                                                                                                                                                                           | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 3     |

|                                       | Local bus and GPIO signals                                                             | BV <sub>IN</sub>                                                                                                                                                                                               | –0.3 to (BV <sub>DD</sub> + 0.3)                                     | —    | —     |

|                                       | DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                                                                                                                                                                                               | –0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 3     |

| Storage temperatu                     | re range                                                                               | T <sub>STG</sub>                                                                                                                                                                                               | –55 to 150                                                           | °C   | —     |

Notes:

1. Functional operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

The 3.63V maximum is only supported when the port is configured in GMII, MII, RMII or TBI modes; otherwise the 2.75V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

3. (M,L,O)V<sub>IN</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

Electrical Characteristics

## 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                                                | Notes |

|---------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>35                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V                             | 1     |

|                                       | 45(default)<br>45(default)<br>125       | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V<br>BV <sub>DD</sub> = 1.8 V |       |

| DDR2 signal                           | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                                                         | 2     |

| DDR3 signal                           | 20<br>40 (half strength mode)           | GV <sub>DD</sub> = 1.5 V                                                         | 2     |

| eTSEC/10/100 signals                  | 45                                      | L/TV <sub>DD</sub> = 2.5/3.3 V                                                   | _     |

| DUART, system control, JTAG           | 45                                      | OV <sub>DD</sub> = 3.3 V                                                         | —     |

| 12C                                   | 150                                     | OV <sub>DD</sub> = 3.3 V                                                         | —     |

Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the DDR2 or DDR3 interface in half-strength mode is at  $T_i = 105^{\circ}C$  and at  $GV_{DD}$  (min).

# 2.2 Power Sequencing

The MPC8572E requires its power rails to be applied in a specific sequence to ensure proper device operation. These requirements are as follows for power up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, SV<sub>DD</sub>, SV<sub>DD</sub>, SV<sub>DD</sub>, XV<sub>DD</sub>, XV<sub>D</sub>

- 2. GV<sub>DD</sub>

All supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

To guarantee MCKE low during power-on reset, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-on reset, then the sequencing for  $GV_{DD}$  is not required.

| PLL config input setup time with stable SYSCLK before HRESET negation                                           | 100 |   | μs      | — |

|-----------------------------------------------------------------------------------------------------------------|-----|---|---------|---|

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET                     | 4   | _ | SYSCLKs | 1 |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET                   | 2   | _ | SYSCLKs | 1 |

| Maximum valid-to-high imp <u>edance time</u> for actively driven POR configs with respect to negation of HRESET | _   | 5 | SYSCLKs | 1 |

Table 9. RESET Initialization Timing Specifications (continued)

#### Notes:

2. Reset assertion timing requirements for DDR3 DRAMs may differ.

### Table 10 provides the PLL lock times.

| Table | 10. | PLL | Lock | Times |

|-------|-----|-----|------|-------|

|-------|-----|-----|------|-------|

| Parameter/Condition | Symbol | Min | Typical | Max |

|---------------------|--------|-----|---------|-----|

| PLL lock times      | —      | 100 | μs      | _   |

| Local bus PLL       | —      | 50  | μs      |     |

# 6 DDR2 and DDR3 SDRAM Controller

This section describes the DC and AC electrical specifications for the DDR2 and DDR3 SDRAM controller interface of the MPC8572E. Note that the required  $GV_{DD}(typ)$  voltage is 1.8Vor 1.5 V when interfacing to DDR2 or DDR3 SDRAM, respectively.

## 6.1 DDR2 and DDR3 SDRAM Interface DC Electrical Characteristics

Table 11 provides the recommended operating conditions for the DDR SDRAM controller of the MPC8572E when interfacing to DDR2 SDRAM.

| Parameter/Condition                              | Symbol              | Min                  | Мах                         | Unit | Notes |

|--------------------------------------------------|---------------------|----------------------|-----------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>    | 1.71                 | 1.89                        | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> n | $0.49 	imes GV_{DD}$ | $0.51 	imes GV_{DD}$        | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>     | $MV_{REF}n - 0.04$   | $MV_{REF}n + 0.04$          | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>     | $MV_{REF}n + 0.125$  | GV <sub>DD</sub> + 0.3      | V    | _     |

| Input low voltage                                | V <sub>IL</sub>     | -0.3                 | MV <sub>REF</sub> n - 0.125 | V    | _     |

| Output leakage current                           | I <sub>OZ</sub>     | -50                  | 50                          | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>     | -13.4                | _                           | mA   | —     |

| Table 11 | DDR2 SDRAM | Interface DC | Electrical | Characteristics | for GV(tvn) | 1 = 18V |

|----------|------------|--------------|------------|-----------------|-------------|---------|

|          |            | menace DO    | Liccultur  | onaracteristics |             | / I.O V |

<sup>1.</sup> SYSCLK is the primary clock input for the MPC8572E.

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

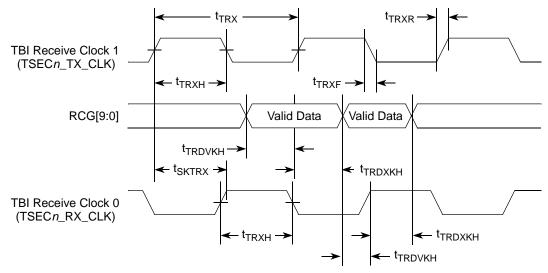

Figure 16 shows the TBI receive AC timing diagram.

Figure 16. TBI Receive AC Timing Diagram

## 8.2.5 TBI Single-Clock Mode AC Specifications

When the eTSEC is configured for TBI modes, all clocks are supplied from external sources to the relevant eTSEC interface. In single-clock TBI mode, when a 125-MHz TBI receive clock is supplied on TSEC*n* pin (no receive clock is used in this mode, whereas for the dual-clock mode this is the PMA1 receive clock). The 125-MHz transmit clock is applied in all TBI modes.

A summary of the single-clock TBI mode AC specifications for receive appears in Table 33.

Table 33. TBI single-clock Mode Receive AC Timing Specification

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5/ 3.3 V ± 5%.

| Parameter/Condition                       | Symbol                               | Min | Тур | Мах | Unit |

|-------------------------------------------|--------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                       | t <sub>TRRX</sub>                    | 7.5 | 8.0 | 8.5 | ns   |

| RX_CLK duty cycle                         | t <sub>TRRH</sub> /t <sub>TRRX</sub> | 40  | 50  | 60  | %    |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>                    | _   | —   | 250 | ps   |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>                    | _   | —   | 1.0 | ns   |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>                    | _   | —   | 1.0 | ns   |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>TRRDVKH</sub>                 | 2.0 | —   | —   | ns   |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>TRRDXKH</sub>                 | 1.0 | —   |     | ns   |

described in Section 21.5, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

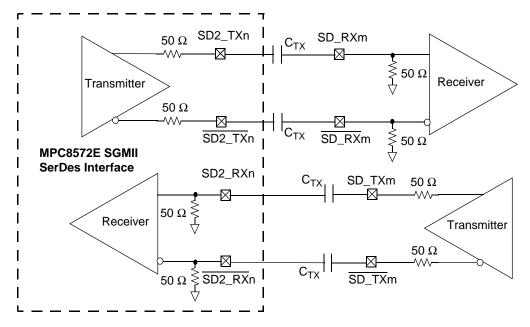

When operating in SGMII mode, the eTSEC EC\_GTX\_CLK125 clock is not required for this port. Instead, SerDes reference clock is required on SD2\_REF\_CLK and SD2\_REF\_CLK pins.

# 8.3.1 DC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 15, "High-Speed Serial Interfaces (HSSI)."

## 8.3.2 AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

Table 37 lists the SGMII SerDes reference clock AC requirements. Note that SD2\_REF\_CLK and SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | _   | 10 (8)  |     | ns    | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles |     |         | 100 | ps    | —     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | —       | 50  | ps    | —     |

### Table 37. SD2\_REF\_CLK and SD2\_REF\_CLK AC Requirements

Note:

1.8 ns applies only when 125 MHz SerDes2 reference clock frequency is selected through cfg\_srds\_sgmii\_refclk during POR.

| Parameter                                     | Symbol                            | Min | Тур | Мах | Unit | Notes |

|-----------------------------------------------|-----------------------------------|-----|-----|-----|------|-------|

| Change in $V_{\mbox{OS}}$ between "0" and "1" | $\Delta V_{OS}$                   | _   | _   | 25  | mV   | —     |

| Output current on short to GND                | I <sub>SA</sub> , I <sub>SB</sub> | _   | _   | 40  | mA   | _     |

Table 38. SGMII DC Transmitter Electrical Characteristics (continued)

Note:

1. This will not align to DC-coupled SGMII.  $XV_{DD\_SRDS2-Typ}$ =1.1 V.

2. |V<sub>OD</sub>| = |V<sub>SD2\_TXn</sub> - V<sub>SD2\_TXn</sub>|. |V<sub>OD</sub>| is also referred as output differential peak voltage. V<sub>TX-DIFFp-p</sub> = 2\*|V<sub>OD</sub>|.

3. The |V<sub>OD</sub>| value shown in the table assumes the following transmit equalization setting in the XMITEQAB (for SerDes 2 lanes A & B) or XMITEQEF (for SerDes 2 lanes E & E) bit field of MPC8572E's SerDes 2 Control Register:

•The MSbit (bit 0) of the above bit field is set to zero (selecting the full V<sub>DD-DIFF-p-p</sub> amplitude - power up default);

•The LSbits (bit [1:3]) of the above bit field is set based on the equalization setting shown in table.

4. V<sub>OS</sub> is also referred to as output common mode voltage.

5.The |V<sub>OD</sub>| value shown in the Typ column is based on the condition of XV<sub>DD\_SRDS2-Typ</sub>=1.1V, no common mode offset variation (V<sub>OS</sub> =550mV), SerDes2 transmitter is terminated with 100-Ω differential load between SD2\_TX[n] and SD2\_TX[n].

Figure 22. 4-Wire AC-Coupled SGMII Serial Link Connection Example

**Ethernet Management Interface Electrical Characteristics**

Table 43. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=3.3 V) (continued)

| Parameter                                                                             | Symbol          | Min  | Мах | Unit | Notes |

|---------------------------------------------------------------------------------------|-----------------|------|-----|------|-------|

| Input low current (LV <sub>DD</sub> /TV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V) | I <sub>IL</sub> | -600 | _   | μΑ   | _     |

Note:

1. EC1\_MDC and EC1\_MDIO operate on LV<sub>DD</sub>.

2. EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

3. Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  and  $TV_{IN}$  symbol referenced in Table 1.

### Table 44. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=2.5 V)

| Parameters                                                         | Symbol                             | Min       | Мах                                      | Unit | Notes  |

|--------------------------------------------------------------------|------------------------------------|-----------|------------------------------------------|------|--------|

| Supply voltage 2.5 V                                               | LV <sub>DD/</sub> TV <sub>DD</sub> | 2.37      | 2.63                                     | V    | 1,2    |

| Output high voltage<br>( $LV_{DD}/TV_{DD} = Min, IOH = -1.0 mA$ )  | V <sub>OH</sub>                    | 2.00      | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _      |

| Output low voltage<br>( $LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA$ ) | V <sub>OL</sub>                    | GND – 0.3 | 0.40                                     | V    | _      |

| Input high voltage                                                 | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$                  | V    | _      |

| Input low voltage                                                  | V <sub>IL</sub>                    | -0.3      | 0.70                                     | V    | _      |

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$          | IIH                                | _         | 10                                       | μA   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                       | IIL                                | -15       | _                                        | μΑ   | 3      |

### Note:

$^1\,$  EC1\_MDC and EC1\_MDIO operate on LV\_DD.

<sup>2</sup> EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

$^3\,$  Note that the symbol V\_{IN}, in this case, represents the LV\_{IN} and TV\_{IN} symbols referenced in Table 1.

## 9.2 MII Management AC Electrical Specifications

Table 45 provides the MII management AC timing specifications. There are three sets of Ethernet management signals (EC1\_MDC and EC1\_MDIO, EC3\_MDC and EC3\_MDIO, EC5\_MDC and EC5\_MDIO). These are not explicitly shown in the table or in the figure following.

### Table 45. MII Management AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%.

| Parameter/Condition            | Symbol <sup>1</sup> | Min   | Тур | Мах                     | Unit | Notes |

|--------------------------------|---------------------|-------|-----|-------------------------|------|-------|

| ECn_MDC frequency              | f <sub>MDC</sub>    | 0.9   | 2.5 | 9.3                     | MHz  | 2, 3  |

| ECn_MDC period                 | t <sub>MDC</sub>    | 107.5 | _   | 1120                    | ns   | —     |

| ECn_MDC clock pulse width high | t <sub>MDCH</sub>   | 32    | _   | _                       | ns   | —     |

| ECn_MDC to ECn_MDIO delay      | t <sub>MDKHDX</sub> | 10    | _   | 16*t <sub>plb_clk</sub> | ns   | 5     |

Table 51. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)—PLL Enabled (continued)

At recommended operating conditions with  $\mathsf{BV}_{\mathsf{DD}}$  of 1.8 V ± 5% (continued)

| Parameter                                                            | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|----------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKH2</sub> | 1.1 | —   | ns   | 3, 4  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>lbotot</sub>  | 1.2 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKHOV1</sub> | —   | 3.2 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKHOV2</sub> | _   | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                             | t <sub>LBKHOV3</sub> | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                    | t <sub>LBKHOV4</sub> | _   | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)           | t <sub>LBKHOX1</sub> | 0.9 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                         | t <sub>LBKHOX2</sub> | 0.9 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)   | t <sub>LBKHOZ1</sub> | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                 | t <sub>LBKHOZ2</sub> |     | 2.6 | ns   | 5     |

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from BV<sub>DD</sub>/2 of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 1.8-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

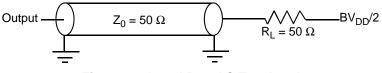

Figure 29 provides the AC test load for the local bus.

Figure 29. Local Bus AC Test Load

High-Speed Serial Interfaces (HSSI)

# 15 High-Speed Serial Interfaces (HSSI)

The MPC8572E features two Serializer/Deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. The SerDes1 interface can be used for PCI Express and/or Serial RapidIO data transfers. The SerDes2 is dedicated for SGMII application.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 15.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 43 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SDn\_TX and SDn\_TX) or a receiver input (SDn\_RX and  $\overline{SDn_RX}$ ). Each signal swings between A Volts and B Volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

### 1. Single-Ended Swing

The transmitter output signals and the receiver input signals SDn\_TX, SDn\_TX, SDn\_RX and SDn\_RX each have a peak-to-peak swing of A - B Volts. This is also referred as each signal wire's Single-Ended Swing.

2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn_TX} - V_{\overline{SDn_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

3. Differential Input Voltage, V<sub>ID</sub> (or Differential Input Swing):

The Differential Input Voltage (or Swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{SDn_RX} - V_{\overline{SDn_RX}}$ . The  $V_{ID}$  value can be either positive or negative.

4. Differential Peak Voltage, V<sub>DIFFp</sub>

The peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak Voltage,  $V_{DIFFp} = |A - B|$  Volts.

### 5. Differential Peak-to-Peak, V<sub>DIFFp-p</sub>

Because the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) Volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak-to-Peak Voltage,  $V_{DIFFp-p} = 2*V_{DIFFp} = 2*|(A – B)|$  Volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2*|V_{OD}|$ .

## 15.2.3 Interfacing With Other Differential Signaling Levels

- With on-chip termination to SGND\_SRDS*n* (xcorevss), the differential reference clocks inputs are HCSL (High-Speed Current Steering Logic) compatible DC-coupled.

- Many other low voltage differential type outputs like LVDS (Low Voltage Differential Signaling) can be used but may need to be AC-coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

- LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, additionally to AC-coupling.

### NOTE

Figure 48 to Figure 51 below are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the MPC8572E SerDes reference clock receiver requirement provided in this document.

| Symbol                            | Parameter                                                                                                         | Min | Nominal | Max           | Units | Comments                                                                                                                                                                                                                                             |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|---------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TX-DC-CM</sub>             | The TX DC<br>Common Mode<br>Voltage                                                                               | 0   | _       | 3.6           | V     | The allowed DC Common Mode voltage under any conditions. See Note 6.                                                                                                                                                                                 |

| I <sub>TX-SHORT</sub>             | TX Short Circuit<br>Current Limit                                                                                 |     | —       | 90            | mA    | The total current the Transmitter can provide when shorted to its ground                                                                                                                                                                             |

| T <sub>TX-IDLE-MIN</sub>          | Minimum time<br>spent in<br>Electrical Idle                                                                       | 50  | _       | _             | UI    | Minimum time a Transmitter must be in Electrical<br>Idle Utilized by the Receiver to start looking for an<br>Electrical Idle Exit after successfully receiving an<br>Electrical Idle ordered set                                                     |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Maximum time to<br>transition to a<br>valid Electrical<br>idle after sending<br>an Electrical Idle<br>ordered set | _   |         | 20            | UI    | After sending an Electrical Idle ordered set, the<br>Transmitter must meet all Electrical Idle<br>Specifications within this time. This is considered a<br>debounce time for the Transmitter to meet Electrical<br>Idle after transitioning from L0. |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Maximum time to<br>transition to valid<br>TX specifications<br>after leaving an<br>Electrical idle<br>condition   | _   |         | 20            | UI    | Maximum time to meet all TX specifications when<br>transitioning from Electrical Idle to sending<br>differential data. This is considered a debounce<br>time for the TX to meet all TX specifications after<br>leaving Electrical Idle               |

| RL <sub>TX-DIFF</sub>             | Differential<br>Return Loss                                                                                       | 12  | —       | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                                         |

| RL <sub>TX-CM</sub>               | Common Mode<br>Return Loss                                                                                        | 6   | —       | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                                         |

| Z <sub>TX-DIFF-DC</sub>           | DC Differential<br>TX Impedance                                                                                   | 80  | 100     | 120           | Ω     | TX DC Differential mode Low Impedance                                                                                                                                                                                                                |

| Z <sub>TX-DC</sub>                | Transmitter DC<br>Impedance                                                                                       | 40  | _       | —             | Ω     | Required TX D+ as well as D- DC Impedance during all states                                                                                                                                                                                          |

| L <sub>TX-SKEW</sub>              | Lane-to-Lane<br>Output Skew                                                                                       |     | —       | 500 +<br>2 UI | ps    | Static skew between any two Transmitter Lanes within a single Link                                                                                                                                                                                   |

| C <sub>TX</sub>                   | AC Coupling<br>Capacitor                                                                                          | 75  | —       | 200           | nF    | All Transmitters shall be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See Note 8.                                                                                                   |

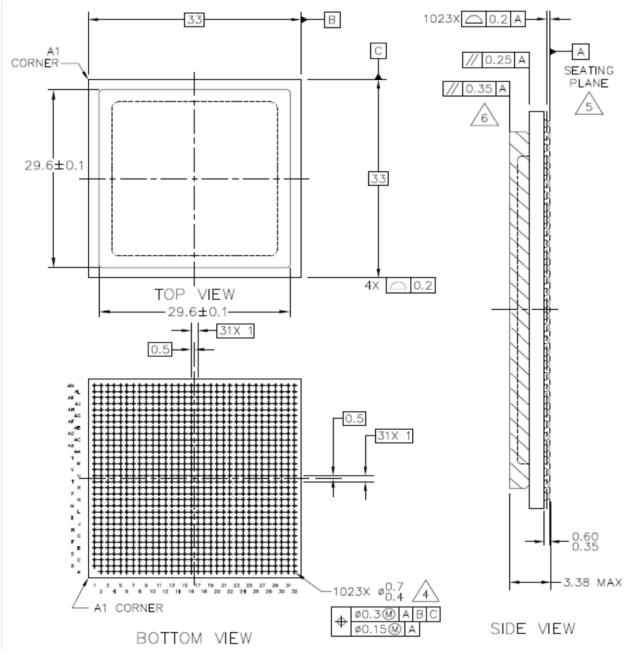

## 18.2 Mechanical Dimensions of the MPC8572E FC-PBGA

Figure 61 shows the mechanical dimensions of the MPC8572E FC-PBGA package with full lid.

Figure 61. Mechanical Dimensions of the MPC8572E FC-PBGA with Full Lid

### NOTES:

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

- 4. Maximum solder ball diameter measured parallel to datum A.

|              |                              | ,                                                                                                                                                                                                                                                                                                                                 |          | Damas            |       |

|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| Signal       | Signal Name                  | Package Pin Number                                                                                                                                                                                                                                                                                                                | Pin Type | Power<br>Supply  | Notes |

| D1_MCAS      | Column Address Strobe        | AC9                                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | _     |

| D1_MRAS      | Row Address Strobe           | AB12                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> |       |

| D1_MCKE[0:3] | Clock Enable                 | M8, L9, T9, N8                                                                                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | 11    |

| D1_MCS[0:3]  | Chip Select                  | AB9, AF10, AB11,<br>AE11                                                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | —     |

| D1_MCK[0:5]  | Clock                        | V7, E13, AH11, Y9,<br>F14, AG10                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | _     |

| D1_MCK[0:5]  | Clock Complements            | Y10, E12, AH12, AA11,<br>F13, AG11                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub> |       |

| D1_MODT[0:3] | On Die Termination           | AD10, AF12, AC10,<br>AE12                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> |       |

| D1_MDIC[0:1] | Driver Impedance Calibration | E15, G14                                                                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | 25    |

|              | DDR SDRAM Mem                | ory Interface 2                                                                                                                                                                                                                                                                                                                   |          |                  |       |

| D2_MDQ[0:63] | Data                         | A6, B7, C5, D5, A7, C8,<br>D8, D6, C4, A3, D3,<br>D2, B4, A4, B1, C1, E3,<br>E1, G2, G6, D1, E4,<br>G5, G3, J4, J2, P4, R5,<br>H3, H1, N5, N3, Y6, Y4,<br>AC3, AD2, V5, W5,<br>AB2, AB3, AD5, AE3,<br>AF6, AG7, AC4, AD4,<br>AF4, AF7, AH5, AJ1,<br>AL2, AM3, AH3, AH6,<br>AM1, AL3, AK5, AL5,<br>AJ7, AK7, AK4, AM4,<br>AL6, AM7 | I/O      | GV <sub>DD</sub> |       |

| D2_MECC[0:7] | Error Correcting Code        | J5, H7, L7, N6, H4, H6,<br>M4, M5                                                                                                                                                                                                                                                                                                 | I/O      | GV <sub>DD</sub> | —     |

| D2_MAPAR_ERR | Address Parity Error         | N1                                                                                                                                                                                                                                                                                                                                | I        | GV <sub>DD</sub> |       |

| D2_MAPAR_OUT | Address Parity Out           | W2                                                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub> |       |

| D2_MDM[0:8]  | Data Mask                    | A5, B3, F4, J1, AA4,<br>AE5, AK1, AM5, K5                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> |       |

| D2_MDQS[0:8] | Data Strobe                  | B6, C2, F5, L4, AB5,<br>AF3, AL1, AM6, L6                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | —     |

| D2_MDQS[0:8] | Data Strobe                  | C7, A2, F2, K3, AA5,<br>AE6, AK2, AJ6, K6                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> |       |

| D2_MA[0:15]  | Address                      | W1, U4, U3, T1, T2, T3,<br>R1, R2, T5, R4, Y3, P1,<br>N2, AF1, M2, M1                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> |       |

### Table 76. MPC8572E Pinout Listing (continued)

| Table 76. MPC8572E Pinout Listing (continued) |

|-----------------------------------------------|

|-----------------------------------------------|

| Signal      | Signal Name                                                                      | Package Pin Number                        | Pin Type | Power<br>Supply            | Notes |

|-------------|----------------------------------------------------------------------------------|-------------------------------------------|----------|----------------------------|-------|

| SD1_RX[7:0] | Receive Data (positive)                                                          | P32, N30, M32, L30,<br>G30, F32, E30, D32 | I        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_RX[7:0] | Receive Data (negative)                                                          | P31, N29, M31, L29,<br>G29, F31, E29, D31 | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[7]   | PCIe1 Tx Data Lane 7 / SRIO or<br>PCIe2 Tx Data Lane 3 / PCIe3<br>TX Data Lane 1 | M26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 |       |

| SD1_TX[6]   | PCIe1 Tx Data Lane 6 / SRIO or<br>PCIe2 Tx Data Lane 2 / PCIe3<br>TX Data Lane 0 | L24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[5]   | PCIe1 Tx Data Lane 5 / SRIO or<br>PCIe2 Tx Data Lane 1                           | K26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[4]   | PCIe1 Tx Data Lane 4 / SRIO or<br>PCIe2 Tx Data Lane 0                           | J24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[3]   | PCIe1 Tx Data Lane 3                                                             | G24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[2]   | PCIe1 Tx Data Lane 2                                                             | F26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[1]   | PCIe1 Tx Data Lane 1]                                                            | E24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[0]   | PCIe1 Tx Data Lane 0                                                             | D26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[7:0] | Transmit Data (negative)                                                         | M27, L25, K27, J25,<br>G25, F27, E25, D27 | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_PLL_TPD | PLL Test Point Digital                                                           | J32                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | 17    |

| SD1_REF_CLK | PLL Reference Clock                                                              | H32                                       | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_REF_CLK | PLL Reference Clock<br>Complement                                                | H31                                       | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| Reserved    | -                                                                                | С29, К32                                  |          | —                          | 26    |

| Reserved    | -                                                                                | С30, К31                                  |          | —                          | 27    |

| Reserved    | -                                                                                | C24, C25, H26, H27                        | _        | —                          | 28    |

| Reserved    | _                                                                                | AL20, AL21                                |          |                            | 29    |

|             | SerDes (x4)                                                                      | SGMII                                     |          |                            |       |

| SD2_RX[3:0] | Receive Data (positive)                                                          | AK32, AJ30, AF30,<br>AE32                 | I        | XV <sub>DD_SR</sub><br>DS2 | _     |

Table 81 describes the clock ratio between e500 Core1 and the e500 core complex bus (CCB). This ratio is determined by the binary value of LWE[0]/LBS[0]/LFWE, UART\_SOUT[1], and READY\_P1 signals at power up, as shown in Table 81.

| <u>Bina</u> ry <u>Value</u> of<br><u>L</u> WE[0]/LBS[0]/<br>LFWE, UART_SOUT[1],<br>READY_P1 Signals | e500 Core1:CCB Clock Ratio | <u>Bina</u> ry <u>Value</u> of<br><u>L</u> WE[0]/LBS[0]/<br>LFWE, UART_SOUT[1],<br>READY_P1 Signals | e500 Core1:CCB Clock Ratio |

|-----------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|----------------------------|

| 000                                                                                                 | Reserved                   | 100                                                                                                 | 2:1                        |

| 001                                                                                                 | Reserved                   | 101                                                                                                 | 5:2 (2.5:1)                |

| 010                                                                                                 | Reserved                   | 110                                                                                                 | 3:1                        |

| 011                                                                                                 | 3:2 (1.5:1)                | 111                                                                                                 | 7:2 (3.5:1)                |

| Table 81. | e500 | Core1 | to | ССВ | <b>Clock Ratio</b> | ) |

|-----------|------|-------|----|-----|--------------------|---|

|           |      |       |    |     | ••••••             |   |

## 19.4 DDR/DDRCLK PLL Ratio

The dual DDR memory controller complexes can be synchronous with, or asynchronous to, the CCB, depending on configuration.

Table 82 describes the clock ratio between the DDR memory controller complexes and the DDR PLL reference clock, DDRCLK, which is not the memory bus clock. The DDR memory controller complexes clock frequency is equal to the DDR data rate.

When synchronous mode is selected, the memory buses are clocked at half the CCB clock rate. The default mode of operation is for the DDR data rate for both DDR controllers to be equal to the CCB clock rate in synchronous mode, or the resulting DDR PLL rate in asynchronous mode.

In asynchronous mode, the DDR PLL rate to DDRCLK ratios listed in Table 82 reflects the DDR data rate to DDRCLK ratio, because the DDR PLL rate in asynchronous mode means the DDR data rate resulting from DDR PLL output.

Note that the DDR PLL reference clock input, DDRCLK, is only required in asynchronous mode. MPC8572E does not support running one DDR controller in synchronous mode and the other in asynchronous mode.

| Binary Value of<br>TSEC_1588_CLK_OUT,<br>TSEC_1588_PULSE_OUT1,<br>TSEC_1588_PULSE_OUT2 Signals | DDR:DDRCLK Ratio |

|------------------------------------------------------------------------------------------------|------------------|

| 000                                                                                            | 3:1              |

| 001                                                                                            | 4:1              |

| 010                                                                                            | 6:1              |

| 011                                                                                            | 8:1              |

| 100                                                                                            | 10:1             |

### Table 82. DDR Clock Ratio

System Design Information

## 21.6 Pull-Up and Pull-Down Resistor Requirements

The MPC8572E requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and MPIC interrupt pins.

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 66. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

The following pins must NOT be pulled down during power-on reset: DMA\_DACK[0:1], EC5\_MDC, HRESET\_REQ, TRIG\_OUT/READY\_P0/QUIESCE, MSRCID[2:4], MDVAL, and ASLEEP. The TEST\_SEL pin must be set to a proper state during POR configuration. For more details, refer to the pinlist table of the individual device.

# 21.7 Output Buffer DC Impedance

The MPC8572E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

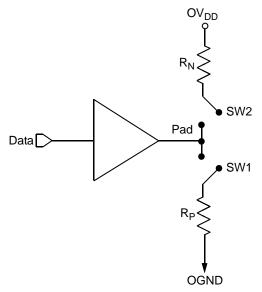

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 64). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

Figure 64. Driver Impedance Measurement

Table 85 summarizes the signal impedance targets. The driver impedances are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet, DUART,<br>Control, Configuration, Power<br>Management | DDR DRAM                                                         | Symbol         | Unit |

|----------------|----------------------------------------------------------------------------|------------------------------------------------------------------|----------------|------|

| R <sub>N</sub> | 45 Target                                                                  | 18 Target (full strength mode)<br>36 Target (half strength mode) | Z <sub>0</sub> | Ω    |

| R <sub>P</sub> | 45 Target                                                                  | 18 Target (full strength mode)<br>36 Target (half strength mode) | Z <sub>0</sub> | Ω    |

Table 85. Impedance Characteristics

**Note:** Nominal supply voltages. See Table 1,  $T_i = 105^{\circ}C$ .

# 21.8 Configuration Pin Muxing

The MPC8572E provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While  $\overline{\text{HRESET}}$  is asserted however, these pins are treated as inputs. The value presented on these pins while  $\overline{\text{HRESET}}$  is asserted, is latched when  $\overline{\text{HRESET}}$  deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Most of these sampled configuration pins are equipped with an on-chip gated resistor of approximately 20 kΩ. This value should permit the 4.7-kΩ resistor to pull the configuration pin to a valid logic low level. The pull-up resistor is enabled only during  $\overline{\text{HRESET}}$  (and for platform /system clocks after  $\overline{\text{HRESET}}$  deassertion to ensure capture of the reset value). When the input receiver is disabled the pull-up is also, thus allowing functional operation of the pin as an output with minimal signal quality or delay disruption. The default value for all configuration bits treated this way has been encoded such that a high voltage level puts the device into the default state and external resistors are needed only when non-default settings are required by the user.

Careful board layout with stubless connections to these pull-down resistors coupled with the large value of the pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

The platform PLL ratio, DDR complex PLL and e500 PLL ratio configuration pins are not equipped with these default pull-up devices.

# 21.9 JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 66. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The  $\overline{\text{TRST}}$  signal is optional in the IEEE Std 1149.1 specification, but it is provided on all processors built on Power Architecture technology. The device requires  $\overline{\text{TRST}}$  to be asserted during power-on reset flow to ensure that the JTAG boundary

System Design Information

## 21.10.3 SerDes 2 Interface (SGMII) Entirely Unused

If the high-speed SerDes 2 interface (SGMII) is not used at all, the unused pin should be terminated as described in this section.

The following pins must be left unconnected (float):

- SD2\_TX[3:0]

- <u>SD2\_TX[3:0]</u>

- Reserved pins: AF26, AF27

The following pins must be connected to XGND\_SRDS2:

- SD2\_RX[3:0]

- $\overline{\text{SD2}_RX}[3:0]$

- SD2\_REF\_CLK

- SD2\_REF\_CLK

The POR configuration pin cfg\_srds\_sgmii\_en on UART\_RTS[1] can be used to power down SerDes 2 block for power saving. Note that both SVDD\_SRDS2 and XVDD\_SRDS2 must remain powered.

## 21.10.4 SerDes 2 Interface (SGMII) Partly Unused

If only part of the high speed SerDes 2 interface (SGMII) pins are used, the remaining high-speed serial I/O pins should be terminated as described in this section.

The following pins must be left unconnected (float):

- SD2\_TX[3:0]

- <u>SD2\_TX[3:0]</u>

- Reserved pins: AF26, AF27

The following pins must be connected to XGND\_SRDS2:

- SD2\_RX[3:0]

- <u>SD2\_RX[3:0]</u>

# 22 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 22.1, "Part Numbers Fully Addressed by this Document."

## 22.1 Part Numbers Fully Addressed by this Document

Table 86 through Table 88 provide the Freescale part numbering nomenclature for the MPC8572E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC                          | nnnn               | е                                       | t                                      | Ι                              | рр                                                                                                                   | ffm                                                                                                                                                                                                                                  | r                                                                                                                           |

|------------------------------|--------------------|-----------------------------------------|----------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Product<br>Code <sup>1</sup> | Part<br>Identifier | Security<br>Engine                      | Temperature                            | Power                          | Package<br>Sphere<br>Type <sup>2</sup>                                                                               | Processor Frequency/<br>DDR Data Rate <sup>3</sup>                                                                                                                                                                                   | Silicon<br>Revision                                                                                                         |

| MPC<br>PPC                   | 8572               | E = Included<br>Blank = Not<br>included | Blank = 0 to 105°C<br>C = −40 to 105°C | Blank =<br>Standard<br>L = Low | PX =<br>Leaded,<br>FC-PBGA<br>VT = Pb-free,<br>FC-PBGA <sup>4</sup><br>VJ = Fully<br>Pb-free<br>FC-PBGA <sup>5</sup> | AVN =<br>1500-MHz processor;<br>800 MT/s DDR data rate<br>AUL =<br>1333-MHz processor;<br>667 MT/s DDR data rate<br>ATL =<br>1200-MHz processor;<br>667 MT/s DDR data rate<br>ARL =<br>1067-MHz processor;<br>667 MT/s DDR data rate | E = Ver. 2.2.1<br>(SVR =<br>0x80E8_0022)<br>SEC included<br>E = Ver. 2.2.1<br>(SVR =<br>0x80E0_0022)<br>SEC not<br>included |

Notes:

- <sup>1</sup> MPC stands for "Qualified."

- PPC stands for "Prototype"

- <sup>2</sup> See Section 18, "Package Description," for more information on the available package types.

- <sup>3</sup> Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

- 4. The VT part number is ROHS-compliant with the permitted exception of the C4 die bumps.

- 5. The VJ part number is entirely lead-free. This includes the C4 die bumps.