Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                         |

| Speed                           | 1.5GHz                                                                 |

| Co-Processors/DSP               | Signal Processing; SPE                                                 |

| RAM Controllers                 | DDR2, DDR3                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                 |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 1023-BFBGA, FCBGA                                                      |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572lvtavne |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing.

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs.

- Interrupt summary registers allow fast identification of interrupt source.

- Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, SSL/TLS, SRTP, 802.16e, and 3GPP

- Four crypto-channels, each supporting multi-command descriptor chains

- Dynamic assignment of crypto-execution units through an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- PKEU—public key execution unit

- RSA and Diffie-Hellman; programmable field size up to 4096 bits

- Elliptic curve cryptography with F<sub>2</sub>m and F(p) modes and programmable field size up to 1023 bits

- DEU—Data Encryption Standard execution unit

- DES, 3DES

- Two key (K1, K2, K1) or three key (K1, K2, K3)

- ECB, CBC and OFB-64 modes for both DES and 3DES

- AESU—Advanced Encryption Standard unit

- Implements the Rijndael symmetric key cipher

- ECB, CBC, CTR, CCM, GCM, CMAC, OFB-128, CFB-128, and LRW modes

- 128-, 192-, and 256-bit key lengths

- AFEU—ARC four execution unit

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- MDEU—message digest execution unit

- SHA-1 with 160-bit message digest

- SHA-2 (SHA-256, SHA-384, SHA-512)

- MD5 with 128-bit message digest

- HMAC with all algorithms

- KEU—Kasumi execution unit

- Implements F8 algorithm for encryption and F9 algorithm for integrity checking

- Also supports A5/3 and GEA-3 algorithms

- RNG—random number generator

- XOR engine for parity checking in RAID storage applications

- CRC execution unit

- CRC-32 and CRC-32C

- Pattern Matching Engine with DEFLATE decompression

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

Table 14 provides the current draw characteristics for MV<sub>REF</sub>n.

Table 14. Current Draw Characteristics for MV<sub>REF</sub> n

| Parameter / Condition                |            | Symbol               | Min | Max  | Unit | Note |

|--------------------------------------|------------|----------------------|-----|------|------|------|

| Current draw for MV <sub>REF</sub> n | DDR2 SDRAM | I <sub>MVREF</sub> n | _   | 1500 | μΑ   | 1    |

|                                      | DDR3 SDRAM |                      |     | 1250 |      |      |

<sup>1.</sup> The voltage regulator for MV<sub>RFF</sub>n must be able to supply up to 1500 μA or 1250 uA current for DDR2 or DDR3, respectively.

### 6.2 DDR2 and DDR3 SDRAM Interface AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM controller interface. The DDR controller supports both DDR2 and DDR3 memories. Note that although the minimum data rate for most off-the-shelf DDR3 DIMMs available is 800 MHz, JEDEC specification does allow the DDR3 to run at the data rate as low as 606 MHz. Unless otherwise specified, the AC timing specifications described in this section for DDR3 is applicable for data rate between 606 MHz and 800 MHz, as long as the DC and AC specifications of the DDR3 memory to be used are compliant to both JEDEC specifications as well as the specifications and requirements described in this MPC8572E hardware specifications document.

### 6.2.1 DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

Table 15, Table 16, and Table 17 provide the input AC timing specifications for the DDR controller when interfacing to DDR2 and DDR3 SDRAM.

Table 15. DDR2 SDRAM Interface Input AC Timing Specifications for 1.8-V Interface At recommended operating conditions with  $GV_{DD}$  of 1.8 V  $\pm$  5%

| Paramet               | er         | Symbol            | Min                | Max                      | Unit | Notes |

|-----------------------|------------|-------------------|--------------------|--------------------------|------|-------|

| AC input low voltage  | >=667 MHz  | V <sub>ILAC</sub> | _                  | MV <sub>REF</sub> n-0.20 | V    | _     |

|                       | <= 533 MHz |                   | _                  | MV <sub>REF</sub> n-0.25 |      |       |

| AC input high voltage | >=667 MHz  | V <sub>IHAC</sub> | $MV_{REF}n + 0.20$ | _                        | V    | _     |

| _                     | <= 533 MHz |                   | $MV_{REF}n + 0.25$ |                          |      |       |

#### Table 16. DDR3 SDRAM Interface Input AC Timing Specifications for 1.5-V Interface

At recommended operating conditions with  $GV_{DD}$  of 1.5 V  $\pm$  5%. DDR3 data rate is between 606 MHz and 800 MHz.

| Parameter             | Symbol            | Min                         | Max                 | Unit | Notes |

|-----------------------|-------------------|-----------------------------|---------------------|------|-------|

| AC input low voltage  | $V_{ILAC}$        | _                           | $MV_{REF}n - 0.175$ | V    | _     |

| AC input high voltage | V <sub>IHAC</sub> | MV <sub>REF</sub> n + 0.175 |                     | V    |       |

# Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications (continued) At recommended operating conditions with $GV_{DD}$ of 1.8 V $\pm$ 5% for DDR2 or 1.5 V $\pm$ 5% for DDR3.

| Parameter                                      | Symbol <sup>1</sup>                         | Min    | Max   | Unit | Notes |

|------------------------------------------------|---------------------------------------------|--------|-------|------|-------|

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        |                                             | 1.95   | _     |      |       |

| ADDR/CMD output hold with respect to MCK       | t <sub>DDKHAX</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        |                                             | 1.95   | _     |      |       |

| MCS[n] output setup with respect to MCK        | t <sub>DDKHCS</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        | t <sub>DDKHCS</sub>                         | 1.95   | _     | ns   | 3     |

| MCS[n] output hold with respect to MCK         | t <sub>DDKHCX</sub>                         |        |       | ns   | 3     |

| 800 MHz                                        |                                             | 0.917  | _     |      |       |

| 667 MHz                                        |                                             | 1.10   | _     |      |       |

| 533 MHz                                        |                                             | 1.48   | _     |      |       |

| 400 MHz                                        |                                             | 1.95   | _     |      |       |

| MCK to MDQS Skew                               | t <sub>DDKHMH</sub>                         |        |       | ns   | 4     |

| 800 MHz                                        |                                             | -0.375 | 0.375 |      |       |

| <= 667 MHz                                     |                                             | -0.6   | 0.6   |      |       |

| MDQ/MECC/MDM output setup with respect to MDQS | t <sub>DDKHDS,</sub> t <sub>DDKLDS</sub>    |        |       | ps   | 5     |

| 800 MHz                                        |                                             | 375    | _     |      |       |

| 667 MHz                                        |                                             | 450    | _     |      |       |

| 533 MHz                                        |                                             | 538    | _     |      |       |

| 400 MHz                                        |                                             | 700    | _     |      |       |

| MDQ/MECC/MDM output hold with respect to MDQS  | t <sub>DDKHDX,</sub><br>t <sub>DDKLDX</sub> |        |       | ps   | 5     |

| 800 MHz                                        |                                             | 375    | _     |      |       |

| 667 MHz                                        |                                             | 450    | _     |      |       |

| •                                              | •                                           | •      | •     | •    |       |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

The Fast Ethernet Controller (FEC) operates in MII mode only, and complies with the AC and DC electrical characteristics specified in this chapter for MII. Note that if FEC is used, eTSEC 3 and 4 are only available in SGMII mode.

### 8.1.1 eTSEC DC Electrical Characteristics

All MII, GMII, RMII, and TBI drivers and receivers comply with the DC parametric attributes specified in Table 23 and Table 24. All RGMII, RTBI and FIFO drivers and receivers comply with the DC parametric attributes specified in Table 24. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

**Parameter** Symbol Unit Min Max **Notes** 1, 2 Supply voltage 3.3 V 3.47 V  $LV_{DD}$ 3.13  $TV_{DD}$ Output high voltage VOH  $LV_{DD}/TV_{DD} + 0.3$ ٧ 2.40  $(LV_{DD}/TV_{DD} = Min, IOH = -4.0 mA)$ Output low voltage VOL **GND** 0.50 ٧  $(LV_{DD}/TV_{DD} = Min, IOL = 4.0 mA)$ Input high voltage  $LV_{DD}/TV_{DD} + 0.3$ 2.0  $V_{IH}$ Input low voltage  $V_{IL}$ -0.3 0.90 ٧ Input high current 40 1, 2,3 μΑ  $I_{IH}$  $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$ 3 Input low current  $I_{IL}$ -600μΑ  $(V_{IN} = GND)$

Table 23. GMII, MII, RMII, and TBI DC Electrical Characteristics

#### Notes:

Table 24. MII, GMII, RMII, RGMII, TBI, RTBI, and FIFO DC Electrical Characteristics

| Parameters                                                                                 | Symbol                             | Min       | Max                     | Unit | Notes |

|--------------------------------------------------------------------------------------------|------------------------------------|-----------|-------------------------|------|-------|

| Supply voltage 2.5 V                                                                       | LV <sub>DD/</sub> TV <sub>DD</sub> | 2.37      | 2.63                    | V    | 1,2   |

| Output high voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, IOH = -1.0 mA)           | V <sub>OH</sub>                    | 2.00      | $LV_{DD}/TV_{DD} + 0.3$ | V    | _     |

| Output low voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>                    | GND - 0.3 | 0.40                    | V    | _     |

| Input high voltage                                                                         | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$ | V    | _     |

| Input low voltage                                                                          | V <sub>IL</sub>                    | -0.3      | 0.70                    | V    | _     |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

<sup>&</sup>lt;sup>1</sup> LV<sub>DD</sub> supports eTSECs 1 and 2.

<sup>&</sup>lt;sup>2</sup> TV<sub>DD</sub> supports eTSECs 3 and 4 or FEC.

$<sup>^3</sup>$  The symbol  $V_{IN}$ , in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1.

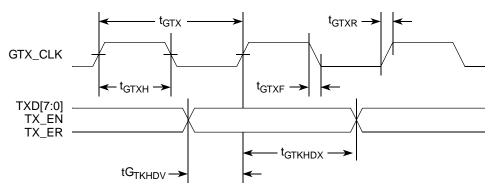

Figure 9 shows the GMII transmit AC timing diagram.

Figure 9. GMII Transmit AC Timing Diagram

### 8.2.2.2 GMII Receive AC Timing Specifications

Table 28 provides the GMII receive AC timing specifications.

#### **Table 28. GMII Receive AC Timing Specifications**

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | _   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | _   | 60  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | _   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0   | _   | _   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>GRXR</sub> <sup>2</sup>      | _   | _   | 1.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>GRXF</sub> <sup>2</sup>      | _   | _   | 1.0 | ns   |

### Note:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)</sub>(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

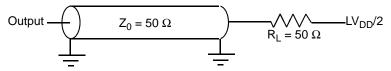

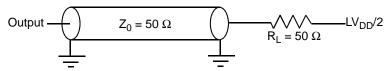

Figure 10 provides the AC test load for eTSEC.

Figure 10. eTSEC AC Test Load

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

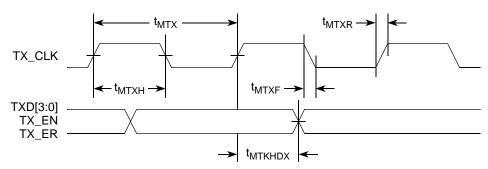

Figure 12 shows the MII transmit AC timing diagram.

Figure 12. MII Transmit AC Timing Diagram

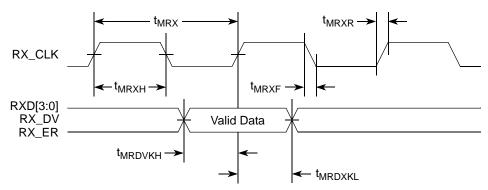

### 8.2.3.2 MII Receive AC Timing Specifications

Table 30 provides the MII receive AC timing specifications.

### Table 30. MII Receive AC Timing Specifications

At recommended operating conditions with LV  $_{DD}$ /TV  $_{DD}$  of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> <sup>2</sup>       | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    | _    | 40  | _   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | _   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>MRXR</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

#### Notes:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

Figure 13 provides the AC test load for eTSEC.

Figure 13. eTSEC AC Test Load

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

Figure 14 shows the MII receive AC timing diagram.

Figure 14. MII Receive AC Timing Diagram

### 8.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

### 8.2.4.1 TBI Transmit AC Timing Specifications

Table 31 provides the TBI transmit AC timing specifications.

### **Table 31. TBI Transmit AC Timing Specifications**

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>            | Min | Тур | Max | Unit |

|--------------------------------------------|--------------------------------|-----|-----|-----|------|

| TCG[9:0] setup time GTX_CLK going high     | t <sub>TTKHDV</sub>            | 2.0 | _   | _   | ns   |

| TCG[9:0] hold time from GTX_CLK going high | t <sub>TTKHDX</sub>            | 1.0 | _   | _   | ns   |

| GTX_CLK rise (20%-80%)                     | t <sub>TTXR</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

| GTX_CLK fall time (80%–20%)                | t <sub>TTXF</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

#### Notes:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state )</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

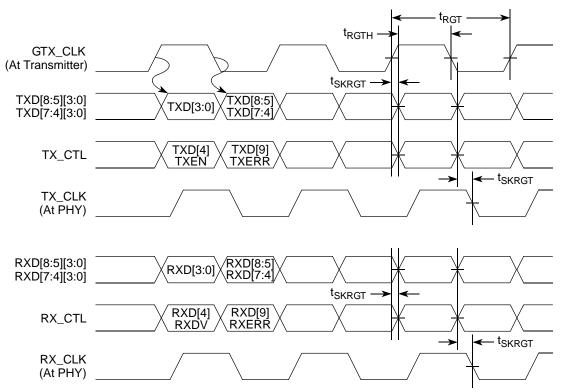

Figure 18 shows the RGMII and RTBI AC timing and multiplexing diagrams.

Figure 18. RGMII and RTBI AC Timing and Multiplexing Diagrams

## 8.2.7 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

### 8.2.7.1 RMII Transmit AC Timing Specifications

Table 35 shows the RMII transmit AC timing specifications.

### **Table 35. RMII Transmit AC Timing Specifications**

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition              | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit |

|----------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period        | t <sub>RMT</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_TX_CLK duty cycle          | t <sub>RMTH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter | t <sub>RMTJ</sub>   | _    | _    | 250  | ps   |

| Rise time TSECn_TX_CLK (20%–80%) | t <sub>RMTR</sub>   | 1.0  | _    | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%–20%) | t <sub>RMTF</sub>   | 1.0  | _    | 2.0  | ns   |

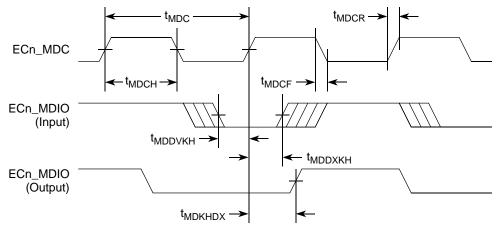

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 45. MII Management AC Timing Specifications (continued)

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%.

| Parameter/Condition            | Symbol <sup>1</sup> | Min | Тур | Max | Unit | Notes |

|--------------------------------|---------------------|-----|-----|-----|------|-------|

| ECn_MDIO to ECn_MDC setup time | t <sub>MDDVKH</sub> | 5   | _   | _   | ns   | _     |

| ECn_MDIO to ECn_MDC hold time  | t <sub>MDDXKH</sub> | 0   | _   | _   | ns   | _     |

| ECn_MDC rise time              | t <sub>MDCR</sub>   | _   | _   | 10  | ns   | 4     |

| ECn_MDC fall time              | t <sub>MDHF</sub>   | _   | _   | 10  | ns   | 4     |

#### Notes:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. This parameter is dependent on the eTSEC system clock speed, which is half of the Platform Frequency (f<sub>CCB</sub>). The actual ECn\_MDC output clock frequency for a specific eTSEC port can be programmed by configuring the MgmtClk bit field of MPC8572E's MIIMCFG register, based on the platform (CCB) clock running for the device. The formula is: Platform Frequency (CCB)/(2\*Frequency Divider determined by MIICFG[MgmtClk] encoding selection). For example, if MIICFG[MgmtClk] = 000 and the platform (CCB) is currently running at 533 MHz, f<sub>MDC</sub> = 533/(2\*4\*8) = 533/64 = 8.3 MHz. That is, for a system running at a particular platform frequency (f<sub>CCB</sub>), the ECn\_MDC output clock frequency can be programmed between maximum f<sub>MDC</sub> = f<sub>CCB</sub>/64 and minimum f<sub>MDC</sub> = f<sub>CCB</sub>/448. Refer to MPC8572E reference manual's MIIMCFG register section for more detail.

- 3. The maximum ECn\_MDC output clock frequency is defined based on the maximum platform frequency for MPC8572E (600 MHz) divided by 64, while the minimum ECn\_MDC output clock frequency is defined based on the minimum platform frequency for MPC8572E (400 MHz) divided by 448, following the formula described in Note 2 above. The typical ECn\_MDC output clock frequency of 2.5 MHz is shown for reference purpose per IEEE 802.3 specification.

- 4. Guaranteed by design.

- 5.  $t_{plb}$  clk is the platform (CCB) clock.

Figure 28 shows the MII management AC timing diagram.

Figure 28. MII Management Interface Timing Diagram

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

#### Table 52. Local Bus General Timing Parameters—PLL Bypassed (continued)

At recommended operating conditions with BV<sub>DD</sub> of 3.3 V  $\pm$  5%

| Parameter                                                            | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|----------------------------------------------------------------------|----------------------|------|------|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKL2</sub> | -1.3 | _    | ns   | 4, 5  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>LBOTOT</sub>  | 1.5  | _    | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKLOV1</sub> | _    | -0.3 | ns   |       |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKLOV2</sub> | _    | -0.1 | ns   | 4     |

| Local bus clock to address valid for LAD                             | t <sub>LBKLOV3</sub> | _    | 0.0  | ns   | 4     |

| Local bus clock to LALE assertion                                    | t <sub>LBKLOV4</sub> | _    | 0.0  | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)           | t <sub>LBKLOX1</sub> | -3.3 | _    | ns   | 4     |

| Output hold from local bus clock for LAD/LDP                         | t <sub>LBKLOX2</sub> | -3.3 | _    | ns   | 4     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)   | t <sub>LBKLOZ1</sub> | _    | 0.2  | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP                 | t <sub>LBKLOZ2</sub> | _    | 0.2  | ns   | 7     |

#### Notes:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to local bus clock for PLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which precedes LCLK by t<sub>I BKHKT</sub>.

- 3. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 4. All signals are measured from BVDD/2 of the rising edge of local bus clock for PLL bypass mode to 0.4 x BVDD of the signal in question for 3.3-V signaling levels.

- 5. Input timings are measured at the pin.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

### **NOTE**

In PLL bypass mode, LCLK[n] is the inverted version of the internal clock with the delay of  $t_{LBKHKT}$ . In this mode, signals are launched at the rising edge of the internal clock and are captured at the falling edge of the internal clock with the exception of  $\overline{LGTA}/LUPWAIT$  (which is captured on the rising edge of the internal clock).

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

**GPIO**

### **14 GPIO**

This section describes the DC and AC electrical specifications for the GPIO interface of the MPC8572E.

### 14.1 GPIO DC Electrical Characteristics

Table 56 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 3.3 \text{ V DC}$ .

Table 56. GPIO DC Electrical Characteristics (3.3 V DC)

| Parameter                                                                                   | Symbol           | Min                    | Max                    | Unit |

|---------------------------------------------------------------------------------------------|------------------|------------------------|------------------------|------|

| Supply voltage 3.3V                                                                         | BV <sub>DD</sub> | 3.13                   | 3.47                   | V    |

| High-level input voltage                                                                    | V <sub>IH</sub>  | 2                      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                     | V <sub>IL</sub>  | -0.3                   | 0.8                    | V    |

| Input current (BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IN</sub>  | _                      | ±5                     | μΑ   |

| High-level output voltage (BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA)                 | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)                | V <sub>OL</sub>  | _                      | 0.2                    | V    |

#### Note:

Table 57 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 2.5 \text{ V DC}$ .

Table 57. GPIO DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                   | Symbol           | Min       | Max                    | Unit |

|-----------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5V                                                         | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level input voltage                                                    | V <sub>IH</sub>  | 1.70      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                     | V <sub>IL</sub>  | -0.3      | 0.7                    | V    |

| Input current                                                               | I <sub>IH</sub>  | _         | 10                     | μΑ   |

| $(BV_{IN}^{1} = 0 \text{ V or } BV_{IN} = BV_{DD})$                         | I <sub>IL</sub>  |           | <b>–15</b>             |      |

| High-level output voltage (BV <sub>DD</sub> = min, I <sub>OH</sub> = -1 mA) | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage (BV <sub>DD</sub> min, I <sub>OL</sub> = 1 mA)     | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

#### Note:

<sup>1.</sup> Note that the symbol  ${\rm BV}_{\rm IN}$ , in this case, represents the  ${\rm BV}_{\rm IN}$  symbol referenced in Table 1.

<sup>1.</sup> The symbol  ${\rm BV}_{\rm IN}$ , in this case, represents the  ${\rm BV}_{\rm IN}$  symbol referenced in Table 1.

SDn\_REF\_CLK

VCROSS MEDIAN +100 mV

VCROSS MEDIAN -100 mV

SDn\_REF\_CLK

SDn\_REF\_CLK

SDn\_REF\_CLK

SDn\_REF\_CLK

Figure 53. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes Reference Clocks is defined by each interface protocol based on application usage. Refer to the following sections for detailed information:

- Section 8.3.2, "AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK"

- Section 16.2, "AC Requirements for PCI Express SerDes Reference Clocks"

- Section 17.2, "AC Requirements for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK"

### 15.2.4.1 Spread Spectrum Clock

SD1\_REF\_CLK/SD1\_REF\_CLK are designed to work with a spread spectrum clock (+0 to -0.5% spreading at 30–33 KHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation should be used.

SD2\_REF\_CLK/SD2\_REF\_CLK are not to be used with, and should not be clocked by, a spread spectrum clock source.

### 15.3 SerDes Transmitter and Receiver Reference Circuits

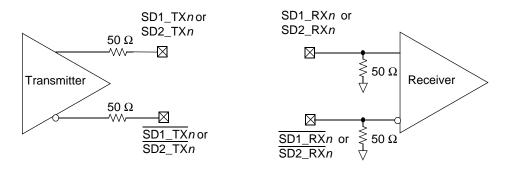

Figure 54 shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 54. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in each interface protocol section below (PCI Express, Serial Rapid IO or SGMII) in this document based on the application usage:

- Section 8.3, "SGMII Interface Electrical Characteristics"

- Section 16, "PCI Express"

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

### **PCI Express**

Table 62. Differential Transmitter (TX) Output Specifications

| Symbol                                       | Parameter                                                                                    | Min    | Nominal | Max    | Units | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|----------------------------------------------------------------------------------------------|--------|---------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                           | Unit Interval                                                                                | 399.88 | 400     | 400.12 | ps    | Each UI is 400 ps ± 300 ppm. UI does not account for Spread Spectrum Clock dictated variations. See Note 1.                                                                                                                                                                                                                                                                                                                                                                                         |

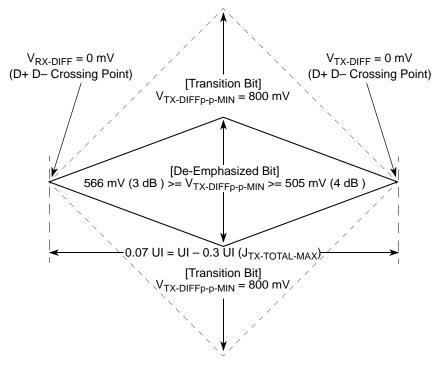

| V <sub>TX-DIFFp-p</sub>                      | Differential<br>Peak-to-Peak<br>Output Voltage                                               | 0.8    | _       | 1.2    | V     | $V_{TX-DIFFp-p} = 2* V_{TX-D+} - V_{TX-D-} $ See Note 2.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>TX-DE-RATIO</sub>                     | De- Emphasized<br>Differential<br>Output Voltage<br>(Ratio)                                  | -3.0   | -3.5    | -4.0   | dB    | Ratio of the $V_{TX-DIFFp-p}$ of the second and following bits after a transition divided by the $V_{TX-DIFFp-p}$ of the first bit after a transition. See Note 2.                                                                                                                                                                                                                                                                                                                                  |

| T <sub>TX-EYE</sub>                          | Minimum TX Eye<br>Width                                                                      | 0.70   | _       | _      | UI    | The maximum Transmitter jitter can be derived as $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.3$ UI. See Notes 2 and 3.                                                                                                                                                                                                                                                                                                                                                                                  |

| T <sub>TX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time<br>between the jitter<br>median and<br>maximum<br>deviation from<br>the median. | _      | _       | 0.15   | UI    | Jitter is defined as the measurement variation of the crossing points ( $V_{TX-DIFFp-p} = 0$ V) in relation to a recovered TX UI. A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI. See Notes 2 and 3.                                                                                                                                 |

| T <sub>TX-RISE</sub> , T <sub>TX-FALL</sub>  | D+/D- TX Output<br>Rise/Fall Time                                                            | 0.125  | _       | _      | UI    | See Notes 2 and 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>TX-CM-ACp</sub>                       | RMS AC Peak<br>Common Mode<br>Output Voltage                                                 | _      | _       | 20     | mV    | $\begin{aligned} & V_{\text{TX-CM-ACp}} = \text{RMS}( V_{\text{TXD+}} + V_{\text{TXD-}} /2 - V_{\text{TX-CM-DC}}) \\ & V_{\text{TX-CM-DC}} = \text{DC}_{(\text{avg})} \text{ of }  V_{\text{TX-D+}} + V_{\text{TX-D-}} /2 \\ & \text{See Note 2} \end{aligned}$                                                                                                                                                                                                                                     |

| V <sub>TX</sub> -CM-DC-ACTIVE-IDLE-DELTA     | Absolute Delta of<br>DC Common<br>Mode Voltage<br>During L0 and<br>Electrical Idle           | 0      | _       | 100    | mV    | $\label{eq:total_loss} \begin{split} & V_{TX\text{-}CM\text{-}DC}\text{ (during L0)} - V_{TX\text{-}CM\text{-}Idle\text{-}DC}\text{ (During Electrical }\\ & _{Idle}  <= 100\text{ mV}\\ &V_{TX\text{-}CM\text{-}DC} = DC_{(avg)}\text{ of } V_{TX\text{-}D\text{+}} + V_{TX\text{-}D\text{-}} /2\text{ [L0]}\\ &V_{TX\text{-}CM\text{-}Idle\text{-}DC} = DC_{(avg)}\text{ of } V_{TX\text{-}D\text{+}} + V_{TX\text{-}D\text{-}} /2\\ &[\text{Electrical Idle}]\\ &\text{See Note 2}. \end{split}$ |

| V <sub>TX-CM-DC-LINE-DELTA</sub>             | Absolute Delta of<br>DC Common<br>Mode between<br>D+ and D-                                  | 0      | _       | 25     | mV    | $\begin{split}  V_{TX\text{-}CM\text{-}DC\text{-}D\text{+}} - V_{TX\text{-}CM\text{-}DC\text{-}D\text{-}}  &<= 25 \text{ mV} \\ V_{TX\text{-}CM\text{-}DC\text{-}D\text{+}} &= DC_{(avg)} \text{ of }  V_{TX\text{-}D\text{+}}  \\ V_{TX\text{-}CM\text{-}DC\text{-}D\text{-}} &= DC_{(avg)} \text{ of }  V_{TX\text{-}D\text{-}}  \\ \text{See Note 2}. \end{split}$                                                                                                                               |

| V <sub>TX-IDLE-DIFFp</sub>                   | Electrical Idle<br>differential Peak<br>Output Voltage                                       | 0      | _       | 20     | mV    | $V_{TX-IDLE-DIFFp} =  V_{TX-IDLE-D+} - V_{TX-IDLE-D-}  \le 20$ mV See Note 2.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>TX-RCV-DETECT</sub>                   | The amount of<br>voltage change<br>allowed during<br>Receiver<br>Detection                   |        | _       | 600    | mV    | The total amount of voltage change that a transmitter can apply to sense whether a low impedance Receiver is present. See Note 6.                                                                                                                                                                                                                                                                                                                                                                   |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

Figure 55. Minimum Transmitter Timing and Voltage Output Compliance Specifications

### 16.4.3 Differential Receiver (RX) Input Specifications

Table 63 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

| Symbol                  | Parameter                                     | Min    | Nominal | Max    | Units | Comments                                                                                                                                                                                        |

|-------------------------|-----------------------------------------------|--------|---------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                      | Unit Interval                                 | 399.88 | 400     | 400.12 | ps    | Each UI is 400 ps ± 300 ppm. UI does not account for Spread Spectrum Clock dictated variations. See Note 1.                                                                                     |

| V <sub>RX-DIFFp-p</sub> | Differential Input<br>Peak-to-Peak<br>Voltage | 0.175  | _       | 1.200  | V     | $V_{RX-DIFFp-p} = 2* V_{RX-D+} - V_{RX-D-} $<br>See Note 2.                                                                                                                                     |

| T <sub>RX-EYE</sub>     | Minimum<br>Receiver Eye<br>Width              | 0.4    | _       | _      | UI    | The maximum interconnect media and Transmitter jitter that can be tolerated by the Receiver can be derived as T <sub>RX-MAX-JITTER</sub> = 1 - T <sub>RX-EYE</sub> = 0.6 UI. See Notes 2 and 3. |

Table 63. Differential Receiver (RX) Input Specifications

Serial RapidIO

# 17.1 <u>DC Requirements</u> for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK

For more information, see Section 15.2, "SerDes Reference Clocks."

# 17.2 <u>AC Requirements for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK</u>

Figure 64lists the AC requirements.

Table 64. SDn REF CLK and SDn REF CLK AC Requirements

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Comments                                                         |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|------------------------------------------------------------------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | _   | 10(8)   | _   | ns    | 8 ns applies only to serial RapidIO with 125-MHz reference clock |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | _       | 80  | ps    | _                                                                |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -40 | _       | 40  | ps    | _                                                                |

### 17.3 Equalization

With the use of high speed serial links, the interconnect media causes degradation of the signal at the receiver. Effects such as Inter-Symbol Interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are as follows:

- A passive high pass filter network placed at the receiver. This is often referred to as passive equalization.

- The use of active circuits in the receiver. This is often referred to as adaptive equalization.

## 17.4 Explanatory Note on Transmitter and Receiver Specifications

AC electrical specifications are given for transmitter and receiver. Long run and short run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to serial RapidIO, as described in Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." The goal of this standard is that electrical designs for Serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

#### Serial RapidIO

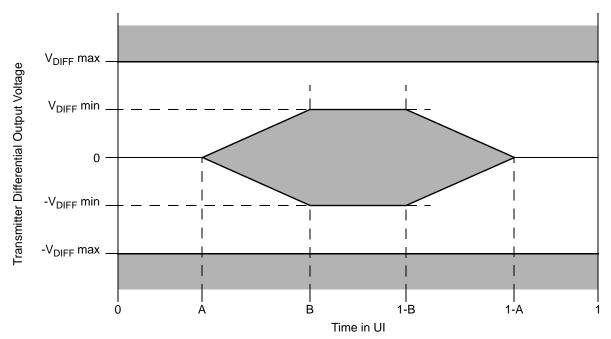

Figure 58. Transmitter Output Compliance Mask

**Table 71. Transmitter Differential Output Eye Diagram Parameters**

| Transmitter Type        | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|-------------------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud short range  | 250                        | 500                        | 0.175  | 0.39   |

| 1.25 GBaud long range   | 400                        | 800                        | 0.175  | 0.39   |

| 2.5 GBaud short range   | 250                        | 500                        | 0.175  | 0.39   |

| 2.5 GBaud long range    | 400                        | 800                        | 0.175  | 0.39   |

| 3.125 GBaud short range | 250                        | 500                        | 0.175  | 0.39   |

| 3.125 GBaud long range  | 400                        | 800                        | 0.175  | 0.39   |

## 17.6 Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance shall result in a differential return loss better that 10 dB and a common mode return loss better than 6 dB from 100 MHz to  $(0.8) \times$  (Baud Frequency). This includes contributions from on-chip circuitry, the chip package and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100 Ohm resistive for differential return loss and 25- $\Omega$  resistive for common mode.

link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. The amount of data represented in the eye shall be adequate to ensure that the bit error ratio is less than  $10^{-12}$ . The eye pattern shall be measured with AC coupling and the compliance template centered at 0 Volts differential. The left and right edges of the template shall be aligned with the mean zero crossing points of the measured data eye. The load for this test shall be  $100 \Omega$  resistive +/- 5% differential to 2.5 GHz.

### 17.8.2 Jitter Test Measurements

For the purpose of jitter measurement, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for jitter measurements is the Continuous Jitter Test Pattern (CJPAT) pattern defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. Jitter shall be measured with AC coupling and at 0 Volts differential. Jitter measurement for the transmitter (or for calibration of a jitter tolerance setup) shall be performed with a test procedure resulting in a BER curve such as that described in Annex 48B of IEEE 802.3ae.

### 17.8.3 Transmit Jitter

Transmit jitter is measured at the driver output when terminated into a load of  $100 \Omega$  resistive +/- 5% differential to 2.5 GHz.

### 17.8.4 Jitter Tolerance

Jitter tolerance is measured at the receiver using a jitter tolerance test signal. This signal is obtained by first producing the sum of deterministic and random jitter defined in Section 17.6, "Receiver Specifications," and then adjusting the signal amplitude until the data eye contacts the 6 points of the minimum eye opening of the receive template shown in Figure 60 and Table 75. Note that for this to occur, the test signal must have vertical waveform symmetry about the average value and have horizontal symmetry (including jitter) about the mean zero crossing. Eye template measurement requirements are as defined above. Random jitter is calibrated using a high pass filter with a low frequency corner at 20 MHz and a 20 dB/decade roll-off below this. The required sinusoidal jitter specified in Section 17.6, "Receiver Specifications," is then added to the signal and the test load is replaced by the receiver being tested.

# 18 Package Description

This section describes package parameters, pin assignments, and dimensions.

### 21.6 Pull-Up and Pull-Down Resistor Requirements

The MPC8572E requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and MPIC interrupt pins.

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 66. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

The following pins must NOT be pulled down during power-on reset:  $\overline{DMA\_DACK[0:1]}$ , EC5\_MDC,  $\overline{HRESET\_REQ}$ , TRIG\_OUT/READY\_P0/QUIESCE, MSRCID[2:4], MDVAL, and ASLEEP. The  $\overline{TEST\_SEL}$  pin must be set to a proper state during POR configuration. For more details, refer to the pinlist table of the individual device.

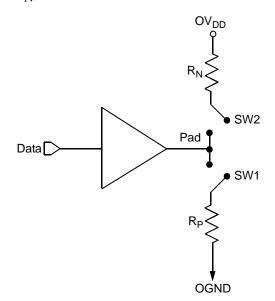

### 21.7 Output Buffer DC Impedance

The MPC8572E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for I<sup>2</sup>C).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 64). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

Figure 64. Driver Impedance Measurement

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

#### **System Design Information**

logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert TRST during the power-on reset flow. Simply tying TRST to HRESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 66 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

The COP interface has a standard header, shown in Figure 65, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; so emulator vendors have issued many different pin numbering schemes. Some COP headers are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom. Still others number the pins counter-clockwise from pin 1 (as with an IC). Regardless of the numbering scheme, the signal placement recommended in Figure 65 is common to all known emulators.

### 21.9.1 Termination of Unused Signals

If the JTAG interface and COP header is not used, Freescale recommends the following connections:

- TRST should be tied to HRESET through a 0 kΩ isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 66. If this is not possible, the isolation resistor allows future access to TRST in case a JTAG interface may need to be wired onto the system in future debug situations.

- No pull-up/pull-down is required for TDI, TMS, TDO or TCK.

**System Design Information**

### 21.10.3 SerDes 2 Interface (SGMII) Entirely Unused

If the high-speed SerDes 2 interface (SGMII) is not used at all, the unused pin should be terminated as described in this section.

The following pins must be left unconnected (float):

- SD2\_TX[3:0]

- $\overline{SD2} \overline{TX}[3:0]$

- Reserved pins: AF26, AF27

The following pins must be connected to XGND SRDS2:

- SD2\_RX[3:0]

- SD2\_RX[3:0]

- SD2\_REF\_CLK

- SD2\_REF\_CLK

The POR configuration pin cfg\_srds\_sgmii\_en on UART\_RTS[1] can be used to power down SerDes 2 block for power saving. Note that both SVDD\_SRDS2 and XVDD\_SRDS2 must remain powered.

### 21.10.4 SerDes 2 Interface (SGMII) Partly Unused

If only part of the high speed SerDes 2 interface (SGMII) pins are used, the remaining high-speed serial I/O pins should be terminated as described in this section.

The following pins must be left unconnected (float):

- SD2\_TX[3:0]

- SD2\_TX[3:0]

- Reserved pins: AF26, AF27

The following pins must be connected to XGND\_SRDS2:

- SD2 RX[3:0]

- $\overline{SD2}RX[3:0]$