# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                        |

| Speed                           | 1.2GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR2, DDR3                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 1023-BFBGA, FCBGA                                                     |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572pxatlb |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- CRC generation and verification of inbound/outbound frames

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- Two MII management interfaces for control and status

- Ability to force allocation of header information and buffer descriptors into L2 cache

- 10/100 Fast Ethernet controller (FEC) management interface

- 10/100 Mbps full and half-duplex IEEE 802.3 MII for system management

- Note: When enabled, the FEC occupies eTSEC3 and eTSEC4 parallel interface signals. In such a mode, eTSEC3 and eTSEC4 are only available through SGMII interfaces.

- OCeaN switch fabric

- Full crossbar packet switch

- Reorders packets from a source based on priorities

- Reorders packets to bypass blocked packets

- Implements starvation avoidance algorithms

- Supports packets with payloads of up to 256 bytes

- Two integrated DMA controllers

- Four DMA channels per controller

- All channels accessible by the local masters

- Extended DMA functions (advanced chaining and striding capability)

- Misaligned transfer capability

- Interrupt on completed segment, link, list, and error

- Supports transfers to or from any local memory or I/O port

- Selectable hardware-enforced coherency (snoop/no snoop)

- Ability to start and flow control up to 4 (both Channel 0 and 1 for each DMA Controller) of the 8 total DMA channels from external 3-pin interface by the remote masters

- The Channel 2 of DMA Controller 2 is only allowed to initiate and start a DMA transfer by the remote master, because only one of the 3-external pins (DMA2\_DREQ[2]) is made available

Electrical Characteristics

# 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values shown are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

| Characteristic                                                                                                    |                                                          | Symbol                               | Recommended Value                                  | Unit | Notes |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------|----------------------------------------------------|------|-------|

| Core supply voltage                                                                                               |                                                          | V <sub>DD</sub>                      | 1.1 V ± 55 mV                                      | V    |       |

| PLL supply voltage                                                                                                |                                                          | AV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | 1     |

| Core power supply for                                                                                             | or SerDes transceivers                                   | SV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    |       |

| Pad power supply fo                                                                                               | r SerDes transceivers                                    | XV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    |       |

| DDR SDRAM                                                                                                         | DDR2 SDRAM Interface                                     | GV <sub>DD</sub>                     | 1.8 V ± 90 mV                                      | V    |       |

| Controller I/O<br>supply voltage                                                                                  | DDR3 SDRAM Interface                                     |                                      | 1.5 V ± 75 mV                                      |      |       |

| Three-speed Ethernet I/O voltage                                                                                  |                                                          | LV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | 4     |

|                                                                                                                   |                                                          | TV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   |      | 4     |

| DUART, system con                                                                                                 | trol and power management, $I^2C$ , and JTAG I/O voltage | OV <sub>DD</sub>                     | 3.3 V ± 165 mV                                     | V    | 3     |

| Local bus and GPIO                                                                                                | I/O voltage                                              | BV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV<br>1.8 V ± 90 mV  | V    | _     |

| Input voltage                                                                                                     | DDR2 and DDR3 SDRAM Interface signals                    | MV <sub>IN</sub>                     | GND to GV <sub>DD</sub>                            | V    | 2     |

|                                                                                                                   | DDR2 and DDR3 SDRAM Interface reference                  | MV <sub>REF</sub> n                  | GV <sub>DD</sub> /2 ± 1%                           | V    | _     |

|                                                                                                                   | Three-speed Ethernet signals                             | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V    | 4     |

|                                                                                                                   | Local bus and GPIO signals                               | BVIN                                 | GND to BV <sub>DD</sub>                            | V    |       |

| Local bus, DUART, SYSCLK, Serial RapidIO, system control and power management, I <sup>2</sup> C, and JTAG signals |                                                          | OV <sub>IN</sub>                     | GND to OV <sub>DD</sub>                            | V    | 3     |

| Junction temperature                                                                                              | e range                                                  | TJ                                   | 0 to 105                                           | °C   | _     |

## **Table 2. Recommended Operating Conditions**

#### Notes:

- 1. This voltage is the input to the filter discussed in Section 21.2.1, "PLL Power Supply Filtering," and not necessarily the voltage at the AV<sub>DD</sub> pin, that may be reduced from V<sub>DD</sub> by the filter.

- 2. Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. Caution: L/TV<sub>IN</sub> must not exceed L/TV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

| PLL config input setup time with stable SYSCLK before HRESET negation                                           | 100 |   | μs      | — |

|-----------------------------------------------------------------------------------------------------------------|-----|---|---------|---|

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET                     | 4   | _ | SYSCLKs | 1 |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET                   | 2   | _ | SYSCLKs | 1 |

| Maximum valid-to-high imp <u>edance time</u> for actively driven POR configs with respect to negation of HRESET | _   | 5 | SYSCLKs | 1 |

Table 9. RESET Initialization Timing Specifications (continued)

#### Notes:

2. Reset assertion timing requirements for DDR3 DRAMs may differ.

## Table 10 provides the PLL lock times.

| Table | 10. | PLL | Lock | Times |

|-------|-----|-----|------|-------|

|-------|-----|-----|------|-------|

| Parameter/Condition | Symbol | Min | Typical | Max |

|---------------------|--------|-----|---------|-----|

| PLL lock times      | —      | 100 | μs      | _   |

| Local bus PLL       | —      | 50  | μs      |     |

# 6 DDR2 and DDR3 SDRAM Controller

This section describes the DC and AC electrical specifications for the DDR2 and DDR3 SDRAM controller interface of the MPC8572E. Note that the required  $GV_{DD}(typ)$  voltage is 1.8Vor 1.5 V when interfacing to DDR2 or DDR3 SDRAM, respectively.

# 6.1 DDR2 and DDR3 SDRAM Interface DC Electrical Characteristics

Table 11 provides the recommended operating conditions for the DDR SDRAM controller of the MPC8572E when interfacing to DDR2 SDRAM.

| Parameter/Condition                              | Symbol              | Min                  | Мах                                | Unit | Notes |

|--------------------------------------------------|---------------------|----------------------|------------------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>    | 1.71                 | 1.89                               | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> n | $0.49 	imes GV_{DD}$ | $0.51 	imes GV_{DD}$               | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>     | $MV_{REF}n - 0.04$   | $MV_{REF}n + 0.04$                 | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>     | $MV_{REF}n + 0.125$  | GV <sub>DD</sub> + 0.3             | V    | _     |

| Input low voltage                                | V <sub>IL</sub>     | -0.3                 | MV <sub>REF</sub> <i>n</i> – 0.125 | V    | _     |

| Output leakage current                           | I <sub>OZ</sub>     | -50                  | 50                                 | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>     | -13.4                | _                                  | mA   | —     |

| Table 11 | DDR2 SDRAM | Interface DC | Electrical | Characteristics | for GV(tvn) | 1 = 18V |

|----------|------------|--------------|------------|-----------------|-------------|---------|

|          |            | menace DO    | Liccultur  | onaracteristics |             | / I.O V |

<sup>1.</sup> SYSCLK is the primary clock input for the MPC8572E.

#### DDR2 and DDR3 SDRAM Controller

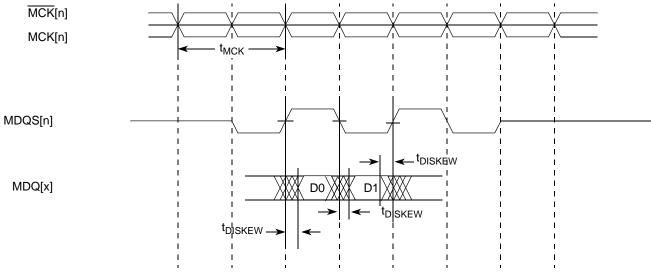

## Table 17. DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                         | Symbol              | Min  | Max | Unit | Notes |

|-----------------------------------|---------------------|------|-----|------|-------|

| Controller Skew for MDQS—MDQ/MECC | t <sub>CISKEW</sub> | —    | _   | ps   | 1, 2  |

| 800 MHz                           | _                   | -200 | 200 | —    | —     |

| 667 MHz                           | _                   | -240 | 240 | —    | —     |

| 533 MHz                           | _                   | -300 | 300 | —    | —     |

| 400 MHz                           | _                   | -365 | 365 |      | —     |

Note:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called tDISKEW. This can be determined by the following equation: tDISKEW =+/-(T/4 – abs(tCISKEW)) where T is the clock period and abs(tCISKEW) is the absolute value of tCISKEW.

Figure 3 shows the DDR2 and DDR3 SDRAM interface input timing diagram.

Figure 3. DDR2 and DDR3 SDRAM Interface Input Timing Diagram

# 6.2.2 DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications

Table 18 contains the output AC timing targets for the DDR2 and DDR3 SDRAM interface.

## Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter                                 | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|-------------------------------------------|---------------------|-----|-----|------|-------|

| MCK[n] cycle time                         | t <sub>MCK</sub>    | 2.5 | 5   | ns   | 2     |

| ADDR/CMD output setup with respect to MCK | t <sub>DDKHAS</sub> |     |     | ns   | 3     |

# NP

#### DDR2 and DDR3 SDRAM Controller

Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications (continued)

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter           | Symbol <sup>1</sup> | Min                             | Мах                                                       | Unit | Notes |

|---------------------|---------------------|---------------------------------|-----------------------------------------------------------|------|-------|

| 533 MHz             |                     | 538                             | —                                                         |      |       |

| 400 MHz             |                     | 700                             | —                                                         |      |       |

| MDQS preamble start | t <sub>DDKHMP</sub> |                                 |                                                           | ns   | 6     |

| 800 MHz             |                     | $-0.5 \times t_{MCK} - 0.375$   | $\begin{array}{c} -0.5\times t_{MCK}\\ +0.375\end{array}$ |      |       |

| <= 667 MHz          |                     | $-0.5\times t_{\text{MCK}}-0.6$ | $-0.5 	imes t_{MCK}$ +0.6                                 |      |       |

| MDQS epilogue end   | t <sub>DDKHME</sub> |                                 |                                                           | ns   | 6     |

| 800 MHz             |                     | -0.375                          | 0.375                                                     |      |       |

| <= 667 MHz          | t <sub>DDKHME</sub> | -0.6                            | 0.6                                                       | ns   | 6     |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub>

(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the MDQS override bits (called WR\_DATA\_DELAY) in the TIMING\_CFG\_2 register. This typically be set to the same delay as in DDR\_SDRAM\_CLK\_CNTL[CLK\_ADJUST]. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8572E PowerQUICC<sup>TM</sup> III Integrated Host Processor Family Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

## NOTE

For the ADDR/CMD setup and hold specifications in Table 18, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

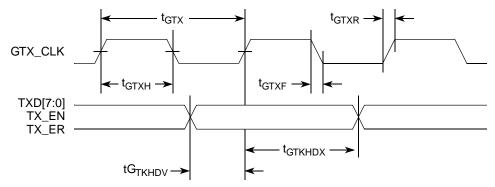

Figure 9 shows the GMII transmit AC timing diagram.

Figure 9. GMII Transmit AC Timing Diagram

# 8.2.2.2 GMII Receive AC Timing Specifications

Table 28 provides the GMII receive AC timing specifications.

## Table 28. GMII Receive AC Timing Specifications

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | —   | 8.0 | —   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | —   | 60  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | —   | —   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0   | —   | —   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>GRXR</sub> <sup>2</sup>      | —   | —   | 1.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>GRXF</sub> 2                 | _   | —   | 1.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

2. Guaranteed by design.

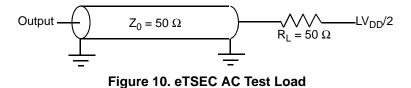

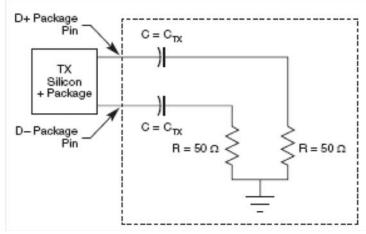

Figure 10 provides the AC test load for eTSEC.

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

# Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

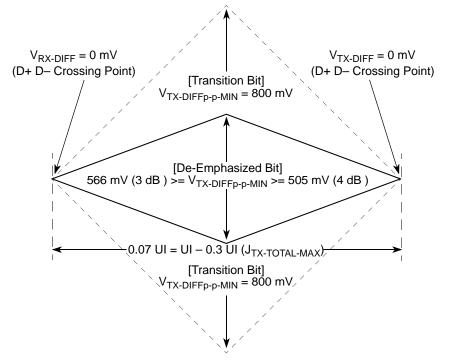

Figure 24. SGMII Receiver Input Compliance Mask

Figure 25. SGMII AC Test/Measurement Load

**Ethernet Management Interface Electrical Characteristics**

Table 43. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=3.3 V) (continued)

| Parameter                                                                             | Symbol          | Min  | Мах | Unit | Notes |

|---------------------------------------------------------------------------------------|-----------------|------|-----|------|-------|

| Input low current (LV <sub>DD</sub> /TV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V) | I <sub>IL</sub> | -600 | _   | μΑ   | _     |

Note:

1. EC1\_MDC and EC1\_MDIO operate on LV<sub>DD</sub>.

2. EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

3. Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  and  $TV_{IN}$  symbol referenced in Table 1.

## Table 44. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=2.5 V)

| Parameters                                                         | Symbol                             | Min       | Мах                                      | Unit | Notes  |

|--------------------------------------------------------------------|------------------------------------|-----------|------------------------------------------|------|--------|

| Supply voltage 2.5 V                                               | LV <sub>DD/</sub> TV <sub>DD</sub> | 2.37      | 2.63                                     | V    | 1,2    |

| Output high voltage<br>( $LV_{DD}/TV_{DD} = Min, IOH = -1.0 mA$ )  | V <sub>OH</sub>                    | 2.00      | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _      |

| Output low voltage<br>( $LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA$ ) | V <sub>OL</sub>                    | GND – 0.3 | 0.40                                     | V    | _      |

| Input high voltage                                                 | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$                  | V    | _      |

| Input low voltage                                                  | V <sub>IL</sub>                    | -0.3      | 0.70                                     | V    | _      |

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$          | IIH                                | _         | 10                                       | μA   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                       | IIL                                | -15       | _                                        | μΑ   | 3      |

## Note:

$^1\,$  EC1\_MDC and EC1\_MDIO operate on LV\_DD.

<sup>2</sup> EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

$^3\,$  Note that the symbol V\_{IN}, in this case, represents the LV\_{IN} and TV\_{IN} symbols referenced in Table 1.

# 9.2 MII Management AC Electrical Specifications

Table 45 provides the MII management AC timing specifications. There are three sets of Ethernet management signals (EC1\_MDC and EC1\_MDIO, EC3\_MDC and EC3\_MDIO, EC5\_MDC and EC5\_MDIO). These are not explicitly shown in the table or in the figure following.

## Table 45. MII Management AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%.

| Parameter/Condition            | Symbol <sup>1</sup> | Min   | Тур | Мах                     | Unit | Notes |

|--------------------------------|---------------------|-------|-----|-------------------------|------|-------|

| ECn_MDC frequency              | f <sub>MDC</sub>    | 0.9   | 2.5 | 9.3                     | MHz  | 2, 3  |

| ECn_MDC period                 | t <sub>MDC</sub>    | 107.5 | _   | 1120                    | ns   | —     |

| ECn_MDC clock pulse width high | t <sub>MDCH</sub>   | 32    | _   | _                       | ns   | —     |

| ECn_MDC to ECn_MDIO delay      | t <sub>MDKHDX</sub> | 10    | _   | 16*t <sub>plb_clk</sub> | ns   | 5     |

#### Local Bus Controller (eLBC)

Table 48 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 1.8 V$  DC.

| Parameter                                                              | Symbol           | Min                     | Мах                     | Unit |

|------------------------------------------------------------------------|------------------|-------------------------|-------------------------|------|

| Supply voltage 1.8V                                                    | BV <sub>DD</sub> | 1.71                    | 1.89                    | V    |

| High-level input voltage                                               | V <sub>IH</sub>  | 0.65 x BV <sub>DD</sub> | BV <sub>DD</sub> + 0.3  | V    |

| Low-level input voltage                                                | V <sub>IL</sub>  | -0.3                    | 0.35 x BV <sub>DD</sub> | V    |

| Input current<br>( $BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD}$ ) | I <sub>IN</sub>  | TBD                     | TBD                     | μA   |

| High-level output voltage<br>(I <sub>OH</sub> = −100 μA)               | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2  | _                       | V    |

| High-level output voltage $(I_{OH} = -2 \text{ mA})$                   | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.45 | _                       | V    |

| Low-level output voltage<br>(I <sub>OL</sub> = 100 μA)                 | V <sub>OL</sub>  | _                       | 0.2                     | V    |

| Low-level output voltage<br>(I <sub>OL</sub> = 2 mA)                   | V <sub>OL</sub>  | _                       | 0.45                    | V    |

Table 48. Local Bus DC Electrical Characteristics (1.8 V DC)

#### Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

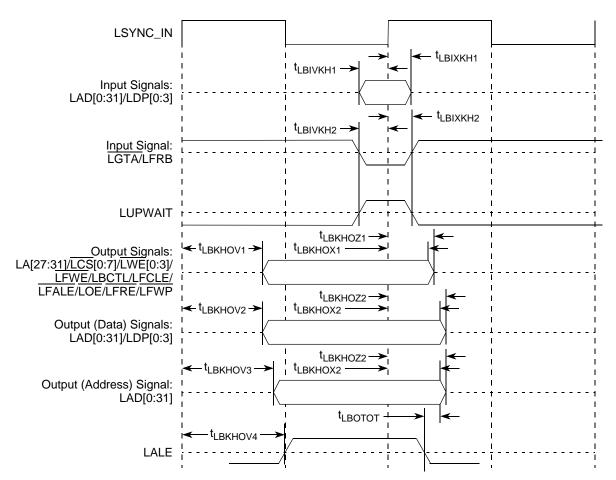

# **10.2 Local Bus AC Electrical Specifications**

Table 49 describes the general timing parameters of the local bus interface at  $BV_{DD} = 3.3 \text{ V DC}$ .

Table 49. Local Bus General Timing Parameters ( $BV_{DD} = 3.3 V DC$ )—PLL EnabledAt recommended operating conditions with  $BV_{DD}$  of 3.3 V ± 5%.

| Parameter                                                            | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|----------------------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                                 | t <sub>LBK</sub>                    | 6.67 | 12  | ns   | 2     |

| Local bus duty cycle                                                 | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                 | t <sub>LBKSKEW</sub>                | —    | 150 | ps   | 7,8   |

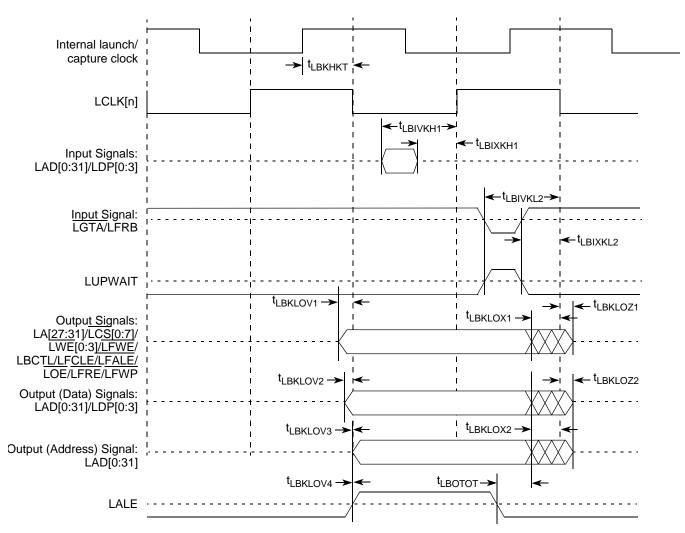

| Input setup to local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIVKH1</sub>                | 1.8  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                          | t <sub>LBIVKH2</sub>                | 1.7  | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                | t <sub>LBIXKH1</sub>                | 1.0  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKH2</sub>                | 1.0  | —   | ns   | 3, 4  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5  | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKHOV1</sub>                | —    | 2.3 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKHOV2</sub>                | —    | 2.4 | ns   | 3     |

| Local bus clock to address valid for LAD                             | t <sub>LBKHOV3</sub>                | —    | 2.3 | ns   | 3     |

Table 51. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)—PLL Enabled (continued)

At recommended operating conditions with  $\mathsf{BV}_{\mathsf{DD}}$  of 1.8 V ± 5% (continued)

| Parameter                                                            | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|----------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKH2</sub> | 1.1 | —   | ns   | 3, 4  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>lbotot</sub>  | 1.2 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKHOV1</sub> | —   | 3.2 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKHOV2</sub> | _   | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                             | t <sub>LBKHOV3</sub> | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                    | t <sub>LBKHOV4</sub> | _   | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)           | t <sub>LBKHOX1</sub> | 0.9 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                         | t <sub>LBKHOX2</sub> | 0.9 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)   | t <sub>LBKHOZ1</sub> | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                 | t <sub>LBKHOZ2</sub> |     | 2.6 | ns   | 5     |

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from BV<sub>DD</sub>/2 of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 1.8-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

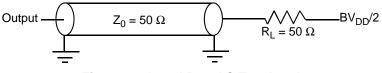

Figure 29 provides the AC test load for the local bus.

Figure 29. Local Bus AC Test Load

#### Local Bus Controller (eLBC)

Figure 30 through Figure 35 show the local bus signals.

Figure 30. Local Bus Signals, Non-Special Signals Only (PLL Enabled)

Table 52 describes the general timing parameters of the local bus interface at  $BV_{DD} = 3.3 \text{ V DC}$  with PLL disabled.

## Table 52. Local Bus General Timing Parameters—PLL Bypassed

At recommended operating conditions with  $BV_{DD}$  of 3.3 V ± 5%

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 12   | _   | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | —     |

| Internal launch/capture clock to LCLK delay           | t <sub>LBKHKT</sub>                 | 2.3  | 4.0 | ns   | —     |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 5.8  | —   | ns   | 4, 5  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKL2</sub>                | 5.7  | _   | ns   | 4, 5  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | -1.3 | —   | ns   | 4, 5  |

Local Bus Controller (eLBC)

Figure 31. Local Bus Signals (PLL Bypass Mode)

High-Speed Serial Interfaces (HSSI)

SD1\_REF\_CLK for PCI Express and Serial RapidIO, or SD2\_REF\_CLK and SD2\_REF\_CLK for the SGMII interface respectively.

The following sections describe the SerDes reference clock requirements and some application information.

# **15.2.1 SerDes Reference Clock Receiver Characteristics**

Figure 44 shows a receiver reference diagram of the SerDes reference clocks. Characteristics are as follows:

- The supply voltage requirements for  $XV_{DD SRDS2}$  are specified in Table 1 and Table 2.

- SerDes Reference Clock Receiver Reference Circuit Structure

- The SDn\_REF\_CLK and SDn\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 44. Each differential clock input (SDn\_REF\_CLK or SDn\_REF\_CLK) has on-chip 50-Ω termination to SGND\_SRDSn (xcorevss) followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. Refer to the Differential Mode and Single-ended Mode description below for further detailed requirements.

- The maximum average current requirement that also determines the common mode voltage range

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA (refer to the following bullet for more detail), because the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V/50 = 8 mA) while the minimum common mode input level is 0.1 V above SGND\_SRDS*n* (xcorevss). For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 mA to 16 mA (0-0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SD*n*\_REF\_CLK and  $\overline{\text{SD}n_\text{REF}\text{-}\text{CLK}}$  inputs cannot drive 50  $\Omega$  to SGND\_SRDS*n* (xcorevss) DC, or it exceeds the maximum input current limitations, then it must be AC-coupled off-chip.

- The input amplitude requirement

- This requirement is described in detail in the following sections.

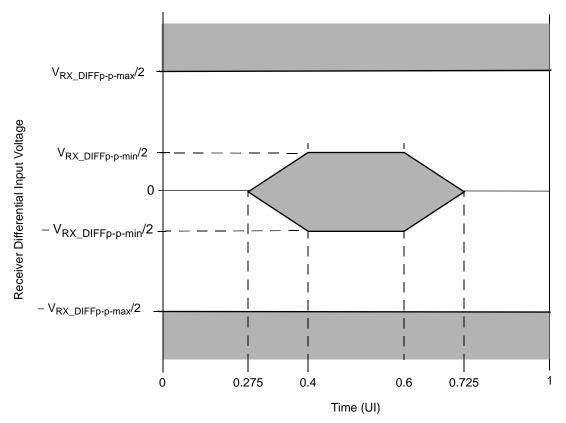

# 16.4.3 Differential Receiver (RX) Input Specifications

Table 63 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

| Symbol                  | Parameter                                     | Min    | Nominal | Max    | Units | Comments                                                                                                                                                                                    |

|-------------------------|-----------------------------------------------|--------|---------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                      | Unit Interval                                 | 399.88 | 400     | 400.12 | ps    | Each UI is 400 ps ± 300 ppm. UI does not<br>account for Spread Spectrum Clock<br>dictated variations. See Note 1.                                                                           |

| V <sub>RX-DIFFp-p</sub> | Differential Input<br>Peak-to-Peak<br>Voltage | 0.175  | _       | 1.200  | V     | $V_{RX-DIFFp-p} = 2^*  V_{RX-D+} - V_{RX-D-} $<br>See Note 2.                                                                                                                               |

| T <sub>RX-EYE</sub>     | Minimum<br>Receiver Eye<br>Width              | 0.4    |         |        | UI    | The maximum interconnect media and<br>Transmitter jitter that can be tolerated by<br>the Receiver can be derived as<br>$T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$ UI.<br>See Notes 2 and 3. |

Table 63. Differential Receiver (RX) Input Specifications

| Table 76. MPC8572E Pinout Listing (continued) |

|-----------------------------------------------|

|-----------------------------------------------|

| Signal      | Signal Name                                                                      | Package Pin Number                        | Pin Type | Power<br>Supply            | Notes |

|-------------|----------------------------------------------------------------------------------|-------------------------------------------|----------|----------------------------|-------|

| SD1_RX[7:0] | Receive Data (positive)                                                          | P32, N30, M32, L30,<br>G30, F32, E30, D32 | I        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_RX[7:0] | Receive Data (negative)                                                          | P31, N29, M31, L29,<br>G29, F31, E29, D31 | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[7]   | PCIe1 Tx Data Lane 7 / SRIO or<br>PCIe2 Tx Data Lane 3 / PCIe3<br>TX Data Lane 1 | M26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 |       |

| SD1_TX[6]   | PCIe1 Tx Data Lane 6 / SRIO or<br>PCIe2 Tx Data Lane 2 / PCIe3<br>TX Data Lane 0 | L24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[5]   | PCIe1 Tx Data Lane 5 / SRIO or<br>PCIe2 Tx Data Lane 1                           | K26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[4]   | PCIe1 Tx Data Lane 4 / SRIO or<br>PCIe2 Tx Data Lane 0                           | J24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[3]   | PCIe1 Tx Data Lane 3                                                             | G24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[2]   | PCIe1 Tx Data Lane 2                                                             | F26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[1]   | PCIe1 Tx Data Lane 1]                                                            | E24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[0]   | PCIe1 Tx Data Lane 0                                                             | D26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[7:0] | Transmit Data (negative)                                                         | M27, L25, K27, J25,<br>G25, F27, E25, D27 | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_PLL_TPD | PLL Test Point Digital                                                           | J32                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | 17    |

| SD1_REF_CLK | PLL Reference Clock                                                              | H32                                       | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_REF_CLK | PLL Reference Clock<br>Complement                                                | H31                                       | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| Reserved    | -                                                                                | С29, К32                                  |          | —                          | 26    |

| Reserved    | -                                                                                | С30, К31                                  |          | —                          | 27    |

| Reserved    | -                                                                                | C24, C25, H26, H27                        | _        | —                          | 28    |

| Reserved    | _                                                                                | AL20, AL21                                |          |                            | 29    |

|             | SerDes (x4)                                                                      | SGMII                                     |          |                            |       |

| SD2_RX[3:0] | Receive Data (positive)                                                          | AK32, AJ30, AF30,<br>AE32                 | I        | XV <sub>DD_SR</sub><br>DS2 | _     |

**Package Description**

| Signal | Signal Name   | Package Pin Number                                                                                                                                                                  | Pin Type | Power<br>Supply | Notes |

|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|-------|

| N/C    | No Connection | A16, A20, B16, B17,<br>B19, B20, C17, C18,<br>C19, D28, R31, T17,<br>V23, W23, Y22, Y23,<br>Y24, AA24, AB24,<br>AC24, AC26, AC27,<br>AC29, AD31, AE29,<br>AJ25, AK28, AL31,<br>AM21 | _        | _               | 17    |

## Table 76. MPC8572E Pinout Listing (continued)

#### Note:

- 1. All multiplexed signals are listed only once and do not re-occur. For example, LCS5/DMA\_REQ2 is listed only once in the local bus controller section, and is not mentioned in the DMA section even though the pin also functions as DMA\_REQ2.

- 2. Recommend a weak pull-up resistor (2–10 K $\Omega$ ) be placed on this pin to OVDD.

- 4. This pin is an open drain signal.

- 5. This pin is a reset configuration pin. It has a weak internal pull-up P-FET which is enabled only when the processor is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-kO pull-down resistor. However, if the signal is intended to be high after reset, and if there is any device on the net which might pull down the value of the net at reset, then a pullup or active driver is needed.

- 6. Treat these pins as no connects (NC) unless using debug address functionality.

- 7. The value of LA[29:31] during reset sets the CCB clock to SYSCLK PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See Section 19.2, "CCB/SYSCLK PLL Ratio."

- 8. The value of LALE, LGPL2 and LBCTL at reset set the e500 core clock to CCB Clock PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See the Section 19.3, "e500 Core PLL Ratio."

- 9. Functionally, this pin is an output, but structurally it is an I/O because it either samples configuration input during reset or because it has other manufacturing test functions. This pin therefore be described as an I/O for boundary scan.

- 10. If this pin is configured for local bus controller usage, recommend a weak pull-up resistor (2-10 K $\Omega$ ) be placed on this pin to BVDD, to ensure no random chip select assertion due to possible noise and so on.

- 11. This output is actively driven during reset rather than being three-stated during reset.

- 12. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 13. These pins are connected to the VDD/GND planes internally and may be used by the core power supply to improve tracking and regulation.

- 14. Internal thermally sensitive diode.

- 15. If this pin is connected to a device that pulls down during reset, an external pull-up is required to drive this pin to a safe state during reset.

- 16. This pin is only an output in FIFO mode when used as Rx Flow Control.

- 17. Do not connect.

- 18. These are test signals for factory use only and must be pulled up (100  $\Omega$  1 K $\Omega$ ) to OVDD for normal machine operation.

- 19. Independent supplies derived from board VDD.

- 20. Recommend a pull-up resistor (~1 K $\Omega$ ) be placed on this pin to OVDD.

- 21. The following pins must NOT be pulled down during power-on reset: DMA1\_DACK[0:1], EC5\_MDC, HRESET\_REQ, TRIG\_OUT/READY\_P0/QUIESCE, MSRCID[2:4], MDVAL, ASLEEP.

- 22. This pin requires an external 4.7-kΩ pull-down resistor to prevent PHY from seeing a valid Transmit Enable before it is actively driven.

- 23. This pin is only an output in eTSEC3 FIFO mode when used as Rx flow control.

- 24. TSEC2\_TXD[1] is used as cfg\_dram\_type. IT MUST BE VALID AT POWER-UP, EVEN BEFORE HRESET ASSERTION.

System Design Information

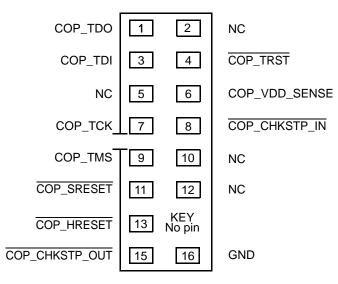

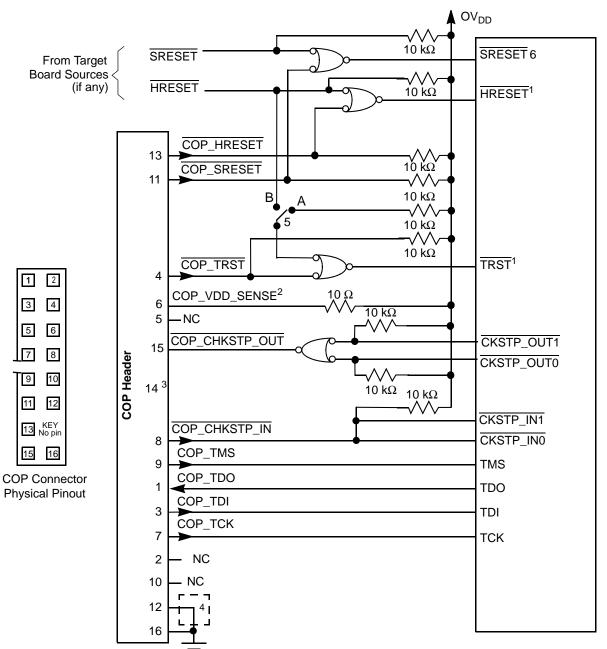

Figure 65. COP Connector Physical Pinout

System Design Information

#### Notes:

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor to fully control the processor as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- 5. This switch is included as a precaution for BSDL testing. The switch should be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed to position B.

- 6. Asserting SRESET causes a machine check interrupt to the e500 cores.

# 22 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 22.1, "Part Numbers Fully Addressed by this Document."

# 22.1 Part Numbers Fully Addressed by this Document

Table 86 through Table 88 provide the Freescale part numbering nomenclature for the MPC8572E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC                          | nnnn               | е                                       | t                                      | Ι                              | рр                                                                                                                   | ffm                                                                                                                                                                                                                                  | r                                                                                                                           |

|------------------------------|--------------------|-----------------------------------------|----------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Product<br>Code <sup>1</sup> | Part<br>Identifier | Security<br>Engine                      | Temperature                            | Power                          | Package<br>Sphere<br>Type <sup>2</sup>                                                                               | Processor Frequency/<br>DDR Data Rate <sup>3</sup>                                                                                                                                                                                   | Silicon<br>Revision                                                                                                         |

| MPC<br>PPC                   | 8572               | E = Included<br>Blank = Not<br>included | Blank = 0 to 105°C<br>C = −40 to 105°C | Blank =<br>Standard<br>L = Low | PX =<br>Leaded,<br>FC-PBGA<br>VT = Pb-free,<br>FC-PBGA <sup>4</sup><br>VJ = Fully<br>Pb-free<br>FC-PBGA <sup>5</sup> | AVN =<br>1500-MHz processor;<br>800 MT/s DDR data rate<br>AUL =<br>1333-MHz processor;<br>667 MT/s DDR data rate<br>ATL =<br>1200-MHz processor;<br>667 MT/s DDR data rate<br>ARL =<br>1067-MHz processor;<br>667 MT/s DDR data rate | E = Ver. 2.2.1<br>(SVR =<br>0x80E8_0022)<br>SEC included<br>E = Ver. 2.2.1<br>(SVR =<br>0x80E0_0022)<br>SEC not<br>included |

Notes:

- <sup>1</sup> MPC stands for "Qualified."

- PPC stands for "Prototype"

- <sup>2</sup> See Section 18, "Package Description," for more information on the available package types.

- <sup>3</sup> Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

- 4. The VT part number is ROHS-compliant with the permitted exception of the C4 die bumps.

- 5. The VJ part number is entirely lead-free. This includes the C4 die bumps.

**Document Revision History**

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6              | 06/2014 | <ul> <li>Updated Table 76, "MPC8572E Pinout Listing," TDO signal is not driven during HRSET* assertion.</li> <li>In Table 86, "Part Numbering Nomenclature—Rev 2.2.1," added full Pb-free part code.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5              | 01/2011 | <ul> <li>Editorial changes throughout</li> <li>Updated Table 4, "MPC8572E Power Dissipation," to include low power product.</li> <li>In Section 22.1, "Part Numbers Fully Addressed by this Document," defined PPC as "Prototype" and changed table headings to say "Package Sphere Type".</li> <li>Added Table 86, "Part Numbering Nomenclature—Rev 2.2.1."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4              | 06/2010 | <ul> <li>In Section 18.3, "Pinout Listings," updated Table 76 showing GPINOUT power rail as BVDD.</li> <li>Updated Section 14.1, "GPIO DC Electrical Characteristics."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3              | 03/2010 | <ul> <li>In Section 2.1, "Overall DC Electrical Characteristics," changed GPIO power from OVDD to BVDD.</li> <li>In Section 22.1, "Part Numbers Fully Addressed by this Document," added Table 87 for Rev 2.1 silicon.</li> <li>In Section 22.1, "Part Numbers Fully Addressed by this Document," updated Table 88 for Rev 1.1.1 silicon.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2              | 06/2009 | <ul> <li>In Section 3, "Power Characteristics," updated CCB Max to 533MHz for 1200MHz core device in Table 5, "MPC8572EL Power Dissipation."</li> <li>In Section 4.4, "DDR Clock Timing," changed DDRCLK Max to 100MHz. This change was announced in Product Bulletin #13572.</li> <li>Clarified restrictions in Section 4.5, "Platform to eTSEC FIFO Restrictions."</li> <li>In Table 9, "RESET Initialization Timing Specifications," added note 2.</li> <li>Added Section 14, "GPIO."</li> <li>In Section 18.1, "Package Parameters for the MPC8572E FC-PBGA," updated material composition to 63% Sn, 37% Pb.</li> <li>In Section 18.2, "Mechanical Dimensions of the MPC8572E FC-PBGA, updated Figure 61 to correct the package thickness and top view.</li> <li>In Section 19.1, "Clock Ranges," updated CCB Max to 533MHz for 1200MHz core device in Table 77, "MPC8572E Processor Core Clocking Specifications."</li> <li>In Section 19.5.2, "Minimum Platform Frequency Requirements for High-Speed Interfaces," changed minimum CCB clock frequency for proper PCI Express operation.</li> <li>Added LPBSE to description of LGPL4/LGTA/LUPWAIT/LPBSE/LFRB signal in Table 76, "MPC8572E Pinout Listing."</li> <li>Corrected supply voltage for GPIO pins in Table 76, "MPC8572E Pinout Listing."</li> <li>Applied note regarding MDIC in Table 76, "MPC8572E Pinout Listing."</li> <li>Added note for LAD pins in Table 76, "MPC8572E Pinout Listing."</li> <li>Updated Table 88, ",Part Numbering Nomenclature—Rev 1.1.1" with Rev 2.0 and Rev 2.1 part number information. Added note indicating that silicon version 2.0 is available for prototype purposes only and will not be available as a qualified device.</li> </ul> |

| 1              | 08/2008 | • In Section 22.1, "Part Numbers Fully Addressed by this Document," added SVR information in,<br>Table 88 "Part Numbering Nomenclature—Rev 1.1.1," for devices without Security Engine feature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0              | 07/2008 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |