# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                        |

| Speed                           | 1.2GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR2, DDR3                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | · .                                                                   |

| Package / Case                  | 1023-BFBGA, FCBGA                                                     |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572pxatld |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

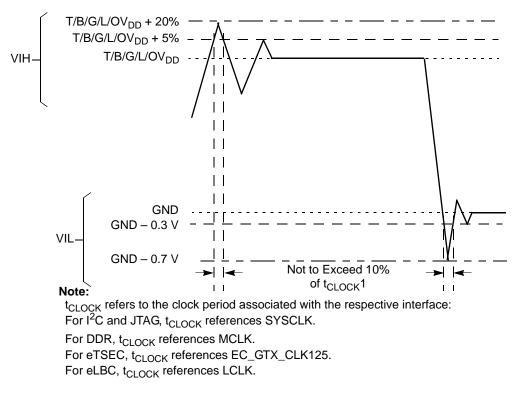

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8572E.

#### Figure 2. Overshoot/Undershoot Voltage for TV<sub>DD</sub>/BV<sub>DD</sub>/GV<sub>DD</sub>/LV<sub>DD</sub>/OV<sub>DD</sub>

The core voltage must always be provided at nominal 1.1 V. (See Table 2 for actual recommended core voltage.) Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ , and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR2 and DDR3 SDRAM interface uses differential receivers referenced by the externally supplied  $MV_{REF}n$  signal (nominally set to  $GV_{DD}/2$ ) as is appropriate for the SSTL\_1.8 electrical signaling standard for DDR2 or 1.5-V electrical signaling for DDR3. The DDR DQS receivers cannot be operated in single-ended fashion. The complement signal must be properly driven and cannot be grounded.

Electrical Characteristics

# 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                                                | Notes |

|---------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>35                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V                             | 1     |

|                                       | 45(default)<br>45(default)<br>125       | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V<br>BV <sub>DD</sub> = 1.8 V |       |

| DDR2 signal                           | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                                                         | 2     |

| DDR3 signal                           | 20<br>40 (half strength mode)           | GV <sub>DD</sub> = 1.5 V                                                         | 2     |

| eTSEC/10/100 signals                  | 45                                      | L/TV <sub>DD</sub> = 2.5/3.3 V                                                   | _     |

| DUART, system control, JTAG           | 45                                      | OV <sub>DD</sub> = 3.3 V                                                         | —     |

| 12C                                   | 150                                     | OV <sub>DD</sub> = 3.3 V                                                         | —     |

Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the DDR2 or DDR3 interface in half-strength mode is at  $T_i = 105^{\circ}C$  and at  $GV_{DD}$  (min).

# 2.2 Power Sequencing

The MPC8572E requires its power rails to be applied in a specific sequence to ensure proper device operation. These requirements are as follows for power up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, SV<sub>DD</sub>, SV<sub>DD</sub>, SV<sub>DD</sub>, XV<sub>DD</sub>, XV<sub>D</sub>

- 2. GV<sub>DD</sub>

All supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

To guarantee MCKE low during power-on reset, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-on reset, then the sequencing for  $GV_{DD}$  is not required.

# 4.3 eTSEC Gigabit Reference Clock Timing

Table 7 provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications for the MPC8572E.

#### Table 7. EC\_GTX\_CLK125 AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3V ± 5% or 2.5V ± 5%

| Parameter/Condition                                                 | Symbol                                  | Min      | Typical | Max         | Unit | Notes |

|---------------------------------------------------------------------|-----------------------------------------|----------|---------|-------------|------|-------|

| EC_GTX_CLK125 frequency                                             | f <sub>G125</sub>                       | _        | 125     |             | MHz  | _     |

| EC_GTX_CLK125 cycle time                                            | t <sub>G125</sub>                       | _        | 8       | _           | ns   | _     |

| EC_GTX_CLK125 rise and fall time L/TV_DD=2.5V L/TV_DD=3.3V          | t <sub>G125R</sub> , t <sub>G125F</sub> | _        | _       | 0.75<br>1.0 | ns   | 1     |

| EC_GTX_CLK125 duty cycle<br>GMII, TBI<br>1000Base-T for RGMII, RTBI | t <sub>G125H</sub> /t <sub>G125</sub>   | 45<br>47 | _       | 55<br>53    | %    | 2, 3  |

Notes:

1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5V and 2.0V for L/TV<sub>DD</sub>=2.5V, and from 0.6V and 2.7V for L/TV<sub>DD</sub>=3.3V.

- 2. Timing is guaranteed by design and characterization.

- 3. EC\_GTX\_CLK125 is used to generate the GTX clock for the eTSEC transmitter with 2% degradation. EC\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the TSEC*n*\_GTX\_CLK. See Section 8.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

# 4.4 DDR Clock Timing

Table 8 provides the DDR clock (DDRCLK) AC timing specifications for the MPC8572E.

#### Table 8. DDRCLK AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition       | Symbol                                | Min  | Typical | Max   | Unit | Notes |

|---------------------------|---------------------------------------|------|---------|-------|------|-------|

| DDRCLK frequency          | f <sub>DDRCLK</sub>                   | 66   | _       | 100   | MHz  | 1     |

| DDRCLK cycle time         | t <sub>DDRCLK</sub>                   | 10.0 | _       | 15.15 | ns   | _     |

| DDRCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6  | 1.0     | 1.2   | ns   | 2     |

| DDRCLK duty cycle         | t <sub>KHK</sub> /t <sub>DDRCLK</sub> | 40   |         | 60    | %    | 3     |

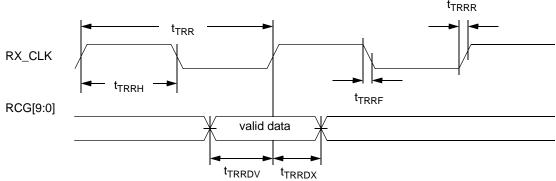

Figure 17 shows the TBI receive the timing diagram.

Figure 17. TBI Single-Clock Mode Receive AC Timing Diagram

# 8.2.6 **RGMII and RTBI AC Timing Specifications**

Table 34 presents the RGMII and RTBI AC timing specifications.

#### Table 34. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $\text{LV}_{\text{DD}}/\text{TV}_{\text{DD}}$  of 2.5 V ± 5%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min  | Тур | Мах  | Unit |

|--------------------------------------------------------|-------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT</sub>                  | -500 | 0   | 500  | ps   |

| Data to clock input skew (at receiver) <sup>2</sup>    | t <sub>SKRGT</sub>                  | 1.0  | _   | 2.8  | ns   |

| Clock period <sup>3</sup>                              | t <sub>RGT</sub>                    | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 4</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub> | 40   | 50  | 60   | %    |

| Rise time (20%–80%)                                    | t <sub>rgtr</sub>                   | —    | _   | 0.75 | ns   |

| Fall time (20%–80%)                                    | t <sub>RGTF</sub>                   | —    | _   | 0.75 | ns   |

#### Notes:

- 1. Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns will be added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

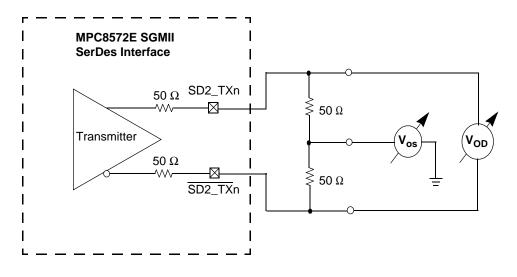

# 8.3.3 SGMII Transmitter and Receiver DC Electrical Characteristics

Table 38 and Table 39 describe the SGMII SerDes transmitter and receiver AC-Coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs (SD2\_TX[n] and SD2\_TX[n]) as depicted in Figure 23.

| Parameter                                                 | Symbol            | Min                                                                      | Тур | Max                                                                      | Unit | Notes                       |                            |

|-----------------------------------------------------------|-------------------|--------------------------------------------------------------------------|-----|--------------------------------------------------------------------------|------|-----------------------------|----------------------------|

| Supply Voltage                                            | $XV_{DD\_SRDS2}$  | 1.045                                                                    | 1.1 | 1.155                                                                    | V    | —                           |                            |

| Output high voltage                                       | VOH               | —                                                                        | _   | XV <sub>DD_SRDS2-Typ</sub> /2<br>+  V <sub>OD</sub>   <sub>-max</sub> /2 | mV   | 1                           |                            |

| Output low voltage                                        | VOL               | XV <sub>DD_SRDS2-Typ</sub> /2<br>-  V <sub>OD</sub>   <sub>-max</sub> /2 | _   | _                                                                        | mV   | 1                           |                            |

| Output ringing                                            | V <sub>RING</sub> | —                                                                        | _   | 10                                                                       | %    | —                           |                            |

|                                                           |                   | 359                                                                      | 550 | 791                                                                      |      | Equalization setting: 1.0x  |                            |

|                                                           |                   | 329                                                                      | 505 | 725                                                                      |      | Equalization setting: 1.09x |                            |

| Output differential voltage <sup>2, 3, 5</sup>            | V <sub>OD</sub>   |                                                                          | 299 | 458                                                                      | 659  |                             | Equalization setting: 1.2x |

| Ouput unrerentiar voltage                                 |                   | 270                                                                      | 414 | 594                                                                      | mV   | Equalization setting: 1.33x |                            |

|                                                           |                   | 239                                                                      | 367 | 527                                                                      |      | Equalization setting: 1.5x  |                            |

|                                                           |                   | 210                                                                      | 322 | 462                                                                      |      | Equalization setting: 1.71x |                            |

|                                                           |                   | 180                                                                      | 275 | 395                                                                      |      | Equalization setting: 2.0x  |                            |

| Output offset voltage                                     | V <sub>OS</sub>   | 473                                                                      | 550 | 628                                                                      | mV   | 1, 4                        |                            |

| Output impedance (single-ended)                           | R <sub>O</sub>    | 40                                                                       | _   | 60                                                                       | Ω    | —                           |                            |

| Mismatch in a pair                                        | $\Delta R_{O}$    | —                                                                        | _   | 10                                                                       | %    | —                           |                            |

| Change in $V_{\mbox{\scriptsize OD}}$ between "0" and "1" | $\Delta  V_{OD} $ | _                                                                        |     | 25                                                                       | mV   | —                           |                            |

### Table 38. SGMII DC Transmitter Electrical Characteristics

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

Table 39 lists the SGMII DC receiver electrical characteristics.

| Parameter                            |                        | Symbol                  | Min | Тур                   | Max  | Unit | Notes |

|--------------------------------------|------------------------|-------------------------|-----|-----------------------|------|------|-------|

| Supply Voltage                       | XV <sub>DD_SRDS2</sub> | 1.045                   | 1.1 | 1.155                 | V    |      |       |

| DC Input voltage range               |                        | —                       |     | N/A                   |      | _    | 1     |

| Input differential voltage LSTS = 0  |                        | V <sub>RX_DIFFp-p</sub> | 100 | —                     | 1200 | mV   | 2, 4  |

|                                      | LSTS = 1               |                         | 175 | —                     |      |      |       |

| Loss of signal threshold             | LSTS = 0               | VLOS                    | 30  | —                     | 100  | mV   | 3, 4  |

|                                      | LSTS = 1               |                         | 65  | —                     | 175  |      |       |

| Input AC common mode v               | voltage                | V <sub>CM_ACp-p</sub>   |     | —                     | 100  | mV   | 5     |

| Receiver differential input          | impedance              | Z <sub>RX_DIFF</sub>    | 80  | 100                   | 120  | Ω    |       |

| Receiver common mode input impedance |                        | Z <sub>RX_CM</sub>      | 20  | —                     | 35   | Ω    | _     |

| Common mode input volta              | age                    | V <sub>CM</sub>         | —   | V <sub>xcorevss</sub> |      | V    | 6     |

Table 39. SGMII DC Receiver Electrical Characteristics

#### Note:

1. Input must be externally AC-coupled.

2. V<sub>RX DIFFp-p</sub> is also referred to as peak to peak input differential voltage

3. The concept of this parameter is equivalent to the Electrical Idle Detect Threshold parameter in PCI Express. Refer to PCI Express Differential Receiver (RX) Input Specifications section for further explanation.

4. The LSTS shown in the table refers to the LSTSAB or LSTSEF bit field of MPC8572E's SerDes 2 Control Register.

5.  $V_{\mbox{CM}\_\mbox{ACp-p}}$  is also referred to as peak to peak AC common mode voltage.

6. On-chip termination to SGND\_SRDS2 (xcorevss).

Table 49. Local Bus General Timing Parameters (BV<sub>DD</sub> = 3.3 V DC)—PLL Enabled (continued)

At recommended operating conditions with  $\mathsf{BV}_{\mathsf{DD}}$  of 3.3 V ± 5%. (continued)

| Parameter                                                          | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to LALE assertion                                  | t <sub>LBKHOV4</sub> | _   | 2.3 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)         | t <sub>LBKHOX1</sub> | 0.7 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKHOX2</sub> | 0.7 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKHOZ1</sub> | _   | 2.5 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKHOZ2</sub> | —   | 2.5 | ns   | 5     |

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

Table 50 describes the general timing parameters of the local bus interface at  $BV_{DD} = 2.5 \text{ V DC}$ .

| ٦ | able 50. | Local I | Bus | s Ger | neral Tir | ning | Parameters | $(\mathbf{BV}_{\mathbf{DD}})$ | = 2.5 V DC | C)—PLL Enabled | I |

|---|----------|---------|-----|-------|-----------|------|------------|-------------------------------|------------|----------------|---|

|   |          |         |     |       |           |      |            |                               |            |                |   |

At recommended operating conditions with  $\text{BV}_{\text{DD}}$  of 2.5 V  $\pm$  5%

| Parameter                                                            | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|----------------------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                                 | t <sub>LBK</sub>                    | 6.67 | 12  | ns   | 2     |

| Local bus duty cycle                                                 | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                 | t <sub>LBKSKEW</sub>                | _    | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIVKH1</sub>                | 1.9  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                          | t <sub>LBIVKH2</sub>                | 1.8  | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                | t <sub>LBIXKH1</sub>                | 1.1  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKH2</sub>                | 1.1  | —   | ns   | 3, 4  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5  | —   | ns   | 6     |

#### Local Bus Controller (eLBC)

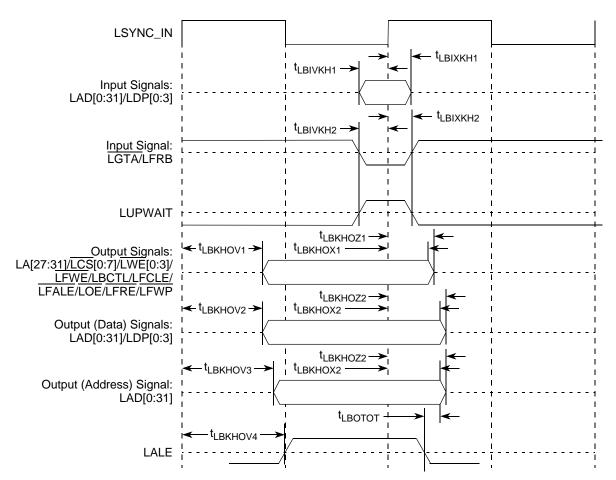

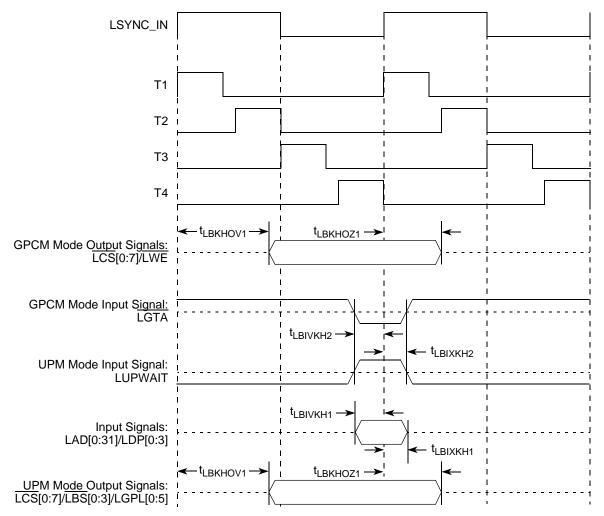

Figure 30 through Figure 35 show the local bus signals.

Figure 30. Local Bus Signals, Non-Special Signals Only (PLL Enabled)

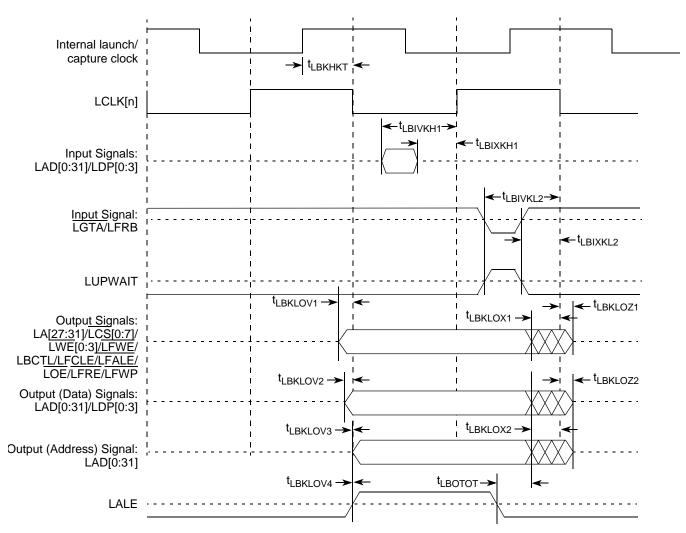

Table 52 describes the general timing parameters of the local bus interface at  $BV_{DD} = 3.3 \text{ V DC}$  with PLL disabled.

#### Table 52. Local Bus General Timing Parameters—PLL Bypassed

At recommended operating conditions with  $BV_{DD}$  of 3.3 V ± 5%

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 12   | _   | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | —     |

| Internal launch/capture clock to LCLK delay           | t <sub>LBKHKT</sub>                 | 2.3  | 4.0 | ns   | —     |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 5.8  | —   | ns   | 4, 5  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKL2</sub>                | 5.7  | _   | ns   | 4, 5  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | -1.3 | —   | ns   | 4, 5  |

Local Bus Controller (eLBC)

Figure 31. Local Bus Signals (PLL Bypass Mode)

Figure 34. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Enabled)

# 16.5.1 Compliance Test and Measurement Load

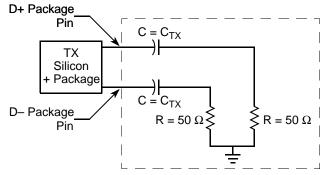

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 57.

### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

Figure 57. Compliance Test/Measurement Load

# 17 Serial RapidIO

This section describes the DC and AC electrical specifications for the RapidIO interface of the MPC8572E for the LP-Serial physical layer. The electrical specifications cover both single and multiple-lane links. Two transmitters (short run and long run) and a single receiver are specified for each of three baud rates, 1.25, 2.50, and 3.125 GBaud.

Two transmitter specifications allow for solutions ranging from simple board-to-board interconnect to driving two connectors across a backplane. A single receiver specification is given that accepts signals from both the short run and long run transmitter specifications.

The short run transmitter should be used mainly for chip-to-chip connections on either the same printed circuit board or across a single connector. This covers the case where connections are made to a mezzanine (daughter) card. The minimum swings of the short run specification reduce the overall power used by the transceivers.

The long run transmitter specifications use larger voltage swings that are capable of driving signals across backplanes. This allows a user to drive signals across two connectors and a backplane. The specifications allow a distance of at least 50 cm at all baud rates.

All unit intervals are specified with a tolerance of +/-100 ppm. The worst case frequency difference between any transmit and receive clock is 200 ppm.

To ensure interoperability between drivers and receivers of different vendors and technologies, AC coupling at the receiver input must be used.

|              |                              | ,                                                                                                                                                                                                                                                                                                                                 |          | Damas            |       |

|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| Signal       | Signal Name                  | Package Pin Number                                                                                                                                                                                                                                                                                                                | Pin Type | Power<br>Supply  | Notes |

| D1_MCAS      | Column Address Strobe        | AC9                                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | _     |

| D1_MRAS      | Row Address Strobe           | AB12                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> |       |

| D1_MCKE[0:3] | Clock Enable                 | M8, L9, T9, N8                                                                                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | 11    |

| D1_MCS[0:3]  | Chip Select                  | AB9, AF10, AB11,<br>AE11                                                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | —     |

| D1_MCK[0:5]  | Clock                        | V7, E13, AH11, Y9,<br>F14, AG10                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | _     |

| D1_MCK[0:5]  | Clock Complements            | Y10, E12, AH12, AA11,<br>F13, AG11                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub> |       |

| D1_MODT[0:3] | On Die Termination           | AD10, AF12, AC10,<br>AE12                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> |       |

| D1_MDIC[0:1] | Driver Impedance Calibration | E15, G14                                                                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | 25    |

|              | DDR SDRAM Mem                | ory Interface 2                                                                                                                                                                                                                                                                                                                   |          |                  |       |

| D2_MDQ[0:63] | Data                         | A6, B7, C5, D5, A7, C8,<br>D8, D6, C4, A3, D3,<br>D2, B4, A4, B1, C1, E3,<br>E1, G2, G6, D1, E4,<br>G5, G3, J4, J2, P4, R5,<br>H3, H1, N5, N3, Y6, Y4,<br>AC3, AD2, V5, W5,<br>AB2, AB3, AD5, AE3,<br>AF6, AG7, AC4, AD4,<br>AF4, AF7, AH5, AJ1,<br>AL2, AM3, AH3, AH6,<br>AM1, AL3, AK5, AL5,<br>AJ7, AK7, AK4, AM4,<br>AL6, AM7 | I/O      | GV <sub>DD</sub> |       |

| D2_MECC[0:7] | Error Correcting Code        | J5, H7, L7, N6, H4, H6,<br>M4, M5                                                                                                                                                                                                                                                                                                 | I/O      | GV <sub>DD</sub> | —     |

| D2_MAPAR_ERR | Address Parity Error         | N1                                                                                                                                                                                                                                                                                                                                | I        | GV <sub>DD</sub> |       |

| D2_MAPAR_OUT | Address Parity Out           | W2                                                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub> |       |

| D2_MDM[0:8]  | Data Mask                    | A5, B3, F4, J1, AA4,<br>AE5, AK1, AM5, K5                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> |       |

| D2_MDQS[0:8] | Data Strobe                  | B6, C2, F5, L4, AB5,<br>AF3, AL1, AM6, L6                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | —     |

| D2_MDQS[0:8] | Data Strobe                  | C7, A2, F2, K3, AA5,<br>AE6, AK2, AJ6, K6                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> |       |

| D2_MA[0:15]  | Address                      | W1, U4, U3, T1, T2, T3,<br>R1, R2, T5, R4, Y3, P1,<br>N2, AF1, M2, M1                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> |       |

### Table 76. MPC8572E Pinout Listing (continued)

# Table 76. MPC8572E Pinout Listing (continued)

| Signal                            | Signal Name                   | Package Pin Number                                   | Pin Type | Power<br>Supply  | Notes   |

|-----------------------------------|-------------------------------|------------------------------------------------------|----------|------------------|---------|

| IRQ_OUT                           | Interrupt Output              | U24                                                  | 0        | OV <sub>DD</sub> | 2, 4    |

|                                   | 1588                          | 3                                                    |          |                  |         |

| TSEC_1588_CLK                     | Clock In                      | AM22                                                 | I        | LV <sub>DD</sub> |         |

| TSEC_1588_TRIG_IN                 | Trigger In                    | AM23                                                 | I        | LV <sub>DD</sub> | _       |

| TSEC_1588_TRIG_OUT                | Trigger Out                   | AA23                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| TSEC_1588_CLK_OUT                 | Clock Out                     | AC23                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| TSEC_1588_PULSE_OUT1              | Pulse Out1                    | AA22                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| TSEC_1588_PULSE_OUT2              | Pulse Out2                    | AB23                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

|                                   | Ethernet Managem              | ent Interface 1                                      |          |                  |         |

| EC1_MDC                           | Management Data Clock         | AL30                                                 | 0        | LV <sub>DD</sub> | 5, 9    |

| EC1_MDIO                          | Management Data In/Out        | AM25                                                 | I/O      | LV <sub>DD</sub> |         |

|                                   | Ethernet Managem              | ent Interface 3                                      |          |                  |         |

| EC3_MDC                           | Management Data Clock         | AF19                                                 | 0        | TV <sub>DD</sub> | 5, 9    |

| EC3_MDIO                          | Management Data In/Out        | AF18                                                 | I/O      | TV <sub>DD</sub> |         |

|                                   | Ethernet Managem              | ent Interface 5                                      |          |                  |         |

| EC5_MDC                           | Management Data Clock         | AF14                                                 | 0        | TV <sub>DD</sub> | 21      |

| EC5_MDIO                          | Management Data In/Out        | AF15                                                 | I/O      | TV <sub>DD</sub> |         |

|                                   | Gigabit Ethernet R            | eference Clock                                       |          |                  |         |

| EC_GTX_CLK125                     | Reference Clock               | AM24                                                 | Ι        | LV <sub>DD</sub> | 32      |

|                                   | Three-Speed Ether             | net Controller 1                                     |          |                  |         |

| TSEC1_RXD[7:0]/FIFO1_RXD[<br>7:0] | Receive Data                  | AM28, AL28, AM26,<br>AK23, AM27, AK26,<br>AL29, AM30 | I        | LV <sub>DD</sub> | 1       |

| TSEC1_TXD[7:0]/FIFO1_TXD[<br>7:0] | Transmit Data                 | AC20, AD20, AE22,<br>AB22, AC22, AD21,<br>AB21, AE21 | 0        | LV <sub>DD</sub> | 1, 5, 9 |

| TSEC1_COL/FIFO1_TX_FC             | Collision Detect/Flow Control | AJ23                                                 | Ι        | LV <sub>DD</sub> | 1       |

| TSEC1_CRS/FIFO1_RX_FC             | Carrier Sense/Flow Control    | AM31                                                 | I/O      | LV <sub>DD</sub> | 1, 16   |

| TSEC1_GTX_CLK                     | Transmit Clock Out            | AK27                                                 | 0        | LV <sub>DD</sub> |         |

| TSEC1_RX_CLK/FIFO1_RX_C<br>LK     | Receive Clock                 | AL25                                                 | I        | LV <sub>DD</sub> | 1       |

| -                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                                 | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Power<br>Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Receive Data (negative)                     | AK31, AJ29, AF29,<br>AE31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SGMII Tx Data eTSEC4                        | AH26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SGMII Tx Data eTSEC3                        | AG24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SGMII Tx Data eTSEC2                        | AE24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SGMII Tx Data eTSEC1                        | AD26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Transmit Data (negative)                    | AH27, AG25, AE25,<br>AD27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PLL Test Point Digital                      | AH32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PLL Reference Clock                         | AG32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PLL Reference Clock<br>Complement           | AG31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| —                                           | AF26, AF27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |