# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                        |

| Speed                           | 1.067GHz                                                              |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR2, DDR3                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 1023-BFBGA, FCBGA                                                     |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572vtarle |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Electrical Characteristics

## 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values shown are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

|                                  | Characteristic                                                                                                    |                                                                        | Recommended Value                                  | Unit            | Notes |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------|-----------------|-------|

| Core supply voltage              |                                                                                                                   | V <sub>DD</sub>                                                        | 1.1 V ± 55 mV                                      | V               |       |

| PLL supply voltage               |                                                                                                                   | AV <sub>DD</sub>                                                       | 1.1 V ± 55 mV                                      | V               | 1     |

| Core power supply for            | or SerDes transceivers                                                                                            | SV <sub>DD</sub>                                                       | 1.1 V ± 55 mV                                      | V               |       |

| Pad power supply fo              | r SerDes transceivers                                                                                             | XV <sub>DD</sub>                                                       | 1.1 V ± 55 mV                                      | 1.1 V ± 55 mV V |       |

| DDR SDRAM                        | DDR2 SDRAM Interface                                                                                              | GV <sub>DD</sub>                                                       | 1.8 V ± 90 mV                                      | V               |       |

| Controller I/O<br>supply voltage | DDR3 SDRAM Interface                                                                                              | $1.5 V \pm 75 mV$ $LV_{DD} \qquad 3.3 V \pm 165 mV$ $2.5 V \pm 125 mV$ |                                                    |                 |       |

| Three-speed Etherne              | et I/O voltage                                                                                                    | LV <sub>DD</sub>                                                       | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V               | 4     |

|                                  |                                                                                                                   | TV <sub>DD</sub>                                                       | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   |                 | 4     |

| DUART, system con                | trol and power management, $I^2C$ , and JTAG I/O voltage                                                          | OV <sub>DD</sub>                                                       | 3.3 V ± 165 mV                                     | V               | 3     |

| Local bus and GPIO               | I/O voltage                                                                                                       | BV <sub>DD</sub>                                                       | 3.3 V ± 165 mV<br>2.5 V ± 125 mV<br>1.8 V ± 90 mV  | V               | _     |

| Input voltage                    | DDR2 and DDR3 SDRAM Interface signals                                                                             | MV <sub>IN</sub>                                                       | GND to GV <sub>DD</sub>                            | V               | 2     |

|                                  | DDR2 and DDR3 SDRAM Interface reference                                                                           | MV <sub>REF</sub> n                                                    | GV <sub>DD</sub> /2 ± 1%                           | V               | _     |

|                                  | Three-speed Ethernet signals                                                                                      | LV <sub>IN</sub><br>TV <sub>IN</sub>                                   | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V               | 4     |

|                                  | Local bus and GPIO signals                                                                                        | BVIN                                                                   | GND to BV <sub>DD</sub>                            | V               |       |

|                                  | Local bus, DUART, SYSCLK, Serial RapidIO, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                                                       | GND to OV <sub>DD</sub>                            | V               | 3     |

| Junction temperature             | e range                                                                                                           | TJ                                                                     | 0 to 105                                           | °C              | _     |

## **Table 2. Recommended Operating Conditions**

#### Notes:

- 1. This voltage is the input to the filter discussed in Section 21.2.1, "PLL Power Supply Filtering," and not necessarily the voltage at the AV<sub>DD</sub> pin, that may be reduced from V<sub>DD</sub> by the filter.

- 2. Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. Caution: L/TV<sub>IN</sub> must not exceed L/TV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

**RESET** Initialization

Table 8. DDRCLK AC Timing Specifications (continued)

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition | Symbol | Min | Typical | Max     | Unit | Notes   |

|---------------------|--------|-----|---------|---------|------|---------|

| DDRCLK jitter       | _      |     |         | +/- 150 | ps   | 4, 5, 6 |

Notes:

- 1. **Caution:** The DDR complex clock to DDRCLK ratio settings must be chosen such that the resulting DDR complex clock frequency does not exceed the maximum or minimum operating frequencies. Refer to Section 19.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

- 2. Rise and fall times for DDRCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The DDRCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track DDRCLK drivers with the specified jitter.

- 6. For spread spectrum clocking, guidelines are +0% to -1% down spread at a modulation rate between 20 kHz and 60 kHz on DDRCLK.

## 4.5 Platform to eTSEC FIFO Restrictions

Note the following eTSEC FIFO mode maximum speed restrictions based on platform (CCB) frequency.

For FIFO GMII modes (both 8 and 16 bit) and 16-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/4.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 127 MHz.

For 8-bit encoded FIFO mode:

FIFO TX/RX clock frequency <= platform clock (CCB) frequency/3.2

For example, if the platform (CCB) frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz.

## 4.6 Other Input Clocks

For information on the input clocks of other functional blocks of the platform, such as SerDes and eTSEC, see the respective sections of this document.

# 5 **RESET** Initialization

Table 9 describes the AC electrical specifications for the RESET initialization timing.

## **Table 9. RESET Initialization Timing Specifications**

| Parameter/Condition               | Min | Мах | Unit    | Notes |

|-----------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET | 100 | —   | μs      | 2     |

| Minimum assertion time for SRESET | 3   | —   | SYSCLKs | 1     |

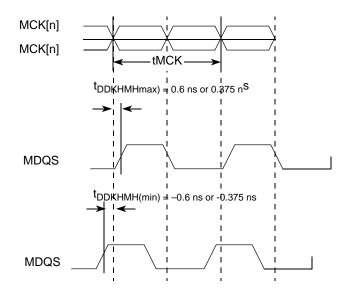

Figure 4 shows the DDR2 and DDR3 SDRAM Interface output timing for the MCK to MDQS skew measurement (tDDKHMH).

Figure 4. Timing Diagram for tDDKHMH

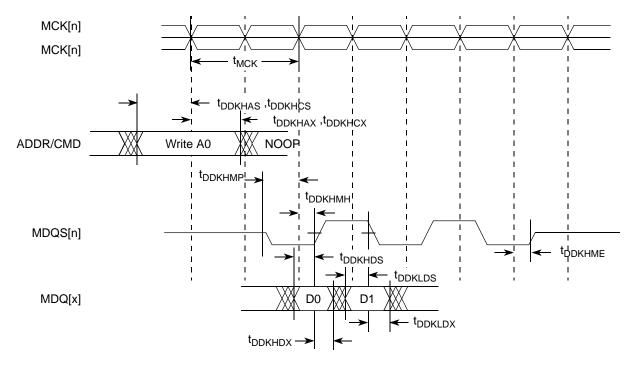

Figure 5 shows the DDR2 and DDR3 SDRAM Interface output timing diagram.

Figure 5. DDR2 and DDR3 SDRAM Interface Output Timing Diagram

| Table 24, MIL GMIL | RMIL RGI | /III. TBI. RTB                          | I, and FIFO DC Electrica | Characteristics | (continued) |

|--------------------|----------|-----------------------------------------|--------------------------|-----------------|-------------|

|                    | ,,       | , , , , , , , , , , , , , , , , , , , , |                          |                 | ooninaca)   |

| Parameters                                                | Symbol          | Min | Мах | Unit | Notes  |

|-----------------------------------------------------------|-----------------|-----|-----|------|--------|

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$ | IIH             | _   | 10  | μΑ   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)              | Ι <sub>ΙL</sub> | -15 | _   | μΑ   | 3      |

Note:

<sup>1</sup>  $LV_{DD}$  supports eTSECs 1 and 2.

$^{2}$  TV<sub>DD</sub> supports eTSECs 3 and 4 or FEC.

$^3$  Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII and RTBI are presented in this section.

## 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, because they have similar performance and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back on the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source-synchronous timing reference. Typically, the clock edge that launched the data can be used, because the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is a relationship between the maximum FIFO speed and the platform (CCB) frequency. For more information see Section 4.5, "Platform to eTSEC FIFO Restrictions."

Table 25 and Table 26 summarize the FIFO AC specifications.

## Table 25. FIFO Mode Transmit AC Timing Specification

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 2.5V ± 5%

| Parameter/Condition                       | Symbol                              | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK, GTX_CLK clock period <sup>1</sup> | t <sub>FIT</sub>                    | 5.3 | 8.0 | 100 | ns   |

| TX_CLK, GTX_CLK duty cycle                | t <sub>FITH</sub> /t <sub>FIT</sub> | 45  | 50  | 55  | %    |

## 8.3.4 SGMII AC Timing Specifications

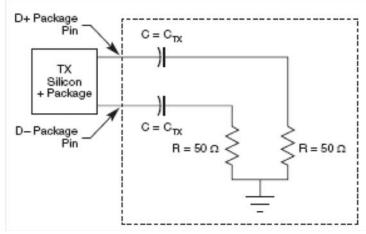

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs ( $SD2_TX[n]$  and  $\overline{SD2_TX[n]}$ ) or at the receiver inputs ( $SD2_RX[n]$  and  $\overline{SD2_RX[n]}$ ) as depicted in Figure 25, respectively.

## 8.3.4.1 SGMII Transmit AC Timing Specifications

Table 40 provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

### Table 40. SGMII Transmit AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2}$  = 1.1V ± 5%.

| Parameter                           | Symbol            | Min    | Тур | Max    | Unit   | Notes |

|-------------------------------------|-------------------|--------|-----|--------|--------|-------|

| Deterministic Jitter                | JD                | —      | _   | 0.17   | UI p-p | _     |

| Total Jitter                        | JT                | —      | _   | 0.35   | UI p-p | _     |

| Unit Interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1     |

| V <sub>OD</sub> fall time (80%-20%) | tfall             | 50     | _   | 120    | ps     | _     |

| V <sub>OD</sub> rise time (20%-80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     | _     |

Notes:

1. Each UI is 800 ps  $\pm$  100 ppm.

## 8.3.4.2 SGMII Receive AC Timing Specifications

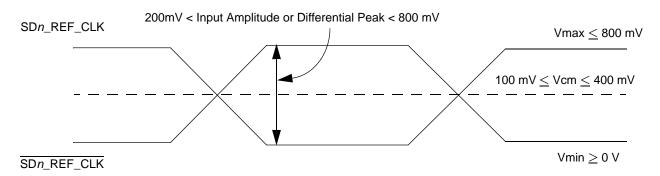

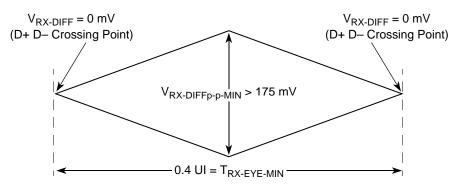

Table 41 provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 24 shows the SGMII receiver input compliance mask eye diagram.

#### Table 41. SGMII Receive AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2} = 1.1V \pm 5\%$ .

| Parameter                                          | Symbol          | Min    | Тур | Max               | Unit   | Notes |

|----------------------------------------------------|-----------------|--------|-----|-------------------|--------|-------|

| Deterministic Jitter Tolerance                     | JD              | 0.37   | —   | —                 | UI p-p | 1     |

| Combined Deterministic and Random Jitter Tolerance | JDR             | 0.55   | —   | _                 | UI p-p | 1     |

| Sinusoidal Jitter Tolerance                        | JSIN            | 0.1    | —   | —                 | UI p-p | 1     |

| Total Jitter Tolerance                             | JT              | 0.65   |     | _                 | UI p-p | 1     |

| Bit Error Ratio                                    | BER             | _      | —   | 10 <sup>-12</sup> |        | _     |

| Unit Interval                                      | UI              | 799.92 | 800 | 800.08            | ps     | 2     |

| AC Coupling Capacitor                              | C <sub>TX</sub> | 5      | —   | 200               | nF     | 3     |

Notes:

1. Measured at receiver.

2. Each UI is 800 ps  $\pm$  100 ppm.

3. The external AC coupling capacitor is required. It is recommended to be placed near the device transmitter outputs.

4. See RapidIO 1x/4x LP Serial Physical Layer Specification for interpretation of jitter specifications.

## Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

Figure 24. SGMII Receiver Input Compliance Mask

Figure 25. SGMII AC Test/Measurement Load

**Ethernet Management Interface Electrical Characteristics**

Table 43. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=3.3 V) (continued)

| Parameter                                                                             | Symbol          | Min  | Мах | Unit | Notes |

|---------------------------------------------------------------------------------------|-----------------|------|-----|------|-------|

| Input low current (LV <sub>DD</sub> /TV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V) | I <sub>IL</sub> | -600 | _   | μΑ   | _     |

Note:

1. EC1\_MDC and EC1\_MDIO operate on LV<sub>DD</sub>.

2. EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

3. Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  and  $TV_{IN}$  symbol referenced in Table 1.

#### Table 44. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=2.5 V)

| Parameters                                                         | Symbol                             | Min       | Мах                                      | Unit | Notes  |

|--------------------------------------------------------------------|------------------------------------|-----------|------------------------------------------|------|--------|

| Supply voltage 2.5 V                                               | LV <sub>DD/</sub> TV <sub>DD</sub> | 2.37      | 2.63                                     | V    | 1,2    |

| Output high voltage<br>( $LV_{DD}/TV_{DD} = Min, IOH = -1.0 mA$ )  | V <sub>OH</sub>                    | 2.00      | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _      |

| Output low voltage<br>( $LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA$ ) | V <sub>OL</sub>                    | GND – 0.3 | 0.40                                     | V    | _      |

| Input high voltage                                                 | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$                  | V    | _      |

| Input low voltage                                                  | V <sub>IL</sub>                    | -0.3      | 0.70                                     | V    | _      |

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$          | IIH                                | _         | 10                                       | μA   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                       | IIL                                | -15       | _                                        | μA   | 3      |

### Note:

$^1\,$  EC1\_MDC and EC1\_MDIO operate on LV\_DD.

<sup>2</sup> EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

$^3\,$  Note that the symbol V\_{IN}, in this case, represents the LV\_{IN} and TV\_{IN} symbols referenced in Table 1.

## 9.2 MII Management AC Electrical Specifications

Table 45 provides the MII management AC timing specifications. There are three sets of Ethernet management signals (EC1\_MDC and EC1\_MDIO, EC3\_MDC and EC3\_MDIO, EC5\_MDC and EC5\_MDIO). These are not explicitly shown in the table or in the figure following.

## Table 45. MII Management AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%.

| Parameter/Condition            | Symbol <sup>1</sup> | Min   | Тур | Мах                     | Unit | Notes |

|--------------------------------|---------------------|-------|-----|-------------------------|------|-------|

| ECn_MDC frequency              | f <sub>MDC</sub>    | 0.9   | 2.5 | 9.3                     | MHz  | 2, 3  |

| ECn_MDC period                 | t <sub>MDC</sub>    | 107.5 | _   | 1120                    | ns   | —     |

| ECn_MDC clock pulse width high | t <sub>MDCH</sub>   | 32    | _   | _                       | ns   | —     |

| ECn_MDC to ECn_MDIO delay      | t <sub>MDKHDX</sub> | 10    | _   | 16*t <sub>plb_clk</sub> | ns   | 5     |

Table 51. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)—PLL Enabled (continued)

At recommended operating conditions with  $\mathsf{BV}_{\mathsf{DD}}$  of 1.8 V ± 5% (continued)

| Parameter                                                            | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|----------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKH2</sub> | 1.1 | —   | ns   | 3, 4  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>lbotot</sub>  | 1.2 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKHOV1</sub> | —   | 3.2 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKHOV2</sub> | _   | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                             | t <sub>LBKHOV3</sub> | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                    | t <sub>LBKHOV4</sub> | _   | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)           | t <sub>LBKHOX1</sub> | 0.9 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                         | t <sub>LBKHOX2</sub> | 0.9 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)   | t <sub>LBKHOZ1</sub> | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                 | t <sub>LBKHOZ2</sub> |     | 2.6 | ns   | 5     |

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from BV<sub>DD</sub>/2 of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 1.8-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

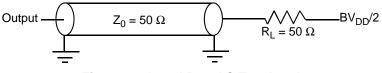

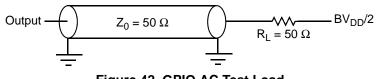

Figure 29 provides the AC test load for the local bus.

Figure 29. Local Bus AC Test Load

Table 58 provides the DC electrical characteristics for the GPIO interface operating at  $BV_{DD} = 1.8 \text{ V DC}$ . Table 58. GPIO DC Electrical Characteristics (1.8 V DC)

| Parameter                                                         | Symbol           | Min                     | Мах                     | Unit |  |  |  |  |

|-------------------------------------------------------------------|------------------|-------------------------|-------------------------|------|--|--|--|--|

| Supply voltage 1.8V                                               | BV <sub>DD</sub> | 1.71                    | 1.89                    | V    |  |  |  |  |

| High-level input voltage                                          | V <sub>IH</sub>  | 0.65 x BV <sub>DD</sub> | BV <sub>DD</sub> + 0.3  | V    |  |  |  |  |

| Low-level input voltage                                           | V <sub>IL</sub>  | -0.3                    | 0.35 x BV <sub>DD</sub> | V    |  |  |  |  |

| Input current $(BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD})$ | I <sub>IN</sub>  | TBD                     | TBD                     | μΑ   |  |  |  |  |

| High-level output voltage $(I_{OH} = -100 \ \mu A)$               | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2  | —                       | V    |  |  |  |  |

| High-level output voltage<br>(I <sub>OH</sub> = -2 mA)            | V <sub>OH</sub>  | BV <sub>DD</sub> - 0.45 | _                       | V    |  |  |  |  |

| Low-level output voltage $(I_{OL} = 100 \ \mu A)$                 | V <sub>OL</sub>  | _                       | 0.2                     | V    |  |  |  |  |

| Low-level output voltage<br>(I <sub>OL</sub> = 2 mA)              | V <sub>OL</sub>  | _                       | 0.45                    | V    |  |  |  |  |

#### Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

# 14.2 GPIO AC Electrical Specifications

Table 59 provides the GPIO input and output AC timing specifications.

## Table 59. GPIO Input AC Timing Specifications<sup>1</sup>

| Parameter                       | Symbol             | Тур | Unit | Notes |

|---------------------------------|--------------------|-----|------|-------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub> | 20  | ns   | 2     |

Notes:

- 1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYSCLK. Timings are measured at the pin.

- 2. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

## Figure 42 provides the AC test load for the GPIO.

Figure 42. GPIO AC Test Load

#### High-Speed Serial Interfaces (HSSI)

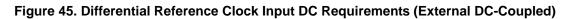

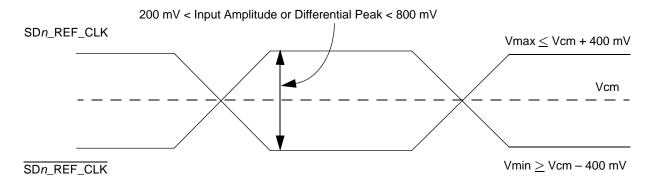

— To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC-coupled externally. For the best noise performance, the reference of the clock could be DC or AC-coupled into the unused phase (SDn\_REF\_CLK) through the same source impedance as the clock input (SDn\_REF\_CLK) in use.

Figure 46. Differential Reference Clock Input DC Requirements (External AC-Coupled)

Figure 47. Single-Ended Reference Clock Input DC Requirements

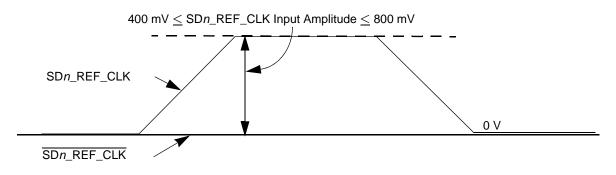

Figure 49 shows the SerDes reference clock connection reference circuits for LVDS type clock driver. Because LVDS clock driver's common mode voltage is higher than the MPC8572E SerDes reference clock input's allowed range (100 to 400mV), AC-coupled connection scheme must be used. It assumes the LVDS output driver features  $50-\Omega$  termination resistor. It also assumes that the LVDS transmitter establishes its own common mode level without relying on the receiver or other external component.

Figure 49. AC-Coupled Differential Connection with LVDS Clock Driver (Reference Only)

Figure 50 shows the SerDes reference clock connection reference circuits for LVPECL type clock driver. Because LVPECL driver's DC levels (both common mode voltages and output swing) are incompatible with MPC8572E SerDes reference clock input's DC requirement, AC-coupling must be used. Figure 50 assumes that the LVPECL clock driver's output impedance is  $50\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from  $140\Omega$  to  $240\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's  $50-\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8572E SerDes reference clock's differential input amplitude requirement (between 200mV and 800mV differential peak). For example, if the LVPECL output's differential peak is 900mV and the desired SerDes reference clock input amplitude is selected as 600mV, the attenuation factor is 0.67, which requires R2 =  $25\Omega$ . Consult

PCI Express

# 16.5 Receiver Compliance Eye Diagrams

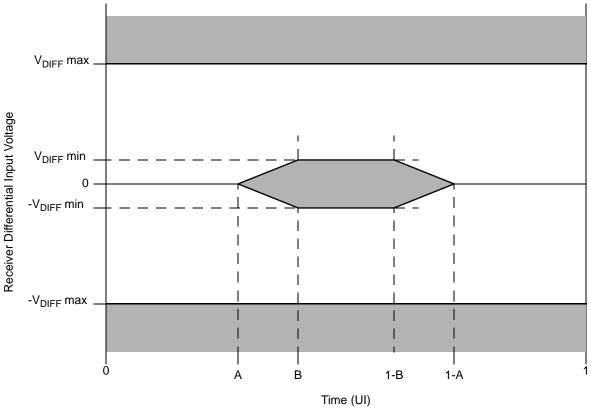

The RX eye diagram in Figure 56 is specified using the passive compliance/test measurement load (see Figure 57) in place of any real PCI Express RX component.

Note: In general, the minimum Receiver eye diagram measured with the compliance/test measurement load (see Figure 57) is larger than the minimum Receiver eye diagram measured over a range of systems at the input Receiver of any real PCI Express component. The degraded eye diagram at the input Receiver is due to traces internal to the package as well as silicon parasitic characteristics which cause the real PCI Express component to vary in impedance from the compliance/test measurement load. The input Receiver eye diagram is implementation specific and is not specified. RX component designer should provide additional margin to adequately compensate for the degraded minimum Receiver eye diagram (shown in Figure 56) expected at the input Receiver based on some adequate combination of system simulations and the Return Loss measured looking into the RX package and silicon. The RX eye diagram must be aligned in time using the jitter median to locate the center of the eye diagram.

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

## NOTE

The reference impedance for return loss measurements is 50. to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50. probes—see Figure 57). Note that the series capacitors, CTX, are optional for the return loss measurement.

Figure 56. Minimum Receiver Eye Timing and Voltage Compliance Specification

Serial RapidIO

# 17.1 <u>DC Requirements</u> for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK

For more information, see Section 15.2, "SerDes Reference Clocks."

# 17.2 <u>AC Requirements</u> for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK

Figure 64lists the AC requirements.

| Table 64. SDn_ | _REF_CLK an | d SD <i>n</i> _REF_ | _CLK AC Requirements |

|----------------|-------------|---------------------|----------------------|

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Comments                                                         |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|------------------------------------------------------------------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 10(8)   | —   | ns    | 8 ns applies only to serial RapidIO with 125-MHz reference clock |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | —       | 80  | ps    | _                                                                |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -40 | _       | 40  | ps    | _                                                                |

# 17.3 Equalization

With the use of high speed serial links, the interconnect media causes degradation of the signal at the receiver. Effects such as Inter-Symbol Interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are as follows:

- A passive high pass filter network placed at the receiver. This is often referred to as passive equalization.

- The use of active circuits in the receiver. This is often referred to as adaptive equalization.

# 17.4 Explanatory Note on Transmitter and Receiver Specifications

AC electrical specifications are given for transmitter and receiver. Long run and short run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to serial RapidIO, as described in Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." The goal of this standard is that electrical designs for Serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

### Table 66. Short Run Transmitter AC Timing Specifications—2.5 GBaud (continued)

| Characteristic       | Symbol          | Ra  | nge  | Unit | Notes                                                                  |

|----------------------|-----------------|-----|------|------|------------------------------------------------------------------------|

| Characteristic       | Symbol          | Min | Мах  | Onic | NOICS                                                                  |

| Multiple Output skew | S <sub>MO</sub> | _   | 1000 | -    | Skew at the transmitter output<br>between lanes of a multilane<br>link |

| Unit Interval        | UI              | 400 | 400  | ps   | +/- 100 ppm                                                            |

## Table 67. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Range Symbol        |       | nge  | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

|                             | Symbol              | Min   | Мах  | Onic   | NOICS                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | —                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | —                                                                                |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | _                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 320   | 320  | ps     | +/– 100 ppm                                                                      |

## Table 68. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                            |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|--|

| Characteristic              | Symbol              | Min   | Мах  |        | NOLES                                                                            |  |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON of<br>either signal comprising a<br>differential pair |  |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | —                                                                                |  |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                                |  |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                                |  |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |  |

| Unit Interval               | UI                  | 800   | 800  | ps     | +/- 100 ppm                                                                      |  |

Serial RapidIO

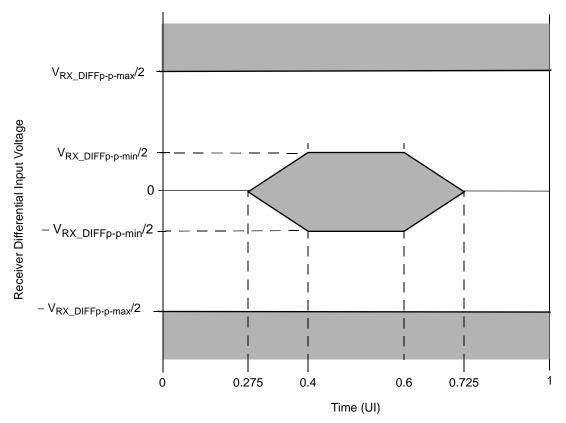

Figure 60. Receiver Input Compliance Mask

| Receiver Type | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|---------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud    | 100                        | 800                        | 0.275  | 0.400  |

| 2.5 GBaud     | 100                        | 800                        | 0.275  | 0.400  |

| 3.125 GBaud   | 100                        | 800                        | 0.275  | 0.400  |

# 17.8 Measurement and Test Requirements

Because the LP-Serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002, the measurement and test requirements defined here are similarly guided by Clause 47. Additionally, the CJPAT test pattern defined in Annex 48A of IEEE 802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter measurements. Annex 48B of IEEE 802.3ae-2002 is recommended as a reference for additional information on jitter test methods.

# 17.8.1 Eye Template Measurements

For the purpose of eye template measurements, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for template measurements is the Continuous Jitter Test Pattern (CJPAT) defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial

Table 81 describes the clock ratio between e500 Core1 and the e500 core complex bus (CCB). This ratio is determined by the binary value of LWE[0]/LBS[0]/LFWE, UART\_SOUT[1], and READY\_P1 signals at power up, as shown in Table 81.

| <u>Bina</u> ry <u>Value</u> of<br><u>L</u> WE[0]/LBS[0]/<br>LFWE, UART_SOUT[1],<br>READY_P1 Signals | e500 Core1:CCB Clock Ratio | <u>Bina</u> ry <u>Value</u> of<br><u>L</u> WE[0]/LBS[0]/<br>LFWE, UART_SOUT[1],<br>READY_P1 Signals | e500 Core1:CCB Clock Ratio |

|-----------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|----------------------------|

| 000                                                                                                 | Reserved                   | 100                                                                                                 | 2:1                        |

| 001                                                                                                 | Reserved                   | 101                                                                                                 | 5:2 (2.5:1)                |

| 010                                                                                                 | Reserved                   | 110                                                                                                 | 3:1                        |

| 011                                                                                                 | 3:2 (1.5:1)                | 111                                                                                                 | 7:2 (3.5:1)                |

| Table 81. | e500 | Core1 | to | ССВ | <b>Clock Ratio</b> | ) |

|-----------|------|-------|----|-----|--------------------|---|

|           |      |       |    |     | ••••••             |   |

## 19.4 DDR/DDRCLK PLL Ratio

The dual DDR memory controller complexes can be synchronous with, or asynchronous to, the CCB, depending on configuration.

Table 82 describes the clock ratio between the DDR memory controller complexes and the DDR PLL reference clock, DDRCLK, which is not the memory bus clock. The DDR memory controller complexes clock frequency is equal to the DDR data rate.

When synchronous mode is selected, the memory buses are clocked at half the CCB clock rate. The default mode of operation is for the DDR data rate for both DDR controllers to be equal to the CCB clock rate in synchronous mode, or the resulting DDR PLL rate in asynchronous mode.

In asynchronous mode, the DDR PLL rate to DDRCLK ratios listed in Table 82 reflects the DDR data rate to DDRCLK ratio, because the DDR PLL rate in asynchronous mode means the DDR data rate resulting from DDR PLL output.

Note that the DDR PLL reference clock input, DDRCLK, is only required in asynchronous mode. MPC8572E does not support running one DDR controller in synchronous mode and the other in asynchronous mode.

| Binary Value of<br>TSEC_1588_CLK_OUT,<br>TSEC_1588_PULSE_OUT1,<br>TSEC_1588_PULSE_OUT2 Signals | DDR:DDRCLK Ratio |

|------------------------------------------------------------------------------------------------|------------------|

| 000                                                                                            | 3:1              |

| 001                                                                                            | 4:1              |

| 010                                                                                            | 6:1              |

| 011                                                                                            | 8:1              |

| 100                                                                                            | 10:1             |

## Table 82. DDR Clock Ratio

| Binary Value of<br>TSEC_1588_CLK_OUT,<br>TSEC_1588_PULSE_OUT1,<br>TSEC_1588_PULSE_OUT2 Signals | DDR:DDRCLK Ratio |  |  |

|------------------------------------------------------------------------------------------------|------------------|--|--|

| 101                                                                                            | 12:1             |  |  |

| 110                                                                                            | 14:1             |  |  |

| 111                                                                                            | Synchronous mode |  |  |

Table 82. DDR Clock Ratio (continued)

## **19.5 Frequency Options**

## **19.5.1** Platform to Sysclk Frequency Options

Table 83 shows the expected frequency values for the platform frequency when using the specified CCB clock to SYSCLK ratio.

| CCB to<br>SYSCLK Ratio | SYSCLK (MHz) |                               |     |       |     |     |     |        |

|------------------------|--------------|-------------------------------|-----|-------|-----|-----|-----|--------|

|                        | 33.33        | 41.66                         | 50  | 66.66 | 83  | 100 | 111 | 133.33 |

|                        |              | Platform /CCB Frequency (MHz) |     |       |     |     |     |        |

| 4                      |              |                               |     |       |     | 400 | 444 | 533    |

| 5                      |              |                               |     |       | 415 | 500 | 555 |        |

| 6                      |              |                               |     | 400   | 498 | 600 |     |        |

| 8                      |              |                               | 400 | 533   |     |     | -   |        |

| 10                     |              | 417                           | 500 |       | -   |     |     |        |

| 12                     | 400          | 500                           | 600 | ]     |     |     |     |        |

Table 83. Frequency Options for Platform Frequency

## 19.5.2 Minimum Platform Frequency Requirements for High-Speed Interfaces

Section 4.4.3.6, "I/O Port Selection," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* describes various high-speed interface configuration options. Note that the CCB clock frequency must be considered for proper operation of such interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than or equal to:

See Section 21.1.3.2, "Link Width," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* for PCI Express interface width details. Note that the "PCI Express link width"

Table 85 summarizes the signal impedance targets. The driver impedances are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet, DUART,<br>Control, Configuration, Power<br>Management | DDR DRAM                                                         | Symbol         | Unit |

|----------------|----------------------------------------------------------------------------|------------------------------------------------------------------|----------------|------|

| R <sub>N</sub> | 45 Target                                                                  | 18 Target (full strength mode)<br>36 Target (half strength mode) | Z <sub>0</sub> | Ω    |

| R <sub>P</sub> | 45 Target                                                                  | 18 Target (full strength mode)<br>36 Target (half strength mode) | Z <sub>0</sub> | Ω    |

Table 85. Impedance Characteristics

**Note:** Nominal supply voltages. See Table 1,  $T_i = 105^{\circ}C$ .

# 21.8 Configuration Pin Muxing

The MPC8572E provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While  $\overline{\text{HRESET}}$  is asserted however, these pins are treated as inputs. The value presented on these pins while  $\overline{\text{HRESET}}$  is asserted, is latched when  $\overline{\text{HRESET}}$  deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Most of these sampled configuration pins are equipped with an on-chip gated resistor of approximately 20 kΩ. This value should permit the 4.7-kΩ resistor to pull the configuration pin to a valid logic low level. The pull-up resistor is enabled only during  $\overline{\text{HRESET}}$  (and for platform /system clocks after  $\overline{\text{HRESET}}$  deassertion to ensure capture of the reset value). When the input receiver is disabled the pull-up is also, thus allowing functional operation of the pin as an output with minimal signal quality or delay disruption. The default value for all configuration bits treated this way has been encoded such that a high voltage level puts the device into the default state and external resistors are needed only when non-default settings are required by the user.

Careful board layout with stubless connections to these pull-down resistors coupled with the large value of the pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

The platform PLL ratio, DDR complex PLL and e500 PLL ratio configuration pins are not equipped with these default pull-up devices.

# 21.9 JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 66. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The  $\overline{\text{TRST}}$  signal is optional in the IEEE Std 1149.1 specification, but it is provided on all processors built on Power Architecture technology. The device requires  $\overline{\text{TRST}}$  to be asserted during power-on reset flow to ensure that the JTAG boundary

System Design Information

## 21.10.3 SerDes 2 Interface (SGMII) Entirely Unused

If the high-speed SerDes 2 interface (SGMII) is not used at all, the unused pin should be terminated as described in this section.

The following pins must be left unconnected (float):

- SD2\_TX[3:0]

- <u>SD2\_TX[3:0]</u>

- Reserved pins: AF26, AF27

The following pins must be connected to XGND\_SRDS2:

- SD2\_RX[3:0]

- $\overline{\text{SD2}_RX}[3:0]$

- SD2\_REF\_CLK

- SD2\_REF\_CLK

The POR configuration pin cfg\_srds\_sgmii\_en on UART\_RTS[1] can be used to power down SerDes 2 block for power saving. Note that both SVDD\_SRDS2 and XVDD\_SRDS2 must remain powered.

## 21.10.4 SerDes 2 Interface (SGMII) Partly Unused

If only part of the high speed SerDes 2 interface (SGMII) pins are used, the remaining high-speed serial I/O pins should be terminated as described in this section.

The following pins must be left unconnected (float):

- SD2\_TX[3:0]

- <u>SD2\_TX[3:0]</u>

- Reserved pins: AF26, AF27

The following pins must be connected to XGND\_SRDS2:

- SD2\_RX[3:0]

- <u>SD2\_RX[3:0]</u>

# 22 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 22.1, "Part Numbers Fully Addressed by this Document."

## 22.1 Part Numbers Fully Addressed by this Document

Table 86 through Table 88 provide the Freescale part numbering nomenclature for the MPC8572E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC                          | nnnn               | е                                       | t                                      | Ι                              | рр                                                                                                                   | ffm                                                                                                                                                                                                                                  | r                                                                                                                           |

|------------------------------|--------------------|-----------------------------------------|----------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Product<br>Code <sup>1</sup> | Part<br>Identifier | Security<br>Engine                      | Temperature                            | Power                          | Package<br>Sphere<br>Type <sup>2</sup>                                                                               | Processor Frequency/<br>DDR Data Rate <sup>3</sup>                                                                                                                                                                                   | Silicon<br>Revision                                                                                                         |

| MPC<br>PPC                   | 8572               | E = Included<br>Blank = Not<br>included | Blank = 0 to 105°C<br>C = −40 to 105°C | Blank =<br>Standard<br>L = Low | PX =<br>Leaded,<br>FC-PBGA<br>VT = Pb-free,<br>FC-PBGA <sup>4</sup><br>VJ = Fully<br>Pb-free<br>FC-PBGA <sup>5</sup> | AVN =<br>1500-MHz processor;<br>800 MT/s DDR data rate<br>AUL =<br>1333-MHz processor;<br>667 MT/s DDR data rate<br>ATL =<br>1200-MHz processor;<br>667 MT/s DDR data rate<br>ARL =<br>1067-MHz processor;<br>667 MT/s DDR data rate | E = Ver. 2.2.1<br>(SVR =<br>0x80E8_0022)<br>SEC included<br>E = Ver. 2.2.1<br>(SVR =<br>0x80E0_0022)<br>SEC not<br>included |

Notes:

- <sup>1</sup> MPC stands for "Qualified."

- PPC stands for "Prototype"

- <sup>2</sup> See Section 18, "Package Description," for more information on the available package types.

- <sup>3</sup> Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

- 4. The VT part number is ROHS-compliant with the permitted exception of the C4 die bumps.

- 5. The VJ part number is entirely lead-free. This includes the C4 die bumps.