# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                        |

| Speed                           | 1.2GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR2, DDR3                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 1023-BFBGA, FCBGA                                                     |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572vtatle |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing.

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs.

- Interrupt summary registers allow fast identification of interrupt source.

- Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, SSL/TLS, SRTP, 802.16e, and 3GPP

- Four crypto-channels, each supporting multi-command descriptor chains

- Dynamic assignment of crypto-execution units through an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- PKEU—public key execution unit

- RSA and Diffie-Hellman; programmable field size up to 4096 bits

- Elliptic curve cryptography with F<sub>2</sub>m and F(p) modes and programmable field size up to 1023 bits

- DEU—Data Encryption Standard execution unit

- DES, 3DES

- Two key (K1, K2, K1) or three key (K1, K2, K3)

- ECB, CBC and OFB-64 modes for both DES and 3DES

- AESU—Advanced Encryption Standard unit

- Implements the Rijndael symmetric key cipher

- ECB, CBC, CTR, CCM, GCM, CMAC, OFB-128, CFB-128, and LRW modes

- 128-, 192-, and 256-bit key lengths

- AFEU—ARC four execution unit

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- MDEU—message digest execution unit

- SHA-1 with 160-bit message digest

- SHA-2 (SHA-256, SHA-384, SHA-512)

- MD5 with 128-bit message digest

- HMAC with all algorithms

- KEU—Kasumi execution unit

- Implements F8 algorithm for encryption and F9 algorithm for integrity checking

- Also supports A5/3 and GEA-3 algorithms

- RNG—random number generator

- XOR engine for parity checking in RAID storage applications

- CRC execution unit

- CRC-32 and CRC-32C

- Pattern Matching Engine with DEFLATE decompression

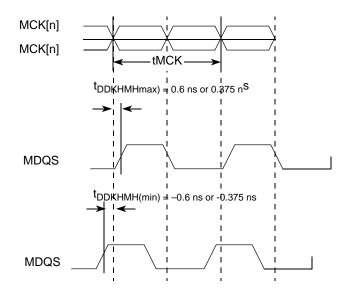

Figure 4 shows the DDR2 and DDR3 SDRAM Interface output timing for the MCK to MDQS skew measurement (tDDKHMH).

Figure 4. Timing Diagram for tDDKHMH

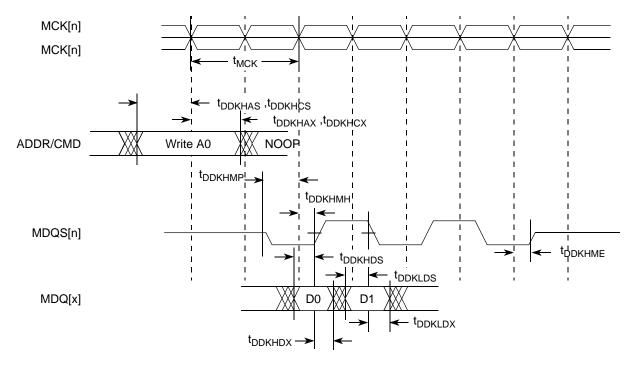

Figure 5 shows the DDR2 and DDR3 SDRAM Interface output timing diagram.

Figure 5. DDR2 and DDR3 SDRAM Interface Output Timing Diagram

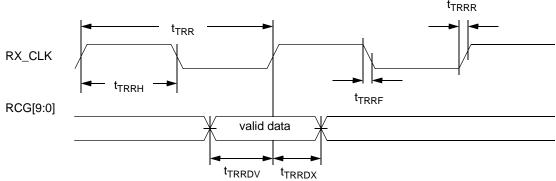

Figure 17 shows the TBI receive the timing diagram.

Figure 17. TBI Single-Clock Mode Receive AC Timing Diagram

### 8.2.6 **RGMII and RTBI AC Timing Specifications**

Table 34 presents the RGMII and RTBI AC timing specifications.

#### Table 34. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $\text{LV}_{\text{DD}}/\text{TV}_{\text{DD}}$  of 2.5 V ± 5%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min  | Тур | Мах  | Unit |

|--------------------------------------------------------|-------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT</sub>                  | -500 | 0   | 500  | ps   |

| Data to clock input skew (at receiver) <sup>2</sup>    | t <sub>SKRGT</sub>                  | 1.0  | _   | 2.8  | ns   |

| Clock period <sup>3</sup>                              | t <sub>RGT</sub>                    | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 4</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub> | 40   | 50  | 60   | %    |

| Rise time (20%–80%)                                    | t <sub>rgtr</sub>                   | —    | _   | 0.75 | ns   |

| Fall time (20%–80%)                                    | t <sub>RGTF</sub>                   | —    | _   | 0.75 | ns   |

#### Notes:

- 1. Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns will be added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

## 8.3.4 SGMII AC Timing Specifications

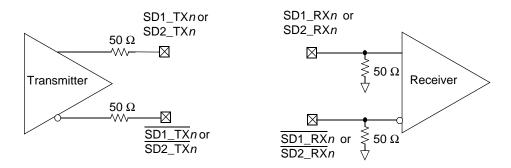

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs ( $SD2_TX[n]$  and  $\overline{SD2_TX[n]}$ ) or at the receiver inputs ( $SD2_RX[n]$  and  $\overline{SD2_RX[n]}$ ) as depicted in Figure 25, respectively.

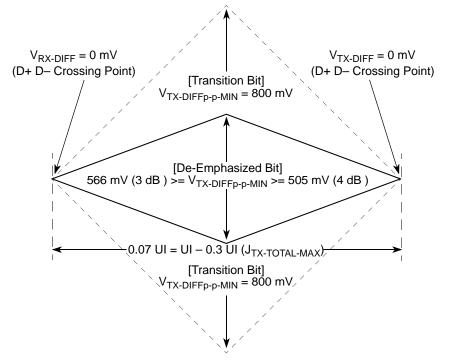

### 8.3.4.1 SGMII Transmit AC Timing Specifications

Table 40 provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### Table 40. SGMII Transmit AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2}$  = 1.1V ± 5%.

| Parameter                           | Symbol            | Min    | Тур | Max    | Unit   | Notes |

|-------------------------------------|-------------------|--------|-----|--------|--------|-------|

| Deterministic Jitter                | JD                | —      | _   | 0.17   | UI p-p | _     |

| Total Jitter                        | JT                | —      | _   | 0.35   | UI p-p | _     |

| Unit Interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1     |

| V <sub>OD</sub> fall time (80%-20%) | tfall             | 50     | _   | 120    | ps     | _     |

| V <sub>OD</sub> rise time (20%-80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     | _     |

Notes:

1. Each UI is 800 ps  $\pm$  100 ppm.

### 8.3.4.2 SGMII Receive AC Timing Specifications

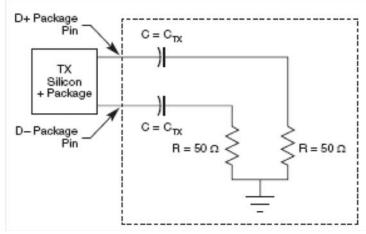

Table 41 provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 24 shows the SGMII receiver input compliance mask eye diagram.

#### Table 41. SGMII Receive AC Timing Specifications

At recommended operating conditions with  $XV_{DD\_SRDS2} = 1.1V \pm 5\%$ .

| Parameter                                          | Symbol          | Min    | Тур | Max               | Unit   | Notes |

|----------------------------------------------------|-----------------|--------|-----|-------------------|--------|-------|

| Deterministic Jitter Tolerance                     | JD              | 0.37   | —   | —                 | UI p-p | 1     |

| Combined Deterministic and Random Jitter Tolerance | JDR             | 0.55   | —   | _                 | UI p-p | 1     |

| Sinusoidal Jitter Tolerance                        | JSIN            | 0.1    | —   | —                 | UI p-p | 1     |

| Total Jitter Tolerance                             | JT              | 0.65   |     | _                 | UI p-p | 1     |

| Bit Error Ratio                                    | BER             | _      | —   | 10 <sup>-12</sup> |        | _     |

| Unit Interval                                      | UI              | 799.92 | 800 | 800.08            | ps     | 2     |

| AC Coupling Capacitor                              | C <sub>TX</sub> | 5      | —   | 200               | nF     | 3     |

Notes:

1. Measured at receiver.

2. Each UI is 800 ps  $\pm$  100 ppm.

3. The external AC coupling capacitor is required. It is recommended to be placed near the device transmitter outputs.

4. See RapidIO 1x/4x LP Serial Physical Layer Specification for interpretation of jitter specifications.

### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

Figure 24. SGMII Receiver Input Compliance Mask

Figure 25. SGMII AC Test/Measurement Load

**Ethernet Management Interface Electrical Characteristics**

Table 43. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=3.3 V) (continued)

| Parameter                                                                             | Symbol          | Min  | Мах | Unit | Notes |

|---------------------------------------------------------------------------------------|-----------------|------|-----|------|-------|

| Input low current (LV <sub>DD</sub> /TV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V) | I <sub>IL</sub> | -600 | _   | μΑ   | _     |

Note:

1. EC1\_MDC and EC1\_MDIO operate on LV<sub>DD</sub>.

2. EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

3. Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  and  $TV_{IN}$  symbol referenced in Table 1.

#### Table 44. MII Management DC Electrical Characteristics (LV<sub>DD</sub>/TV<sub>DD</sub>=2.5 V)

| Parameters                                                         | Symbol                             | Min       | Мах                                      | Unit | Notes  |

|--------------------------------------------------------------------|------------------------------------|-----------|------------------------------------------|------|--------|

| Supply voltage 2.5 V                                               | LV <sub>DD/</sub> TV <sub>DD</sub> | 2.37      | 2.63                                     | V    | 1,2    |

| Output high voltage<br>( $LV_{DD}/TV_{DD} = Min, IOH = -1.0 mA$ )  | V <sub>OH</sub>                    | 2.00      | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _      |

| Output low voltage<br>( $LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA$ ) | V <sub>OL</sub>                    | GND – 0.3 | 0.40                                     | V    | _      |

| Input high voltage                                                 | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$                  | V    | _      |

| Input low voltage                                                  | V <sub>IL</sub>                    | -0.3      | 0.70                                     | V    | _      |

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$          | IIH                                | _         | 10                                       | μA   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                       | IIL                                | -15       | _                                        | μΑ   | 3      |

#### Note:

$^1\,$  EC1\_MDC and EC1\_MDIO operate on LV\_DD.

<sup>2</sup> EC3\_MDC & EC3\_MDIO and EC5\_MDC & EC5\_MDIO operate on TV<sub>DD</sub>.

$^3\,$  Note that the symbol V\_{IN}, in this case, represents the LV\_{IN} and TV\_{IN} symbols referenced in Table 1.

## 9.2 MII Management AC Electrical Specifications

Table 45 provides the MII management AC timing specifications. There are three sets of Ethernet management signals (EC1\_MDC and EC1\_MDIO, EC3\_MDC and EC3\_MDIO, EC5\_MDC and EC5\_MDIO). These are not explicitly shown in the table or in the figure following.

#### Table 45. MII Management AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%.

| Parameter/Condition            | Symbol <sup>1</sup> | Min   | Тур | Мах                     | Unit | Notes |

|--------------------------------|---------------------|-------|-----|-------------------------|------|-------|

| ECn_MDC frequency              | f <sub>MDC</sub>    | 0.9   | 2.5 | 9.3                     | MHz  | 2, 3  |

| ECn_MDC period                 | t <sub>MDC</sub>    | 107.5 | _   | 1120                    | ns   | —     |

| ECn_MDC clock pulse width high | t <sub>MDCH</sub>   | 32    | _   | _                       | ns   | —     |

| ECn_MDC to ECn_MDIO delay      | t <sub>MDKHDX</sub> | 10    | _   | 16*t <sub>plb_clk</sub> | ns   | 5     |

# NP

#### Local Bus Controller (eLBC)

Table 50. Local Bus General Timing Parameters ( $BV_{DD} = 2.5 V DC$ )—PLL Enabled (continued)At recommended operating conditions with  $BV_{DD}$  of 2.5 V ± 5% (continued)

| Parameter                                                          | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output valid (except LAD/LDP and LALE)          | t <sub>LBKHOV1</sub> | —   | 2.4 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                          | t <sub>LBKHOV2</sub> | —   | 2.5 | ns   | 3     |

| Local bus clock to address valid for LAD                           | t <sub>LBKHOV3</sub> | —   | 2.4 | ns   | 3     |

| Local bus clock to LALE assertion                                  | t <sub>LBKHOV4</sub> | —   | 2.4 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)         | t <sub>LBKHOX1</sub> | 0.8 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKHOX2</sub> | 0.8 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKHOZ1</sub> | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKHOZ2</sub> | —   | 2.6 | ns   | 5     |

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 2.5-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

Table 51 describes the general timing parameters of the local bus interface at  $BV_{DD} = 1.8 \text{ V DC}$

Table 51. Local Bus General Timing Parameters ( $BV_{DD} = 1.8 V DC$ )—PLL Enabled At recommended operating conditions with  $BV_{DD}$  of 1.8 V ± 5%

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 6.67 | 12  | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43   | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                  | t <sub>LBKSKEW</sub>                | _    | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 2.4  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKH2</sub>                | 1.9  | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | 1.1  | —   | ns   | 3, 4  |

High-Speed Serial Interfaces (HSSI)

SD1\_REF\_CLK for PCI Express and Serial RapidIO, or SD2\_REF\_CLK and SD2\_REF\_CLK for the SGMII interface respectively.

The following sections describe the SerDes reference clock requirements and some application information.

# **15.2.1 SerDes Reference Clock Receiver Characteristics**

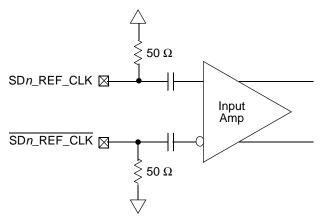

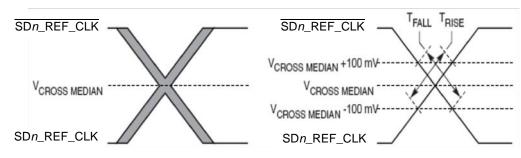

Figure 44 shows a receiver reference diagram of the SerDes reference clocks. Characteristics are as follows:

- The supply voltage requirements for  $XV_{DD SRDS2}$  are specified in Table 1 and Table 2.

- SerDes Reference Clock Receiver Reference Circuit Structure

- The SDn\_REF\_CLK and SDn\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 44. Each differential clock input (SDn\_REF\_CLK or SDn\_REF\_CLK) has on-chip 50-Ω termination to SGND\_SRDSn (xcorevss) followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. Refer to the Differential Mode and Single-ended Mode description below for further detailed requirements.

- The maximum average current requirement that also determines the common mode voltage range

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA (refer to the following bullet for more detail), because the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V/50 = 8 mA) while the minimum common mode input level is 0.1 V above SGND\_SRDS*n* (xcorevss). For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 mA to 16 mA (0-0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SD*n*\_REF\_CLK and  $\overline{\text{SD}n_\text{REF}\text{-}\text{CLK}}$  inputs cannot drive 50  $\Omega$  to SGND\_SRDS*n* (xcorevss) DC, or it exceeds the maximum input current limitations, then it must be AC-coupled off-chip.

- The input amplitude requirement

- This requirement is described in detail in the following sections.

Figure 44. Receiver of SerDes Reference Clocks

### 15.2.2 DC Level Requirement for SerDes Reference Clocks

The DC level requirement for the MPC8572E SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs as described below.

- Differential Mode

- The input amplitude of the differential clock must be between 400mV and 1600mV differential peak-peak (or between 200mV and 800mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing less than 800mV and greater than 200mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

- For external DC-coupled connection, as described in Section 15.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 mV and 400 mV.

Figure 45 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Because the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND\_SRDSn. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND\_SRDSn). Figure 46 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

- Single-ended Mode

- The reference clock can also be single-ended. The SDn\_REF\_CLK input amplitude (single-ended swing) must be between 400 mV and 800 mV peak-peak (from Vmin to Vmax) with SDn\_REF\_CLK either left unconnected or tied to ground.

- The SDn\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 47 shows the SerDes reference clock input requirement for single-ended signaling mode.

#### High-Speed Serial Interfaces (HSSI)

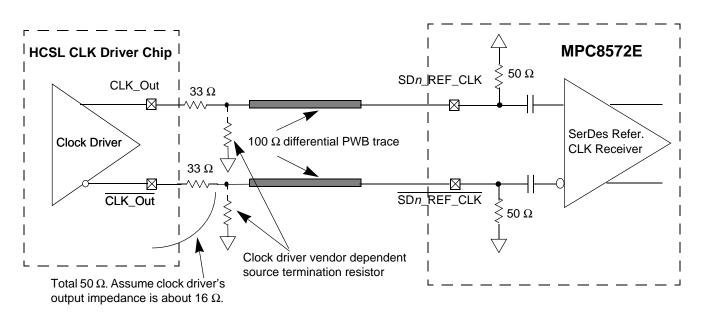

Figure 48 shows the SerDes reference clock connection reference circuits for HCSL type clock driver. It assumes that the DC levels of the clock driver chip is compatible with MPC8572E SerDes reference clock input's DC requirement.

Figure 48. DC-Coupled Differential Connection with HCSL Clock Driver (Reference Only)

High-Speed Serial Interfaces (HSSI)

Figure 53. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes Reference Clocks is defined by each interface protocol based on application usage. Refer to the following sections for detailed information:

- Section 8.3.2, "AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK"

- Section 16.2, "AC Requirements for PCI Express SerDes Reference Clocks"

- Section 17.2, "AC Requirements for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK"

### 15.2.4.1 Spread Spectrum Clock

SD1\_REF\_CLK/SD1\_REF\_CLK are designed to work with a spread spectrum clock (+0 to -0.5% spreading at 30-33 KHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation should be used.

SD2\_REF\_CLK/SD2\_REF\_CLK are not to be used with, and should not be clocked by, a spread spectrum clock source.

# 15.3 SerDes Transmitter and Receiver Reference Circuits

Figure 54 shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 54. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in each interface protocol section below (PCI Express, Serial Rapid IO or SGMII) in this document based on the application usage:

- Section 8.3, "SGMII Interface Electrical Characteristics"

- Section 16, "PCI Express"

### 16.4.3 Differential Receiver (RX) Input Specifications

Table 63 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

| Symbol                  | Parameter                                     | Min    | Nominal | Max    | Units | Comments                                                                                                                                                                                    |

|-------------------------|-----------------------------------------------|--------|---------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                      | Unit Interval                                 | 399.88 | 400     | 400.12 | ps    | Each UI is 400 ps ± 300 ppm. UI does not<br>account for Spread Spectrum Clock<br>dictated variations. See Note 1.                                                                           |

| V <sub>RX-DIFFp-p</sub> | Differential Input<br>Peak-to-Peak<br>Voltage | 0.175  | _       | 1.200  | V     | $V_{RX-DIFFp-p} = 2^*  V_{RX-D+} - V_{RX-D-} $<br>See Note 2.                                                                                                                               |

| T <sub>RX-EYE</sub>     | Minimum<br>Receiver Eye<br>Width              | 0.4    |         |        | UI    | The maximum interconnect media and<br>Transmitter jitter that can be tolerated by<br>the Receiver can be derived as<br>$T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6 UI.$<br>See Notes 2 and 3. |

Table 63. Differential Receiver (RX) Input Specifications

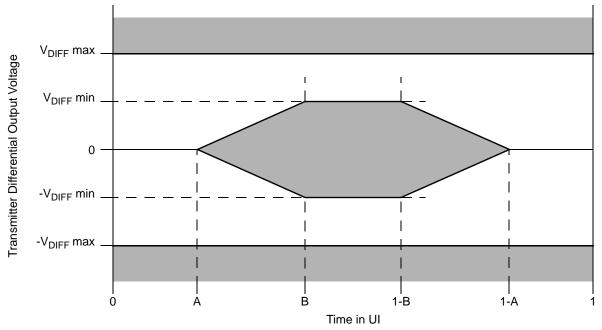

Serial RapidIO

Figure 58. Transmitter Output Compliance Mask

| Transmitter Type        | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|-------------------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud short range  | 250                        | 500                        | 0.175  | 0.39   |

| 1.25 GBaud long range   | 400                        | 800                        | 0.175  | 0.39   |

| 2.5 GBaud short range   | 250                        | 500                        | 0.175  | 0.39   |

| 2.5 GBaud long range    | 400                        | 800                        | 0.175  | 0.39   |

| 3.125 GBaud short range | 250                        | 500                        | 0.175  | 0.39   |

| 3.125 GBaud long range  | 400                        | 800                        | 0.175  | 0.39   |

Table 71. Transmitter Differential Output Eye Diagram Parameters

# 17.6 Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance shall result in a differential return loss better that 10 dB and a common mode return loss better than 6 dB from 100 MHz to  $(0.8) \times$  (Baud Frequency). This includes contributions from on-chip circuitry, the chip package and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100 Ohm resistive for differential return loss and 25- $\Omega$  resistive for common mode.

| Characteristic                                     | Symbol          | Ra   | nge               | Unit   | Notes                                                              |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------------|

| Gharacteristic                                     | Min Max         |      | Max               | Unit   | NOLES                                                              |

| Differential Input Voltage                         | V <sub>IN</sub> | 200  | 1600              | mV p-p | Measured at receiver                                               |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37 | _                 | UI p-p | Measured at receiver                                               |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55 | _                 | UI p-p | Measured at receiver                                               |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | _                 | UI p-p | Measured at receiver                                               |

| Multiple Input Skew                                | S <sub>MI</sub> | —    | 24                | ns     | Skew at the receiver input<br>between lanes of a multilane<br>link |

| Bit Error Rate                                     | BER             | —    | 10 <sup>-12</sup> | —      | _                                                                  |

| Unit Interval                                      | UI              | 800  | 800               | ps     | +/- 100 ppm                                                        |

#### Table 72. Receiver AC Timing Specifications—1.25 GBaud

Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 59. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                              |  |  |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------------|--|--|

| Characteristic                                     |                 | Min   | Max               | Unit   | Noles                                                              |  |  |

| Differential Input Voltage                         | V <sub>IN</sub> | 200   | 1600              | mV p-p | Measured at receiver                                               |  |  |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37  | _                 | UI p-p | Measured at receiver                                               |  |  |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55  | —                 | UI p-p | Measured at receiver                                               |  |  |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | _                 | UI p-p | Measured at receiver                                               |  |  |

| Multiple Input Skew                                | S <sub>MI</sub> | _     | 24                | ns     | Skew at the receiver input<br>between lanes of a multilane<br>link |  |  |

| Bit Error Rate                                     | BER             | —     | 10 <sup>-12</sup> | —      | —                                                                  |  |  |

| Unit Interval                                      | UI              | 400   | 400               | ps     | +/– 100 ppm                                                        |  |  |

#### Table 73. Receiver AC Timing Specifications—2.5 GBaud

Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 59. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

Serial RapidIO

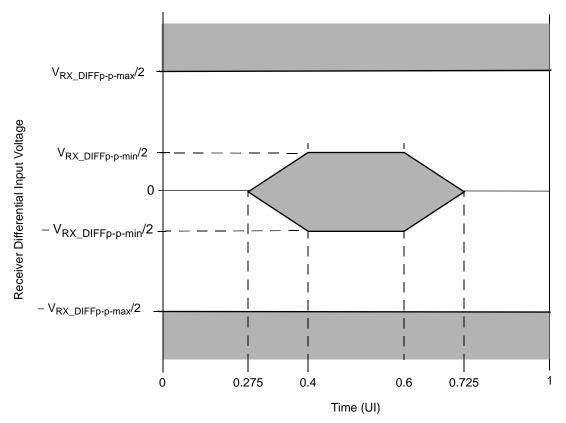

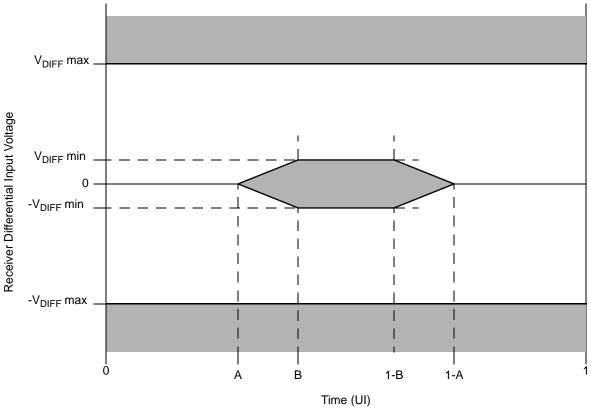

Figure 60. Receiver Input Compliance Mask

| Receiver Type | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|---------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud    | 100                        | 800                        | 0.275  | 0.400  |

| 2.5 GBaud     | 100                        | 800                        | 0.275  | 0.400  |

| 3.125 GBaud   | 100                        | 800                        | 0.275  | 0.400  |

# 17.8 Measurement and Test Requirements

Because the LP-Serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002, the measurement and test requirements defined here are similarly guided by Clause 47. Additionally, the CJPAT test pattern defined in Annex 48A of IEEE 802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter measurements. Annex 48B of IEEE 802.3ae-2002 is recommended as a reference for additional information on jitter test methods.

# 17.8.1 Eye Template Measurements

For the purpose of eye template measurements, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for template measurements is the Continuous Jitter Test Pattern (CJPAT) defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial

Package Description

| Signal               | Signal Name                  | Package Pin Number                                                                                                                                                                  | Pin Type | Power<br>Supply  | Notes   |

|----------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| D2_MBA[0:2]          | Bank Select                  | Y1, W3, P3                                                                                                                                                                          | 0        | GV <sub>DD</sub> | _       |

| D2_MWE               | Write Enable                 | AA2                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MCAS              | Column Address Strobe        | AD1                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MRAS              | Row Address Strobe           | AA1                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MCKE[0:3]         | Clock Enable                 | L3, L1, K1, K2                                                                                                                                                                      | 0        | GV <sub>DD</sub> | 11      |

| D2_MCS[0:3]          | Chip Select                  | AB1, AG2, AC1, AH2                                                                                                                                                                  | 0        | GV <sub>DD</sub> | _       |

| D2_MCK[0:5]          | Clock                        | V4, F7, AJ3, V2, E7,<br>AG4                                                                                                                                                         | 0        | GV <sub>DD</sub> | —       |

| D2_MCK[0:5]          | Clock Complements            | V1, F8, AJ4, U1, E6,<br>AG5                                                                                                                                                         | 0        | GV <sub>DD</sub> | —       |

| D2_MODT[0:3]         | On Die Termination           | AE1, AG1, AE2, AH1                                                                                                                                                                  | 0        | GV <sub>DD</sub> | —       |

| D2_MDIC[0:1]         | Driver Impedance Calibration | F1, G1                                                                                                                                                                              | I/O      | GV <sub>DD</sub> | 25      |

|                      | Local Bus Contr              | oller Interface                                                                                                                                                                     |          |                  |         |

| LAD[0:31]            | Muxed Data/Address           | M22, L22, F22, G22,<br>F21, G21, E20, H22,<br>K22, K21, H19, J20,<br>J19, L20, M20, M19,<br>E22, E21, L19, K19,<br>G19, H18, E18, G18,<br>J17, K17, K14, J15,<br>H16, J14, H15, G15 | I/O      | BV <sub>DD</sub> | 34      |

| LDP[0:3]             | Data Parity                  | M21, D22, A24, E17                                                                                                                                                                  | I/O      | BV <sub>DD</sub> | _       |

| LA[27]               | Burst Address                | J21                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LA[28:31]            | Port Address                 | F20, K18, H20, G17                                                                                                                                                                  | 0        | BV <sub>DD</sub> | 5, 7, 9 |

| LCS[0:4]             | Chip Selects                 | B23, E16, D20, B25,<br>A22                                                                                                                                                          | 0        | BV <sub>DD</sub> | 10      |

| LCS[5]/DMA2_DREQ[1]  | Chip Selects / DMA Request   | D19                                                                                                                                                                                 | I/O      | BV <sub>DD</sub> | 1, 10   |

| LCS[6]/DMA2_DACK[1]  | Chip Selects / DMA Ack       | E19                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 1, 10   |

| LCS[7]/DMA2_DDONE[1] | Chip Selects / DMA Done      | C21                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 1, 10   |

| LWE[0]/LBS[0]/LFWE   | Write Enable / Byte Select   | D17                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[1]/LBS[1]        | Write Enable / Byte Select   | F15                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[2]/LBS[2]        | Write Enable / Byte Select   | B24                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[3]/LBS[3]        | Write Enable / Byte Select   | D18                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LALE                 | Address Latch Enable         | F19                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                | Buffer Control               | L18                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| Signal     | Signal Name                                     | Package Pin Number                                                                                                                                                                                                                                                                                                                                            | Pin Type | Power<br>Supply | Notes |  |

|------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|-------|--|

| SGND_SRDS1 | SerDes Transceiver Core Logic<br>GND (xcorevss) | C28, C32, D30, E31,<br>F28, F29, G32, H28,<br>H30, J28, K29, L32,<br>M30, N31, P29, R32                                                                                                                                                                                                                                                                       | _        | _               | _     |  |

| SGND_SRDS2 | SerDes Transceiver Core Logic<br>GND (xcorevss) | AE28, AE30, AF28,<br>AF32, AG28, AG30,<br>AH28, AJ28, AJ31,<br>AL32                                                                                                                                                                                                                                                                                           | _        | _               |       |  |

| AGND_SRDS1 | SerDes PLL GND                                  | J31                                                                                                                                                                                                                                                                                                                                                           | —        | —               | _     |  |

| AGND_SRDS2 | SerDes PLL GND                                  | AH31                                                                                                                                                                                                                                                                                                                                                          | —        | —               | _     |  |

| OVDD       | General I/O Supply                              | U31, V24, V28, Y31,<br>AA27, AB25, AB29                                                                                                                                                                                                                                                                                                                       | —        | OVDD            | _     |  |

| LVDD       | TSEC 1&2 I/O Supply                             | AC18, AC21, AG21,<br>AL27                                                                                                                                                                                                                                                                                                                                     | —        | LVDD            | _     |  |

| TVDD       | TSEC 3&4 I/O Supply                             | AC15, AE16, AH18                                                                                                                                                                                                                                                                                                                                              | —        | TVDD            | _     |  |

| GVDD       | SSTL_1.8 DDR Supply                             | B2, B5, B8, B11, B14,<br>D4, D7, D10, D13, E2,<br>F6, F9, F12, G4, H2,<br>H8, H11, H14, J6, K4,<br>K10, K13, L2, L8, M6,<br>N4, N10, P2, P8, R6,<br>T4, T10, U2, U8, V6,<br>W4, W10, Y2, Y8, AA6,<br>AB4, AB10, AC2, AC8,<br>AD6, AD12, AE4,<br>AE10, AF2, AF8, AG6,<br>AG12, AH4, AH10,<br>AH16, AJ2, AJ8, AJ14,<br>AK6, AK12, AK18, AL4,<br>AL10, AL16, AM2 |          | GVDD            | _     |  |

| BVDD       | Local Bus and GPIO Supply                       | A26, A30, B21, D16,<br>D21, F18, G20, H17,<br>J22, K15, K20                                                                                                                                                                                                                                                                                                   | —        | BVDD            | _     |  |

| Signal             | Signal Name                         | Package Pin Number | Pin Type | Power<br>Supply         | Notes |

|--------------------|-------------------------------------|--------------------|----------|-------------------------|-------|

| SD1_IMP_CAL_RX     | SerDes1 Rx Impedance<br>Calibration | B32                | I        | 200Ω<br>(±1%) to<br>GND | _     |

| SD1_IMP_CAL_TX     | SerDes1 Tx Impedance<br>Calibration | T32                | I        | 100Ω<br>(±1%) to<br>GND | _     |

| SD1_PLL_TPA        | SerDes1 PLL Test Point Analog       | J30                | 0        | AVDD_S<br>RDS<br>analog | 17    |

| SD2_IMP_CAL_RX     | SerDes2 Rx Impedance<br>Calibration | AC32               | I        | 200Ω<br>(±1%) to<br>GND | —     |

| SD2_IMP_CAL_TX     | SerDes2 Tx Impedance<br>Calibration | AM32               | I        | 100Ω<br>(±1%) to<br>GND | —     |

| SD2_PLL_TPA        | SerDes2 PLL Test Point Analog       | AH30               | 0        | AVDD_S<br>RDS<br>analog | 17    |

| TEMP_ANODE         | Temperature Diode Anode             | AA31               | _        | internal<br>diode       | 14    |

| TEMP_CATHODE       | Temperature Diode Cathode           | AB31               |          | internal<br>diode       | 14    |

| No Connection Pins |                                     | 1                  |          | 11                      |       |

### Table 76. MPC8572E Pinout Listing (continued)

Table 85 summarizes the signal impedance targets. The driver impedances are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet, DUART,<br>Control, Configuration, Power<br>Management | DDR DRAM                                                         | Symbol         | Unit |

|----------------|----------------------------------------------------------------------------|------------------------------------------------------------------|----------------|------|

| R <sub>N</sub> | 45 Target                                                                  | 18 Target (full strength mode)<br>36 Target (half strength mode) | Z <sub>0</sub> | Ω    |

| R <sub>P</sub> | 45 Target                                                                  | 18 Target (full strength mode)<br>36 Target (half strength mode) | Z <sub>0</sub> | Ω    |

Table 85. Impedance Characteristics

**Note:** Nominal supply voltages. See Table 1,  $T_i = 105^{\circ}C$ .

# 21.8 Configuration Pin Muxing

The MPC8572E provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While  $\overline{\text{HRESET}}$  is asserted however, these pins are treated as inputs. The value presented on these pins while  $\overline{\text{HRESET}}$  is asserted, is latched when  $\overline{\text{HRESET}}$  deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Most of these sampled configuration pins are equipped with an on-chip gated resistor of approximately 20 kΩ. This value should permit the 4.7-kΩ resistor to pull the configuration pin to a valid logic low level. The pull-up resistor is enabled only during  $\overline{\text{HRESET}}$  (and for platform /system clocks after  $\overline{\text{HRESET}}$  deassertion to ensure capture of the reset value). When the input receiver is disabled the pull-up is also, thus allowing functional operation of the pin as an output with minimal signal quality or delay disruption. The default value for all configuration bits treated this way has been encoded such that a high voltage level puts the device into the default state and external resistors are needed only when non-default settings are required by the user.

Careful board layout with stubless connections to these pull-down resistors coupled with the large value of the pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

The platform PLL ratio, DDR complex PLL and e500 PLL ratio configuration pins are not equipped with these default pull-up devices.

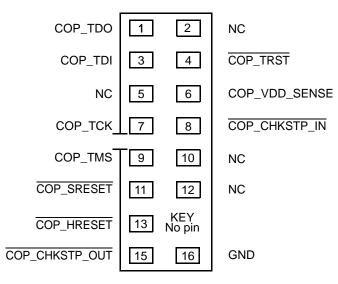

# 21.9 JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 66. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The  $\overline{\text{TRST}}$  signal is optional in the IEEE Std 1149.1 specification, but it is provided on all processors built on Power Architecture technology. The device requires  $\overline{\text{TRST}}$  to be asserted during power-on reset flow to ensure that the JTAG boundary

System Design Information

Figure 65. COP Connector Physical Pinout