# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                        |

| Speed                           | 1.5GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR2, DDR3                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 1023-BFBGA, FCBGA                                                     |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8572vtavnb |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- CRC generation and verification of inbound/outbound frames

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- Two MII management interfaces for control and status

- Ability to force allocation of header information and buffer descriptors into L2 cache

- 10/100 Fast Ethernet controller (FEC) management interface

- 10/100 Mbps full and half-duplex IEEE 802.3 MII for system management

- Note: When enabled, the FEC occupies eTSEC3 and eTSEC4 parallel interface signals. In such a mode, eTSEC3 and eTSEC4 are only available through SGMII interfaces.

- OCeaN switch fabric

- Full crossbar packet switch

- Reorders packets from a source based on priorities

- Reorders packets to bypass blocked packets

- Implements starvation avoidance algorithms

- Supports packets with payloads of up to 256 bytes

- Two integrated DMA controllers

- Four DMA channels per controller

- All channels accessible by the local masters

- Extended DMA functions (advanced chaining and striding capability)

- Misaligned transfer capability

- Interrupt on completed segment, link, list, and error

- Supports transfers to or from any local memory or I/O port

- Selectable hardware-enforced coherency (snoop/no snoop)

- Ability to start and flow control up to 4 (both Channel 0 and 1 for each DMA Controller) of the 8 total DMA channels from external 3-pin interface by the remote masters

- The Channel 2 of DMA Controller 2 is only allowed to initiate and start a DMA transfer by the remote master, because only one of the 3-external pins (DMA2\_DREQ[2]) is made available

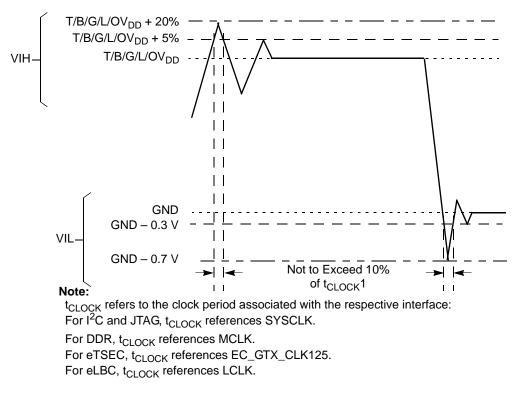

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8572E.

### Figure 2. Overshoot/Undershoot Voltage for TV<sub>DD</sub>/BV<sub>DD</sub>/GV<sub>DD</sub>/LV<sub>DD</sub>/OV<sub>DD</sub>

The core voltage must always be provided at nominal 1.1 V. (See Table 2 for actual recommended core voltage.) Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ , and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR2 and DDR3 SDRAM interface uses differential receivers referenced by the externally supplied  $MV_{REF}n$  signal (nominally set to  $GV_{DD}/2$ ) as is appropriate for the SSTL\_1.8 electrical signaling standard for DDR2 or 1.5-V electrical signaling for DDR3. The DDR DQS receivers cannot be operated in single-ended fashion. The complement signal must be properly driven and cannot be grounded.

# NP

#### DDR2 and DDR3 SDRAM Controller

Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications (continued)

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter           | Symbol <sup>1</sup> | Min                             | Мах                                                                 | Unit | Notes |

|---------------------|---------------------|---------------------------------|---------------------------------------------------------------------|------|-------|

| 533 MHz             |                     | 538                             | —                                                                   |      |       |

| 400 MHz             |                     | 700                             | —                                                                   |      |       |

| MDQS preamble start | t <sub>DDKHMP</sub> |                                 |                                                                     | ns   | 6     |

| 800 MHz             |                     | $-0.5 \times t_{MCK} - 0.375$   | $\begin{array}{c} -0.5 \times t_{\text{MCK}} \\ +0.375 \end{array}$ |      |       |

| <= 667 MHz          |                     | $-0.5\times t_{\text{MCK}}-0.6$ | $-0.5 	imes t_{MCK}$ +0.6                                           |      |       |

| MDQS epilogue end   | t <sub>DDKHME</sub> |                                 |                                                                     | ns   | 6     |

| 800 MHz             |                     | -0.375                          | 0.375                                                               |      |       |

| <= 667 MHz          | t <sub>DDKHME</sub> | -0.6                            | 0.6                                                                 | ns   | 6     |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub>

(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the MDQS override bits (called WR\_DATA\_DELAY) in the TIMING\_CFG\_2 register. This typically be set to the same delay as in DDR\_SDRAM\_CLK\_CNTL[CLK\_ADJUST]. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8572E PowerQUICC<sup>TM</sup> III Integrated Host Processor Family Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

### NOTE

For the ADDR/CMD setup and hold specifications in Table 18, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

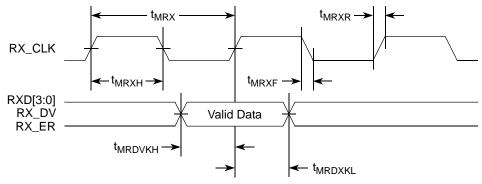

Figure 14 shows the MII receive AC timing diagram.

Figure 14. MII Receive AC Timing Diagram

## 8.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

## 8.2.4.1 TBI Transmit AC Timing Specifications

Table 31 provides the TBI transmit AC timing specifications.

### Table 31. TBI Transmit AC Timing Specifications

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>            | Min | Тур | Мах | Unit |

|--------------------------------------------|--------------------------------|-----|-----|-----|------|

| TCG[9:0] setup time GTX_CLK going high     | t <sub>TTKHDV</sub>            | 2.0 | _   | _   | ns   |

| TCG[9:0] hold time from GTX_CLK going high | t <sub>TTKHDX</sub>            | 1.0 | _   | _   | ns   |

| GTX_CLK rise (20%-80%)                     | t <sub>TTXR</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

| GTX_CLK fall time (80%–20%)                | t <sub>TTXF</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

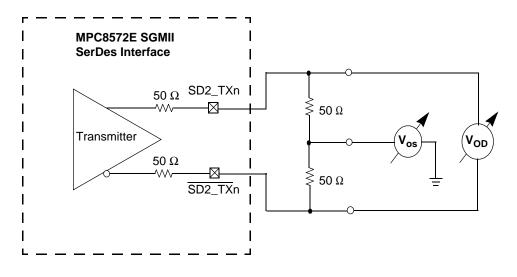

Table 39 lists the SGMII DC receiver electrical characteristics.

| Parameter                        |                | Symbol                  | Min   | Тур                   | Max   | Unit | Notes |

|----------------------------------|----------------|-------------------------|-------|-----------------------|-------|------|-------|

| Supply Voltage                   | Supply Voltage |                         | 1.045 | 1.1                   | 1.155 | V    |       |

| DC Input voltage range           |                | —                       |       | N/A                   |       | _    | 1     |

| Input differential voltage       | LSTS = 0       | V <sub>RX_DIFFp-p</sub> | 100   | —                     | 1200  | mV   | 2, 4  |

|                                  | LSTS = 1       |                         | 175   | —                     |       |      |       |

| Loss of signal threshold         | LSTS = 0       | VLOS                    | 30    | —                     | 100   | mV   | 3, 4  |

|                                  | LSTS = 1       |                         | 65    | —                     | 175   |      |       |

| Input AC common mode v           | voltage        | V <sub>CM_ACp-p</sub>   |       | —                     | 100   | mV   | 5     |

| Receiver differential input      | impedance      | Z <sub>RX_DIFF</sub>    | 80    | 100                   | 120   | Ω    |       |

| Receiver common mode i impedance | nput           | Z <sub>RX_CM</sub>      | 20    | —                     | 35    | Ω    | _     |

| Common mode input volta          | age            | V <sub>CM</sub>         | —     | V <sub>xcorevss</sub> |       | V    | 6     |

Table 39. SGMII DC Receiver Electrical Characteristics

### Note:

1. Input must be externally AC-coupled.

2. V<sub>RX DIFFp-p</sub> is also referred to as peak to peak input differential voltage

3. The concept of this parameter is equivalent to the Electrical Idle Detect Threshold parameter in PCI Express. Refer to PCI Express Differential Receiver (RX) Input Specifications section for further explanation.

4. The LSTS shown in the table refers to the LSTSAB or LSTSEF bit field of MPC8572E's SerDes 2 Control Register.

5.  $V_{\mbox{CM\_ACp-p}}$  is also referred to as peak to peak AC common mode voltage.

6. On-chip termination to SGND\_SRDS2 (xcorevss).

### Table 52. Local Bus General Timing Parameters—PLL Bypassed (continued)

At recommended operating conditions with  $BV_{DD}$  of 3.3 V ± 5%

| Parameter                                                            | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|----------------------------------------------------------------------|----------------------|------|------|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                         | t <sub>LBIXKL2</sub> | -1.3 | _    | ns   | 4, 5  |

| LALE output negation to high impedance for LAD/LDP (LATCH hold time) | t <sub>lbotot</sub>  | 1.5  | _    | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)            | t <sub>LBKLOV1</sub> | _    | -0.3 | ns   |       |

| Local bus clock to data valid for LAD/LDP                            | t <sub>LBKLOV2</sub> | —    | -0.1 | ns   | 4     |

| Local bus clock to address valid for LAD                             | t <sub>LBKLOV3</sub> | —    | 0.0  | ns   | 4     |

| Local bus clock to LALE assertion                                    | t <sub>LBKLOV4</sub> | —    | 0.0  | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)           | t <sub>LBKLOX1</sub> | -3.3 | _    | ns   | 4     |

| Output hold from local bus clock for LAD/LDP                         | t <sub>LBKLOX2</sub> | -3.3 | —    | ns   | 4     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)   | t <sub>LBKLOZ1</sub> | _    | 0.2  | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP                 | t <sub>lbkloz2</sub> | —    | 0.2  | ns   | 7     |

#### Notes:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to local bus clock for PLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which precedes LCLK by t<sub>LBKHKT</sub>.

- 3. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 4. All signals are measured from BVDD/2 of the rising edge of local bus clock for PLL bypass mode to 0.4 x BVDD of the signal in question for 3.3-V signaling levels.

- 5. Input timings are measured at the pin.

- t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

### NOTE

In PLL bypass mode, LCLK[n] is the inverted version of the internal clock with the delay of  $t_{LBKHKT}$ . In this mode, signals are launched at the rising edge of the internal clock and are captured at the falling edge of the internal clock with the exception of LGTA/LUPWAIT (which is captured on the rising edge of the internal clock).

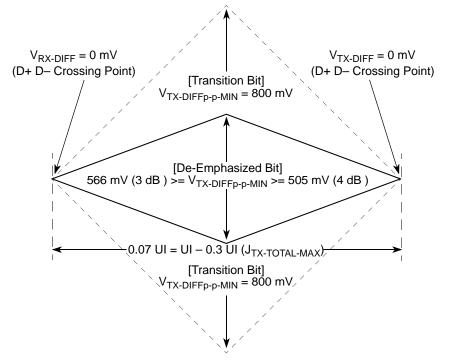

# 16.4.3 Differential Receiver (RX) Input Specifications

Table 63 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

| Symbol                  | Parameter                                     | Min    | Nominal | Max    | Units | Comments                                                                                                                                                                                    |

|-------------------------|-----------------------------------------------|--------|---------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                      | Unit Interval                                 | 399.88 | 400     | 400.12 | ps    | Each UI is 400 ps ± 300 ppm. UI does not<br>account for Spread Spectrum Clock<br>dictated variations. See Note 1.                                                                           |

| V <sub>RX-DIFFp-p</sub> | Differential Input<br>Peak-to-Peak<br>Voltage | 0.175  | _       | 1.200  | V     | $V_{RX-DIFFp-p} = 2^*  V_{RX-D+} - V_{RX-D-} $<br>See Note 2.                                                                                                                               |

| T <sub>RX-EYE</sub>     | Minimum<br>Receiver Eye<br>Width              | 0.4    |         |        | UI    | The maximum interconnect media and<br>Transmitter jitter that can be tolerated by<br>the Receiver can be derived as<br>$T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$ UI.<br>See Notes 2 and 3. |

Table 63. Differential Receiver (RX) Input Specifications

| Symbol               | Parameter  | Min | Nominal | Max | Units | Comments                                                                                                                                                                                                                                 |

|----------------------|------------|-----|---------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L <sub>RX-SKEW</sub> | Total Skew |     |         | 20  | ns    | Skew across all lanes on a Link. This<br>includes variation in the length of SKP<br>ordered set (for example, COM and one to<br>five SKP Symbols) at the RX as well as any<br>delay differences arising from the<br>interconnect itself. |

#### Notes:

- 1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 57 should be used as the RX device when taking measurements (also refer to the Receiver compliance eye diagram shown in Figure 56). If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

- 3. A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the Transmitter and interconnect collected any 250 consecutive UIs. The T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as the reference for the eye diagram.

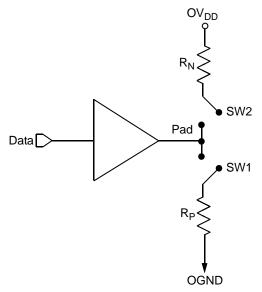

- 4. The Receiver input impedance shall result in a differential return loss greater than or equal to 15 dB with the D+ line biased to 300 mV and the D- line biased to -300 mV and a common mode return loss greater than or equal to 6 dB (no bias required) over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements for is 50 ohms to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50 ohm probes see Figure 57). Note: that the series capacitors CTX is optional for the return loss measurement.

- 5. Impedance during all LTSSM states. When transitioning from a Fundamental Reset to Detect (the initial state of the LTSSM) there is a 5 ms transition time before Receiver termination values must be met on all un-configured Lanes of a Port.

- 6. The RX DC Common Mode Impedance that exists when no power is present or Fundamental Reset is asserted. This helps ensure that the Receiver Detect circuit does not falsely assume a Receiver is powered on when it is not. This term must be measured at 300 mV above the RX ground.

- 7. It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function. Least squares and median deviation fits have worked well with experimental and simulated data.

**Package Description**

- 5. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 6. Parallelism measurement shall exclude any effect of mark on top surface of package.

# 18.3 Pinout Listings

Table 76 provides the pin-out listing for the MPC8572E 1023 FC-PBGA package.

### Table 76. MPC8572E Pinout Listing

| Signal       | Signal Name           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                        | Pin Type | Power<br>Supply  | Notes |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

|              | DDR SDRAM N           | lemory Interface 1                                                                                                                                                                                                                                                                                                                                                                        |          |                  |       |

| D1_MDQ[0:63] | Data                  | D15, A14, B12, D12,<br>A15, B15, B13, C13,<br>C11, D11, D9, A8, A12,<br>A11, A9, B9, F11, G12,<br>K11, K12, E10, E9, J11,<br>J10, G8, H10, L10,<br>M11, F10, G9, K9, K8,<br>AC6, AC7, AG8, AH9,<br>AB6, AB8, AE9, AF9,<br>AL8, AM8, AM10,<br>AK11, AH8, AK8, AJ10,<br>AK10, AL12, AJ12,<br>AL14, AK14, AL11,<br>AM11, AK13, AM14,<br>AM15, AJ16, AL18,<br>AM18, AJ15, AL15,<br>AK17, AM17 | I/O      | GV <sub>DD</sub> | _     |

| D1_MECC[0:7] | Error Correcting Code | M10, M7, R8, T11, L12,<br>L11, P9, R10                                                                                                                                                                                                                                                                                                                                                    | I/O      | GV <sub>DD</sub> | —     |

| D1_MAPAR_ERR | Address Parity Error  | P6                                                                                                                                                                                                                                                                                                                                                                                        | Ι        | GV <sub>DD</sub> | _     |

| D1_MAPAR_OUT | Address Parity Out    | W6                                                                                                                                                                                                                                                                                                                                                                                        | 0        | GV <sub>DD</sub> | _     |

| D1_MDM[0:8]  | Data Mask             | C14, A10, G11, H9,<br>AD7, AJ9, AM12,<br>AK16, N11                                                                                                                                                                                                                                                                                                                                        | 0        | GV <sub>DD</sub> | _     |

| D1_MDQS[0:8] | Data Strobe           | A13, C10, H12, J7,<br>AE8, AM9, AM13,<br>AL17, N9                                                                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | _     |

| D1_MDQS[0:8] | Data Strobe           | D14, B10, H13, J8,<br>AD8, AL9, AJ13,<br>AM16, P10                                                                                                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _     |

| D1_MA[0:15]  | Address               | Y7, W8, U6, W9, U7,<br>V8, Y11, V10, T6, V11,<br>AA10, U9, U10, AD11,<br>T8, P7                                                                                                                                                                                                                                                                                                           | 0        | GV <sub>DD</sub> | _     |

| D1_MBA[0:2]  | Bank Select           | AA7, AA8, R7                                                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> |       |

| D1_MWE       | Write Enable          | AC12                                                                                                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> |       |

Package Description

| Signal               | Signal Name                  | Package Pin Number                                                                                                                                                                  | Pin Type | Power<br>Supply  | Notes   |

|----------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| D2_MBA[0:2]          | Bank Select                  | Y1, W3, P3                                                                                                                                                                          | 0        | GV <sub>DD</sub> |         |

| D2_MWE               | Write Enable                 | AA2                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MCAS              | Column Address Strobe        | AD1                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MRAS              | Row Address Strobe           | AA1                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MCKE[0:3]         | Clock Enable                 | L3, L1, K1, K2                                                                                                                                                                      | 0        | GV <sub>DD</sub> | 11      |

| D2_MCS[0:3]          | Chip Select                  | AB1, AG2, AC1, AH2                                                                                                                                                                  | 0        | GV <sub>DD</sub> | _       |

| D2_MCK[0:5]          | Clock                        | V4, F7, AJ3, V2, E7,<br>AG4                                                                                                                                                         | 0        | GV <sub>DD</sub> | —       |

| D2_MCK[0:5]          | Clock Complements            | V1, F8, AJ4, U1, E6,<br>AG5                                                                                                                                                         | 0        | GV <sub>DD</sub> |         |

| D2_MODT[0:3]         | On Die Termination           | AE1, AG1, AE2, AH1                                                                                                                                                                  | 0        | GV <sub>DD</sub> | _       |

| D2_MDIC[0:1]         | Driver Impedance Calibration | F1, G1                                                                                                                                                                              | I/O      | GV <sub>DD</sub> | 25      |

|                      | Local Bus Contr              | oller Interface                                                                                                                                                                     |          |                  |         |

| LAD[0:31]            | Muxed Data/Address           | M22, L22, F22, G22,<br>F21, G21, E20, H22,<br>K22, K21, H19, J20,<br>J19, L20, M20, M19,<br>E22, E21, L19, K19,<br>G19, H18, E18, G18,<br>J17, K17, K14, J15,<br>H16, J14, H15, G15 | I/O      | BV <sub>DD</sub> | 34      |

| LDP[0:3]             | Data Parity                  | M21, D22, A24, E17                                                                                                                                                                  | I/O      | BV <sub>DD</sub> | _       |

| LA[27]               | Burst Address                | J21                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LA[28:31]            | Port Address                 | F20, K18, H20, G17                                                                                                                                                                  | 0        | BV <sub>DD</sub> | 5, 7, 9 |

| LCS[0:4]             | Chip Selects                 | B23, E16, D20, B25,<br>A22                                                                                                                                                          | 0        | BV <sub>DD</sub> | 10      |

| LCS[5]/DMA2_DREQ[1]  | Chip Selects / DMA Request   | D19                                                                                                                                                                                 | I/O      | BV <sub>DD</sub> | 1, 10   |

| LCS[6]/DMA2_DACK[1]  | Chip Selects / DMA Ack       | E19                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 1, 10   |

| LCS[7]/DMA2_DDONE[1] | Chip Selects / DMA Done      | C21                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 1, 10   |

| LWE[0]/LBS[0]/LFWE   | Write Enable / Byte Select   | D17                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[1]/LBS[1]        | Write Enable / Byte Select   | F15                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[2]/LBS[2]        | Write Enable / Byte Select   | B24                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[3]/LBS[3]        | Write Enable / Byte Select   | D18                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LALE                 | Address Latch Enable         | F19                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                | Buffer Control               | L18                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| Table 76. MPC8572E Pinout Listing (continued) |                                                                                              |                                                                     |          |                  |         |  |  |  |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------|------------------|---------|--|--|--|--|

| Signal                                        | Signal Name                                                                                  | Package Pin Number                                                  | Pin Type | Power<br>Supply  | Notes   |  |  |  |  |

| LGPL0/LFCLE                                   | UPM General Purpose Line 0 /<br>Flash Command Latch Enable                                   | J13                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |  |

| LGPL1/LFALE                                   | UPM General Purpose Line 1/<br>Flash Address Latch Enable                                    | J16                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |  |

| LGPL2/LOE/LFRE                                | UPM General Purpose Line 2 /<br>Output Enable / Flash Read<br>Enable                         | A27                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |  |  |  |  |

| LGPL3/LFWP                                    | UPM General Purpose Line 3 /<br>Flash Write Protect                                          | K16                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |  |

| LGPL4/LGTA/LUPWAIT/LPBSE<br>/LFRB             | UPM General Purpose Line 4 /<br>Target Ack / Wait / Parity Byte<br>Select / Flash Ready-Busy | L17                                                                 | I/O      | BV <sub>DD</sub> |         |  |  |  |  |

| LGPL5                                         | UPM General Purpose Line 5 /<br>Amux                                                         | B26                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |  |  |  |  |

| LCLK[0:2]                                     | Local Bus Clock                                                                              | F17, F16, A23                                                       | 0        | BV <sub>DD</sub> | _       |  |  |  |  |

| LSYNC_IN                                      | Local Bus DLL Synchronization                                                                | B22                                                                 | Ι        | BV <sub>DD</sub> | —       |  |  |  |  |

| LSYNC_OUT                                     | Local Bus DLL Synchronization                                                                | A21                                                                 | 0        | BV <sub>DD</sub> | —       |  |  |  |  |

|                                               | DMA                                                                                          |                                                                     |          |                  |         |  |  |  |  |

| DMA1_DACK[0:1]                                | DMA Acknowledge                                                                              | W25, U30                                                            | 0        | OV <sub>DD</sub> | 21      |  |  |  |  |

| DMA2_DACK[0]                                  | DMA Acknowledge                                                                              | AA26                                                                | 0        | OV <sub>DD</sub> | 5, 9    |  |  |  |  |

| DMA1_DREQ[0:1]                                | DMA Request                                                                                  | Y29, V27                                                            | Ι        | OV <sub>DD</sub> | —       |  |  |  |  |

| DMA2_DREQ[0]                                  | DMA Request                                                                                  | V29                                                                 | Ι        | OV <sub>DD</sub> | —       |  |  |  |  |

| DMA1_DDONE[0:1]                               | DMA Done                                                                                     | Y28, V30                                                            | 0        | OV <sub>DD</sub> | 5, 9    |  |  |  |  |

| DMA2_DDONE[0]                                 | DMA Done                                                                                     | AA28                                                                | 0        | OV <sub>DD</sub> | 5, 9    |  |  |  |  |

| DMA2_DREQ[2]                                  | DMA Request                                                                                  | M23                                                                 | Ι        | BV <sub>DD</sub> | —       |  |  |  |  |

|                                               | Programmable Inter                                                                           | rupt Controller                                                     |          |                  |         |  |  |  |  |

| UDE0                                          | Unconditional Debug Event<br>Processor 0                                                     | AC25                                                                | Ι        | OV <sub>DD</sub> | _       |  |  |  |  |

| UDE1                                          | Unconditional Debug Event<br>Processor 1                                                     | AA25                                                                | Ι        | OV <sub>DD</sub> | —       |  |  |  |  |

| MCP0                                          | Machine Check Processor 0                                                                    | M28                                                                 | Ι        | OV <sub>DD</sub> | _       |  |  |  |  |

| MCP1                                          | Machine Check Processor 1                                                                    | L28                                                                 | I        | OV <sub>DD</sub> | _       |  |  |  |  |

| IRQ[0:11]                                     | External Interrupts                                                                          | T24, R24, R25, R27,<br>R28, AB27, AB28, P27,<br>R30, AC28, R29, T31 | Ι        | OV <sub>DD</sub> | _       |  |  |  |  |

### Table 76. MPC8572E Pinout Listing (continued)

| Table 76. MPC8572E Pinout Listing (continued) |

|-----------------------------------------------|

|-----------------------------------------------|

| Signal                             | Signal Name                                                                      | Package Pin Number                        | Pin Type | Power<br>Supply            | Notes |  |

|------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------|----------|----------------------------|-------|--|

| SD1_RX[7:0]                        | Receive Data (positive)                                                          | P32, N30, M32, L30,<br>G30, F32, E30, D32 | I        | XV <sub>DD_SR</sub><br>DS1 | —     |  |

| SD1_RX[7:0]                        | Receive Data (negative)                                                          | P31, N29, M31, L29,<br>G29, F31, E29, D31 | I        | XV <sub>DD_SR</sub><br>DS1 | _     |  |

| SD1_TX[7]                          | PCIe1 Tx Data Lane 7 / SRIO or<br>PCIe2 Tx Data Lane 3 / PCIe3<br>TX Data Lane 1 | M26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 |       |  |

| SD1_TX[6]                          | PCIe1 Tx Data Lane 6 / SRIO or<br>PCIe2 Tx Data Lane 2 / PCIe3<br>TX Data Lane 0 | L24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |  |

| SD1_TX[5]                          | PCIe1 Tx Data Lane 5 / SRIO or<br>PCIe2 Tx Data Lane 1                           | K26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |  |

| SD1_TX[4]                          | D1_TX[4] PCle1 Tx Data Lane 4 / SRIO or J24<br>PCle2 Tx Data Lane 0              |                                           | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |  |

| SD1_TX[3]                          | D1_TX[3] PCIe1 Tx Data Lane 3                                                    |                                           | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |  |

| SD1_TX[2]                          | TX[2] PCIe1 Tx Data Lane 2                                                       |                                           | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |  |

| SD1_TX[1]                          | TX[1] PCIe1 Tx Data Lane 1]                                                      |                                           | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |  |

| SD1_TX[0]                          | D1_TX[0] PCIe1 Tx Data Lane 0 D                                                  |                                           | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |  |

| SD1_TX[7:0]                        | D1_TX[7:0] Transmit Data (negative) M27, L<br>G25, F                             |                                           | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |  |

| SD1_PLL_TPD PLL Test Point Digital |                                                                                  | J32                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | 17    |  |

| SD1_REF_CLK PLL Reference Clock    |                                                                                  | H32                                       | I        | XV <sub>DD_SR</sub><br>DS1 | _     |  |

| SD1_REF_CLK                        | D1_REF_CLK PLL Reference Clock<br>Complement                                     |                                           | I        | XV <sub>DD_SR</sub><br>DS1 | _     |  |

| Reserved                           | -                                                                                | С29, К32                                  |          | —                          | 26    |  |

| Reserved                           | -                                                                                | С30, К31                                  |          | —                          | 27    |  |

| Reserved                           | -                                                                                | C24, C25, H26, H27                        | _        | —                          | 28    |  |

| Reserved                           | _                                                                                | AL20, AL21                                |          |                            | 29    |  |

|                                    | SerDes (x4)                                                                      | SGMII                                     |          |                            |       |  |

| SD2_RX[3:0]                        | Receive Data (positive)                                                          | AK32, AJ30, AF30,<br>AE32                 | I        | XV <sub>DD_SR</sub><br>DS2 | _     |  |

Package Description

| -                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                                 | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Power<br>Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SGMII Tx Data eTSEC4                        | AH26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SGMII Tx Data eTSEC3                        | AG24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SGMII Tx Data eTSEC2                        | AE24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SGMII Tx Data eTSEC1                        | AD26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Transmit Data (negative)                    | AH27, AG25, AE25,<br>AD27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PLL Test Point Digital                      | AH32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |