Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                         |

| Speed                           | 1.067GHz                                                               |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                  |

| RAM Controllers                 | DDR2, DDR3                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                 |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                  |

| Package / Case                  | 1023-BFBGA, FCBGA                                                      |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/ppc8572epxarlc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Electrical Characteristics**

## 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths.

**Table 3. Output Drive Capability**

| Driver Type                           | Programmable Output Impedance $(\Omega)$ | Supply<br>Voltage                                                                   | Notes |

|---------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>35                                 | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V                                | 1     |

|                                       | 45(default)<br>45(default)<br>125        | $BV_{DD} = 3.3 \text{ V}$<br>$BV_{DD} = 2.5 \text{ V}$<br>$BV_{DD} = 1.8 \text{ V}$ |       |

| DDR2 signal                           | 18<br>36 (half strength mode)            | GV <sub>DD</sub> = 1.8 V                                                            | 2     |

| DDR3 signal                           | 20<br>40 (half strength mode)            | GV <sub>DD</sub> = 1.5 V                                                            | 2     |

| eTSEC/10/100 signals                  | 45                                       | L/TV <sub>DD</sub> = 2.5/3.3 V                                                      | _     |

| DUART, system control, JTAG           | 45                                       | OV <sub>DD</sub> = 3.3 V                                                            | _     |

| I2C                                   | 150                                      | OV <sub>DD</sub> = 3.3 V                                                            | _     |

#### Notes:

## 2.2 Power Sequencing

The MPC8572E requires its power rails to be applied in a specific sequence to ensure proper device operation. These requirements are as follows for power up:

- 1.  $V_{DD}$ ,  $AV_{DD\_n}$ ,  $BV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ ,  $SV_{DD\_SRDS1}$  and  $SV_{DD\_SRDS2}$ ,  $TV_{DD}$ ,  $XV_{DD\_SRDS1}$  and  $XV_{DD\_SRDS2}$

- $2. \text{ GV}_{DD}$

All supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

To guarantee MCKE low during power-on reset, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-on reset, then the sequencing for  $GV_{DD}$  is not required.

<sup>1.</sup> The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

<sup>2.</sup> The drive strength of the DDR2 or DDR3 interface in half-strength mode is at  $T_i = 105$ °C and at  $GV_{DD}$  (min).

Table 14 provides the current draw characteristics for MV<sub>REF</sub>n.

Table 14. Current Draw Characteristics for MV<sub>REF</sub> n

| Parameter / Condition                |            | Symbol               | Min | Max  | Unit | Note |

|--------------------------------------|------------|----------------------|-----|------|------|------|

| Current draw for MV <sub>REF</sub> n | DDR2 SDRAM | I <sub>MVREF</sub> n | _   | 1500 | μΑ   | 1    |

|                                      | DDR3 SDRAM |                      |     | 1250 |      |      |

<sup>1.</sup> The voltage regulator for MV<sub>RFF</sub>n must be able to supply up to 1500 μA or 1250 uA current for DDR2 or DDR3, respectively.

## 6.2 DDR2 and DDR3 SDRAM Interface AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM controller interface. The DDR controller supports both DDR2 and DDR3 memories. Note that although the minimum data rate for most off-the-shelf DDR3 DIMMs available is 800 MHz, JEDEC specification does allow the DDR3 to run at the data rate as low as 606 MHz. Unless otherwise specified, the AC timing specifications described in this section for DDR3 is applicable for data rate between 606 MHz and 800 MHz, as long as the DC and AC specifications of the DDR3 memory to be used are compliant to both JEDEC specifications as well as the specifications and requirements described in this MPC8572E hardware specifications document.

## 6.2.1 DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

Table 15, Table 16, and Table 17 provide the input AC timing specifications for the DDR controller when interfacing to DDR2 and DDR3 SDRAM.

Table 15. DDR2 SDRAM Interface Input AC Timing Specifications for 1.8-V Interface At recommended operating conditions with  $GV_{DD}$  of 1.8 V  $\pm$  5%

| Paramet               | er         | Symbol Min        |                    | Max                      | Unit | Notes |

|-----------------------|------------|-------------------|--------------------|--------------------------|------|-------|

| AC input low voltage  | >=667 MHz  | V <sub>ILAC</sub> | _                  | MV <sub>REF</sub> n-0.20 | V    | _     |

|                       | <= 533 MHz |                   | _                  | MV <sub>REF</sub> n-0.25 |      |       |

| AC input high voltage | >=667 MHz  | V <sub>IHAC</sub> | $MV_{REF}n + 0.20$ | _                        | V    | _     |

| _                     | <= 533 MHz |                   | $MV_{REF}n + 0.25$ |                          |      |       |

#### Table 16. DDR3 SDRAM Interface Input AC Timing Specifications for 1.5-V Interface

At recommended operating conditions with  $GV_{DD}$  of 1.5 V  $\pm$  5%. DDR3 data rate is between 606 MHz and 800 MHz.

| Parameter             | Symbol            | Min                         | Max                 | Unit | Notes |

|-----------------------|-------------------|-----------------------------|---------------------|------|-------|

| AC input low voltage  | $V_{ILAC}$        | _                           | $MV_{REF}n - 0.175$ | V    | _     |

| AC input high voltage | V <sub>IHAC</sub> | MV <sub>REF</sub> n + 0.175 |                     | V    |       |

#### **DDR2 and DDR3 SDRAM Controller**

#### Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications (continued)

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter           | Symbol <sup>1</sup> | Min                             | Max                               | Unit | Notes |

|---------------------|---------------------|---------------------------------|-----------------------------------|------|-------|

| 533 MHz             |                     | 538                             | _                                 |      |       |

| 400 MHz             |                     | 700                             | _                                 |      |       |

| MDQS preamble start | t <sub>DDKHMP</sub> |                                 |                                   | ns   | 6     |

| 800 MHz             |                     | -0.5 × t <sub>MCK</sub> - 0.375 | −0.5 × t <sub>MCK</sub><br>+0.375 |      |       |

| <= 667 MHz          |                     | $-0.5 \times t_{MCK} - 0.6$     | $-0.5 \times t_{MCK} + 0.6$       |      |       |

| MDQS epilogue end   | t <sub>DDKHME</sub> |                                 |                                   | ns   | 6     |

| 800 MHz             | 1                   | -0.375                          | 0.375                             |      |       |

| <= 667 MHz          | t <sub>DDKHME</sub> | -0.6                            | 0.6                               | ns   | 6     |

#### Note:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the MDQS override bits (called WR\_DATA\_DELAY) in the TIMING\_CFG\_2 register. This typically be set to the same delay as in DDR\_SDRAM\_CLK\_CNTL[CLK\_ADJUST]. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8572E PowerQUICC<sup>TM</sup> III Integrated Host Processor Family Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

- Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

#### **NOTE**

For the ADDR/CMD setup and hold specifications in Table 18, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

The Fast Ethernet Controller (FEC) operates in MII mode only, and complies with the AC and DC electrical characteristics specified in this chapter for MII. Note that if FEC is used, eTSEC 3 and 4 are only available in SGMII mode.

### 8.1.1 eTSEC DC Electrical Characteristics

All MII, GMII, RMII, and TBI drivers and receivers comply with the DC parametric attributes specified in Table 23 and Table 24. All RGMII, RTBI and FIFO drivers and receivers comply with the DC parametric attributes specified in Table 24. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

**Parameter** Symbol Unit Min Max **Notes** 1, 2 Supply voltage 3.3 V 3.47 V  $LV_{DD}$ 3.13  $TV_{DD}$ Output high voltage VOH  $LV_{DD}/TV_{DD} + 0.3$ ٧ 2.40  $(LV_{DD}/TV_{DD} = Min, IOH = -4.0 mA)$ Output low voltage VOL **GND** 0.50 ٧  $(LV_{DD}/TV_{DD} = Min, IOL = 4.0 mA)$ Input high voltage  $LV_{DD}/TV_{DD} + 0.3$ 2.0  $V_{IH}$ Input low voltage  $V_{IL}$ -0.3 0.90 ٧ Input high current 40 1, 2,3 μΑ  $I_{IH}$  $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$ 3 Input low current  $I_{IL}$ -600μΑ  $(V_{IN} = GND)$

Table 23. GMII, MII, RMII, and TBI DC Electrical Characteristics

#### Notes:

Table 24. MII, GMII, RMII, RGMII, TBI, RTBI, and FIFO DC Electrical Characteristics

| Parameters                                                                                 | Symbol                             | Min       | Max                     | Unit | Notes |

|--------------------------------------------------------------------------------------------|------------------------------------|-----------|-------------------------|------|-------|

| Supply voltage 2.5 V                                                                       | LV <sub>DD/</sub> TV <sub>DD</sub> | 2.37      | 2.63                    | V    | 1,2   |

| Output high voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, IOH = -1.0 mA)           | V <sub>OH</sub>                    | 2.00      | $LV_{DD}/TV_{DD} + 0.3$ | V    | _     |

| Output low voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>                    | GND - 0.3 | 0.40                    | V    | _     |

| Input high voltage                                                                         | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$ | V    | _     |

| Input low voltage                                                                          | V <sub>IL</sub>                    | -0.3      | 0.70                    | V    | _     |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

<sup>&</sup>lt;sup>1</sup> LV<sub>DD</sub> supports eTSECs 1 and 2.

<sup>&</sup>lt;sup>2</sup> TV<sub>DD</sub> supports eTSECs 3 and 4 or FEC.

$<sup>^3</sup>$  The symbol  $V_{IN}$ , in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1.

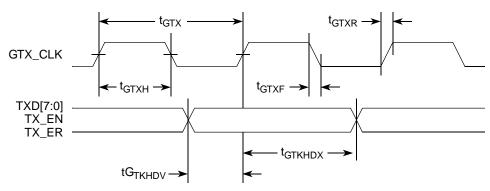

Figure 9 shows the GMII transmit AC timing diagram.

Figure 9. GMII Transmit AC Timing Diagram

## 8.2.2.2 GMII Receive AC Timing Specifications

Table 28 provides the GMII receive AC timing specifications.

#### Table 28. GMII Receive AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | _   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | _   | 60  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | _   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0   | _   | _   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>GRXR</sub> <sup>2</sup>      | _   | _   | 1.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>GRXF</sub> <sup>2</sup>      | _   | _   | 1.0 | ns   |

#### Note:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)</sub>(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

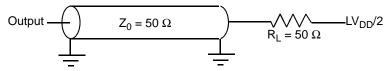

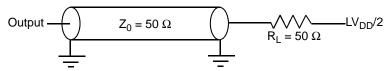

Figure 10 provides the AC test load for eTSEC.

Figure 10. eTSEC AC Test Load

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

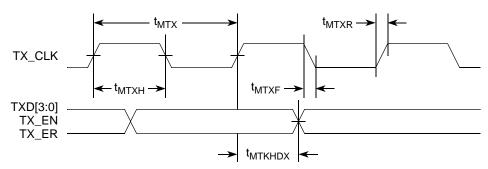

Figure 12 shows the MII transmit AC timing diagram.

Figure 12. MII Transmit AC Timing Diagram

## 8.2.3.2 MII Receive AC Timing Specifications

Table 30 provides the MII receive AC timing specifications.

#### Table 30. MII Receive AC Timing Specifications

At recommended operating conditions with LV  $_{DD}$ /TV  $_{DD}$  of 2.5/3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> <sup>2</sup>       | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    | _    | 40  | _   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | _   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>MRXR</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

#### Notes:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

Figure 13 provides the AC test load for eTSEC.

Figure 13. eTSEC AC Test Load

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

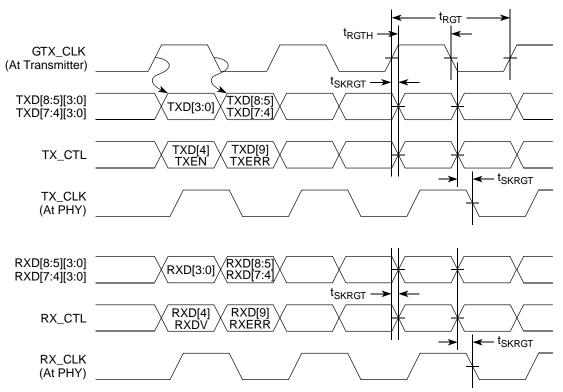

Figure 18 shows the RGMII and RTBI AC timing and multiplexing diagrams.

Figure 18. RGMII and RTBI AC Timing and Multiplexing Diagrams

## 8.2.7 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

## 8.2.7.1 RMII Transmit AC Timing Specifications

Table 35 shows the RMII transmit AC timing specifications.

## **Table 35. RMII Transmit AC Timing Specifications**

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition              | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit |

|----------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period        | t <sub>RMT</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_TX_CLK duty cycle          | t <sub>RMTH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter | t <sub>RMTJ</sub>   | _    | _    | 250  | ps   |

| Rise time TSECn_TX_CLK (20%–80%) | t <sub>RMTR</sub>   | 1.0  | _    | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%–20%) | t <sub>RMTF</sub>   | 1.0  | _    | 2.0  | ns   |

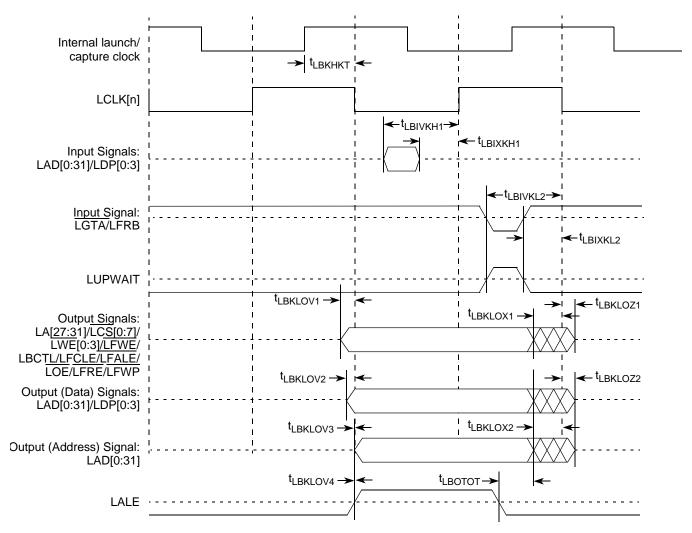

#### Local Bus Controller (eLBC)

Figure 31. Local Bus Signals (PLL Bypass Mode)

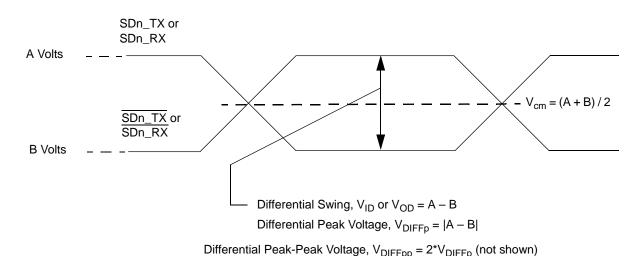

#### 6. Differential Waveform

1. The differential waveform is constructed by subtracting the inverting signal (SD*n*\_TX, for example) from the non-inverting signal (SDn\_TX, for example) within a differential pair. There is only one signal trace curve in a differential waveform. The voltage represented in the differential waveform is not referenced to ground. Refer to Figure 52 as an example for differential waveform.

## 2. Common Mode Voltage, V<sub>cm</sub>

The Common Mode Voltage is equal to one half of the sum of the voltages between each conductor of a balanced interchange circuit and ground. In this example, for SerDes output,  $V_{cm\_out} = (V_{SDn\_TX} + V_{\overline{SDn}\_TX})/2 = (A+B)/2$ , which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. Sometimes, it may be even different between the receiver input and driver output circuits within the same component. It is also referred as the DC offset in some occasion.

Figure 43. Differential Voltage Definitions for Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (Current Mode Logic) transmitter that has a common mode voltage of 2.25 V and each of its outputs, TD and  $\overline{\text{TD}}$ , has a swing that goes between 2.5 V and 2.0 V. Using these values, the peak-to-peak voltage swing of each signal (TD or  $\overline{\text{TD}}$ ) is 500 mV p-p, which is referred as the single-ended swing for each signal. In this example, because the differential signaling environment is fully symmetrical, the transmitter output's differential swing (V<sub>OD</sub>) has the same amplitude as each signal's single-ended swing. The differential output signal ranges between 500 mV and –500 mV, in other words, V<sub>OD</sub> is 500 mV in one phase and –500 mV in the other phase. The peak differential voltage (V<sub>DIFFp</sub>) is 500 mV. The peak-to-peak differential voltage (V<sub>DIFFp</sub>) is 1000 mV p-p.

## 15.2 SerDes Reference Clocks

The SerDes reference clock inputs are applied to an internal PLL whose output creates the clock used by the corresponding SerDes lanes. The SerDes reference clocks inputs are SD1\_REF\_CLK and

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

#### **High-Speed Serial Interfaces (HSSI)**

clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

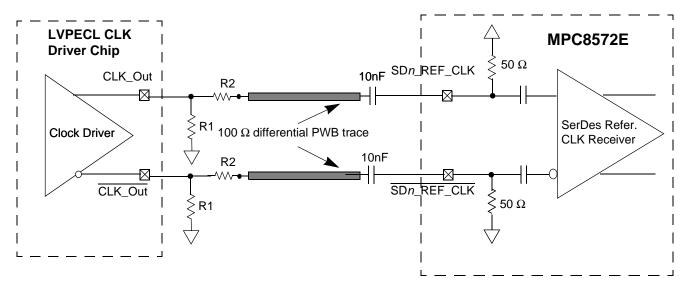

Figure 50. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

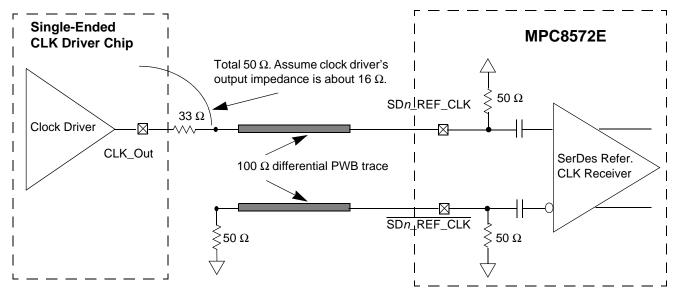

Figure 51 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with MPC8572E SerDes reference clock input's DC requirement.

Figure 51. Single-Ended Connection (Reference Only)

## 15.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100KHz can be tracked by the PLL and data recovery loops and

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

83

• Section 17, "Serial RapidIO"

Note that external AC Coupling capacitor is required for the above three serial transmission protocols with the capacitor value defined in specification of each protocol section.

# 16 PCI Express

This section describes the DC and AC electrical specifications for the PCI Express bus of the MPC8572E.

# 16.1 <u>DC Requirements for PCI Express SD1\_REF\_CLK and SD1\_REF\_CLK</u>

For more information, see Section 15.2, "SerDes Reference Clocks."

## 16.2 AC Requirements for PCI Express SerDes Reference Clocks

Table 61 lists AC requirements.

Table 61. SD1\_REF\_CLK and SD1\_REF\_CLK AC Requirements

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | 1   | 10      |     | ns    | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | _       | 100 | ps    | _     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _       | 50  | ps    | _     |

#### Notes:

## 16.3 Clocking Dependencies

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million (ppm) of each other at all times. This is specified to allow bit rate clock sources with a  $\pm -300$  ppm tolerance.

## 16.4 Physical Layer Specifications

The following is a summary of the specifications for the physical layer of PCI Express on this device. For further details as well as the specifications of the transport and data link layer, Use the PCI Express Base Specification. REV. 1.0a document.

## **16.4.1** Differential Transmitter (TX) Output

Table 62 defines the specifications for the differential output at all transmitters (TXs). The parameters are specified at the component pins.

<sup>1.</sup> Typical cycle time is based on PCI Express Card Electromechanical Specification Revision 1.0a.

## Table 62. Differential Transmitter (TX) Output Specifications (continued)

| Symbol                            | Parameter                                                                                                         | Min | Nominal | Max           | Units | Comments                                                                                                                                                                                                                                 |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|---------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TX-DC-CM</sub>             | The TX DC<br>Common Mode<br>Voltage                                                                               | 0   | _       | 3.6           | V     | The allowed DC Common Mode voltage under any conditions. See Note 6.                                                                                                                                                                     |

| I <sub>TX-SHORT</sub>             | TX Short Circuit<br>Current Limit                                                                                 |     | _       | 90            | mA    | The total current the Transmitter can provide when shorted to its ground                                                                                                                                                                 |

| T <sub>TX-IDLE-MIN</sub>          | Minimum time<br>spent in<br>Electrical Idle                                                                       | 50  | _       |               | UI    | Minimum time a Transmitter must be in Electrical Idle Utilized by the Receiver to start looking for an Electrical Idle Exit after successfully receiving an Electrical Idle ordered set                                                  |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Maximum time to<br>transition to a<br>valid Electrical<br>idle after sending<br>an Electrical Idle<br>ordered set | l   | _       | 20            | UI    | After sending an Electrical Idle ordered set, the Transmitter must meet all Electrical Idle Specifications within this time. This is considered a debounce time for the Transmitter to meet Electrical Idle after transitioning from L0. |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Maximum time to<br>transition to valid<br>TX specifications<br>after leaving an<br>Electrical idle<br>condition   |     | _       | 20            | UI    | Maximum time to meet all TX specifications when transitioning from Electrical Idle to sending differential data. This is considered a debounce time for the TX to meet all TX specifications after leaving Electrical Idle               |

| RL <sub>TX-DIFF</sub>             | Differential<br>Return Loss                                                                                       | 12  | _       | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                             |

| RL <sub>TX-CM</sub>               | Common Mode<br>Return Loss                                                                                        | 6   | _       | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                             |

| Z <sub>TX-DIFF-DC</sub>           | DC Differential TX Impedance                                                                                      | 80  | 100     | 120           | Ω     | TX DC Differential mode Low Impedance                                                                                                                                                                                                    |

| Z <sub>TX-DC</sub>                | Transmitter DC Impedance                                                                                          | 40  | _       | _             | Ω     | Required TX D+ as well as D- DC Impedance during all states                                                                                                                                                                              |

| L <sub>TX-SKEW</sub>              | Lane-to-Lane<br>Output Skew                                                                                       | _   | _       | 500 +<br>2 UI | ps    | Static skew between any two Transmitter Lanes within a single Link                                                                                                                                                                       |

| C <sub>TX</sub>                   | AC Coupling<br>Capacitor                                                                                          | 75  | _       | 200           | nF    | All Transmitters shall be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See Note 8.                                                                                       |

### **PCI Express**

Table 63. Differential Receiver (RX) Input Specifications (continued)

| Symbol                                      | Parameter                                                                                    | Min   | Nominal | Max | Units | Comments                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------|----------------------------------------------------------------------------------------------|-------|---------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>RX-EYE-MEDIAN-to-MAX</sub> -JITTER   | Maximum time<br>between the jitter<br>median and<br>maximum<br>deviation from<br>the median. |       | _       | 0.3 | UI    | Jitter is defined as the measurement variation of the crossing points (V <sub>RX-DIFFp-p</sub> = 0 V) in relation to a recovered TX UI. A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI. See Notes 2, 3 and 7. |

| V <sub>RX-CM-ACp</sub>                      | AC Peak<br>Common Mode<br>Input Voltage                                                      |       | _       | 150 | mV    | $ \begin{vmatrix} V_{\text{RX-CM-ACp}} =  V_{\text{RXD+}} + V_{\text{RXD-}} /2 - V_{\text{RX-CM-DC}} \\ V_{\text{RX-CM-DC}} = DC_{(avg)} \text{ of }  V_{\text{RX-D+}} + V_{\text{RX-D-}} /2 \\ \text{See Note 2} \end{vmatrix} $                                                                                                                                            |

| RL <sub>RX-DIFF</sub>                       | Differential<br>Return Loss                                                                  | 15    | _       | _   | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D- lines biased at +300 mV and -300 mV, respectively. See Note 4                                                                                                                                                                                                                                                            |

| RL <sub>RX-CM</sub>                         | Common Mode<br>Return Loss                                                                   | 6     | _       | _   | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D- lines biased at 0 V. See Note 4                                                                                                                                                                                                                                                                                          |

| Z <sub>RX-DIFF-DC</sub>                     | DC Differential Input Impedance                                                              | 80    | 100     | 120 | Ω     | RX DC Differential mode impedance. See Note 5                                                                                                                                                                                                                                                                                                                                |

| Z <sub>RX-DC</sub>                          | DC Input<br>Impedance                                                                        | 40    | 50      | 60  | Ω     | Required RX D+ as well as D- DC Impedance (50 ± 20% tolerance). See Notes 2 and 5.                                                                                                                                                                                                                                                                                           |

| Z <sub>RX-HIGH-IMP-DC</sub>                 | Powered Down<br>DC Input<br>Impedance                                                        | 200 k | _       | _   | Ω     | Required RX D+ as well as D- DC Impedance when the Receiver terminations do not have power. See Note 6.                                                                                                                                                                                                                                                                      |

| V <sub>RX-IDLE-DET-DIFFp-p</sub>            | Electrical Idle<br>Detect Threshold                                                          | 65    | _       | 175 | mV    | V <sub>RX-IDLE-DET-DIFFp-p</sub> = 2* V <sub>RX-D+</sub> -V <sub>RX-D-</sub>   Measured at the package pins of the Receiver                                                                                                                                                                                                                                                  |

| T <sub>RX-IDLE-DET-DIFF-</sub><br>ENTERTIME | Unexpected<br>Electrical Idle<br>Enter Detect<br>Threshold<br>Integration Time               | _     | _       | 10  | ms    | An unexpected Electrical Idle (V <sub>RX-DIFFp-p</sub> < V <sub>RX-IDLE-DET-DIFFp-p</sub> ) must be recognized no longer than T <sub>RX-IDLE-DET-DIFF-ENTERING</sub> to signal an unexpected idle condition.                                                                                                                                                                 |

Serial RapidIO

# 17.1 <u>DC Requirements</u> for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK

For more information, see Section 15.2, "SerDes Reference Clocks."

# 17.2 <u>AC Requirements for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK</u>

Figure 64lists the AC requirements.

Table 64. SDn REF CLK and SDn REF CLK AC Requirements

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Comments                                                         |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|------------------------------------------------------------------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | _   | 10(8)   | _   | ns    | 8 ns applies only to serial RapidIO with 125-MHz reference clock |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | _       | 80  | ps    | _                                                                |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -40 | _       | 40  | ps    | _                                                                |

## 17.3 Equalization

With the use of high speed serial links, the interconnect media causes degradation of the signal at the receiver. Effects such as Inter-Symbol Interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are as follows:

- A passive high pass filter network placed at the receiver. This is often referred to as passive equalization.

- The use of active circuits in the receiver. This is often referred to as adaptive equalization.

## 17.4 Explanatory Note on Transmitter and Receiver Specifications

AC electrical specifications are given for transmitter and receiver. Long run and short run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to serial RapidIO, as described in Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." The goal of this standard is that electrical designs for Serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

### **Package Description**

## Table 76. MPC8572E Pinout Listing (continued)

| Signal               | Signal Name                  | Package Pin Number                                                                                                                                                                  | Pin Type | Power<br>Supply  | Notes   |

|----------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| D2_MBA[0:2]          | Bank Select                  | Y1, W3, P3                                                                                                                                                                          | 0        | GV <sub>DD</sub> | _       |

| D2_MWE               | Write Enable                 | AA2                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MCAS              | Column Address Strobe        | AD1                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MRAS              | Row Address Strobe           | AA1                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| D2_MCKE[0:3]         | Clock Enable                 | L3, L1, K1, K2                                                                                                                                                                      | 0        | GV <sub>DD</sub> | 11      |

| D2_MCS[0:3]          | Chip Select                  | AB1, AG2, AC1, AH2                                                                                                                                                                  | 0        | GV <sub>DD</sub> | _       |

| D2_MCK[0:5]          | Clock                        | V4, F7, AJ3, V2, E7,<br>AG4                                                                                                                                                         | 0        | GV <sub>DD</sub> | _       |

| D2_MCK[0:5]          | Clock Complements            | V1, F8, AJ4, U1, E6,<br>AG5                                                                                                                                                         | 0        | GV <sub>DD</sub> | _       |

| D2_MODT[0:3]         | On Die Termination           | AE1, AG1, AE2, AH1                                                                                                                                                                  | 0        | GV <sub>DD</sub> | _       |

| D2_MDIC[0:1]         | Driver Impedance Calibration | F1, G1                                                                                                                                                                              | I/O      | GV <sub>DD</sub> | 25      |

|                      | Local Bus Contro             | oller Interface                                                                                                                                                                     |          |                  |         |

| LAD[0:31]            | Muxed Data/Address           | M22, L22, F22, G22,<br>F21, G21, E20, H22,<br>K22, K21, H19, J20,<br>J19, L20, M20, M19,<br>E22, E21, L19, K19,<br>G19, H18, E18, G18,<br>J17, K17, K14, J15,<br>H16, J14, H15, G15 | I/O      | BV <sub>DD</sub> | 34      |

| LDP[0:3]             | Data Parity                  | M21, D22, A24, E17                                                                                                                                                                  | I/O      | BV <sub>DD</sub> | _       |

| LA[27]               | Burst Address                | J21                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LA[28:31]            | Port Address                 | F20, K18, H20, G17                                                                                                                                                                  | 0        | BV <sub>DD</sub> | 5, 7, 9 |

| LCS[0:4]             | Chip Selects                 | B23, E16, D20, B25,<br>A22                                                                                                                                                          | 0        | BV <sub>DD</sub> | 10      |

| LCS[5]/DMA2_DREQ[1]  | Chip Selects / DMA Request   | D19                                                                                                                                                                                 | I/O      | BV <sub>DD</sub> | 1, 10   |

| LCS[6]/DMA2_DACK[1]  | Chip Selects / DMA Ack       | E19                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 1, 10   |

| LCS[7]/DMA2_DDONE[1] | Chip Selects / DMA Done      | C21                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 1, 10   |

| LWE[0]/LBS[0]/LFWE   | Write Enable / Byte Select   | D17                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[1]/LBS[1]        | Write Enable / Byte Select   | F15                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| TWE[2]/LBS[2]        | Write Enable / Byte Select   | B24                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE[3]/LBS[3]        | Write Enable / Byte Select   | D18                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 9    |

| LALE                 | Address Latch Enable         | F19                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                | Buffer Control               | L18                                                                                                                                                                                 | 0        | BV <sub>DD</sub> | 5, 8, 9 |

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

Clocking

## 19 Clocking

This section describes the PLL configuration of the MPC8572E. Note that the platform clock is identical to the core complex bus (CCB) clock.

## 19.1 Clock Ranges

Table 77 provides the clocking specifications for both processor cores.

Table 77. MPC8572E Processor Core Clocking Specifications

|                               | Maximum Processor Core Frequency |      |          |      |          |      |          |      |      |       |

|-------------------------------|----------------------------------|------|----------|------|----------|------|----------|------|------|-------|

| Characteristic                | 1067 MHz                         |      | 1200 MHz |      | 1333 MHz |      | 1500 MHz |      | Unit | Notes |

|                               | Min                              | Max  | Min      | Max  | Min      | Max  | Min      | Max  |      |       |

| e500 core processor frequency | 800                              | 1067 | 800      | 1200 | 800      | 1333 | 800      | 1500 | MHz  | 1, 2  |

| CCB frequency                 | 400                              | 533  | 400      | 533  | 400      | 533  | 400      | 600  | MHz  |       |

| DDR Data Rate                 | 400                              | 667  | 400      | 667  | 400      | 667  | 400      | 800  | MHz  |       |

#### Notes:

- Caution: The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," Section 19.3, "e500 Core PLL Ratio," and Section 19.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

- The processor core frequency speed bins listed also reflect the maximum platform (CCB) and DDR data rate frequency supported by production test. Running CCB and/or DDR data rate higher than the limit shown above, although logically possible via valid clock ratio setting in some condition, is not supported.

The DDR memory controller can run in either synchronous or asynchronous mode. When running in synchronous mode, the memory bus is clocked relative to the platform clock frequency. When running in asynchronous mode, the memory bus is clocked with its own dedicated PLL with clock provided on DDRCLK input pin. Table 78 provides the clocking specifications for the memory bus.

Clocking

**Table 79. CCB Clock Ratio**

| Binary Value of<br>LA[29:31] Signals | CCB:SYSCLK Ratio |

|--------------------------------------|------------------|

| 000                                  | 4:1              |

| 001                                  | 5:1              |

| 010                                  | 6:1              |

| 011                                  | 8:1              |

| 100                                  | 10:1             |

| 101                                  | 12:1             |

| 110                                  | Reserved         |

| 111                                  | Reserved         |

## 19.3 e500 Core PLL Ratio

The clock speed for each e500 core can be configured differently, determined by the values of various signals at power up.

Table 80 describes the clock ratio between e500 Core0 and the e500 core complex bus (CCB). This ratio is determined by the binary value of LBCTL, LALE and LGPL2/LOE/LFRE at power up, as shown in Table 80.

Table 80. e500 Core0 to CCB Clock Ratio

| Binary Value of<br>LBCT <u>L, LALE,</u><br>LGPL2/LOE/LFRE<br>Signals | e500 Core0:CCB Clock Ratio | Binary Value of<br>LBCT <u>L, LALE,</u><br>LGPL2/LOE/LFRE<br>Signals | e500 Core0:CCB Clock Ratio |  |  |

|----------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------|----------------------------|--|--|

| 000                                                                  | Reserved                   | 100                                                                  | 2:1                        |  |  |

| 001                                                                  | Reserved                   | 101                                                                  | 5:2 (2.5:1)                |  |  |

| 010                                                                  | Reserved                   | 110                                                                  | 3:1                        |  |  |

| 011                                                                  | 3:2 (1.5:1)                | 111                                                                  | 7:2 (3.5:1)                |  |  |

in the above equation refers to the negotiated link width as the result of PCI Express link training, which may or may not be the same as the link width POR selection.

For proper serial RapidIO operation, the CCB clock frequency must be greater than:

$$2 \times (0.80) \times (\text{serial RapidIO interface frequency}) \times (\text{serial RapidIO link width})$$

See Section 20.4, "1x/4x LP-Serial Signal Descriptions," in the MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual for Serial RapidIO interface width and frequency details.

## 20 Thermal

This section describes the thermal specifications of the MPC8572E.

Table 84 shows the thermal characteristics for the package,  $1023\ 33 \times 33\ FC$ -PBGA.

The package uses a  $29.6 \times 29.6$  mm lid that attaches to the substrate. Recommended maximum heat sink force is 10 pounds force (45 Newton).

| Rating                                  | Board             | Symbol           | Value | Unit | Notes |

|-----------------------------------------|-------------------|------------------|-------|------|-------|

| Junction to ambient, natural convection | Single-layer (1s) | $R_{\Theta JA}$  | 15    | °C/W | 1, 2  |

| Junction to ambient, natural convection | Four-layer (2s2p) | $R_{\Theta JA}$  | 11    | °C/W | 1, 3  |

| Junction to ambient (at 200 ft./min.)   | Single-layer (1s) | $R_{\Theta JMA}$ | 11    | °C/W | 1, 3  |

| Junction to ambient (ar 200 ft./min.)   | Four-layer (2s2p) | $R_{\Theta JMA}$ | 8     | °C/W | 1, 3  |

| Junction to board                       | _                 | $R_{\Theta JB}$  | 4     | °C/W | 4     |

| Junction to case                        | _                 | $R_{\Theta JC}$  | 0.5   | °C/W | 5     |

**Table 84. Package Thermal Characteristics**

#### Notes:

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance

- 2. Per JEDEC JESD51-2 with the single-layer board (JESD51-3) horizontal.

- 3. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883, Method 1012.1).

## 20.1 Temperature Diode

The MPC8572E has a temperature diode on the microprocessor that can be used in conjunction with other system temperature monitoring devices (such as Analog Devices, ADT7461<sup>TM</sup>). These devices use the negative temperature coefficient of a diode operated at a constant current to determine the temperature of the microprocessor and its environment. It is recommended that each MPC8572E device be calibrated.

The following are the specifications of the on-board temperature diode:

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

#### **System Design Information**

logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert TRST during the power-on reset flow. Simply tying TRST to HRESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 66 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

The COP interface has a standard header, shown in Figure 65, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; so emulator vendors have issued many different pin numbering schemes. Some COP headers are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom. Still others number the pins counter-clockwise from pin 1 (as with an IC). Regardless of the numbering scheme, the signal placement recommended in Figure 65 is common to all known emulators.

## 21.9.1 Termination of Unused Signals

If the JTAG interface and COP header is not used, Freescale recommends the following connections:

- TRST should be tied to HRESET through a 0 kΩ isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 66. If this is not possible, the isolation resistor allows future access to TRST in case a JTAG interface may need to be wired onto the system in future debug situations.

- No pull-up/pull-down is required for TDI, TMS, TDO or TCK.

#### Figure 66. JTAG Interface Connection

## 21.10 Guidelines for High-Speed Interface Termination

## 21.10.1 SerDes 1 Interface Entirely Unused

If the high-speed SerDes 1 interface is not used at all, the unused pin should be terminated as described in this section.

The following pins must be left unconnected (float):

- SD1\_TX[7:0]

- SD1 TX[7:0]

- Reserved pins C24, C25, H26, H27

The following pins must be connected to XGND\_SRDS1:

- SD1\_RX[7:0]

- SD1\_RX[7:0]

- SD1\_REF\_CLK

- SD1 REF CLK

Pins K32 and C29 must be tied to  $XV_{DD}$ \_SRDS1. Pins K31 and C30 must be tied to XGND\_SRDS1 through a 300- $\Omega$  resistor.

The POR configuration pin cfg\_srds1\_en on TSEC2\_TXD[5] can be used to power down SerDes 1 block for power saving. Note that both SVDD\_SRDS1 and XVDD\_SRDS1 must remain powered.

## 21.10.2 SerDes 1 Interface Partly Unused

If only part of the high speed SerDes 1 interface pins are used, the remaining high-speed serial I/O pins should be terminated as described in this section.

The following pins must be left unconnected (float) if not used:

- SD1\_TX[7:0]

- SD1\_TX[7:0]

- Reserved pins: C24, C25, H26, H27

The following pins must be connected to XGND\_SRDS1 if not used:

- SD1\_RX[7:0]

- SD1\_RX[7:0]

Pins K32 and C29 must be tied to XV<sub>DD</sub>\_SRDS1. Pins K31 and C30 must be tied to XGND\_SRDS1 through a 300- $\Omega$  resistor.

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

NXP Semiconductors

135