## E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                         |

| Speed                           | 1.067GHz                                                               |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                  |

| RAM Controllers                 | DDR2, DDR3                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                 |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                  |

| Package / Case                  | 1023-BFBGA, FCBGA                                                      |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/ppc8572evtarlc |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

- Ability to launch DMA from single write transaction

- Serial RapidIO interface unit

- Supports RapidIO Interconnect Specification, Revision 1.2

- Both 1x and 4x LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto-detection of 1x- and 4x-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO–compliant message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

- Single inbound doorbell message structure

- Facility to accept port-write messages

### 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

### 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| Table 1. Absolute Maximum Ratings | 1 |

|-----------------------------------|---|

|-----------------------------------|---|

|                                       | Characteristic                                                                         | Symbol                                                    | Range                                                                | Unit | Notes |

|---------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------|------|-------|

| Core supply voltag                    | e                                                                                      | V <sub>DD</sub>                                           | -0.3 to 1.21                                                         | V    |       |

| PLL supply voltage                    | 3                                                                                      | AV <sub>DD</sub>                                          | -0.3 to 1.21                                                         | V    | _     |

| Core power supply                     | ofor SerDes transceivers                                                               | SV <sub>DD</sub>                                          | -0.3 to 1.21                                                         | V    | _     |

| Pad power supply                      | for SerDes transceivers                                                                | XV <sub>DD</sub>                                          | -0.3 to 1.21                                                         | V    | _     |

| DDR SDRAM                             | DDR2 SDRAM Interface                                                                   | GV <sub>DD</sub>                                          | -0.3 to 1.98                                                         | V    | _     |

| Controller I/O<br>supply voltage      | DDR3 SDRAM Interface                                                                   | _                                                         | -0.3 to 1.65                                                         |      | —     |

| Three-speed Ether<br>management volta | rnet I/O, FEC management interface, MII<br>ge                                          | LV <sub>DD</sub> (for eTSEC1 and eTSEC2)                  | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | 2     |

|                                       |                                                                                        | TV <sub>DD</sub> (for eTSEC3 and eTSEC4, FEC)             | -0.3 to 3.63<br>-0.3 to 2.75                                         | —    | 2     |

| DUART, system co<br>I/O voltage       | ontrol and power management, I <sup>2</sup> C, and JTAG                                | OV <sub>DD</sub>                                          | -0.3 to 3.63                                                         | V    | —     |

| Local bus and GPI                     | O I/O voltage                                                                          | BV <sub>DD</sub>                                          | -0.3 to 3.63<br>-0.3 to 2.75<br>-0.3 to 1.98                         | V    | _     |

| Input voltage                         | DDR2 and DDR3 SDRAM interface signals                                                  | MV <sub>IN</sub>                                          | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 3     |

|                                       | DDR2 and DDR3 SDRAM interface reference                                                | MV <sub>REF</sub> $n$ -0.3 to (GV <sub>DD</sub> /2 + 0.3) |                                                                      | V    | —     |

| Three-speed Ethernet signals          |                                                                                        | LV <sub>IN</sub><br>TV <sub>IN</sub>                      | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 3     |

| Local bus and GPIO signals            |                                                                                        | BV <sub>IN</sub>                                          | –0.3 to (BV <sub>DD</sub> + 0.3)                                     | —    | —     |

|                                       | DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                                          | –0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 3     |

| Storage temperatu                     | re range                                                                               | T <sub>STG</sub>                                          | –55 to 150                                                           | °C   | —     |

Notes:

1. Functional operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

The 3.63V maximum is only supported when the port is configured in GMII, MII, RMII or TBI modes; otherwise the 2.75V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

3. (M,L,O)V<sub>IN</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

## NP

#### DDR2 and DDR3 SDRAM Controller

Table 18. DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications (continued)

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5% for DDR2 or 1.5 V ± 5% for DDR3.

| Parameter           | Symbol <sup>1</sup> | Min                             | Мах                                                                 | Unit | Notes |

|---------------------|---------------------|---------------------------------|---------------------------------------------------------------------|------|-------|

| 533 MHz             |                     | 538                             | —                                                                   |      |       |

| 400 MHz             |                     | 700                             | —                                                                   |      |       |

| MDQS preamble start | t <sub>DDKHMP</sub> |                                 |                                                                     | ns   | 6     |

| 800 MHz             |                     | $-0.5 \times t_{MCK} - 0.375$   | $\begin{array}{c} -0.5 \times t_{\text{MCK}} \\ +0.375 \end{array}$ |      |       |

| <= 667 MHz          |                     | $-0.5\times t_{\text{MCK}}-0.6$ | $-0.5 	imes t_{MCK}$ +0.6                                           |      |       |

| MDQS epilogue end   | t <sub>DDKHME</sub> |                                 |                                                                     | ns   | 6     |

| 800 MHz             |                     | -0.375                          | 0.375                                                               |      |       |

| <= 667 MHz          | t <sub>DDKHME</sub> | -0.6                            | 0.6                                                                 | ns   | 6     |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub>

(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the MDQS override bits (called WR\_DATA\_DELAY) in the TIMING\_CFG\_2 register. This typically be set to the same delay as in DDR\_SDRAM\_CLK\_CNTL[CLK\_ADJUST]. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8572E PowerQUICC<sup>TM</sup> III Integrated Host Processor Family Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

### NOTE

For the ADDR/CMD setup and hold specifications in Table 18, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

### 7.2 DUART AC Electrical Specifications

Table 22 provides the AC timing parameters for the DUART interface.

### Table 22. DUART AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter         | Value                       | Unit | Notes   |

|-------------------|-----------------------------|------|---------|

| Minimum baud rate | f <sub>CCB</sub> /1,048,576 | baud | 1, 2    |

| Maximum baud rate | f <sub>CCB</sub> /16        | baud | 1, 2, 3 |

| Oversample rate   | 16                          | _    | 1, 4    |

#### Notes:

1. Guaranteed by design

- 2. f<sub>CCB</sub> refers to the internal platform clock frequency.

- 3. Actual attainable baud rate is limited by the latency of interrupt processing.

- 4. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

### 8 Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

This section provides the AC and DC electrical characteristics for the enhanced three-speed Ethernet controller.

### 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics

The electrical characteristics specified here apply to all FIFO mode, gigabit media independent interface (GMII), media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), and reduced media independent interface (RMII) signals except management data input/output (MDIO) and management data clock (MDC), and serial gigabit media independent interface (SGMII). The RGMII, RTBI and FIFO mode interfaces are defined for 2.5 V, while the GMII, MII, RMII, and TBI interfaces can operate at both 2.5 V and 3.3V.

The GMII, MII, or TBI interface timing is compliant with IEEE 802.3. The RGMII and RTBI interfaces follow the Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3 (12/10/2000). The RMII interface follows the RMII Consortium RMII Specification Version 1.2 (3/20/1998).

The electrical characteristics for MDIO and MDC are specified in Section 9, "Ethernet Management Interface Electrical Characteristics."

The electrical characteristics for SGMII is specified in Section 8.3, "SGMII Interface Electrical Characteristics." The SGMII interface conforms (with exceptions) to the Serial-GMII Specification Version 1.8.

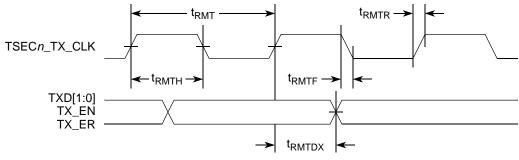

#### Table 35. RMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup> | Min | Тур | Мах  | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|------|

| TSECn_TX_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 1.0 |     | 10.0 | ns   |

Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

Figure 19 shows the RMII transmit AC timing diagram.

Figure 19. RMII Transmit AC Timing Diagram

### 8.2.7.2 RMII Receive AC Timing Specifications

Table 36 shows the RMII receive AC timing specifications.

#### Table 36. RMII Receive AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub>/TV<sub>DD</sub> of 2.5/ 3.3 V  $\pm$  5%.

| Parameter/Condition                                               | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period                                         | t <sub>RMR</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_TX_CLK duty cycle                                           | t <sub>RMRH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter                                  | t <sub>RMRJ</sub>   | —    | —    | 250  | ps   |

| Rise time TSECn_TX_CLK (20%-80%)                                  | t <sub>RMRR</sub>   | 1.0  | —    | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%–20%)                                  | t <sub>RMRF</sub>   | 1.0  | —    | 2.0  | ns   |

| RXD[1:0], CRS_DV, RX_ER setup time to<br>TSECn_TX_CLK rising edge | t <sub>RMRDV</sub>  | 4.0  | -    | —    | ns   |

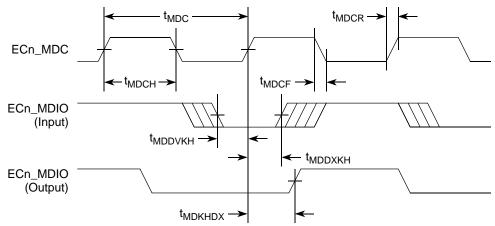

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 45. MII Management AC Timing Specifications (continued)

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 3.3 V ± 5% or 2.5 V ± 5%.

| Parameter/Condition            | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Notes |

|--------------------------------|---------------------|-----|-----|-----|------|-------|

| ECn_MDIO to ECn_MDC setup time | t <sub>MDDVKH</sub> | 5   | -   | —   | ns   | _     |

| ECn_MDIO to ECn_MDC hold time  | t <sub>MDDXKH</sub> | 0   | -   | _   | ns   | —     |

| ECn_MDC rise time              | t <sub>MDCR</sub>   | _   | _   | 10  | ns   | 4     |

| ECn_MDC fall time              | t <sub>MDHF</sub>   | _   | _   | 10  | ns   | 4     |

#### Notes:

1. The symbols used for timing specifications herein follow the pattern of t(first two letters of functional block)(signal)(state)

(reference)(state) for inputs and  $t_{(first two letters of functional block)(reference)(state)(signal)(state)}$  for outputs. For example,  $t_{MDKHDX}$  symbolizes management data timing (MD) for the time  $t_{MDC}$  from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also,  $t_{MDDVKH}$  symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the  $t_{MDC}$  clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. This parameter is dependent on the eTSEC system clock speed, which is half of the Platform Frequency ( $f_{CCB}$ ). The actual ECn\_MDC output clock frequency for a specific eTSEC port can be programmed by configuring the MgmtClk bit field of MPC8572E's MIIMCFG register, based on the platform (CCB) clock running for the device. The formula is: Platform Frequency (CCB)/(2\*Frequency Divider determined by MIICFG[MgmtClk] encoding selection). For example, if MIICFG[MgmtClk] = 000 and the platform (CCB) is currently running at 533 MHz,  $f_{MDC} = 533/(2*4*8) = 533/64 = 8.3$  MHz. That is, for a system running at a particular platform frequency ( $f_{CCB}$ ), the ECn\_MDC output clock frequency can be programmed between maximum  $f_{MDC} = f_{CCB}/64$  and minimum  $f_{MDC} = f_{CCB}/448$ . Refer to MPC8572E reference manual's MIIMCFG register section for more detail.

- 3. The maximum ECn\_MDC output clock frequency is defined based on the maximum platform frequency for MPC8572E (600 MHz) divided by 64, while the minimum ECn\_MDC output clock frequency is defined based on the minimum platform frequency for MPC8572E (400 MHz) divided by 448, following the formula described in Note 2 above. The typical ECn\_MDC output clock frequency of 2.5 MHz is shown for reference purpose per IEEE 802.3 specification.

- 4. Guaranteed by design.

- 5. t<sub>plb clk</sub> is the platform (CCB) clock.

Figure 28 shows the MII management AC timing diagram.

Figure 28. MII Management Interface Timing Diagram

### 10 Local Bus Controller (eLBC)

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8572E.

### **10.1** Local Bus DC Electrical Characteristics

Table 46 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 3.3 \text{ V}$  DC.

| Parameter                                                                      | Symbol           | Min                    | Мах                    | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------------------------|------|

| Supply voltage 3.3V                                                            | BV <sub>DD</sub> | 3.13                   | 3.47                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 2                      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3                   | 0.8                    | V    |

| Input current<br>( $BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD}$ )         | I <sub>IN</sub>  | —                      | ±5                     | μΑ   |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = −2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  | —                      | 0.2                    | V    |

Table 46. Local Bus DC Electrical Characteristics (3.3 V DC)

#### Note:

1. Note that the symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

Table 47 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 2.5 V DC$ .

Table 47. Local Bus DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                    | Symbol           | Min       | Мах                    | Unit |

|------------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5V                                                          | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level input voltage                                                     | V <sub>IH</sub>  | 1.70      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                      | V <sub>IL</sub>  | -0.3      | 0.7                    | V    |

| Input current                                                                | I <sub>IH</sub>  | _         | 10                     | μΑ   |

| $(BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD})$                          | ۱ <sub>IL</sub>  |           | -15                    |      |

| High-level output voltage<br>( $BV_{DD} = min, I_{OH} = -1 mA$ )             | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 1 mA) | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

At recommended operating conditions with OV<sub>DD</sub> of 3.3 V ± 5%. All values refer to V<sub>IH</sub> (min) and V<sub>IL</sub> (max) levels (see Table 2).

| Parameter                         | Symbol <sup>1</sup> | Min | Max | Unit |

|-----------------------------------|---------------------|-----|-----|------|

| Capacitive load for each bus line | Cb                  | —   | 400 | pF   |

#### Notes:

NXP Semiconductors

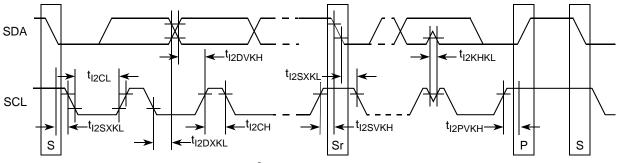

- 1. The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>I2DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>I2SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the t<sub>I2C</sub> clock reference (K) going to the t<sub>I2C</sub> clock reference (K) going to the t<sub>I2C</sub> timing (I2) for the time that the data with respect to the t<sub>I2C</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the t<sub>I2C</sub> clock reference (K) going to the low (L) state or hold time. Also, t<sub>I2PVKH</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the t<sub>I2C</sub> clock reference (K) going to the t<sub>I2C</sub> clock reference (K) going to the t<sub>I2C</sub> timing (I2) for the time that the data with respect to the t<sub>I2C</sub> clock reference (K) going to the t<sub>I2C</sub> clock reference (K) going to the t<sub>I2C</sub> timing (I2) for the time that the data with respect to the STOP condition (P) reaching the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time.</sub>

- 2. As a transmitter, the MPC8572E provides a delay time of at least 300 ns for the SDA signal (referred to the VIHmin of the SCL signal) to bridge the undefined region of the falling edge of SCL to avoid unintended generation of START or STOP condition. When the MPC8572E acts as the I2C bus master while transmitting, the MPC8572E drives both SCL and SDA. As long as the load on SCL and SDA are balanced, the MPC8572E would not cause unintended generation of START or STOP condition. Therefore, the 300 ns SDA output delay time is not a concern. If, under some rare condition, the 300 ns SDA output delay time is required for the MPC8572E as transmitter, application note AN2919 referred to in note 4 below is recommended.

- 3. The maximum t<sub>I2OVKL</sub> has only to be met if the device does not stretch the LOW period (t<sub>I2CL</sub>) of the SCL signal.

- 4. The requirements for I<sup>2</sup>C frequency calculation must be followed. Refer to Freescale application note AN2919, *Determining the I<sup>2</sup>C Frequency Divider Ratio for SCL*.

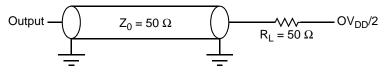

Figure 40 provides the AC test load for the  $I^2C$ .

Figure 40. I<sup>2</sup>C AC Test Load

Figure 41 shows the AC timing diagram for the  $I^2C$  bus.

Figure 41. I<sup>2</sup>C Bus AC Timing Diagram

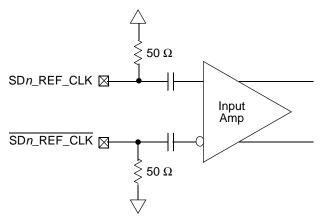

Figure 44. Receiver of SerDes Reference Clocks

### 15.2.2 DC Level Requirement for SerDes Reference Clocks

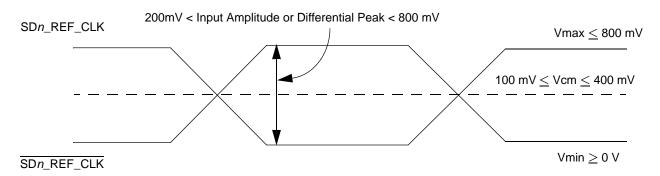

The DC level requirement for the MPC8572E SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs as described below.

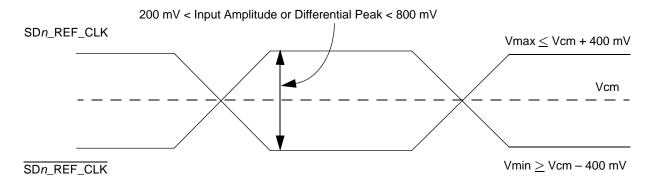

- Differential Mode

- The input amplitude of the differential clock must be between 400mV and 1600mV differential peak-peak (or between 200mV and 800mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing less than 800mV and greater than 200mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

- For external DC-coupled connection, as described in Section 15.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 mV and 400 mV.

Figure 45 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Because the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND\_SRDSn. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND\_SRDSn). Figure 46 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

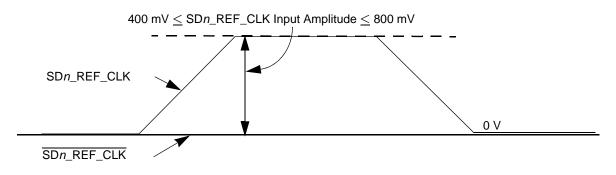

- Single-ended Mode

- The reference clock can also be single-ended. The SDn\_REF\_CLK input amplitude (single-ended swing) must be between 400 mV and 800 mV peak-peak (from Vmin to Vmax) with SDn\_REF\_CLK either left unconnected or tied to ground.

- The SDn\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 47 shows the SerDes reference clock input requirement for single-ended signaling mode.

#### High-Speed Serial Interfaces (HSSI)

— To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC-coupled externally. For the best noise performance, the reference of the clock could be DC or AC-coupled into the unused phase (SDn\_REF\_CLK) through the same source impedance as the clock input (SDn\_REF\_CLK) in use.

Figure 46. Differential Reference Clock Input DC Requirements (External AC-Coupled)

Figure 47. Single-Ended Reference Clock Input DC Requirements

Table 62. Differential Transmitter (TX) Output Specifications (continued)

| Symbol                 | Parameter                   | Min | Nominal | Max | Units | Comments                                                                                                                                                          |

|------------------------|-----------------------------|-----|---------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>crosslink</sub> | Crosslink<br>Random Timeout | 0   |         | 1   |       | This random timeout helps resolve conflicts in<br>crosslink configuration by eventually resulting in<br>only one Downstream and one Upstream Port. See<br>Note 7. |

#### Notes:

- 1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 57 and measured over any 250 consecutive TX UIs. (Also refer to the transmitter compliance eye diagram shown in Figure 55.)

- 3. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the Transmitter collected over any 250 consecutive TX UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

- 4. The Transmitter input impedance shall result in a differential return loss greater than or equal to 12 dB and a common mode return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements is 50 ohms to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50 ohm probes—see Figure 57). Note that the series capacitors C<sub>TX</sub> is optional for the return loss measurement.

- 5. Measured between 20-80% at transmitter package pins into a test load as shown in Figure 57 for both V<sub>TX-D+</sub> and V<sub>TX-D-</sub>.

- 6. See Section 4.3.1.8 of the PCI Express Base Specifications Rev 1.0a.

- 7. See Section 4.2.6.3 of the PCI Express Base Specifications Rev 1.0a.

- 8. MPC8572E SerDes transmitter does not have C<sub>TX</sub> built-in. An external AC Coupling capacitor is required.

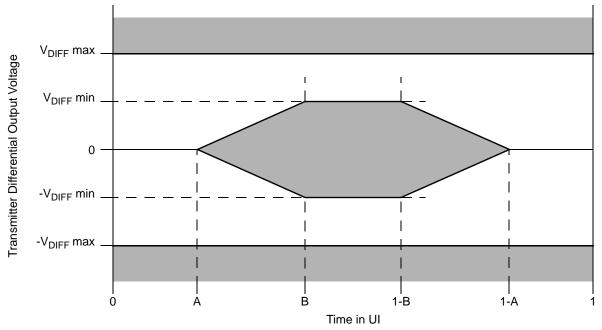

### 16.4.2 Transmitter Compliance Eye Diagrams

The TX eye diagram in Figure 55 is specified using the passive compliance/test measurement load (see Figure 57) in place of any real PCI Express interconnect + RX component.

There are two eye diagrams that must be met for the transmitter. Both eye diagrams must be aligned in time using the jitter median to locate the center of the eye diagram. The different eye diagrams differ in voltage depending whether it is a transition bit or a de-emphasized bit. The exact reduced voltage level of the de-emphasized bit is always relative to the transition bit.

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

### NOTE

It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function (that is, least squares and median deviation fits).

Serial RapidIO

# 17.1 <u>DC Requirements</u> for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK

For more information, see Section 15.2, "SerDes Reference Clocks."

# 17.2 <u>AC Requirements</u> for Serial RapidIO SD1\_REF\_CLK and SD1\_REF\_CLK

Figure 64lists the AC requirements.

| Table 64. SDn_ | _REF_CLK an | d SD <i>n</i> _REF_ | _CLK AC Requirements |

|----------------|-------------|---------------------|----------------------|

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Comments                                                         |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|------------------------------------------------------------------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 10(8)   | —   | ns    | 8 ns applies only to serial RapidIO with 125-MHz reference clock |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | —       | 80  | ps    | _                                                                |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -40 | _       | 40  | ps    | _                                                                |

### 17.3 Equalization

With the use of high speed serial links, the interconnect media causes degradation of the signal at the receiver. Effects such as Inter-Symbol Interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are as follows:

- A passive high pass filter network placed at the receiver. This is often referred to as passive equalization.

- The use of active circuits in the receiver. This is often referred to as adaptive equalization.

### 17.4 Explanatory Note on Transmitter and Receiver Specifications

AC electrical specifications are given for transmitter and receiver. Long run and short run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to serial RapidIO, as described in Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." The goal of this standard is that electrical designs for Serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

Serial RapidIO

Figure 58. Transmitter Output Compliance Mask

| Transmitter Type        | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|-------------------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud short range  | 250                        | 500                        | 0.175  | 0.39   |

| 1.25 GBaud long range   | 400                        | 800                        | 0.175  | 0.39   |

| 2.5 GBaud short range   | 250                        | 500                        | 0.175  | 0.39   |

| 2.5 GBaud long range    | 400                        | 800                        | 0.175  | 0.39   |

| 3.125 GBaud short range | 250                        | 500                        | 0.175  | 0.39   |

| 3.125 GBaud long range  | 400                        | 800                        | 0.175  | 0.39   |

Table 71. Transmitter Differential Output Eye Diagram Parameters

### 17.6 Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance shall result in a differential return loss better that 10 dB and a common mode return loss better than 6 dB from 100 MHz to  $(0.8) \times$  (Baud Frequency). This includes contributions from on-chip circuitry, the chip package and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100 Ohm resistive for differential return loss and 25- $\Omega$  resistive for common mode.

Package Description

### 18.1 Package Parameters for the MPC8572E FC-PBGA

The package parameters are as provided in the following list. The package type is  $33 \text{ mm} \times 33 \text{ mm}$ , 1023 flip chip plastic ball grid array (FC-PBGA).

| Package outline          | $33 \text{ mm} \times 33 \text{ mm}$ |

|--------------------------|--------------------------------------|

| I ackage outline         | 55 IIIII × 55 IIIII                  |

| Interconnects            | 1023                                 |

| Ball Pitch               | 1 mm                                 |

| Ball Diameter (Typical)  | 0.6 mm                               |

| Solder Balls             | 63% Sn                               |

|                          | 37% Pb                               |

| Solder Balls (Lead-Free) | 96.5% Sn                             |

|                          | 3.5% Ag                              |

| Table 76. MPC8572E Pinout Listing (continued) |

|-----------------------------------------------|

|-----------------------------------------------|

| Signal      | Signal Name                                                                      | Package Pin Number                        | Pin Type | Power<br>Supply            | Notes |

|-------------|----------------------------------------------------------------------------------|-------------------------------------------|----------|----------------------------|-------|

| SD1_RX[7:0] | Receive Data (positive)                                                          | P32, N30, M32, L30,<br>G30, F32, E30, D32 | I        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_RX[7:0] | Receive Data (negative)                                                          | P31, N29, M31, L29,<br>G29, F31, E29, D31 | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[7]   | PCIe1 Tx Data Lane 7 / SRIO or<br>PCIe2 Tx Data Lane 3 / PCIe3<br>TX Data Lane 1 | M26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 |       |

| SD1_TX[6]   | PCIe1 Tx Data Lane 6 / SRIO or<br>PCIe2 Tx Data Lane 2 / PCIe3<br>TX Data Lane 0 | L24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[5]   | PCIe1 Tx Data Lane 5 / SRIO or<br>PCIe2 Tx Data Lane 1                           | K26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[4]   | PCIe1 Tx Data Lane 4 / SRIO or<br>PCIe2 Tx Data Lane 0                           | J24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[3]   | PCIe1 Tx Data Lane 3                                                             | G24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[2]   | PCIe1 Tx Data Lane 2                                                             | F26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_TX[1]   | PCIe1 Tx Data Lane 1]                                                            | E24                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[0]   | PCIe1 Tx Data Lane 0                                                             | D26                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | —     |

| SD1_TX[7:0] | Transmit Data (negative)                                                         | M27, L25, K27, J25,<br>G25, F27, E25, D27 | 0        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_PLL_TPD | PLL Test Point Digital                                                           | J32                                       | 0        | XV <sub>DD_SR</sub><br>DS1 | 17    |

| SD1_REF_CLK | PLL Reference Clock                                                              | H32                                       | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| SD1_REF_CLK | PLL Reference Clock<br>Complement                                                | H31                                       | I        | XV <sub>DD_SR</sub><br>DS1 | _     |

| Reserved    | -                                                                                | С29, К32                                  |          | —                          | 26    |

| Reserved    | -                                                                                | С30, К31                                  |          | —                          | 27    |

| Reserved    | -                                                                                | C24, C25, H26, H27                        | _        | —                          | 28    |

| Reserved    | _                                                                                | AL20, AL21                                |          |                            | 29    |

|             | SerDes (x4)                                                                      | SGMII                                     |          |                            |       |

| SD2_RX[3:0] | Receive Data (positive)                                                          | AK32, AJ30, AF30,<br>AE32                 | I        | XV <sub>DD_SR</sub><br>DS2 | _     |

|            |                                                 |                                                                                                                                                                                                                                                                                                                                                               |          | _               |       |

|------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|-------|

| Signal     | Signal Name                                     | Package Pin Number                                                                                                                                                                                                                                                                                                                                            | Pin Type | Power<br>Supply | Notes |

| SGND_SRDS1 | SerDes Transceiver Core Logic<br>GND (xcorevss) | C28, C32, D30, E31,<br>F28, F29, G32, H28,<br>H30, J28, K29, L32,<br>M30, N31, P29, R32                                                                                                                                                                                                                                                                       | _        | _               | _     |

| SGND_SRDS2 | SerDes Transceiver Core Logic<br>GND (xcorevss) | AE28, AE30, AF28,<br>AF32, AG28, AG30,<br>AH28, AJ28, AJ31,<br>AL32                                                                                                                                                                                                                                                                                           | _        | _               | _     |

| AGND_SRDS1 | SerDes PLL GND                                  | J31                                                                                                                                                                                                                                                                                                                                                           | —        | —               | _     |

| AGND_SRDS2 | SerDes PLL GND                                  | AH31                                                                                                                                                                                                                                                                                                                                                          | —        | —               | _     |

| OVDD       | General I/O Supply                              | U31, V24, V28, Y31,<br>AA27, AB25, AB29                                                                                                                                                                                                                                                                                                                       | —        | OVDD            | _     |

| LVDD       | TSEC 1&2 I/O Supply                             | AC18, AC21, AG21,<br>AL27                                                                                                                                                                                                                                                                                                                                     | —        | LVDD            | _     |

| TVDD       | TSEC 3&4 I/O Supply                             | AC15, AE16, AH18                                                                                                                                                                                                                                                                                                                                              | —        | TVDD            | _     |

| GVDD       | SSTL_1.8 DDR Supply                             | B2, B5, B8, B11, B14,<br>D4, D7, D10, D13, E2,<br>F6, F9, F12, G4, H2,<br>H8, H11, H14, J6, K4,<br>K10, K13, L2, L8, M6,<br>N4, N10, P2, P8, R6,<br>T4, T10, U2, U8, V6,<br>W4, W10, Y2, Y8, AA6,<br>AB4, AB10, AC2, AC8,<br>AD6, AD12, AE4,<br>AE10, AF2, AF8, AG6,<br>AG12, AH4, AH10,<br>AH16, AJ2, AJ8, AJ14,<br>AK6, AK12, AK18, AL4,<br>AL10, AL16, AM2 |          | GVDD            | _     |

| BVDD       | Local Bus and GPIO Supply                       | A26, A30, B21, D16,<br>D21, F18, G20, H17,<br>J22, K15, K20                                                                                                                                                                                                                                                                                                   | —        | BVDD            | —     |

| Signal             | Signal Name                         | Package Pin Number | Pin Type | Power<br>Supply         | Notes |

|--------------------|-------------------------------------|--------------------|----------|-------------------------|-------|

| SD1_IMP_CAL_RX     | SerDes1 Rx Impedance<br>Calibration | B32                | I        | 200Ω<br>(±1%) to<br>GND | _     |

| SD1_IMP_CAL_TX     | SerDes1 Tx Impedance<br>Calibration | T32                | I        | 100Ω<br>(±1%) to<br>GND | _     |

| SD1_PLL_TPA        | SerDes1 PLL Test Point Analog       | J30                | 0        | AVDD_S<br>RDS<br>analog | 17    |

| SD2_IMP_CAL_RX     | SerDes2 Rx Impedance<br>Calibration | AC32               | I        | 200Ω<br>(±1%) to<br>GND | —     |

| SD2_IMP_CAL_TX     | SerDes2 Tx Impedance<br>Calibration | AM32               | I        | 100Ω<br>(±1%) to<br>GND | —     |

| SD2_PLL_TPA        | SerDes2 PLL Test Point Analog       | AH30               | 0        | AVDD_S<br>RDS<br>analog | 17    |

| TEMP_ANODE         | Temperature Diode Anode             | AA31               | _        | internal<br>diode       | 14    |

| TEMP_CATHODE       | Temperature Diode Cathode           | AB31               |          | internal<br>diode       | 14    |

| No Connection Pins |                                     | 1                  |          | 11                      |       |

### Table 76. MPC8572E Pinout Listing (continued)

| Binary Value of<br>TSEC_1588_CLK_OUT,<br>TSEC_1588_PULSE_OUT1,<br>TSEC_1588_PULSE_OUT2 Signals | DDR:DDRCLK Ratio |

|------------------------------------------------------------------------------------------------|------------------|

| 101                                                                                            | 12:1             |

| 110                                                                                            | 14:1             |

| 111                                                                                            | Synchronous mode |

Table 82. DDR Clock Ratio (continued)

### **19.5 Frequency Options**

### **19.5.1** Platform to Sysclk Frequency Options

Table 83 shows the expected frequency values for the platform frequency when using the specified CCB clock to SYSCLK ratio.

| CCB to<br>SYSCLK Ratio | SYSCLK (MHz) |                               |     |       |     |     |     |        |  |

|------------------------|--------------|-------------------------------|-----|-------|-----|-----|-----|--------|--|

|                        | 33.33        | 41.66                         | 50  | 66.66 | 83  | 100 | 111 | 133.33 |  |

|                        |              | Platform /CCB Frequency (MHz) |     |       |     |     |     |        |  |

| 4                      |              |                               |     |       |     | 400 | 444 | 533    |  |

| 5                      |              |                               |     |       | 415 | 500 | 555 |        |  |

| 6                      |              |                               |     | 400   | 498 | 600 |     |        |  |

| 8                      |              |                               | 400 | 533   |     |     | -   |        |  |

| 10                     |              | 417                           | 500 |       | -   |     |     |        |  |

| 12                     | 400          | 500                           | 600 | ]     |     |     |     |        |  |

Table 83. Frequency Options for Platform Frequency

### 19.5.2 Minimum Platform Frequency Requirements for High-Speed Interfaces

Section 4.4.3.6, "I/O Port Selection," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* describes various high-speed interface configuration options. Note that the CCB clock frequency must be considered for proper operation of such interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than or equal to:

See Section 21.1.3.2, "Link Width," in the *MPC8572E PowerQUICC III Integrated Host Processor Family Reference Manual* for PCI Express interface width details. Note that the "PCI Express link width"

Table 85 summarizes the signal impedance targets. The driver impedances are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet, DUART,<br>Control, Configuration, Power<br>Management | DDR DRAM                                                         | Symbol         | Unit |

|----------------|----------------------------------------------------------------------------|------------------------------------------------------------------|----------------|------|

| R <sub>N</sub> | 45 Target                                                                  | 18 Target (full strength mode)<br>36 Target (half strength mode) | Z <sub>0</sub> | Ω    |

| R <sub>P</sub> | 45 Target                                                                  | 18 Target (full strength mode)<br>36 Target (half strength mode) | Z <sub>0</sub> | Ω    |

Table 85. Impedance Characteristics

**Note:** Nominal supply voltages. See Table 1,  $T_i = 105^{\circ}C$ .

### 21.8 Configuration Pin Muxing

The MPC8572E provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While  $\overline{\text{HRESET}}$  is asserted however, these pins are treated as inputs. The value presented on these pins while  $\overline{\text{HRESET}}$  is asserted, is latched when  $\overline{\text{HRESET}}$  deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Most of these sampled configuration pins are equipped with an on-chip gated resistor of approximately 20 kΩ. This value should permit the 4.7-kΩ resistor to pull the configuration pin to a valid logic low level. The pull-up resistor is enabled only during  $\overline{\text{HRESET}}$  (and for platform /system clocks after  $\overline{\text{HRESET}}$  deassertion to ensure capture of the reset value). When the input receiver is disabled the pull-up is also, thus allowing functional operation of the pin as an output with minimal signal quality or delay disruption. The default value for all configuration bits treated this way has been encoded such that a high voltage level puts the device into the default state and external resistors are needed only when non-default settings are required by the user.

Careful board layout with stubless connections to these pull-down resistors coupled with the large value of the pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

The platform PLL ratio, DDR complex PLL and e500 PLL ratio configuration pins are not equipped with these default pull-up devices.

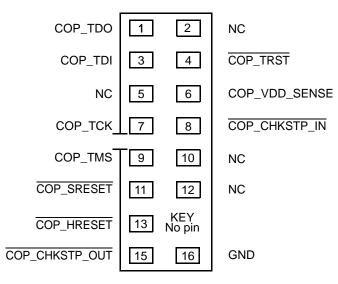

### 21.9 JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 66. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The  $\overline{\text{TRST}}$  signal is optional in the IEEE Std 1149.1 specification, but it is provided on all processors built on Power Architecture technology. The device requires  $\overline{\text{TRST}}$  to be asserted during power-on reset flow to ensure that the JTAG boundary

System Design Information

Figure 65. COP Connector Physical Pinout