# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                         |

| Speed                           | 1.5GHz                                                                 |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                  |

| RAM Controllers                 | DDR2, DDR3                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                                 |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                  |

| Package / Case                  | 1023-BFBGA, FCBGA                                                      |

| Supplier Device Package         | 1023-FCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/ppc8572evtavnc |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

- Ability to launch DMA from single write transaction

- Serial RapidIO interface unit

- Supports RapidIO Interconnect Specification, Revision 1.2

- Both 1x and 4x LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto-detection of 1x- and 4x-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO–compliant message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

- Single inbound doorbell message structure

- Facility to accept port-write messages

- Three PCI Express controllers

- PCI Express 1.0a compatible

- Supports x8, x4, x2, and x1 link widths (see following bullet for specific width configuration options)

- Auto-detection of number of connected lanes

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 256-byte maximum payload size

- Virtual channel 0 only

- Full 64-bit decode with 36-bit wide windows

- Pin multiplexing for the high-speed I/O interfaces supports one of the following configurations:

- Single x8/x4/x2/x1 PCI Express

- Dual x4/x2/x1 PCI Express

- Single x4/x2/x1 PCI Express and dual x2/x1 PCI Express

- Single 1x/4x Serial RapidIO and single x4/x2/x1 PCI Express

- Power management

- Supports power saving modes: doze, nap, and sleep

- Employs dynamic power management, that automatically minimizes power consumption of blocks when they are idle

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the eight counters

- Supports duration and quantity threshold counting

- Permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- IEEE Std 1149.1<sup>™</sup> compatible, JTAG boundary scan

- 1023 FC-PBGA package

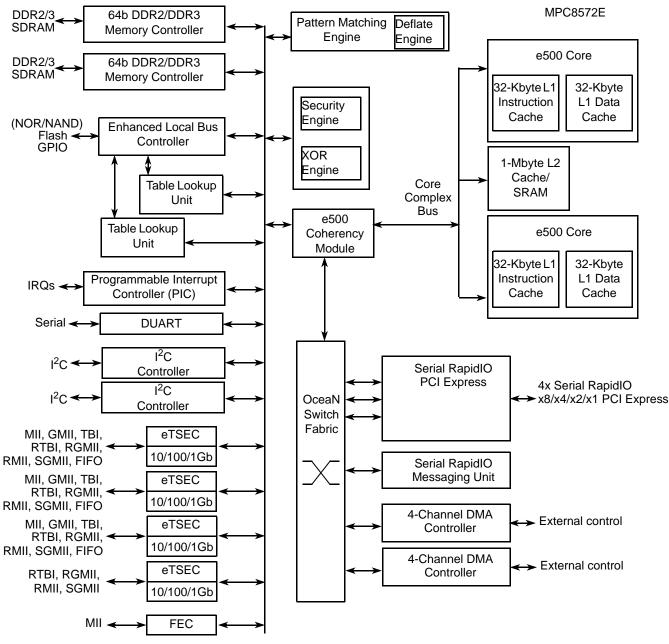

Figure 1 shows the MPC8572E block diagram.

# 2 **Electrical Characteristics**

This section provides the AC and DC electrical specifications for the MPC8572E. The MPC8572E is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

## NOTE

From a system standpoint, if any of the I/O power supplies ramp prior to the VDD core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-on reset, and extra current may be drawn by the device.

# **3** Power Characteristics

The estimated typical power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III devices with out the L in its part ordering is shown in Table 4.

| CCB Frequency | Core Frequency | Typical-65 <sup>2</sup> | Typical-105 <sup>3</sup> | Maximum <sup>4</sup> | Unit |

|---------------|----------------|-------------------------|--------------------------|----------------------|------|

| 533           | 1067           | 12.3                    | 17.8                     | 18.5                 | W    |

| 533           | 1200           | 12.3                    | 17.8                     | 18.5                 | W    |

| 533           | 1333           | 16.3                    | 22.8                     | 24.5                 | W    |

| 600           | 1500           | 17.3                    | 23.9                     | 25.9                 | W    |

| Table 4. MPC8572E | Power | Dissipation <sup>1</sup> |  |

|-------------------|-------|--------------------------|--|

|                   |       | Dissipation              |  |

Notes:

<sup>1</sup> This reflects the MPC8572E power dissipation excluding the power dissipation from B/G/L/O/T/XV<sub>DD</sub> rails.

$^2~$  Typical-65 is based on V\_DD = 1.1 V, T\_j = 65 °C, running Dhrystone.

<sup>3</sup> Typical-105 is based on  $V_{DD}$  = 1.1 V,  $T_i$  = 105 °C, running Dhrystone.

<sup>4</sup> Maximum is based on  $V_{DD}$  = 1.1 V,  $T_j$  = 105 °C, running a smoke test.

The estimated typical power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III devices with the L in its port ordering is shown in Table 5.

| CCB Frequency | Core Frequency | Typical-65 <sup>2</sup> | Typical-105 <sup>3</sup> | Maximum <sup>4</sup> | Unit |

|---------------|----------------|-------------------------|--------------------------|----------------------|------|

| 533           | 1067           | 12                      | 15                       | 15.8                 | W    |

| 533           | 1200           | 12                      | 15.5                     | 16.3                 | W    |

| 533           | 1333           | 12                      | 15.9                     | 16.9                 | W    |

| 600           | 1500           | 13                      | 18.7                     | 20.0                 | W    |

Table 5. MPC8572EL Power Dissipation <sup>1</sup>

Notes:

<sup>1</sup> This reflects the MPC8572E power dissipation excluding the power dissipation from B/G/L/O/T/XV<sub>DD</sub> rails.

<sup>2</sup> Typical-65 is based on  $V_{DD}$  = 1.1 V, T<sub>j</sub> = 65 °C, running Dhrystone.

<sup>3</sup> Typical-105 is based on V<sub>DD</sub> = 1.1 V,  $T_i$  = 105 °C, running Dhrystone.

$^4$  Maximum is based on V\_{DD} = 1.1 V, T\_j = 105 °C, running a smoke test.

Table 25. FIFO Mode Transmit AC Timing Specification (continued)

At recommended operating conditions with LV\_{DD}/TV\_{DD} of 2.5V  $\pm\,5\%$

| Parameter/Condition                                    | Symbol             | Min | Тур | Max  | Unit |

|--------------------------------------------------------|--------------------|-----|-----|------|------|

| TX_CLK, GTX_CLK peak-to-peak jitter                    | t <sub>FITJ</sub>  | _   | —   | 250  | ps   |

| Rise time TX_CLK (20%–80%)                             | t <sub>FITR</sub>  | _   | —   | 0.75 | ns   |

| Fall time TX_CLK (80%–20%)                             | t <sub>FITF</sub>  | _   | —   | 0.75 | ns   |

| FIFO data TXD[7:0], TX_ER, TX_EN setup time to GTX_CLK | t <sub>FITDV</sub> | 2.0 | —   | —    | ns   |

| GTX_CLK to FIFO data TXD[7:0], TX_ER, TX_EN hold time  | t <sub>FITDX</sub> | 0.5 | —   | 3.0  | ns   |

Notes:

1. The minimum cycle period (or maximum frequency) of the TX\_CLK is dependent on the maximum platform frequency of the speed bins the part belongs to as well as the FIFO mode under operation. Refer to Section 4.5, "Platform to eTSEC FIFO Restrictions," for more detailed description.

#### Table 26. FIFO Mode Receive AC Timing Specification

At recommended operating conditions with  $LV_{DD}/TV_{DD}$  of 2.5V ± 5%

| Parameter/Condition                         | Symbol                              | Min | Тур | Max  | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|------|------|

| RX_CLK clock period <sup>1</sup>            | t <sub>FIR</sub>                    | 5.3 | 8.0 | 100  | ns   |

| RX_CLK duty cycle                           | t <sub>FIRH</sub> /t <sub>FIR</sub> | 45  | 50  | 55   | %    |

| RX_CLK peak-to-peak jitter                  | t <sub>FIRJ</sub>                   | —   | —   | 250  | ps   |

| Rise time RX_CLK (20%-80%)                  | t <sub>FIRR</sub>                   | —   | —   | 0.75 | ns   |

| Fall time RX_CLK (80%–20%)                  | t <sub>FIRF</sub>                   | —   | —   | 0.75 | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>FIRDV</sub>                  | 1.5 | —   | —    | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>FIRDX</sub>                  | 0.5 | —   | —    | ns   |

1. The minimum cycle period (or maximum frequency) of the RX\_CLK is dependent on the maximum platform frequency of the speed bins the part belongs to as well as the FIFO mode under operation. Refer to Section 4.5, "Platform to eTSEC FIFO Restrictions," for more detailed description.

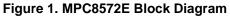

Figure 7 and Figure 8 show the FIFO timing diagrams.

Figure 7. FIFO Transmit AC Timing Diagram

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

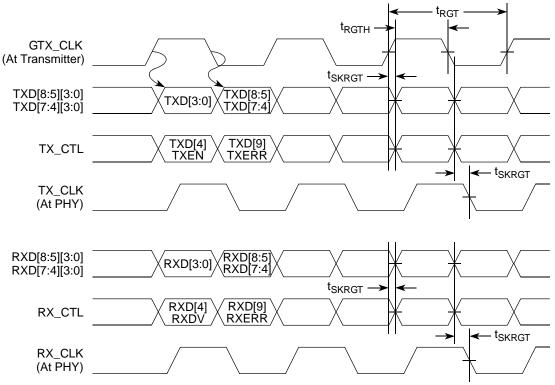

Figure 18. RGMII and RTBI AC Timing and Multiplexing Diagrams

# 8.2.7 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

## 8.2.7.1 RMII Transmit AC Timing Specifications

Table 35 shows the RMII transmit AC timing specifications.

#### Table 35. RMII Transmit AC Timing Specifications

```

At recommended operating conditions with LV_{DD}/TV_{DD} of 2.5/ 3.3 V \pm 5%.

```

| Parameter/Condition              | Symbol <sup>1</sup> | Min  | Тур  | Мах  | Unit |

|----------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period        | t <sub>RMT</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_TX_CLK duty cycle          | t <sub>RMTH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter | t <sub>RMTJ</sub>   | _    | _    | 250  | ps   |

| Rise time TSECn_TX_CLK (20%-80%) | t <sub>RMTR</sub>   | 1.0  | _    | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%–20%) | t <sub>RMTF</sub>   | 1.0  | _    | 2.0  | ns   |

described in Section 21.5, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

When operating in SGMII mode, the eTSEC EC\_GTX\_CLK125 clock is not required for this port. Instead, SerDes reference clock is required on SD2\_REF\_CLK and SD2\_REF\_CLK pins.

# 8.3.1 DC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 15, "High-Speed Serial Interfaces (HSSI)."

## 8.3.2 AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

Table 37 lists the SGMII SerDes reference clock AC requirements. Note that SD2\_REF\_CLK and SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | _   | 10 (8)  |     | ns    | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles |     |         | 100 | ps    | —     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | —       | 50  | ps    | —     |

## Table 37. SD2\_REF\_CLK and SD2\_REF\_CLK AC Requirements

Note:

1.8 ns applies only when 125 MHz SerDes2 reference clock frequency is selected through cfg\_srds\_sgmii\_refclk during POR.

# 10 Local Bus Controller (eLBC)

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8572E.

# **10.1** Local Bus DC Electrical Characteristics

Table 46 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 3.3 \text{ V}$  DC.

| Parameter                                                                      | Symbol           | Min                    | Мах                    | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------------------------|------|

| Supply voltage 3.3V                                                            | BV <sub>DD</sub> | 3.13                   | 3.47                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 2                      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3                   | 0.8                    | V    |

| Input current<br>( $BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD}$ )         | I <sub>IN</sub>  | —                      | ±5                     | μΑ   |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = −2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  | —                      | 0.2                    | V    |

Table 46. Local Bus DC Electrical Characteristics (3.3 V DC)

Image: Comparison of the second sec

#### Note:

1. Note that the symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

Table 47 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 2.5 V DC$ .

Table 47. Local Bus DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                    | Symbol           | Min       | Мах                    | Unit |

|------------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5V                                                          | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level input voltage                                                     | V <sub>IH</sub>  | 1.70      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                      | V <sub>IL</sub>  | -0.3      | 0.7                    | V    |

| Input current                                                                | I <sub>IH</sub>  | _         | 10                     | μΑ   |

| $(BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD})$                          | ۱ <sub>IL</sub>  |           | -15                    |      |

| High-level output voltage<br>( $BV_{DD} = min, I_{OH} = -1 mA$ )             | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 1 mA) | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

# NP

#### Local Bus Controller (eLBC)

Table 50. Local Bus General Timing Parameters ( $BV_{DD} = 2.5 V DC$ )—PLL Enabled (continued)At recommended operating conditions with  $BV_{DD}$  of 2.5 V ± 5% (continued)

| Parameter                                                          | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output valid (except LAD/LDP and LALE)          | t <sub>LBKHOV1</sub> | —   | 2.4 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                          | t <sub>LBKHOV2</sub> | —   | 2.5 | ns   | 3     |

| Local bus clock to address valid for LAD                           | t <sub>LBKHOV3</sub> | —   | 2.4 | ns   | 3     |

| Local bus clock to LALE assertion                                  | t <sub>LBKHOV4</sub> | —   | 2.4 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)         | t <sub>LBKHOX1</sub> | 0.8 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKHOX2</sub> | 0.8 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKHOZ1</sub> | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKHOZ2</sub> | —   | 2.6 | ns   | 5     |

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 2.5-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

Table 51 describes the general timing parameters of the local bus interface at  $BV_{DD} = 1.8 \text{ V DC}$

Table 51. Local Bus General Timing Parameters ( $BV_{DD} = 1.8 \text{ V DC}$ )—PLL Enabled At recommended operating conditions with  $BV_{DD}$  of 1.8 V ± 5%

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 6.67 | 12  | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43   | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                  | t <sub>LBKSKEW</sub>                | _    | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 2.4  | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKH2</sub>                | 1.9  | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | 1.1  | —   | ns   | 3, 4  |

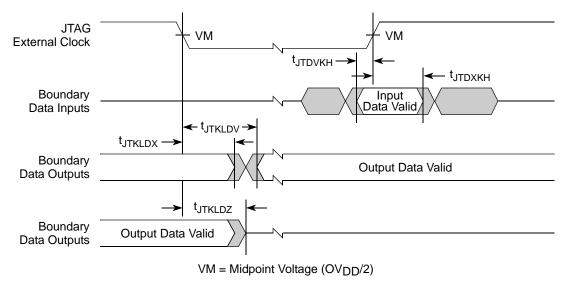

Figure 39. Boundary-Scan Timing Diagram

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the MPC8572E.

# 13.1 I<sup>2</sup>C DC Electrical Characteristics

Table 54 provides the DC electrical characteristics for the  $I^2C$  interfaces.

| Table 54. I <sup>2</sup> C DC Electrical Characteristic | ;S |

|---------------------------------------------------------|----|

|---------------------------------------------------------|----|

| Parameter                                                                                                | Symbol              | Min                                | Мах                    | Unit | Notes |

|----------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------|------|-------|

| Input high voltage level                                                                                 | V <sub>IH</sub>     | $0.7 \times \text{OV}_{\text{DD}}$ | OV <sub>DD</sub> + 0.3 | V    | —     |

| Input low voltage level                                                                                  | V <sub>IL</sub>     | -0.3                               | $0.3 	imes OV_{DD}$    | V    | —     |

| Low level output voltage                                                                                 | V <sub>OL</sub>     | 0                                  | 0.4                    | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>I2KHKL</sub> | 0                                  | 50                     | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | Ι <sub>Ι</sub>      | -10                                | 10                     | μΑ   | 3     |

1<sup>2</sup>C

## Table 54. I<sup>2</sup>C DC Electrical Characteristics (continued)

| Capacitance for each I/O pin C <sub>1</sub> | — 10 | pF | — |

|---------------------------------------------|------|----|---|

|---------------------------------------------|------|----|---|

#### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2. Refer to the MPC8572E PowerQUICC<sup>™</sup> III Integrated Host Processor Family Reference Manual for information on the digital filter used.

3. I/O pins will obstruct the SDA and SCL lines if  $\mathsf{OV}_\mathsf{DD}$  is switched off.

# 13.2 I<sup>2</sup>C AC Electrical Specifications

Table 55 provides the AC timing parameters for the  $I^2C$  interfaces.

## Table 55. I<sup>2</sup>C AC Electrical Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 5%. All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 2).

| Parameter                                                                                    | Symbol <sup>1</sup> | Min                  | Мах              | Unit             |

|----------------------------------------------------------------------------------------------|---------------------|----------------------|------------------|------------------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0                    | 400              | kHz <sup>4</sup> |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3                  | _                | μs               |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6                  | —                | μs               |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6                  | —                | μs               |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6                  | _                | μs               |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100                  | —                | ns               |

| Data input hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices             | t <sub>I2DXKL</sub> | $\overline{0^2}$     | _                | μs               |

| Data output delay time                                                                       | t <sub>I2OVKL</sub> | —                    | 0.9 <sup>3</sup> | μs               |

| Setup time for STOP condition                                                                | t <sub>I2PVKH</sub> | 0.6                  | —                | μs               |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub> | 1.3                  | —                | μs               |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>     | $0.1 \times OV_{DD}$ | _                | V                |

| Noise margin at the HIGH level for each connected device (including hysteresis)              | V <sub>NH</sub>     | $0.2 \times OV_{DD}$ | _                | V                |

#### High-Speed Serial Interfaces (HSSI)

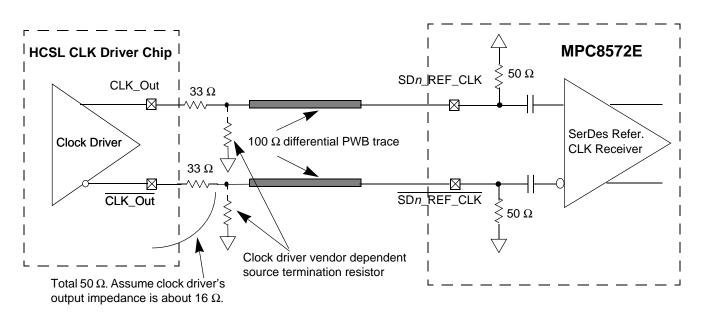

Figure 48 shows the SerDes reference clock connection reference circuits for HCSL type clock driver. It assumes that the DC levels of the clock driver chip is compatible with MPC8572E SerDes reference clock input's DC requirement.

Figure 48. DC-Coupled Differential Connection with HCSL Clock Driver (Reference Only)

Serial RapidIO

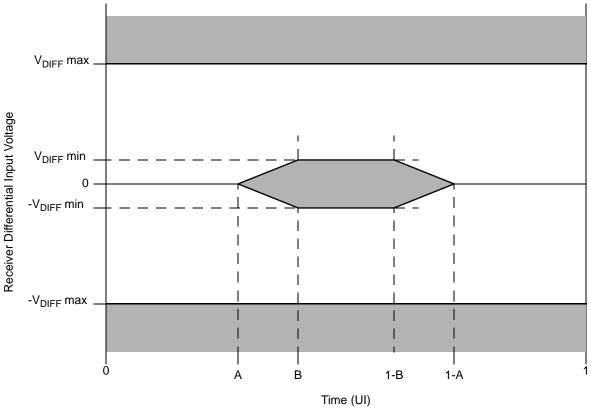

Figure 60. Receiver Input Compliance Mask

| Receiver Type | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|---------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud    | 100                        | 800                        | 0.275  | 0.400  |

| 2.5 GBaud     | 100                        | 800                        | 0.275  | 0.400  |

| 3.125 GBaud   | 100                        | 800                        | 0.275  | 0.400  |

# 17.8 Measurement and Test Requirements

Because the LP-Serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002, the measurement and test requirements defined here are similarly guided by Clause 47. Additionally, the CJPAT test pattern defined in Annex 48A of IEEE 802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter measurements. Annex 48B of IEEE 802.3ae-2002 is recommended as a reference for additional information on jitter test methods.

# 17.8.1 Eye Template Measurements

For the purpose of eye template measurements, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for template measurements is the Continuous Jitter Test Pattern (CJPAT) defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial

Package Description

# 18.1 Package Parameters for the MPC8572E FC-PBGA

The package parameters are as provided in the following list. The package type is  $33 \text{ mm} \times 33 \text{ mm}$ , 1023 flip chip plastic ball grid array (FC-PBGA).

| Package outline          | $33 \text{ mm} \times 33 \text{ mm}$ |

|--------------------------|--------------------------------------|

| I ackage outline         | 55 IIIII × 55 IIIII                  |

| Interconnects            | 1023                                 |

| Ball Pitch               | 1 mm                                 |

| Ball Diameter (Typical)  | 0.6 mm                               |

| Solder Balls             | 63% Sn                               |

|                          | 37% Pb                               |

| Solder Balls (Lead-Free) | 96.5% Sn                             |

|                          | 3.5% Ag                              |

**Package Description**

- 5. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 6. Parallelism measurement shall exclude any effect of mark on top surface of package.

# 18.3 Pinout Listings

Table 76 provides the pin-out listing for the MPC8572E 1023 FC-PBGA package.

### Table 76. MPC8572E Pinout Listing

| Signal       | Signal Name           | Signal Name Package Pin Number                                                                                                                                                                                                                                                                                                                                                            |     | Power<br>Supply  | Notes |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-------|

|              | DDR SDRAM N           | lemory Interface 1                                                                                                                                                                                                                                                                                                                                                                        |     |                  |       |

| D1_MDQ[0:63] | Data                  | D15, A14, B12, D12,<br>A15, B15, B13, C13,<br>C11, D11, D9, A8, A12,<br>A11, A9, B9, F11, G12,<br>K11, K12, E10, E9, J11,<br>J10, G8, H10, L10,<br>M11, F10, G9, K9, K8,<br>AC6, AC7, AG8, AH9,<br>AB6, AB8, AE9, AF9,<br>AL8, AM8, AM10,<br>AK11, AH8, AK8, AJ10,<br>AK10, AL12, AJ12,<br>AL14, AK14, AL11,<br>AM11, AK13, AM14,<br>AM15, AJ16, AL18,<br>AM18, AJ15, AL15,<br>AK17, AM17 | I/O | GV <sub>DD</sub> | _     |

| D1_MECC[0:7] | Error Correcting Code | M10, M7, R8, T11, L12,<br>L11, P9, R10                                                                                                                                                                                                                                                                                                                                                    | I/O | GV <sub>DD</sub> | —     |

| D1_MAPAR_ERR | Address Parity Error  | P6                                                                                                                                                                                                                                                                                                                                                                                        | Ι   | GV <sub>DD</sub> | _     |

| D1_MAPAR_OUT | Address Parity Out    | W6                                                                                                                                                                                                                                                                                                                                                                                        | 0   | GV <sub>DD</sub> | _     |

| D1_MDM[0:8]  | Data Mask             | C14, A10, G11, H9,<br>AD7, AJ9, AM12,<br>AK16, N11                                                                                                                                                                                                                                                                                                                                        | 0   | GV <sub>DD</sub> | _     |

| D1_MDQS[0:8] | Data Strobe           | A13, C10, H12, J7,<br>AE8, AM9, AM13,<br>AL17, N9                                                                                                                                                                                                                                                                                                                                         | I/O | GV <sub>DD</sub> | _     |

| D1_MDQS[0:8] | Data Strobe           | D14, B10, H13, J8,<br>AD8, AL9, AJ13,<br>AM16, P10                                                                                                                                                                                                                                                                                                                                        | I/O | GV <sub>DD</sub> | _     |

| D1_MA[0:15]  | Address               | Y7, W8, U6, W9, U7,<br>V8, Y11, V10, T6, V11,<br>AA10, U9, U10, AD11,<br>T8, P7                                                                                                                                                                                                                                                                                                           | 0   | GV <sub>DD</sub> |       |

| D1_MBA[0:2]  | Bank Select           | AA7, AA8, R7                                                                                                                                                                                                                                                                                                                                                                              | 0   | GV <sub>DD</sub> | —     |

| D1_MWE       | Write Enable          | AC12                                                                                                                                                                                                                                                                                                                                                                                      | 0   | GV <sub>DD</sub> | _     |

|              |                              | ,                                                                                                                                                                                                                                                                                                                                 |          | Damas            |       |

|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| Signal       | Signal Name                  | Package Pin Number                                                                                                                                                                                                                                                                                                                | Pin Type | Power<br>Supply  | Notes |

| D1_MCAS      | Column Address Strobe        | AC9                                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | _     |

| D1_MRAS      | Row Address Strobe           | AB12                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> |       |

| D1_MCKE[0:3] | Clock Enable                 | M8, L9, T9, N8                                                                                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | 11    |

| D1_MCS[0:3]  | Chip Select                  | AB9, AF10, AB11,<br>AE11                                                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | —     |

| D1_MCK[0:5]  | Clock                        | V7, E13, AH11, Y9,<br>F14, AG10                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | _     |

| D1_MCK[0:5]  | Clock Complements            | Y10, E12, AH12, AA11,<br>F13, AG11                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub> |       |

| D1_MODT[0:3] | On Die Termination           | AD10, AF12, AC10,<br>AE12                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> |       |

| D1_MDIC[0:1] | Driver Impedance Calibration | E15, G14                                                                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | 25    |

|              | DDR SDRAM Mem                | ory Interface 2                                                                                                                                                                                                                                                                                                                   |          |                  |       |

| D2_MDQ[0:63] | Data                         | A6, B7, C5, D5, A7, C8,<br>D8, D6, C4, A3, D3,<br>D2, B4, A4, B1, C1, E3,<br>E1, G2, G6, D1, E4,<br>G5, G3, J4, J2, P4, R5,<br>H3, H1, N5, N3, Y6, Y4,<br>AC3, AD2, V5, W5,<br>AB2, AB3, AD5, AE3,<br>AF6, AG7, AC4, AD4,<br>AF4, AF7, AH5, AJ1,<br>AL2, AM3, AH3, AH6,<br>AM1, AL3, AK5, AL5,<br>AJ7, AK7, AK4, AM4,<br>AL6, AM7 | I/O      | GV <sub>DD</sub> |       |

| D2_MECC[0:7] | Error Correcting Code        | J5, H7, L7, N6, H4, H6,<br>M4, M5                                                                                                                                                                                                                                                                                                 | I/O      | GV <sub>DD</sub> | —     |

| D2_MAPAR_ERR | Address Parity Error         | N1                                                                                                                                                                                                                                                                                                                                | I        | GV <sub>DD</sub> |       |

| D2_MAPAR_OUT | Address Parity Out           | W2                                                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub> |       |

| D2_MDM[0:8]  | Data Mask                    | A5, B3, F4, J1, AA4,<br>AE5, AK1, AM5, K5                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> |       |

| D2_MDQS[0:8] | Data Strobe                  | B6, C2, F5, L4, AB5,<br>AF3, AL1, AM6, L6                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | —     |

| D2_MDQS[0:8] | Data Strobe                  | C7, A2, F2, K3, AA5,<br>AE6, AK2, AJ6, K6                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> |       |

| D2_MA[0:15]  | Address                      | W1, U4, U3, T1, T2, T3,<br>R1, R2, T5, R4, Y3, P1,<br>N2, AF1, M2, M1                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> |       |

## Table 76. MPC8572E Pinout Listing (continued)

Package Description

| Signal Name                                 | Package Pin Number                                                                                                                                                                                          | Pin Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power<br>Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Data (negative)                     | AK31, AJ29, AF29,<br>AE31                                                                                                                                                                                   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SGMII Tx Data eTSEC4                        | AH26                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SGMII Tx Data eTSEC3                        | AG24                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SGMII Tx Data eTSEC2                        | AE24                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SGMII Tx Data eTSEC1                        | AD26                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Transmit Data (negative)                    | AH27, AG25, AE25,<br>AD27                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PLL Test Point Digital                      | AH32                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PLL Reference Clock                         | AG32                                                                                                                                                                                                        | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PLL Reference Clock<br>Complement           | AG31                                                                                                                                                                                                        | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XV <sub>DD_SR</sub><br>DS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| —                                           | AF26, AF27                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| General-Purpose                             | Input/Output                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| General Purpose Input / Output              | B27, A28, B31, A32,<br>B30, A31, B28, B29                                                                                                                                                                   | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| System Co                                   | ontrol                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |