Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | F <sup>2</sup> MC-8FX                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 16MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                            |

| Number of I/O              | 54                                                                            |

| Program Memory Size        | 60KB (60K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                   |

| Data Converters            | A/D 12x8/10b                                                                  |

| Oscillator Type            | External                                                                      |

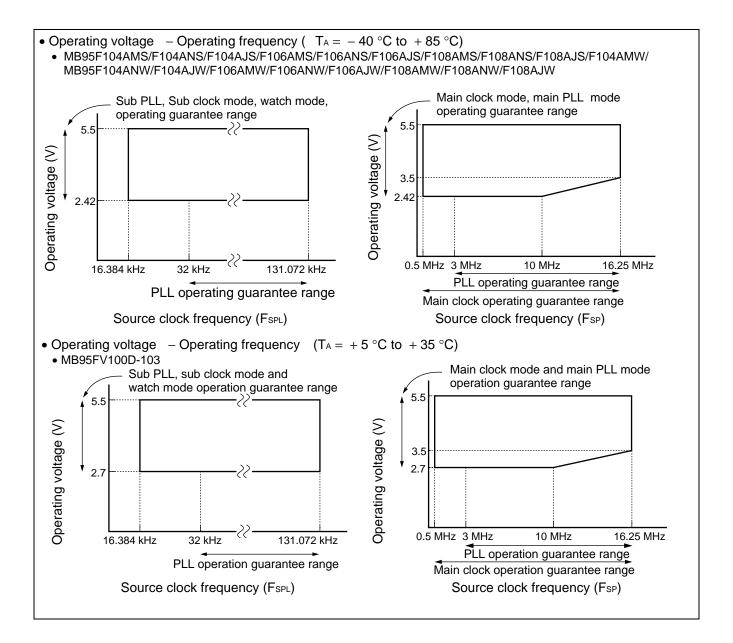

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-LQFP                                                                       |

| Supplier Device Package    | 64-LQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f108ajwpmc-ge1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## ■ HANDLING DEVICES

Preventing Latch-up

Care must be taken to ensure that maximum voltage ratings are not exceeded when they are used.

Latch-up may occur on CMOS ICs if voltage higher than  $V_{cc}$  or lower than  $V_{ss}$  is applied to input and output pins other than medium- and high-withstand voltage pins or if higher than the rating voltage is applied between  $V_{cc}$  pin and  $V_{ss}$  pin.

When latch-up occurs, power supply current increases rapidly and might thermally damage elements.

Also, take care to prevent the analog power supply voltage (AVcc, AVR) and analog input voltage from exceeding the digital power supply voltage (Vcc) when the analog system power supply is turned on or off.

• Stable Supply Voltage

Supply voltage should be stabilized.

A sudden change in power-supply voltage may cause a malfunction even within the guaranteed operating range of the Vcc power-supply voltage.

For stabilization, in principle, keep the variation in Vcc ripple (p-p value) in a commercial frequency range (50 Hz/60 Hz) not to exceed 10% of the standard Vcc value and suppress the voltage variation so that the transient variation rate does not exceed 0.1 V/ms during a momentary change such as when the power supply is switched.

• Precautions for Use of External Clock

Even when an external clock is used, oscillation stabilization wait time is required for power-on reset, wake-up from sub clock mode or stop mode.

Serial communication

There is a possibility to receive wrong data due to noise or other causes on the serial communication.

Therefore, design a printed circuit board so as to avoid noise.

Consider receiving of wrong data when designing the system. For example apply a checksum and retransmit the data if an error occurs.

## ■ PIN CONNECTION

• Treatment of Unused Input Pin

Leaving unused input pins unconnected can cause abnormal operation or latch-up, leaving to permanent damage. Unused input pins should always be pulled up or down through resistance of at least 2 k $\Omega$ . Any unused input/output pins may be set to output mode and left open, or set to input mode and treated the same as unused input pins. If there is unused output pin, make it to open.

• Treatment of Power Supply Pins on A/D Converter

Connect to be  $AV_{CC} = V_{CC}$  and  $AV_{SS} = AVR = V_{SS}$  even if the A/D converter is not in use.

Noise riding on the AV<sub>CC</sub> pin may cause accuracy degradation. So, connect approx. 0.1  $\mu$ F ceramic capacitor as a bypass capacitor between AV<sub>CC</sub> and AV<sub>ss</sub> pins in the vicinity of this device.

## PROGRAMMING FLASH MEMORY MICROCONTROLLERS USING PARALLEL PROGRAMMER

## • Supported Parallel Programmers and Adapters

The following table lists supported parallel programmers and adapters.

| Package     | Applicable adapter model | Parallel programmers                                                |

|-------------|--------------------------|---------------------------------------------------------------------|

| FPT-64P-M24 | TEF110-108F35AP          | AF9708 (Ver 02.35G or more)<br>AF9709/B (Ver 02.35G or more)        |

| FPT-64P-M23 | TEF110-108F36AP          | AF9709/B (Ver 02.33G of more)<br>AF9723+AF9834 (Ver 02.08E or more) |

Note : For information on applicable adapter models and parallel programmers, contact the following: Flash Support Group, Inc. TEL: +81-53-428-8380

Sector Configuration

The individual sectors of Flash memory correspond to addresses used for CPU access and programming by the parallel programmer as follows:

| Flash memory    | CPU address    | Programmer address*                              |            |

|-----------------|----------------|--------------------------------------------------|------------|

| SA1 (4 Kbytes)  | 1000н          | 71000н                                           |            |

|                 | 1FFFH          | 71FFFн                                           | ¥          |

| SA2 (4 Kbytes)  | <u>2000</u> н  | 72000н                                           | Lower bank |

|                 | 2FFFн          | 72FFFн                                           | MAC .      |

| SA3 (4 Kbytes)  | <u>3000</u> н  | — — — <del>73</del> 000н — — –                   |            |

|                 | 3FFFH          | 73FFF⊦                                           |            |

| SA4 (16 Kbytes) | 4000н          | <b>74000</b> H                                   |            |

|                 | 7 <u>F</u> FFH | 77FFFH                                           |            |

| SA5 (16 Kbytes) | 8000H          | 78000H                                           |            |

|                 | BFFFH          | 7BFFFн                                           |            |

| SA6 (4 Kbytes)  | С000н          | — — — 7С000н — — — — — — — — — — — — — — — — — — | × u        |

|                 | CFF <u>F</u> + | 7 <u>CFFF+_</u>                                  | psq _      |

| SA7 (4 Kbytes)  | <b>D</b> 000н  | 7D000н                                           | Upper bank |

|                 | DFFFH          | 7 <u>DFFF</u> +                                  |            |

| SA8 (4 Kbytes)  | E000H          | 7E000H                                           |            |

|                 | EFF <u>F</u> + | 7 <u>EFFF</u> +                                  |            |

| SA9 (4 Kbytes)  | F000H          | 7F000 <sub>H</sub>                               |            |

|                 | F <u>FF</u> H  | 7 <u>FFFFH</u>                                   |            |

These programmer addresses are used for the parallel programmer to program or erase data in Flash memory.

• Programming Method

- 1) Set the type code of the parallel programmer to "17222".

- 2) Load program data to programmer addresses 71000<sub>H</sub> to 7FFFF<sub>H</sub>.

- 3) Programmed by parallel programmer

|                             | Flash     | RAM       | Address #1        | Address #2        |

|-----------------------------|-----------|-----------|-------------------|-------------------|

| MB95F104AMS/F104ANS/F104AJS | 16 Kbytes | 512 bytes | 0280 <sub>H</sub> | С000н             |

| MB95F104AMW/F104ANW/F104AJW | TO Royles | JTZ byles | 0200H             | COOOH             |

| MB95F106AMS/F106ANS/F106AJS | 32 Kbytes | 1 Kbyte   | 0480 <sub>H</sub> | 8000 <sub>H</sub> |

| MB95F106AMW/F106ANW/F106AJW | 32 NUYLES | T Kbyle   | 0400H             | 8000H             |

| MB95F108AMS/F108ANS/F108AJS | 60 Kbytes | 2 Kbytes  | 0880 <sub>H</sub> | 1000н             |

| MB95F108AMW/F108ANW/F108AJW | ou Ruyles | 2 Royles  | 0000H             | ТОООН             |

The RP indicates the address of the register bank currently being used. The relationship between the content of RP and the real address conforms to the conversion rule illustrated below:

| Rule for Conversion of | Actua | al Ad | dress | ses ir | n the | Gen | eral- | purp | ose F | Regis    | ster A | rea |               |   |       |   |

|------------------------|-------|-------|-------|--------|-------|-----|-------|------|-------|----------|--------|-----|---------------|---|-------|---|

|                        |       |       |       |        |       |     |       |      |       | RP upper |        |     | OP code lower |   | lower |   |

|                        | ŧ     | ¥     | ¥     | ŧ      | ¥     | ¥   | ¥     | ¥    | +     | ¥        | +      | ¥   | +             | + | +     | + |

| Generated address      |       |       |       |        |       |     |       |      |       |          |        |     |               |   |       |   |

The DP specifies the area for mapping instructions (16 different instructions such as MOV A, dir) using direct addresses to 0080<sup> H</sup> to 00FF<sup> H</sup>.

| Direct bank pointer (DP2 to DP0)        | Specified address area | Mapping area                     |

|-----------------------------------------|------------------------|----------------------------------|

| XXX <sub>B</sub> (no effect to mapping) | 0000н to 007Fн         | 0000н to 007Fн (without mapping) |

| 000₀ (initial value)                    |                        | 0080н to 00FFн (without mapping) |

| 001в                                    |                        | 0100н to 017Fн                   |

| 010в                                    |                        | 0180н to 01FFн                   |

| 011в                                    | 0080н to 00FFн         | 0200н to 027Fн                   |

| 100в                                    |                        | 0280н to 02FFн                   |

| 101в                                    |                        | 0300н to 037Fн                   |

| 110в                                    |                        | 0380н to 03FFн                   |

| 111в                                    |                        | 0400н to 047Fн                   |

The CCR consists of the bits indicating arithmetic operation results or transfer data contents and the bits that control CPU operations at interrupt.

- H flag : Set to "1" when a carry or a borrow from bit 3 to bit 4 occurs as a result of an arithmetic operation. Cleared to "0" otherwise. This flag is for decimal adjustment instructions.

- I flag : Interrupt is enabled when this flag is set to "1". Interrupt is disabled when this flag is set to "0". The flag is set to "0" when reset.

- IL1, IL0 : Indicates the level of the interrupt currently enabled. Processes an interrupt only if its request level is higher than the value indicated by this bit.

| IL1 | ILO | Interrupt level | Priority              |

|-----|-----|-----------------|-----------------------|

| 0   | 0   | 0               | High                  |

| 0   | 1   | 1               | <b>≜</b>              |

| 1   | 0   | 2               | ļ                     |

| 1   | 1   | 3               | Low = no interruption |

- N flag : Set to "1" if the MSB is set to "1" as the result of an arithmetic operation. Cleared to "0" when the bit is set to "0".

- Z flag : Set to "1" when an arithmetic operation results in "0". Cleared to "0" otherwise.

- V flag : Set to "1" if the complement on 2 overflows as a result of an arithmetic operation. Cleared to "0" otherwise.

- C flag : Set to "1" when a carry or a borrow from bit 7 occurs as a result of an arithmetic operation. Cleared to "0" otherwise. Set to the shift-out value in the case of a shift instruction.

# MB95100AM Series

| Address         | Register<br>abbreviation | Register name                                                 | R/W | Initial value |

|-----------------|--------------------------|---------------------------------------------------------------|-----|---------------|

| 002Вн           | DDRG                     | Port G direction register                                     | R/W | 0000000в      |

| 002Сн           |                          | (Disabled)                                                    |     |               |

| 002Dн           | PUL1                     | Port 1 pull-up register                                       | R/W | 0000000B      |

| 002Eн           | PUL2                     | Port 2 pull-up register                                       | R/W | 0000000E      |

| 002Fн           | PUL3                     | Port 3 pull-up register                                       | R/W | 0000000e      |

| 0030н           | PUL4                     | Port 4 pull-up register                                       | R/W | 0000000e      |

| <b>0031</b> н   | PUL5                     | Port 5 pull-up register                                       | R/W | 0000000e      |

| 0032н           | PUL7                     | Port 7 pull-up register                                       | R/W | 0000000E      |

| 0033н           |                          | (Disabled)                                                    |     | _             |

| 0034н           | PULE                     | Port E pull-up register                                       | R/W | 0000000e      |

| 0035н           | PULG                     | Port G pull-up register                                       | R/W | 0000000e      |

| 0036н           | T01CR1                   | 8/16-bit compound timer 01 control status register 1 ch.0     | R/W | 0000000e      |

| 0037н           | T00CR1                   | 8/16-bit compound timer 00 control status register 1 ch.0     | R/W | 0000000       |

| 0038н           | T11CR1                   | 8/16-bit compound timer 11 control status register 1 ch.1     | R/W | 0000000e      |

| 0039н           | T10CR1                   | 8/16-bit compound timer 10 control status register 1 ch.1     | R/W | 0000000       |

| 003Ан           | PC01                     | 8/16-bit PPG1 control register ch.0                           | R/W | 0000000       |

| 003Вн           | PC00                     | 8/16-bit PPG0 control register ch.0                           | R/W | 0000000       |

| 003Сн           | PC11                     | 8/16-bit PPG1 control register ch.1                           | R/W | 0000000e      |

| 003Dн           | PC10                     | 8/16-bit PPG0 control register ch.1                           | R/W | 0000000e      |

| 003Ен           | TMCSRH0                  | 16-bit reload timer control status register (Upper byte) ch.0 | R/W | 0000000       |

| 003Fн           | TMCSRL0                  | 16-bit reload timer control status register (Lower byte) ch.0 | R/W | 0000000e      |

| 0040н,<br>0041н |                          | (Disabled)                                                    | _   | _             |

| 0042н           | PCNTH0                   | 16-bit PPG status control register (Upper byte) ch.0          | R/W | 0000000e      |

| 0043н           | PCNTL0                   | 16-bit PPG status control register (Lower byte) ch.0          | R/W | 0000000e      |

| 0044н           | PCNTH1                   | 16-bit PPG status control register (Upper byte) ch.1          | R/W | 0000000e      |

| <b>0045</b> н   | PCNTL1                   | 16-bit PPG status control register (Lower byte) ch.1          | R/W | 0000000       |

| 0046н,<br>0047н |                          | (Disabled)                                                    |     | _             |

| <b>0048</b> н   | EIC00                    | External interrupt circuit control register ch.0/ch.1         | R/W | 0000000       |

| 0049н           | EIC10                    | External interrupt circuit control register ch.2/ch.3         | R/W | 0000000       |

| 004Ан           | EIC20                    | External interrupt circuit control register ch.4/ch.5         | R/W | 0000000       |

| 004Bн           | EIC30                    | External interrupt circuit control register ch.6/ch.7         | R/W | 0000000       |

| 004Cн           | EIC01                    | External interrupt circuit control register ch.8/ch.9         | R/W | 0000000       |

| 004Dн           | EIC11                    | External interrupt circuit control register ch.10/ch.11       | R/W | 0000000e      |

(Continued)

## MB95100AM Series

(Continued)

|                                          |      | (\                                               | $/cc = AVcc = 5.0 V \pm 10\%$                                                                     | , AVss = | = Vss = ( | 0.0 V, Ta | = -4 | $0 \circ C$ to $+ 85 \circ C$ )               |

|------------------------------------------|------|--------------------------------------------------|---------------------------------------------------------------------------------------------------|----------|-----------|-----------|------|-----------------------------------------------|

| Parameter                                | Sym- | Pin name                                         | Conditions                                                                                        |          | Value     |           | Unit | Remarks                                       |

| Falameter                                | bol  | Finname                                          | Conditions                                                                                        | Min      | Тур       | Typ Max   |      | Remarks                                       |

| Power<br>supply<br>current <sup>*4</sup> | Істѕ | V <sub>cc</sub><br>(External clock<br>operation) | $V_{CC} = 5.5 V$<br>$F_{CH} = 10 MHz$<br>Timebase timer mode<br>$T_A = +25 °C$                    |          | 0.15      | 1.10      | mA   |                                               |

|                                          | Іссн |                                                  | $V_{CC} = 5.5 V$<br>Sub stop mode<br>$T_A = +25 \text{ °C}$                                       | _        | 3.5       | 20        | μΑ   | Main stop<br>mode for single<br>clock product |

|                                          | Ilvd | Vcc                                              | Current consumption for<br>low voltage detection<br>circuit only                                  |          | 38        | 50        | μA   |                                               |

|                                          | Icsv |                                                  | At oscillating 100 kHz<br>current consumption of<br>internal CR oscillator                        |          | 20        | 36        | μΑ   |                                               |

|                                          | IA   | AVcc                                             | $V_{CC} = 5.5 V$<br>$F_{CH} = 16 MHz$<br>At operating of A/D<br>conversion                        | _        | 2.4       | 4.7       | mA   |                                               |

|                                          | Іан  |                                                  | $V_{CC} = 5.5 V$<br>$F_{CH} = 16 MHz$<br>At stopping A/D<br>conversion<br>$T_A = +25 \ ^{\circ}C$ |          | 1         | 5         | μΑ   |                                               |

\*1: P10, P50, P51, and P67 can switch the input level to either the "CMOS input level" or "hysteresis input level". The switching of the input level can be set by the input level selection register (ILSR).

- \*2: Single clock products only

- \*3 : Product without clock supervisor only

- \*4: The power-supply current is determined by the external clock. When the low voltage detection option is selected, the power-supply current will be a value of adding current consumption of the low voltage detection circuit (ILVD) to the specified value. Also, when both low voltage detection option and clock supervisor are selected, the power-supply current will be a value of adding current consumption of the low voltage detection circuit (ILVD) and current consumption of internal CR oscillator (ICSV) to the specified value.

FUĬĪTSU

- Refer to "4. AC Characteristics (1) Clock Timing" for FCH and FCL.

- Refer to "4. AC Characteristics (2) Source Clock/Machine Clock" for FMP and FMPL.

- - · · -

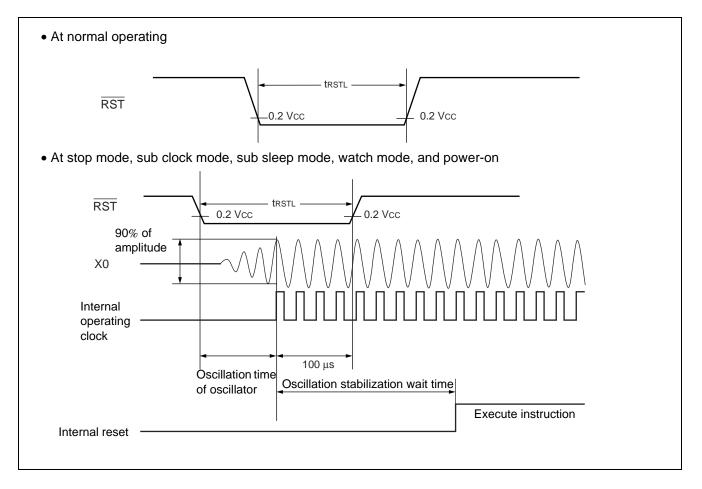

### (3) External Reset

|               | $(Vcc = 5.0 V \pm 10\%, AVss = Vss = 0.0 V, T_A = -40 \text{ °C to } +85$ |                                           |     |      |                                                                 |  |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------|-------------------------------------------|-----|------|-----------------------------------------------------------------|--|--|--|--|--|--|--|

| Parameter     | Symbol                                                                    | Value                                     |     |      | Remarks                                                         |  |  |  |  |  |  |  |

| Falameter     | Symbol                                                                    | Min                                       | Max | Unit | Remarks                                                         |  |  |  |  |  |  |  |

| RST "L" level |                                                                           | 2 tMcLK*1 —                               |     | ns   | At normal operating                                             |  |  |  |  |  |  |  |

| pulse width   | <b>t</b> rstl                                                             | Oscillation time of oscillator*2<br>+ 100 | _   | μs   | At stop mode, sub clock mode,<br>sub sleep mode, and watch mode |  |  |  |  |  |  |  |

|               |                                                                           | 100                                       |     | μs   | At timebase timer mode                                          |  |  |  |  |  |  |  |

\*1 : Refer to " (2) Source Clock/Machine Clock" for tmclk.

\*2 : Oscillation time of oscillator is the time that the amplitude reaches 90 %. In the crystal oscillator, the oscillation time is between several ms and tens of ms. In ceramic oscillators, the oscillation time is between hundreds of μs and several ms. In the external clock, the oscillation time is 0 ms.

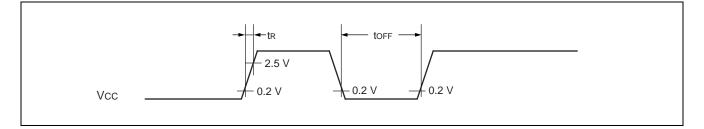

### (4) Power-on Reset

| $(AVss = Vss = 0.0 V, T_A = -40 \circ C to +85$ |        |            |     |     |      |                    |  |  |  |  |

|-------------------------------------------------|--------|------------|-----|-----|------|--------------------|--|--|--|--|

| Parameter                                       | Symbol | Conditions | Va  | lue | Unit | Pomarks            |  |  |  |  |

| Farameter                                       | Symbol | Conditions | Min | Max | Unit |                    |  |  |  |  |

| Power supply rising time                        | tr     | —          | —   | 50  | ms   |                    |  |  |  |  |

| Power supply cutoff time                        | toff   |            | 1   |     | ms   | Waiting time until |  |  |  |  |

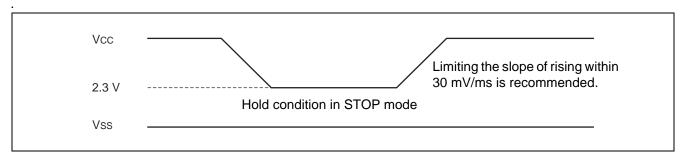

Note : Sudden change of power supply voltage may activate the power-on reset function. When changing power supply voltages during operation, set the slope of rising within 30 mV/ms as shown below

power-on

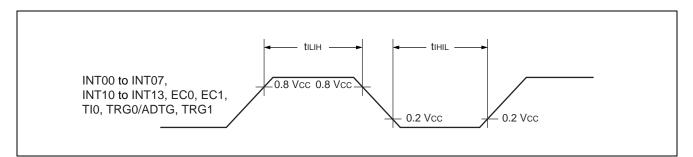

(5) Peripheral Input Timing

### (Vcc = 5.0 V $\pm$ 10%, AVss = Vss = 0.0 V, T<sub>A</sub> = -40 °C to +85 °C)

| Parameter                        | Symbol | Pin name                           | Va               | Unit |      |  |

|----------------------------------|--------|------------------------------------|------------------|------|------|--|

| Falanielei                       |        |                                    | Min              | Max  | Unit |  |

| Peripheral input "H" pulse width | tılıн  | INT00 to INT07,<br>INT10 to INT13, | 2 <b>t</b> MCLK* | —    | ns   |  |

| Peripheral input "L" pulse width | tını∟  | EC0, EC1, TI0, TRG0/ADTG,<br>TRG1  | <b>2 t</b> мськ* | _    | ns   |  |

\* : Refer to " (2) Source Clock/Machine Clock" for tmclk.

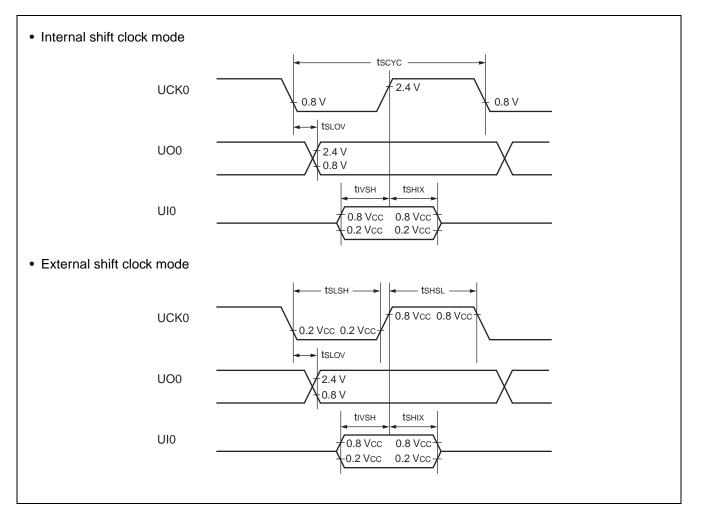

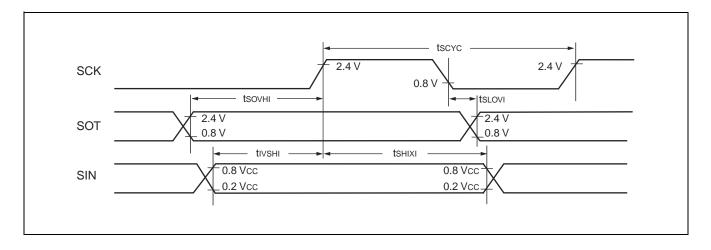

## (6) UART/SIO, Serial I/O Timing

| $(Vcc = 5.0 V \pm 10\%, AVss = Vss = 0.0 V, T_A = -40 °C to + 8$ |               |           |                   |                  |       |      |  |

|------------------------------------------------------------------|---------------|-----------|-------------------|------------------|-------|------|--|

| Parameter                                                        | Symbol        | Pin name  | Conditions        | Val              | Unit  |      |  |

| i didificici                                                     | Symbol        | Tinname   | Conditions        | Min              | Max   | Onit |  |

| Serial clock cycle time                                          | tscyc         | UCK0      |                   | <b>4 t</b> мськ* | —     | ns   |  |

| UCK $\downarrow \rightarrow$ UO time                             | <b>t</b> slov | UCK0, UO0 | Internal<br>clock | - 190            | + 190 | ns   |  |

| $Valid\;UI\toUCK\;\uparrow$                                      | tıvsн         | UCK0, UI0 | operation         | 2 <b>t</b> мськ* | —     | ns   |  |

| UCK $\uparrow \rightarrow$ valid UI hold time                    | tsнıx         | UCK0, UI0 |                   | 2 <b>t</b> мськ* | _     | ns   |  |

| Serial clock "H" pulse width                                     | <b>t</b> s∺s∟ | UCK0      |                   | 4 <b>t</b> MCLK* | _     | ns   |  |

| Serial clock "L" pulse width                                     | tslsн         | UCK0      | External          | <b>4 t</b> мськ* |       | ns   |  |

| UCK $\downarrow \rightarrow$ UO time                             | <b>t</b> slov | UCK0, UO0 | clock             | _                | 190   | ns   |  |

| $Valid\;UI\toUCK\;\uparrow$                                      | <b>t</b> ivsh | UCK0, UI0 | operation         | 2 <b>t</b> MCLK* | _     | ns   |  |

| UCK $\uparrow \rightarrow$ valid UI hold time                    | tsнıx         | UCK0, UI0 |                   | 2 <b>t</b> MCLK* |       | ns   |  |

\* : Refer to " (2) Source Clock/Machine Clock" for tmclk.

# MB95100AM Series

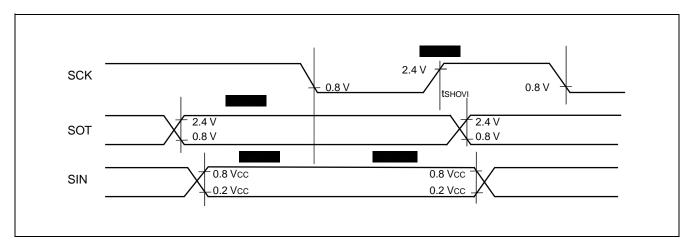

Sampling at the rising edge of sampling clock  $^{\ast_1}$  and enabled serial clock delay  $^{\ast_2}$

(ESCR register : SCES bit = 0, ECCR register : SCDE bit = 1) (Vcc =  $5.0 \text{ V} \pm 10\%$ , AVss = Vss = 0.0 V, T<sub>A</sub> = -40 °C to + 85 °C)

| Parameter                                      | Sym-<br>bol    | Pin name | Conditions             | Valu                          | Unit              |      |

|------------------------------------------------|----------------|----------|------------------------|-------------------------------|-------------------|------|

| Faidilielei                                    |                |          | Conditions             | Min                           | Max               | Onit |

| Serial clock cycle time                        | tscyc          | SCK      |                        | 5 <b>t</b> MCLK* <sup>3</sup> |                   | ns   |

| $SCK \uparrow \to SOT \text{ delay time}$      | <b>t</b> shovi | SCK, SOT | Internal clock         | - 95                          | + 95              | ns   |

| $Valid\ SIN \to SCK \downarrow$                | tivsli         | SCK, SIN | operation output pin : | tмськ*3 + 190                 | _                 | ns   |

| $SCK \downarrow \to valid \ SIN \ hold \ time$ | tslixi         | SCK, SIN | C∟ = 80 pF + 1 TTL.    | 0                             |                   | ns   |

| $SOT \to SCK \downarrow delay  time$           | tsovli         | SCK, SOT |                        |                               | 4 <b>t</b> MCLK*3 | ns   |

\*1 : Provide switch function whether sampling of reception data is performed at rising edge or falling edge of the serial clock.

\*2 : Serial clock delay function is used to delay half clock for the output signal of serial clock.

\*3 : Refer to " (2) Source Clock/Machine Clock" for tmclk.

Sampling at the falling edge of sampling clock <sup>\*1</sup> and enabled serial clock delay <sup>\*2</sup>

(ESCR register : SCES bit = 1, ECCR register : SCDE bit = 1) (Vcc =  $5.0 \text{ V} \pm 10\%$ , AVss = Vss = 0.0 V, T<sub>A</sub> = -40 °C to + 85 °C)

| Parameter                                      | Sym-           | Pin name | Conditions             | Valu                          | Unit              |      |  |

|------------------------------------------------|----------------|----------|------------------------|-------------------------------|-------------------|------|--|

| Falameter                                      | bol            | Finname  | Conditions             | Min                           | Max               | Onit |  |

| Serial clock cycle time                        | <b>t</b> scyc  | SCK      |                        | <b>5 t</b> мськ* <sup>3</sup> | _                 | ns   |  |

| $SCK \downarrow \to SOT \text{ delay time}$    | <b>t</b> slovi | SCK, SOT | Internal clock         | - 95                          | + 95              | ns   |  |

| Valid SIN $ ightarrow$ SCK $\uparrow$          | <b>t</b> ivshi | SCK, SIN | operating output pin : | tмськ*3 + 190                 | _                 | ns   |  |

| SCK $\uparrow \rightarrow$ valid SIN hold time | <b>t</b> shixi | SCK, SIN | C∟ = 80 pF + 1 TTL.    | 0                             |                   | ns   |  |

| $SOT \to SCK \uparrow delay  time$             | <b>t</b> sovнi | SCK, SOT |                        |                               | 4 <b>t</b> MCLK*3 | ns   |  |

\*1 : Provide switch function whether sampling of reception data is performed at rising edge or falling edge of the serial clock.

\*2 : Serial clock delay function is used to delay half clock for the output signal of serial clock.

\*3 : Refer to " (2) Source Clock/Machine Clock" for tmclk.

(Continued)

$(Vcc = 5.0 V \pm 10\%, AVss = Vss = 0.0 V, T_A = -40 \circ C to + 85 \circ C)$

|                                    |                 |              |                                                                                     |                                                          |     |         | · · · · · · · · · · · · · · · · · · · |

|------------------------------------|-----------------|--------------|-------------------------------------------------------------------------------------|----------------------------------------------------------|-----|---------|---------------------------------------|

| Parameter                          | Sym- Pin        | Condition    | Value*2                                                                             |                                                          |     | Remarks |                                       |

| Farameter                          | bol             | name         | Condition                                                                           | Min                                                      | Max | Unit    | Remarks                               |

| Data hold time                     | <b>t</b> hd;dat | SCL0<br>SDA0 | $\label{eq:R} \begin{split} &R = 1.7 \; k\Omega, \\ &C = 50 \; pF^{*1} \end{split}$ | 0                                                        |     | ns      | At reception                          |

| Data setup time                    | tsu;dat         | SCL0<br>SDA0 |                                                                                     | tмськ – 20                                               |     | ns      | At reception                          |

| SDA↓→SCL↑<br>(at wake-up function) | <b>t</b> wakeup | SCL0<br>SDA0 |                                                                                     | Oscillation stabilization<br>wait time<br>+ 2 tMCLK - 20 |     | ns      |                                       |

\*1 : R, C : Pull-up resistor and load capacitor of the SCL and SDA lines.

- m is CS4 bit and CS3 bit (bit 4 and bit 3) of clock control register (ICCR0) .

- n is CS2 bit to CS0 bit (bit 2 to bit 0) of clock control register (ICCR0).

- Actual timing of I<sup>2</sup>C is determined by m and n values set by the machine clock (t<sub>MCLK</sub>) and CS4 to CS0 of ICCR0 register.

- Standard-mode :

m and n can be set at the range :  $0.9 \text{ MHz} < t_{MCLK}$  (machine clock) < 10 MHz. Setting of m and n limits the machine clock that can be used below.

• Fast-mode :

m and n can be set at the range : 3.3 MHz <  $t_{MCLK}$  (machine clock) < 10 MHz.

Setting of m and n limits the machine clock that can be used below. (m, n) = (1, 8) : 3.3 MHz < t<sub>MCLK</sub>  $\leq$  4 MHz

$\begin{array}{ll} (m,\,n) \;=\; (1,\,22)\;,\; (5,\,4)\;: 3.3\;MHz < t_{\text{MCLK}} \leq 8\;MHz \\ (m,\,n) \;=\; (6,\,4) & : 3.3\;MHz < t_{\text{MCLK}} \leq 10\;MHz \end{array}$

<sup>\*2 : •</sup> Refer to " (2) Source Clock/Machine Clock" for tMCLK.

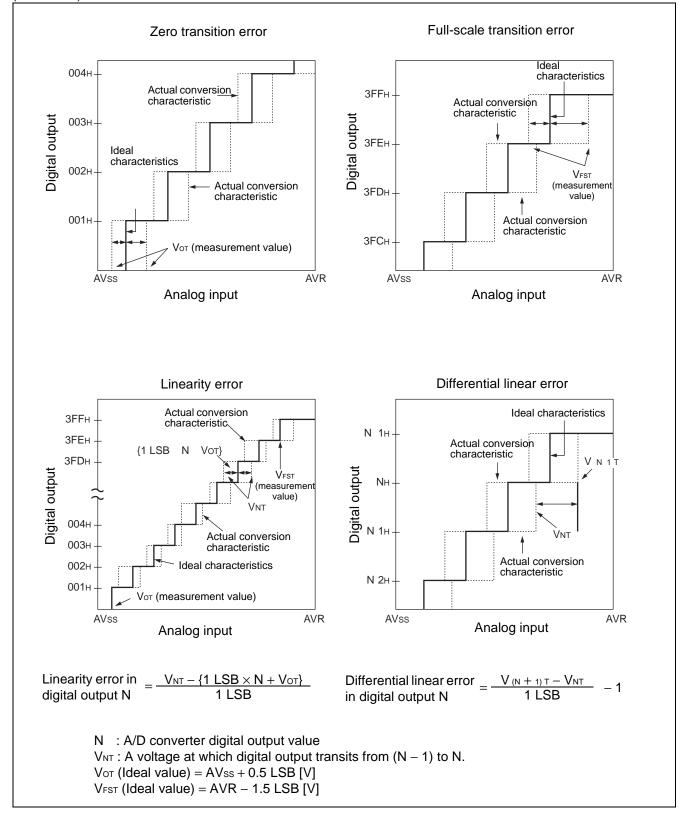

## 5. A/D Converter

## (1)

| _                                | Symbol |                   | Value             | 1                 |        |                                                                                                                                          |

|----------------------------------|--------|-------------------|-------------------|-------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                        |        | Min               | Тур               | Max               | – Unit | Remarks                                                                                                                                  |

| Resolution                       |        |                   |                   | 10                | bit    |                                                                                                                                          |

| Total error                      | -      | - 3.0             |                   | + 3.0             | LSB    |                                                                                                                                          |

| Linearity error                  |        | - 2.5             |                   | + 2.5             | LSB    |                                                                                                                                          |

| Differential linear error        |        | – 1.9             |                   | + 1.9             | LSB    |                                                                                                                                          |

| Zero transition voltage          | Vот    | AVss –<br>1.5 LSB | AVss +<br>0.5 LSB | AVss +<br>2.5 LSB | V      |                                                                                                                                          |

| Full-scale transition voltage    | Vfst   | AVR –<br>3.5 LSB  | AVR –<br>1.5 LSB  | AVR +<br>0.5 LSB  | V      |                                                                                                                                          |

| Compare time                     |        | 0.9               |                   | 16500             | μs     | $4.5 \text{ V} \le \text{AVcc} \le 5.5 \text{ V}$                                                                                        |

|                                  |        | 1.8               |                   | 16500             | μs     | $4.0 \text{ V} \le \text{AVcc} < 4.5 \text{ V}$                                                                                          |

| Sampling time                    |        | 0.6               | _                 | œ                 | μs     | $\begin{array}{l} \text{4.5 V} \leq \text{AVcc} \leq 5.5 \text{ V},\\ \text{At external impedance} < \\ \text{5.4 k} \Omega \end{array}$ |

|                                  |        | 1.2               |                   | ~                 | μs     | $4.0 V \le AVcc < 4.5 V$ ,<br>At external impedance <<br>$2.4 k\Omega$                                                                   |

| Analog input current             | Iain   | - 0.3             |                   | + 0.3             | μA     |                                                                                                                                          |

| Analog input voltage             | VAIN   | AVss              |                   | AVR               | V      |                                                                                                                                          |

| Reference voltage                |        | AVss + 4.0        |                   | AVcc              | V      | AVR pin                                                                                                                                  |

| Reference voltage supply current | IR     |                   | 600               | 900               | μA     | AVR pin,<br>During A/D operation                                                                                                         |

|                                  | Ігн    |                   |                   | 5                 | μA     | AVR pin,<br>At stop mode                                                                                                                 |

#### (Continued)

## ■ MASK OPTION

| No. | Part number                                                                                                          | MB95108AM                                                                             | MB95F104AMS<br>MB95F104ANS<br>MB95F104AJS<br>MB95F106AMS<br>MB95F106AJS<br>MB95F108AMS<br>MB95F108ANS<br>MB95F108ANS<br>MB95F108AJS | MB95F104AMW<br>MB95F104ANW<br>MB95F104AJW<br>MB95F106AMW<br>MB95F106ANW<br>MB95F106AJW<br>MB95F108AMW<br>MB95F108ANW<br>MB95F108AJW | MB95FV100D-103                                                                                                                                                          |

|-----|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Specifying procedure                                                                                                 | Specify when<br>ordering<br>MASK                                                      | ordering                                                                                                                            |                                                                                                                                     | Setting<br>disabled                                                                                                                                                     |

| 1   | Clock mode select<br>• Single-system clock mode<br>• Dual-system clock mode                                          | Selectable                                                                            | Single-system<br>clock mode                                                                                                         | Dual-system<br>clock mode                                                                                                           | Changing by the switch on MCU board                                                                                                                                     |

| 2   | Low voltage detection<br>reset*<br>• With low voltage detection<br>reset<br>• Without low voltage<br>detection reset | Specify when ordering MASK                                                            | Specified by part number                                                                                                            | Specified by part number                                                                                                            | Changing by the switch on MCU board                                                                                                                                     |

| 3   | Clock supervisor*<br>• With clock supervisor<br>• Without clock supervisor                                           | Specify when ordering MASK                                                            | Specified by part number                                                                                                            | Specified by part number                                                                                                            | Changing by the switch on MCU board                                                                                                                                     |

| 4   | Reset output*<br>• With reset output<br>• Without reset output                                                       | Specify when<br>ordering MASK                                                         | Specified by part number                                                                                                            | Specified by part number                                                                                                            | <ul> <li>MCU board switch set<br/>as following ;</li> <li>With supervisor :<br/>Without reset<br/>output</li> <li>Without supervisor :<br/>With reset output</li> </ul> |

| 5   | Oscillation stabilization wait time                                                                                  | Fixed to<br>oscillation<br>stabilization wait<br>time of<br>(2 <sup>14</sup> -2) /FCH | Fixed to<br>oscillation<br>stabilization wait<br>time of<br>(2 <sup>14</sup> -2) /F <sub>CH</sub>                                   | Fixed to<br>oscillation<br>stabilization wait<br>time of<br>(2 <sup>14</sup> -2) /F <sub>CH</sub>                                   | Fixed to<br>oscillation<br>stabilization wait<br>time of<br>(2 <sup>14</sup> -2) /Fсн                                                                                   |

\*: Refer to table below about clock mode select, low voltage detection reset, clock supervisor select and reset output.

(Continued)

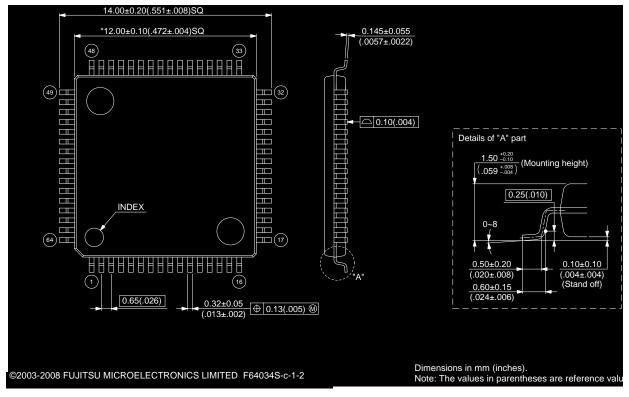

Please confirm the latest Package dimension by following URL. http://edevice.fujitsu.com/package/en-search/