Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 8051                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 24MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                          |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 12KB (12K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 2K x 8                                                                   |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89s8253-24ju |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.3 44J – 44-lead PLCC

| (MOSI) P1.5 1 0<br>(MISO) P1.6 8<br>(SCK) R5T 1 0<br>(RXD) P3.1 13<br>(INTI) P3.3 15<br>(TO) P3.4 17<br>(T1) P3.5 15<br>(T0) P3.4 17<br>(T1) P3.5 16<br>(HW) | 0        | ((V) (V) (V) (V) (V) (V) (V) (V) (V) (V) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------|

|                                                                                                                                                              |          |                                          |

| RST 🗆                                                                                                                                                        | 1        | 42 🗆 P1.7 (SCK)                          |

| (RXD) P3.0 [                                                                                                                                                 | 2        | 41 D P1.6 (MISO)                         |

| (TXD) P3.1                                                                                                                                                   | 3        | 40 D P1.5 (MOSI)                         |

| (INT0) P3.2                                                                                                                                                  | 4        | 39 🗆 P1.4 (SS)                           |

| (INT1) P3.3 [                                                                                                                                                | 5        | 38 🗆 P1.3                                |

| (T0) P3.4 🗆                                                                                                                                                  | 6        | 37 🗆 P1.2                                |

| (T1) P3.5 🗆                                                                                                                                                  | 7        | 36 🗆 P1.1 (T2EX)                         |

| (WR) P3.6 🗆                                                                                                                                                  | 8        | 35 🗆 P1.0 (T2)                           |

| (RD) P3.7 🗆                                                                                                                                                  | 9        | 34 🗆 VDD                                 |

| XTAL2                                                                                                                                                        | 10       | 33 🗆 PWRVDD                              |

| XTAL1 🗆                                                                                                                                                      | 11       | 32 🗆 P0.0 (AD0)                          |

| GND 🗆                                                                                                                                                        | 12       | 31 🛛 P0.1 (AD1)                          |

| PWRGND                                                                                                                                                       | 13       | 30 🗌 P0.2 (AD2)                          |

| (A8) P2.0 🗆                                                                                                                                                  | 14       | 29 🗆 P0.3 (AD3)                          |

| (A9) P2.1                                                                                                                                                    | 15       | 28 P0.4 (AD4)                            |

| (A10) P2.2                                                                                                                                                   | 16       | 27 	P0.5 (AD5)                           |

| (A11) P2.3 □<br>(A12) P2.4 □                                                                                                                                 | 17<br>18 | 26 🗆 P0.6 (AD6)<br>25 🗋 P0.7 (AD7)       |

| (A12) P2.4 (A13) P2.5 (A13) P2.5                                                                                                                             | 10       | 25 🗆 P0.7 (AD7)<br>24 🗆 EA/VPP           |

| (A13) P2.5 (A14) P2.6 (A14)                                                                                                                                  | 20       | 24 DEAVER<br>23 DALE/PROG                |

| (A14) P2.0 L                                                                                                                                                 | 20       |                                          |

| (,                                                                                                                                                           |          |                                          |

Ŷ

### 2.4 42PS6 – PDIP

## 3. Pin Description

3.1 VCC

Supply voltage (all packages except 42-PDIP).

3.2 GND

Ground (all packages except 42-PDIP; for 42-PDIP GND connects only the logic core and the embedded program/data memories).

3.3 VDD

Supply voltage for the 42-PDIP which connects only the logic core and the embedded program/data memories.

#### 3.4 PWRVDD

Supply voltage for the 42-PDIP which connects only the I/O Pad Drivers. The application board **must** connect both VDD and PWRVDD to the board supply voltage.

## 3.13 EA/VPP

External Access Enable.  $\overline{EA}$  must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed,  $\overline{EA}$  will be internally latched on reset.

$\overline{\text{EA}}$  should be strapped to V<sub>CC</sub> for internal program executions. This pin also receives the 12-volt programming enable voltage (V<sub>PP</sub>) during Flash programming when 12-volt programming is selected.

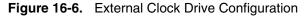

#### 3.14 XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

#### 3.15 XTAL2

Output from the inverting oscillator amplifier. XTAL2 should not drive a board-level clock without a buffer.

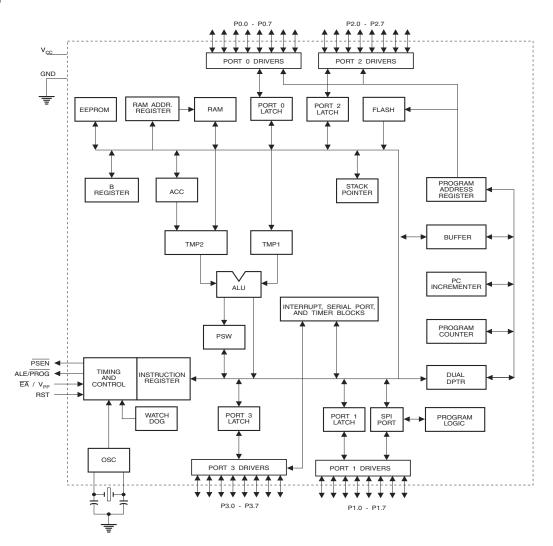

## 4. Block Diagram

# AT89S8253

## 5. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in Table 5-1.

Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will generally return random data, and write accesses will have an indeterminate effect.

User software should not write 1s to these unlisted locations, since they may be used in future products to invoke new features. In that case, the reset or inactive values of the new bits will always be 0.

Table 5-1.

AT89S8253 SFR Map and Reset Values

|       |                   |                   | -                  |                    |                  |                  |                        |                     | -    |

|-------|-------------------|-------------------|--------------------|--------------------|------------------|------------------|------------------------|---------------------|------|

| 0F8H  |                   |                   |                    |                    |                  |                  |                        |                     | 0FFH |

| 0F0H  | B<br>00000000     |                   |                    |                    |                  |                  |                        |                     | 0F7H |

| 0E8H  |                   |                   |                    |                    |                  |                  |                        |                     | 0EFH |

| 0E0H  | ACC<br>00000000   |                   |                    |                    |                  |                  |                        |                     | 0E7H |

| 0D8H  |                   |                   |                    |                    |                  |                  |                        |                     | 0DFH |

| 0D0H  | PSW<br>00000000   |                   |                    |                    |                  | SPCR<br>00000100 |                        |                     | 0D7H |

| 0C8H  | T2CON<br>00000000 | T2MOD<br>XXXXXX00 | RCAP2L<br>00000000 | RCAP2H<br>00000000 | TL2<br>00000000  | TH2<br>00000000  |                        |                     | 0CFH |

| 0C0H  |                   |                   |                    |                    |                  |                  |                        |                     | 0C7H |

| 0B8H  | IP<br>XX000000    | SADEN<br>00000000 |                    |                    |                  |                  |                        |                     | 0BFH |

| 0B0H  | P3<br>11111111    |                   |                    |                    |                  |                  |                        | IPH<br>XX000000     | 0B7H |

| 0A8H  | IE<br>0X000000    | SADDR<br>00000000 | SPSR<br>000XXX00   |                    |                  |                  |                        |                     | 0AFH |

| 0A0H  | P2<br>11111111    |                   |                    |                    |                  |                  | WDTRST<br>(Write Only) | WDTCON<br>0000 0000 | 0A7H |

| 98H   | SCON<br>00000000  | SBUF<br>XXXXXXXX  |                    |                    |                  |                  |                        |                     | 9FH  |

| 90H   | P1<br>11111111    |                   |                    |                    |                  |                  | EECON<br>XX000011      |                     | 97H  |

| 88H   | TCON<br>00000000  | TMOD<br>00000000  | TL0<br>00000000    | TL1<br>00000000    | TH0<br>00000000  | TH1<br>00000000  | AUXR<br>XXXXXXX0       | CLKREG<br>XXXXXXX0  | 8FH  |

| 80H   | P0<br>11111111    | SP<br>00000111    | DP0L<br>00000000   | DP0H<br>00000000   | DP1L<br>00000000 | DP1H<br>00000000 | SPDR<br>########       | PCON<br>00XX0000    | 87H  |

| Note: | # means: 0 aft    | er cold reset and | d unchanged a      | fter warm rese     | et.              |                  |                        |                     | -    |

Note: # means: 0 after cold reset and unchanged after warm reset.

### 5.1 Auxiliary Register

#### Table 5-2.AUXR – Auxiliary Register

| AUXI   | R Address = 8 | BEH             |   |                   |                 |   | Reset Value = X                                     | XXX XXX0B |       |

|--------|---------------|-----------------|---|-------------------|-----------------|---|-----------------------------------------------------|-----------|-------|

| Not E  | Bit Addressab | le              |   |                   |                 |   |                                                     |           |       |

|        |               |                 |   |                   |                 |   | Intel Durd Evit                                     |           | 1     |

|        | _             | -               | - | -                 | _               | - | Intel_Pwd_Exit                                      | DISALE    |       |

| Bit    | 7             | 6               | 5 | 4                 | 3               | 2 | 1                                                   | 0         |       |

| Sym    | bol           | Function        |   |                   |                 |   |                                                     |           |       |

| Intel_ | _Pwd_Exit     | the interrupt s |   | nis bit is cleare | d, the executio |   | to resume execution of ter a self-timed intervation |           |       |

| DISA   | LE            |                 |   |                   |                 |   | or frequency (except de<br>MOVX or MOVC instru      |           | nen 1 |

#### 5.2 Clock Register

#### Table 5-3.CLKREG – Clock Register

| CLKRE     | G Address = | 8FH               |                  |                |                   |                  | Reset Value = >    | XXX XXX0B        |

|-----------|-------------|-------------------|------------------|----------------|-------------------|------------------|--------------------|------------------|

| Not Bit A | Addressable |                   |                  |                |                   |                  |                    |                  |

|           |             |                   |                  |                | _                 | _                | _                  | X2               |

| Bit       | 7           | 6                 | 5                | 4              | 3                 | 2                | 1                  | 0                |

| Symbol    | Functi      | on                |                  |                |                   |                  |                    |                  |

|           | When        | X2 = 0, the oscil | llator frequency | (at XTAL1 pin) | is internally div | rided by 2 befor | e it is used as tl | ne device system |

| X0 | When X2 = 0, the oscillator frequency (at XTAL1 pin) is internally divided by 2 before it is used as the device system frequency.                                                                                              |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X2 | When X2 = 1, the divider by 2 is no longer used and the XTAL1 frequency becomes the device system frequency. This enables the user to choose a 6 MHz crystal instead of a 12 MHz crystal, for example, in order to reduce EMI. |

#### 5.3 SPI Registers

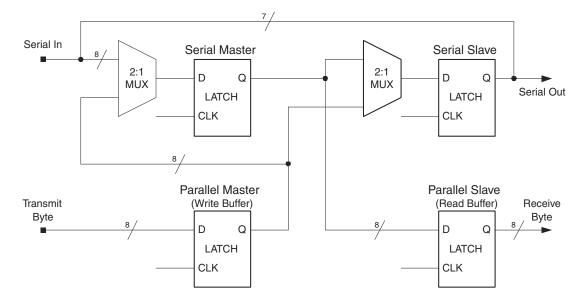

Control and status bits for the Serial Peripheral Interface are contained in registers SPCR (see Table 14-1 on page 25) and SPSR (see Table 14-2 on page 26). The SPI data bits are contained in the SPDR register. In normal SPI mode, writing the SPI data register during serial data transfer sets the Write Collision bit (WCOL) in the SPSR register. In enhanced SPI mode, the SPDR is also write double-buffered because WCOL works as a Write Buffer Full Flag instead of being a collision flag. The values in SPDR are not changed by Reset.

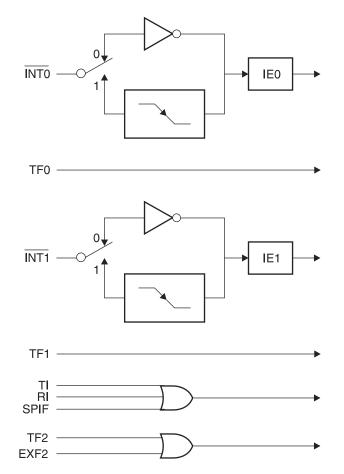

#### 5.4 Interrupt Registers

The global interrupt enable bit and the individual interrupt enable bits are in the IE register. In addition, the individual interrupt enable bit for the SPI is in the SPCR register. Four priorities can be set for each of the six interrupt sources in the IP and IPH registers.

IPH bits have the same functions as IP bits, except IPH has higher priority than IP. By using IPH in conjunction with IP, a priority level of 0, 1, 2, or 3 may be set for each interrupt.

## 8. Programmable Watchdog Timer

The programmable Watchdog Timer (WDT) counts instruction cycles. The prescaler bits, PS0, PS1 and PS2 in SFR WDTCON are used to set the period of the Watchdog Timer from 16K to 2048K instruction cycles. The available timer periods are shown in Table 8-1. The WDT time-out period is dependent upon the external clock frequency.

The WDT is disabled by Power-on Reset and during Power-down mode. When WDT times out without being serviced or disabled, an internal RST pulse is generated to reset the CPU. See Table 8-1 for the WDT period selections.

|     | WDT Prescaler Bits |     | Period (Nominal for        |

|-----|--------------------|-----|----------------------------|

| PS2 | PS1                | PS0 | $F_{CLK} = 12 \text{ MHz}$ |

| 0   | 0                  | 0   | 16 ms                      |

| 0   | 0                  | 1   | 32 ms                      |

| 0   | 1                  | 0   | 64 ms                      |

| 0   | 1                  | 1   | 128 ms                     |

| 1   | 0                  | 0   | 256 ms                     |

| 1   | 0                  | 1   | 512 ms                     |

| 1   | 1                  | 0   | 1024 ms                    |

| 1   | 1                  | 1   | 2048 ms                    |

Table 8-1.

Watchdog Timer Time-out Period Selection

### 9. Timer 0 and 1

Timer 0 and Timer 1 in the AT89S8253 operate the same way as Timer 0 and Timer 1 in the AT89S51 and AT89S52. For more detailed information on the Timer/Counter operation, please click on the document link below:

http://www.atmel.com/dyn/resources/prod\_documents/DOC4316.PDF

### 10. Timer 2

Timer 2 is a 16-bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit  $C/\overline{12}$  in the SFR T2CON (see Table 10-2 on page 15). Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator. The modes are selected by bits in T2CON, as shown in Table 10-2.

Timer 2 consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

In the Counter function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since two machine cycles (24 oscillator periods) are required to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. To ensure that a given level is sampled at least once before it changes, the level should be held for at least one full machine cycle.

| RCLK + TCLK | CP/RL2 | TR2 | MODE                |

|-------------|--------|-----|---------------------|

| 0           | 0      | 1   | 16-bit Auto-reload  |

| 0           | 1      | 1   | 16-bit Capture      |

| 1           | х      | 1   | Baud Rate Generator |

| Х           | х      | 0   | (Off)               |

Table 10-1.Timer 2 Operating Modes

Figure 14-3. SPI Shift Register Diagram

The CPHA (<u>C</u>lock <u>PHA</u>se), CPOL (<u>C</u>lock <u>POL</u>arity), and SPR (<u>S</u>erial <u>P</u>eripheral clock <u>R</u>ate = baud rate) bits in SPCR control the shape and rate of SCK. The two SPR bits provide four possible clock rates when the SPI is in master mode. In slave mode, the SPI will operate at the rate of the incoming SCK as long as it does not exceed the maximum bit rate. There are also four possible combinations of SCK phase and polarity with respect to the serial data. CPHA and CPOL determine which format is used for transmission. The SPI data transfer formats are shown in Figure 14-4 and Figure 14-5. To prevent glitches on SCK from disrupting the interface, CPHA, CPOL, and SPR should be set up before the interface is enabled, and the master device should be enabled before the slave device(s).

| Symbol            | Parameter                | Min                      | Max | Units |

|-------------------|--------------------------|--------------------------|-----|-------|

| t <sub>CLCL</sub> | Oscillator Period        | 41.6                     |     | ns    |

| t <sub>scк</sub>  | Serial Clock Cycle Time  | 4t <sub>CLCL</sub>       |     | ns    |

| t <sub>SHSL</sub> | Clock High Time          | t <sub>SCK</sub> /2 - 25 |     | ns    |

| t <sub>SLSH</sub> | Clock Low Time           | t <sub>SCK</sub> /2 - 25 |     | ns    |

| t <sub>SR</sub>   | Rise Time                |                          | 25  | ns    |

| t <sub>SF</sub>   | Fall Time                |                          | 25  | ns    |

| t <sub>sis</sub>  | Serial Input Setup Time  | 10                       |     | ns    |

| t <sub>SIH</sub>  | Serial Input Hold Time   | 10                       |     | ns    |

| t <sub>SOH</sub>  | Serial Output Hold Time  |                          | 10  | ns    |

| t <sub>SOV</sub>  | Serial Output Valid Time |                          | 35  | ns    |

Table 14-4.

SPI Master Characteristics

# AT89S8253

| Interrupt            | Source           | Vector Address |

|----------------------|------------------|----------------|

| System Reset         | RST or POR       | 0000H          |

| External Interrupt 0 | IEO              | 0003H          |

| Timer 0 Overflow     | TF0              | 000BH          |

| External Interrupt 1 | IE1              | 0013H          |

| Timer 1 Overflow     | TF1              | 001BH          |

| Serial Port          | RI or TI or SPIF | 0023H          |

#### Table 15-1. Interrupt Enable (IE) Register

| IE Addres  | s = A8H       |               |                  |                                      |                |                  | Reset Value        | e = 0X00 0000B     |         |

|------------|---------------|---------------|------------------|--------------------------------------|----------------|------------------|--------------------|--------------------|---------|

| Bit Addres | ssable        |               |                  |                                      |                |                  |                    |                    |         |

|            |               |               |                  |                                      |                |                  |                    |                    |         |

|            | EA            | _             | ET2              | ES                                   | ET1            | EX1              | ET0                | EX0                |         |

| E          | Enable Bit =  | 1 enables the | e interrupt, 0 d | isables the inte                     | errupt.        |                  |                    |                    |         |

| Symbol     | Position      | Function      |                  |                                      |                |                  |                    |                    |         |

| EA         | IE.7          |               | •                | EA = 0, no inte<br>setting or cleari |                | •                | = 1, each interrup | ot source is indiv | idually |

| -          | IE.6          | Reserved.     |                  |                                      |                |                  |                    |                    |         |

| ET2        | IE.5          | Timer 2 int   | errupt enable    | bit.                                 |                |                  |                    |                    |         |

| ES         | IE.4          | SPI and U     | ART interrupt    | enable bit.                          |                |                  |                    |                    |         |

| ET1        | IE.3          | Timer 1 int   | errupt enable    | bit.                                 |                |                  |                    |                    |         |

| EX1        | IE.2          | External in   | terrupt 1 enal   | ole bit.                             |                |                  |                    |                    |         |

| ET0        | IE.1          | Timer 0 int   | errupt enable    | bit.                                 |                |                  |                    |                    |         |

| EX0        | IE.0          | External in   | terrupt 0 enal   | ole bit.                             |                |                  |                    |                    |         |

| User softv | vare should n | never write 1 | s to reserved l  | oits, because th                     | ney may be use | ed in future AT8 | 9 products.        |                    |         |

#### Table 15-2. IP – Interrupt Priority Register

| IP = B8I | IP = B8H Reset Value = XX00 0000B |   |     |    |     |     |     |     |  |  |

|----------|-----------------------------------|---|-----|----|-----|-----|-----|-----|--|--|

| Bit Addr | ressable                          |   |     |    |     |     |     |     |  |  |

|          | _                                 | _ | PT2 | PS | PT1 | PX1 | PT0 | PX0 |  |  |

| Bit      | 7                                 | 6 | 5   | 4  | 3   | 2   | 1   | 0   |  |  |

| Symbol | Function                           |

|--------|------------------------------------|

| PT2    | Timer 2 Interrupt Priority Low     |

| PS     | Serial Port Interrupt Priority Low |

| PT1    | Timer 1 Interrupt Priority Low     |

| PX1    | External Interrupt 1 Priority Low  |

| PT0    | Timer 0 Interrupt Priority Low     |

| PX0    | External Interrupt 0 Priority Low  |

### Table 15-3. IPH – Interrupt Priority High Register

| IPH = B7H |                                     |   |      |     |      | Reset Value = XX00 0000B |      |      |  |

|-----------|-------------------------------------|---|------|-----|------|--------------------------|------|------|--|

| Not Bi    | t Addressable                       |   |      |     |      |                          |      |      |  |

|           | -                                   | - | PT2H | PSH | PT1H | PX1H                     | PT0H | PX0H |  |

| Bit       | 7                                   | 6 | 5    | 4   | 3    | 2                        | 1    | 0    |  |

| Symbol    | Function                            |   |      |     |      |                          |      |      |  |

| PT2H      | Timer 2 Interrupt Priority High     |   |      |     |      |                          |      |      |  |

| PSH       | Serial Port Interrupt Priority High |   |      |     |      |                          |      |      |  |

| PT1H      | Timer 1 Interrupt Priority High     |   |      |     |      |                          |      |      |  |

| PX1H      | External Interrupt 1 Priority High  |   |      |     |      |                          |      |      |  |

| PT0H      | Timer 0 Interrupt Priority High     |   |      |     |      |                          |      |      |  |

| PX0H      | External Interrupt 0 Priority High  |   |      |     |      |                          |      |      |  |

Figure 15-1. Interrupt Sources

# 32 AT89S8253

## 16. Oscillator Characteristics

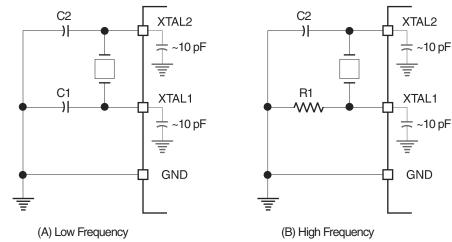

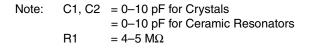

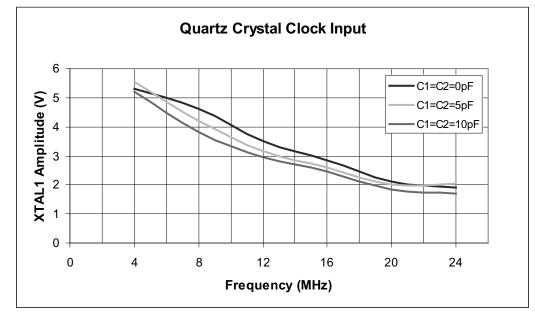

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator, as shown in Figure 16-1 (A) and (B). Either a quartz crystal or ceramic resonator may be used. For frequencies above 16MHz it is recommended that C1 be replaced with R1 for improved startup performance. Note that the internal structure of the devices adds about 10 pF of capacitance to both XTAL1 and XTAL2. The total capacitance on XTAL1 or XTAL2, including the external load capacitor (C1/C2) plus internal device load, board trace and crystal loadings, should not exceed 20 pF. Figure 16-2, 16-3, 16-4 and 16-5 illustrate the relationship between clock loading and the respective resulting clock amplitudes.

Figure 16-1. Oscillator Connections

Figure 16-2. Quartz Crystal Clock Source (A)

Figure 16-5. Ceramic Resonator Clock Source (B)

To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven, as shown in Figure 16-6.

#### 17. Idle Mode

In idle mode, the CPU puts itself to sleep while all the on-chip peripherals remain active. This mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.

Note that when idle mode is terminated by a hardware reset, the device normally resumes program execution from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when idle mode is terminated by a reset, the instruction following the one that invokes idle mode should not write to a port pin or to external memory.

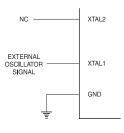

## 20. Programming the Flash and EEPROM

Atmel's AT89S8253 Flash microcontroller offers 12K bytes of In-System reprogrammable Flash code memory and 2K bytes of EEPROM data memory.

The AT89S8253 is normally shipped with the on-chip Flash code and EEPROM data memory arrays in the erased state (i.e. contents = FFH) and ready to be programmed. This device supports a parallel programming mode and a serial programming mode. The serial programming mode provides a convenient way to reprogram the AT89S8253 inside the user's system. The parallel programming mode is compatible with conventional third-party Flash or EPROM programmers.

The code and data memory arrays are mapped via separate address spaces in the parallel and serial programming modes: 0000H to 2FFFH for code memory and 000H to 7FFH for data memory.

The code and data memory arrays in the AT89S8253 are programmed byte-by-byte or by page in either programming mode. To reprogram any non-blank byte in the parallel or serial mode, the user needs to invoke the Chip Erase operation first to erase both arrays since there is no built-in auto-erase capability.

**Parallel Programming Algorithm:** To program and verify the AT89S8253 in the parallel programming mode, the following sequence is recommended (see Figure 26-1):

- 1. Power-up sequence:

- a. Apply power between  $V_{CC}$  and GND pins.

- b. Set RST pin to "H".

- c. Apply a 3 MHz to 24 MHz clock to XTAL1 pin and wait for at least 10 ms.

- 2. Set PSEN pin to "L"

- a. ALE pin to "H"

- b. EA pin to "H" and all other pins to "H".

- 3. Raise  $\overline{EA}/VPP$  to 12V to enable Flash programming, erase or verification. Enable the P3.0 pull-up (10 K $\Omega$ typical) for RDY/ $\overline{BSY}$  operation.

- Apply the appropriate combination of "H" or "L" logic levels to pins P3.3, P3.4, P3.5, P3.6, P3.7 to select one of the programming operations shown in the Flash Programming Modes table.

- 5. Apply the desired byte address to pins P1.0 to P1.7 and P2.0 to P2.5.

- a. Apply data to pins P0.0 to P0.7 for write code operation.

- 6. Pulse ALE/PROG once to load a byte in the code memory array, the data memory array, or the lock bits.

- 7. Repeat steps 5 and 6, changing the address and data for up to 64 bytes in the code memory page or 32 bytes in the data memory (EEPROM) page. When loading a page with individual bytes, the interval between consecutive byte loads should be no longer than 150 µs. Otherwise the device internally times out and assumes that the page load sequence is completed, rejecting any further loads before the page programming sequence has finished. This timing restriction also applies to Page Write of the 64-byte User Row.

- 8. After the last byte of the current page has been loaded, wait for 5 ms or monitor the RDY/BUSY pin until it transitions high. The page write cycle is self-timed and typically takes less than 5 ms.

- 9. To verify the last byte of the page just programmed, bring pin P3.4 to "L" and read the programmed data at pins P0.0 to P0.7.

# AT89S8253

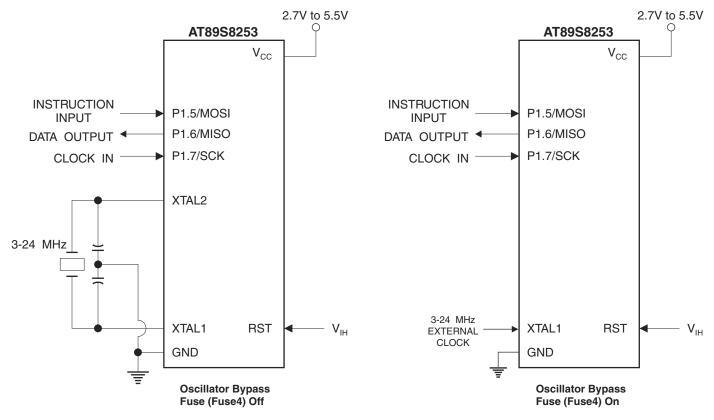

# **31. AC Characteristics**

The values shown in this table are valid for  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and  $V_{CC} = 2.7$  to 5.5V, unless otherwise noted.

Under operating conditions, load capacitance for Port 0, ALE/ $\overline{PROG}$ , and  $\overline{PSEN} = 100 \text{ pF}$ ; load capacitance for all other outputs = 80 pF.

#### 31.1 External Program and Data Memory Characteristics

|                     |                                    | Variable                | Variable Oscillator     |       |  |

|---------------------|------------------------------------|-------------------------|-------------------------|-------|--|

| Symbol              | Parameter                          | Min                     | Мах                     | Units |  |

| 1/t <sub>CLCL</sub> | Oscillator Frequency               | 0                       | 24                      | MHz   |  |

| LHLL                | ALE Pulse Width                    | 2t <sub>CLCL</sub> - 12 |                         | ns    |  |

| AVLL                | Address Valid to ALE Low           | t <sub>CLCL</sub> - 12  |                         | ns    |  |

| LLAX                | Address Hold after ALE Low         | t <sub>CLCL</sub> - 16  |                         | ns    |  |

| LLIV                | ALE Low to Valid Instruction In    |                         | 4t <sub>CLCL</sub> - 50 | ns    |  |

| LLPL                | ALE Low to PSEN Low                | t <sub>CLCL</sub> - 12  |                         | ns    |  |

| PLPH                | PSEN Pulse Width                   | 3t <sub>CLCL</sub> - 12 |                         | ns    |  |

| PLIV                | PSEN Low to Valid Instruction In   |                         | 3t <sub>CLCL</sub> - 50 | ns    |  |

| PXIX                | Input Instruction Hold after PSEN  | -10                     |                         | ns    |  |

| PXIZ                | Input Instruction Float after PSEN |                         | t <sub>CLCL</sub> - 20  | ns    |  |

| PXAV                | PSEN to Address Valid              | t <sub>CLCL</sub> - 4   |                         | ns    |  |

| AVIV                | Address to Valid Instruction In    |                         | 5t <sub>CLCL</sub> - 50 | ns    |  |

| PLAZ                | PSEN Low to Address Float          |                         | 20                      | ns    |  |

| RLRH                | RD Pulse Width                     | 6t <sub>CLCL</sub>      |                         | ns    |  |

| WLWH                | WR Pulse Width                     | 6t <sub>CLCL</sub>      |                         | ns    |  |

| RLDV                | RD Low to Valid Data In            |                         | 5t <sub>CLCL</sub> - 50 | ns    |  |

| RHDX                | Data Hold after RD                 | 0                       |                         | ns    |  |

| RHDZ                | Data Float after RD                |                         | 2t <sub>CLCL</sub> - 20 | ns    |  |

| LLDV                | ALE Low to Valid Data In           |                         | 8t <sub>CLCL</sub> - 50 | ns    |  |

| AVDV                | Address to Valid Data In           |                         | 9t <sub>CLCL</sub> - 50 | ns    |  |

| LLWL                | ALE Low to RD or WR Low            | 3t <sub>CLCL</sub> - 24 | 3t <sub>CLCL</sub>      | ns    |  |

| AVWL                | Address to RD or WR Low            | 4t <sub>CLCL</sub> - 12 |                         | ns    |  |

| QVWX                | Data Valid to WR Transition        | 2t <sub>CLCL</sub> - 24 |                         | ns    |  |

| QVWH                | Data Valid to WR High              | 8t <sub>CLCL</sub> - 24 |                         | ns    |  |

| WHQX                | Data Hold after WR                 | 2t <sub>CLCL</sub> - 24 |                         | ns    |  |

| RLAZ                | RD Low to Address Float            |                         | 0                       | ns    |  |

| WHLH                | RD or WR High to ALE High          | t <sub>CLCL</sub> - 10  | t <sub>CLCL</sub> + 20  | ns    |  |

| WHAX                | Address Hold after RD or WR High   | t <sub>CLCL</sub> - 10  |                         | ns    |  |

## 34. External Data Memory Write Cycle

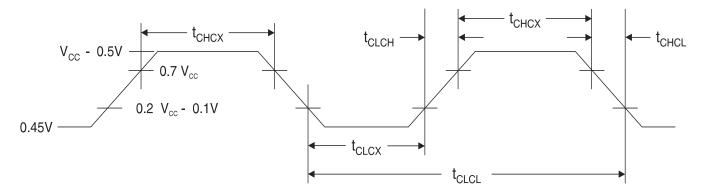

# 35. External Clock Drive Waveforms

# **36. External Clock Drive**

|                     |                      | V <sub>CC</sub> = 2.7\ |     |       |

|---------------------|----------------------|------------------------|-----|-------|

| Symbol              | Parameter            | Min                    | Max | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                      | 24  | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 41.6                   |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 12                     |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 12                     |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |                        | 5   | ns    |

| t <sub>CHCL</sub>   | Fall Time            |                        | 5   | ns    |

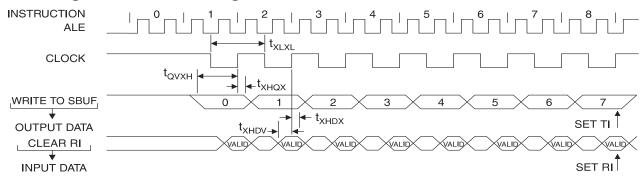

# 37. Serial Port Timing: Shift Register Mode Test Conditions

|        |           | Variable Oscillator |     |       |

|--------|-----------|---------------------|-----|-------|

| Symbol | Parameter | Min                 | Max | Units |

|        |           |                     |     |       |

|        |           |                     |     |       |

|        |           |                     |     |       |

|        |           |                     |     |       |

|        |           |                     |     |       |

# 38. Shift Register Mode Timing Waveforms

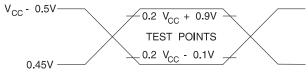

# **39. AC Testing Input/Output Waveforms**<sup>(1)</sup>

Note: 1. AC Inputs during testing are driven at V<sub>CC</sub> - 0.5V for a logic 1 and 0.45V for a logic 0. Timing measurements are made at V<sub>IH</sub> min. for a logic 1 and V<sub>IL</sub> max. for a logic 0.

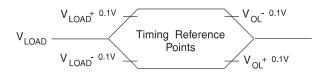

# 40. Float Waveforms<sup>(1)</sup>

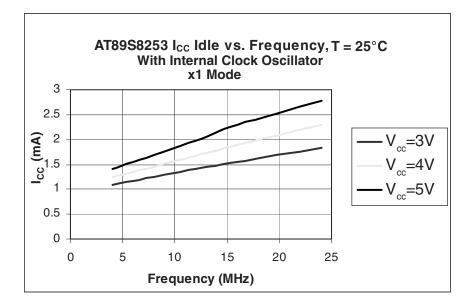

# 46. I<sub>CC</sub> (Idle Mode) Measurements

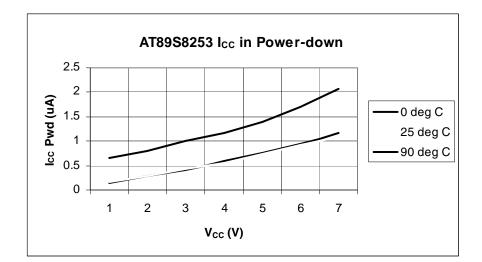

# 47. I<sub>CC</sub> (Power Down Mode) Measurements

# 48. Ordering Information

# 48.1 Green Package (Pb/Halide-free)

| Speed<br>(MHz) | Power<br>Supply | Ordering Code   | Package | Operation Range   |

|----------------|-----------------|-----------------|---------|-------------------|

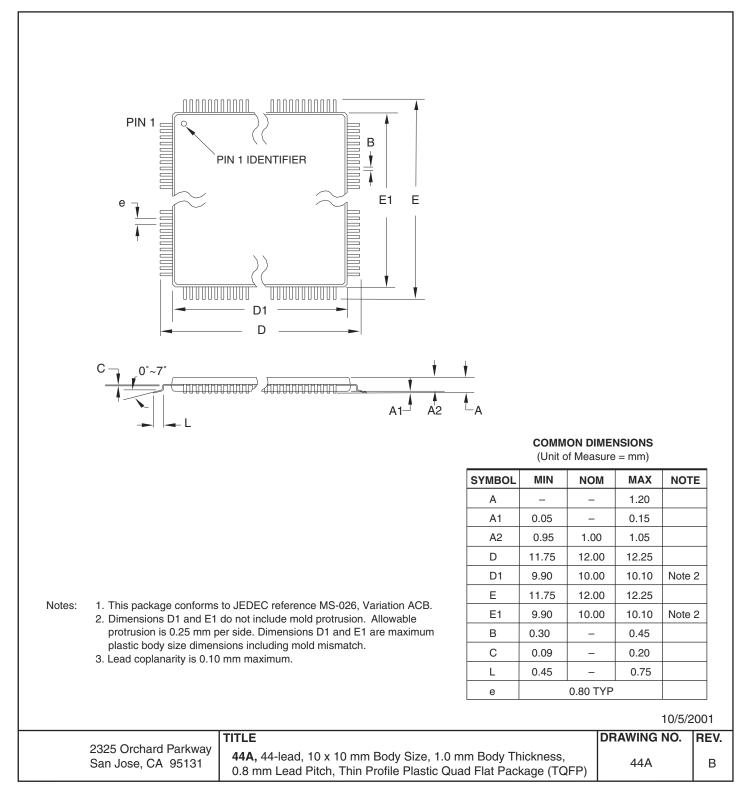

|                |                 | AT89S8253-24AU  | 44A     |                   |

| 24             |                 | AT89S8253-24JU  | 44J     | Industrial        |

| 24             | 2.7V to 5.5V    | AT89S8253-24PU  | 40P6    | (-40° C to 85° C) |

|                |                 | AT89S8253-24PSU | 42PS6   |                   |

| Package Type |                                                          |  |

|--------------|----------------------------------------------------------|--|

| 44 <b>A</b>  | 44-lead, Thin Plastic Gull Wing Quad Flat Package (TQFP) |  |

| 44J          | 44-lead, Plastic J-leaded Chip Carrier (PLCC)            |  |

| 40P6         | 40-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP) |  |

| 42PS6        | 42-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP) |  |

## 49. Package Information

56 **AT89S8253**

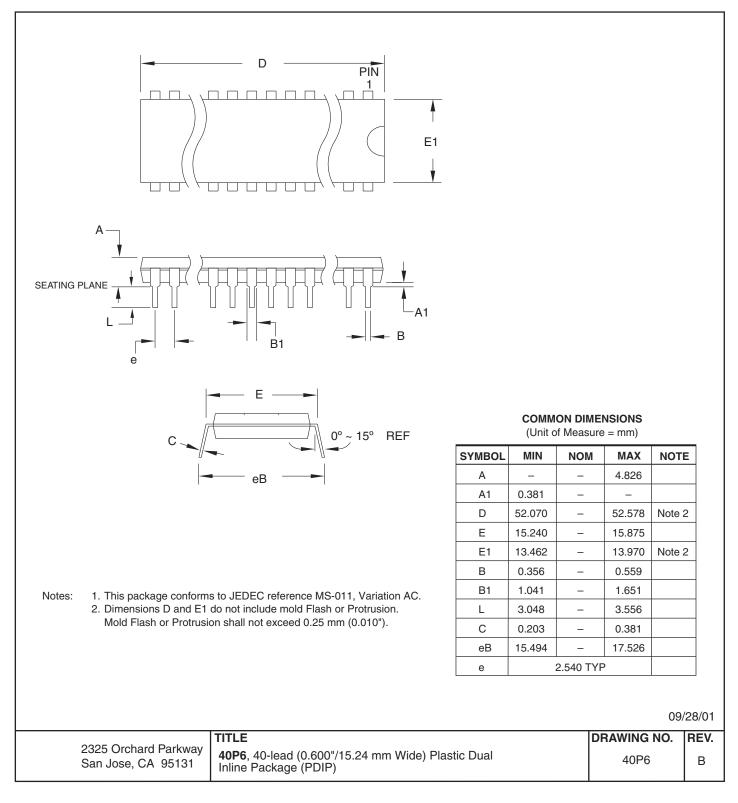

#### 49.3 40P6 - PDIP