#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit Dual-Core                                                                 |

| Speed                      | 180MHz, 200MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 152KB (152K x 8)                                                                 |

| Program Memory Type        | FLASH, PRAM                                                                      |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 20K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 23x12b; D/A 4x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch128mp202-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 3-136: C1TEFCONH: CAN TRANSMIT EVENT FIFO CONTROL REGISTER HIGH

| U-0             | U-0          | U-0                          | R/W-0                              | R/W-0                        | R/W-0 | R/W-0 | R/W-0     |  |

|-----------------|--------------|------------------------------|------------------------------------|------------------------------|-------|-------|-----------|--|

| _               | _            | —                            | FSIZE<4:0> <sup>(1)</sup>          |                              |       |       |           |  |

| bit 15          |              |                              |                                    |                              |       |       | bit 8     |  |

|                 |              |                              |                                    |                              |       |       |           |  |

| U-0             | U-0          | U-0                          | U-0                                | U-0                          | U-0   | U-0   | U-0       |  |

|                 | —            | —                            |                                    | —                            | —     | —     |           |  |

| bit 7           | ·            | •                            |                                    |                              |       | •     | bit 0     |  |

|                 |              |                              |                                    |                              |       |       |           |  |

| Legend:         |              |                              |                                    |                              |       |       |           |  |

| R = Readable    | bit          | W = Writable bi              | U = Unimplemented bit, read as '0' |                              |       |       |           |  |

| -n = Value at F | POR          | '1' = Bit is set             |                                    | '0' = Bit is cleared x = Bit |       |       | s unknown |  |

|                 |              |                              |                                    |                              |       |       |           |  |

| bit 15-13       | Unimplemen   | ted: Read as '0'             |                                    |                              |       |       |           |  |

| bit 12-8        | FSIZE<4:0>:  | FIFO Size bits <sup>(1</sup> | )                                  |                              |       |       |           |  |

|                 | 11111 = FIFC | D is 32 message              | s deep                             |                              |       |       |           |  |

|                 |              |                              |                                    |                              |       |       |           |  |

|                 | 00010 = FIFC | D is 3 messages              | deep                               |                              |       |       |           |  |

|                 | 00001 = FIFC | ) is 2 messages              | deep                               |                              |       |       |           |  |

|                 | 00000 = FIFC | D is 1 message o             | deep                               |                              |       |       |           |  |

| bit 7-0         | Unimplemen   | ted: Read as '0'             | 1                                  |                              |       |       |           |  |

**Note 1:** These bits can only be modified in Configuration mode (OPMOD<2:0> = 100).

| R/W-0 R<br>bit 15                                                    | R/W-0                                                       | R/W-0 | R/W-0<br>EFMSG  | R/W-0<br>CNT<15:8> | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------------------------------------------------------------|-------|-----------------|--------------------|-------|-------|-------|

| bit 15                                                               |                                                             |       | EFMSG           | CNT<15:8>          |       |       |       |

| bit 15                                                               |                                                             |       |                 |                    |       |       |       |

|                                                                      |                                                             |       |                 |                    |       |       | bit 8 |

|                                                                      |                                                             |       |                 |                    |       |       |       |

| R/W-0 R                                                              | R/W-0                                                       | R/W-0 | R/W-0           | R/W-0              | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |                                                             |       | EFMSG           | CNT<7:0>           |       |       |       |

| bit 7                                                                |                                                             |       |                 |                    |       |       | bit 0 |

|                                                                      |                                                             |       |                 |                    |       |       |       |

| Legend:                                                              |                                                             |       |                 |                    |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                             |       | 1 as '0'        |                    |       |       |       |

| -n = Value at POR                                                    | - Value at POR '1' = Bit is set '0' = Bit is cleared x = Bi |       | x = Bit is unkn | iown               |       |       |       |

## REGISTER 3-150: C1BDIAG1L: CAN BUS DIAGNOSTICS REGISTER 1 LOW

bit 15-0 EFMSGCNT<15:0>: Error-Free Message Counter bits

| PTG Input Number     | PTG Input Description                         |

|----------------------|-----------------------------------------------|

| PTG Trigger Input 0  | Trigger Input from Master PWM Channel 1       |

| PTG Trigger Input 1  | Trigger Input from Master PWM Channel 2       |

| PTG Trigger Input 2  | Trigger Input from Master PWM Channel 3       |

| PTG Trigger Input 3  | Trigger Input from Master PWM Channel 4       |

| PTG Trigger Input 4  | Trigger Input from Slave PWM Channel 1        |

| PTG Trigger Input 5  | Trigger Input from Slave PWM Channel 2        |

| PTG Trigger Input 6  | Trigger Input from Slave PWM Channel 3        |

| PTG Trigger Input 7  | Trigger Input from Master SCCP4               |

| PTG Trigger Input 8  | Trigger Input from Slave SCCP4                |

| PTG Trigger Input 9  | Trigger Input from Master Comparator 1        |

| PTG Trigger Input 10 | Trigger Input from Slave Comparator 1         |

| PTG Trigger Input 11 | Trigger Input from Slave Comparator 2         |

| PTG Trigger Input 12 | Trigger Input from Slave Comparator 3         |

| PTG Trigger Input 13 | Trigger Input Master ADC Done Group Interrupt |

| PTG Trigger Input 14 | Trigger Input Slave ADC Done Group Interrupt  |

| PTG Trigger Input 15 | Trigger Input from INT2 PPS                   |

## TABLE 3-46: PTG INPUT DESCRIPTIONS

## TABLE 3-47: PTG OUTPUT DESCRIPTIONS

| PTG Output Number | PTG Output Description            |

|-------------------|-----------------------------------|

| PTGO0 to PTGO11   | Reserved                          |

| PTGO12            | Trigger for Master ADC TRGSRC<30> |

| PTGO13            | Trigger for Slave ADC TRGSRC<30>  |

| PTGO16 to PTGO23  | Reserved                          |

| PTGO24            | PPS Master Output RP46            |

| PTGO25            | PPS Master Output RP47            |

| PTGO26            | PPS Master Input RP6              |

| PTGO27            | PPS Master Input RP7              |

| PTGO28            | PPS Slave Output RP46             |

| PTGO29            | PPS Slave Output RP47             |

| PTGO30            | PPS Slave Input RP6               |

| PTGO31            | PPS Slave Input RP7               |

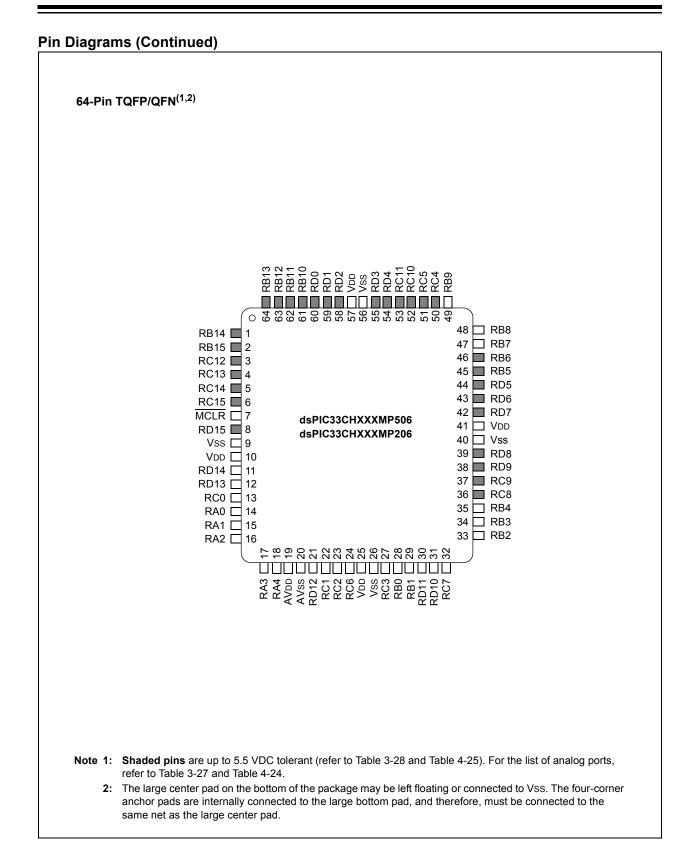

## dsPIC33CH128MP508 FAMILY

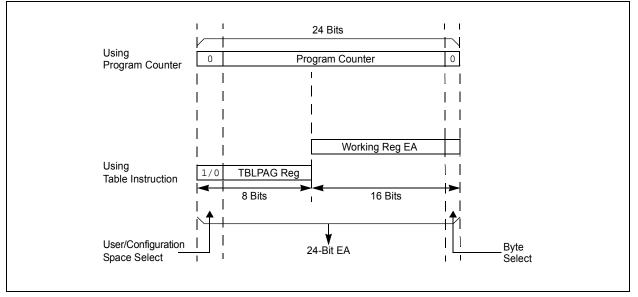

## FIGURE 4-13: ADDRESSING FOR TABLE REGISTERS

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a Built-In Self-Test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRISx setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRISx settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned.

- All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Select for PORTx (ANSELx) registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Select for PORTx registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 4.6.7 I/O PORTS RESOURCES

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 4.6.7.1 Key Resources

- "I/O Ports with Edge Detect" (DS70005322) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

|  | REGISTER 4-89: | ADCON4L: ADC CONTROL REGISTER 4 LOW |

|--|----------------|-------------------------------------|

|--|----------------|-------------------------------------|

| U-0     | U-0 | U-0          | U-0 | U-0 | U-0 | r-0     | r-0     |

|---------|-----|--------------|-----|-----|-----|---------|---------|

| —       | —   | —            | —   | —   | —   | —       | —       |

| bit 15  |     |              |     |     |     |         | bit 8   |

|         |     |              |     |     |     |         |         |

| U-0     | U-0 | U-0          | U-0 | U-0 | U-0 | R/W-0   | R/W-0   |

| —       | —   | —            | —   | —   | —   | SAMC1EN | SAMC0EN |

| bit 7   |     |              |     |     |     |         | bit 0   |

|         |     |              |     |     |     |         |         |

| Legend: |     | r = Reserved | bit |     |     |         |         |

| Legend:           | r = Reserved bit |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

- bit 15-10 Unimplemented: Read as '0'

- bit 9-8 Reserved: Must be written as '0'

- bit 7-2 Unimplemented: Read as '0'

- bit 1 SAMC1EN: Dedicated ADC Core 1 Conversion Delay Enable bit

- 1 = After trigger, the conversion will be delayed and the ADC core will continue sampling during the time specified by the SAMC<9:0> bits in the ADCORE1L register

- 0 = After trigger, the sampling will be stopped immediately and the conversion will be started on the next core clock cycle

- bit 0 SAMCOEN: Dedicated ADC Core 0 Conversion Delay Enable bit

- 1 = After trigger, the conversion will be delayed and the ADC core will continue sampling during the time specified by the SAMC<9:0> bits in the ADCORE0L register

- 0 = After trigger, the sampling will be stopped immediately and the conversion will be started on the next core clock cycle

## REGISTER 6-18: APLLDIV: APLL OUTPUT DIVIDER REGISTER (SLAVE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0        | R/W-0 |

|--------|-----|-----|-----|-----|-----|--------------|-------|

| —      | _   |     | —   | —   | —   | AVCODIV<1:0> |       |

| bit 15 |     |     |     |     |     |              | bit 8 |

|        |     |     |     |     |     |              |       |

| U-0   | R/W-1                           | R/W-0 | R/W-0 | U-0 | R/W-0                           | R/W-0 | R/W-1 |  |

|-------|---------------------------------|-------|-------|-----|---------------------------------|-------|-------|--|

| —     | APOST1DIV<2:0> <sup>(1,2)</sup> |       |       | —   | APOST2DIV<2:0> <sup>(1,2)</sup> |       |       |  |

| bit 7 |                                 |       |       |     |                                 |       | bit 0 |  |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 15-10 Unimplemented: Read as '0'

- bit 9-8 AVCODIV<1:0>: APLL VCO Output Divider Select bits

- 11 = AFvco 10 = AFvco/2 01 = AFvco/3 00 = AFvco/4

#### bit 7 Unimplemented: Read as '0'

bit 6-4 APOST1DIV<2:0>: APLL Output Divider #1 Ratio bits<sup>(1,2)</sup>

APOST1DIV<2:0> can have a valid value, from 1 to 7 (APOST1DIVx value should be greater than or equal to the APOST2DIVx value). The APOST1DIVx divider is designed to operate at higher clock rates than the APOST2DIVx divider.

#### bit 3 Unimplemented: Read as '0'

bit 2-0 APOST2DIV<2:0>: APLL Output Divider #2 Ratio bits<sup>(1,2)</sup>

APOST2DIV<2:0> can have a valid value, from 1 to 7 (APOST2DIVx value should be less than or equal to the APOST1DIVx value). The APOST1DIVx divider is designed to operate at higher clock rates than the APOST2DIVx divider.

- Note 1: The APOST1DIVx and APOST2DIVx divider values must not be changed while the PLL is operating.

- 2: The default values for APOST1DIVx and APOST2DIVx are 4 and 1, respectively, yielding a 150 MHz system source clock.

| U-0                                | U-0          | U-0            | U-0 | R/W-0                                   | U-0 | U-0 | U-0   |  |

|------------------------------------|--------------|----------------|-----|-----------------------------------------|-----|-----|-------|--|

| _                                  | _            | _              | _   | PMDLOCK                                 | _   | _   | —     |  |

| bit 15                             |              |                |     |                                         |     |     | bit 8 |  |

|                                    |              |                |     |                                         |     |     |       |  |

| U-0                                | U-0          | U-0            | U-0 | U-0                                     | U-0 | U-0 | U-0   |  |

| —                                  | —            | —              | —   | —                                       | —   | —   | —     |  |

| bit 7                              |              |                |     |                                         |     |     | bit 0 |  |

|                                    |              |                |     |                                         |     |     |       |  |

| Legend:                            |              |                |     |                                         |     |     |       |  |

| R = Readable                       | e bit        | W = Writable   | bit | U = Unimplemented bit, read as '0'      |     |     |       |  |

| -n = Value at POR '1' = Bit is set |              |                |     | '0' = Bit is cleared x = Bit is unknown |     |     | nown  |  |

|                                    |              |                |     |                                         |     |     |       |  |

| bit 15-12                          | Unimplement  | ted: Read as ' | 0'  |                                         |     |     |       |  |

| bit 11                             | PMDLOCK: F   | MD Lock bit    |     |                                         |     |     |       |  |

|                                    | 1 = PMD bits | can be written |     |                                         |     |     |       |  |

## REGISTER 7-9: PMDCON: SLAVE PMD CONTROL REGISTER

0 = PMD bits are not allowed to be written

Unimplemented: Read as '0'

bit 10-0

| U-0           | U-0         | U-0              | U-0       | U-0               | U-0              | R/W-0           | R/W-0  |

|---------------|-------------|------------------|-----------|-------------------|------------------|-----------------|--------|

| —             | —           | —                | —         | —                 | —                | DMA1MD          | DMA0MD |

| bit 15        |             |                  |           |                   |                  |                 | bit 8  |

|               |             |                  |           |                   |                  |                 |        |

| U-0           | U-0         | U-0              | U-0       | U-0               | U-0              | U-0             | U-0    |

| —             | —           | —                | —         | —                 | —                | —               | —      |

| bit 7         |             |                  |           |                   |                  |                 | bit 0  |

|               |             |                  |           |                   |                  |                 |        |

| Legend:       |             |                  |           |                   |                  |                 |        |

| R = Readabl   | le bit      | W = Writable     | bit       | U = Unimplem      | nented bit, read | l as '0'        |        |

| -n = Value at | t POR       | '1' = Bit is set |           | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |

|               |             |                  |           |                   |                  |                 |        |

| bit 15-10     | Unimplement | ted: Read as '   | כי        |                   |                  |                 |        |

| bit 9         | DMA1MD: DN  | /A1 Module Di    | sable bit |                   |                  |                 |        |

|               | 1 = DMA1 mo | dule is disable  | d         |                   |                  |                 |        |

|               | 0 = DMA1 mo | dule is enabled  | b         |                   |                  |                 |        |

| bit 8         | DMA0MD: DN  | /A0 Module Di    | sable bit |                   |                  |                 |        |

|               | 1 = DMA0 mo | dule is disable  | d         |                   |                  |                 |        |

## REGISTER 7-13: PMD6: SLAVE PERIPHERAL MODULE DISABLE 6 CONTROL REGISTER HIGH

0 = DMA0 module is enabled

## TABLE 7-2: MASTER PMD REGISTERS

| Register | Bit 15 | Bit14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------|--------|-------|--------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| PMDCONL  | _      | _     | _      | —       | PMDLOCK |        | _      | _      |        | _      |        |        |        |        |        | _      |

| PMD1     | _      | _     | _      | —       | T1MD    | QEIMD  | PWMMD  | _      | I2C1MD | U2MD   | U1MD   | SPI2MD | SPI1MD | _      | C1MD   | ADC1MD |

| PMD2     |        |       | _      | _       | _       |        | _      |        | CCP8MD | CCP7MD | CCP6MD | CCP5MD | CCP4MD | CCP3MD | CCP2MD | CCP1MD |

| PMD3     | -      | _     | —      | —       | -       | _      | —      | _      | CRCMD  | —      | -      | _      | _      | —      | I2C2MD | _      |

| PMD4     | _      | _     | _      | —       | _       | —      | _      | _      | _      | —      | _      | _      | REFOMD | _      | _      | —      |

| PMD6     |        |       | DMA5MD | DMA4MD  | DMA3MD  | DMA2MD | DMA1MD | DMA0MD |        | _      |        |        |        | _      | _      | _      |

| PMD7     | _      | _     | _      | _       | _       |        | _      | CMP1MD |        | _      | _      | _      | PTGMD  | —      | _      | _      |

| PMD8     | _      | _     | _      | SENT2MD | SENT1MD |        | _      | _      | _      | —      | CLC4MD | CLC3MD | CLC2MD | CLC1MD | BIASMD | —      |

## TABLE 7-3: SLAVE PMD REGISTERS

| Register | Bit 15 | Bit14  | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------|--------|--------|--------|--------|---------|--------|--------|--------|--------|-------|--------|--------|--------|--------|--------|--------|

| PMDCON   | _      | —      | —      |        | PMDLOCK | _      | —      | —      | —      | —     | _      | _      |        | _      | —      | —      |

| PMD1     | _      | —      |        | _      | T1MD    | QEIMD  | PWMMD  | -      | I2C1MD | —     | U1MD   | _      | SPI1MD | _      |        | ADC1MD |

| PMD2     | _      | _      |        | _      | _       | _      | _      | _      | _      | _     | _      | _      | CCP4MD | CCP3MD | CCP2MD | CCP1MD |

| PMD4     | _      | —      |        | _      | —       | _      | —      | _      |        | _     |        | _      | REFOMD | _      |        | —      |

| PMD6     | _      | _      |        | _      | _       | _      | DMA1MD | DMA0MD | _      | _     | _      | _      | _      | _      | _      | _      |

| PMD7     | _      | —      | —      |        | _       | CMP3MD | CMP2MD | CMP1MD | —      | _     | —      | —      | —      | —      | PGA1MD | _      |

| PMD8     | _      | PGA3MD | —      |        | _       | PGA2MD | _      | —      | —      | _     | CLC4MD | CLC3MD | CLC2MD | CLC1MD | —      | _      |

| REGISTER 11-4: | DACxCONH: DACx CONTROL HIGH REGISTER |

|----------------|--------------------------------------|

|                |                                      |

| U-0          | U-0   | U-0              | U-0   | U-0          | U-0              | R/W-0    | R/W-0  |

|--------------|-------|------------------|-------|--------------|------------------|----------|--------|

| _            |       | —                | _     | —            | —                | TMCE     | 3<9:8> |

| bit 15       |       |                  |       |              |                  |          | bit 8  |

|              |       |                  |       |              |                  |          |        |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

|              |       |                  | TMC   | 3<7:0>       |                  |          |        |

| bit 7        |       |                  |       |              |                  |          | bit 0  |

|              |       |                  |       |              |                  |          |        |

| Legend:      |       |                  |       |              |                  |          |        |

| R = Readable | e bit | W = Writable bit |       | U = Unimpler | nented bit, read | d as '0' |        |

bit 15-10 **Unimplemented:** Read as '0'

-n = Value at POR

bit 9-0 **TMCB<9:0>:** DACx Leading-Edge Blanking bits These register bits specify the blanking period for the comparator, following changes to the DAC output during Change-of-State (COS), for the input signal selected by the HCFSEL<3:0> bits in Register 11-9.

'0' = Bit is cleared

## REGISTER 11-5: DACxCONL: DACx CONTROL LOW REGISTER

'1' = Bit is set

| R/W-0  | R/W-0                  | R/W-0                  | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  |

|--------|------------------------|------------------------|-----|-----|-------|--------|--------|

| DACEN  | IRQM1 <sup>(1,2)</sup> | IRQM0 <sup>(1,2)</sup> | —   | _   | CBE   | DACOEN | FLTREN |

| bit 15 |                        |                        |     |     |       |        | bit 8  |

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   |

|---------|--------|--------|--------|--------|--------|---------|---------|

| CMPSTAT | CMPPOL | INSEL2 | INSEL1 | INSEL0 | HYSPOL | HYSSEL1 | HYSSEL0 |

| bit 7   |        |        |        |        |        |         | bit 0   |

| Legend:           |                  |                                    |  |

|-------------------|------------------|------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |  |

bit 15 DACEN: Individual DACx Module Enable bit

- 1 = Enables DACx module

- 0 = Disables DACx module to reduce power consumption; any pending Slope mode and/or underflow conditions are cleared

- bit 14-13 IRQM<1:0>: Interrupt Mode select bits<sup>(1,2)</sup>

- 11 = Generates an interrupt on either a rising or falling edge detect

- 10 = Generates an interrupt on a falling edge detect

- 01 = Generates an interrupt on a rising edge detect

- 00 = Interrupts are disabled

- bit 12-11 Unimplemented: Read as '0'

#### Note 1: Changing these bits during operation may generate a spurious interrupt.

2: The edge selection is a post-polarity selection via the CMPPOL bit.

## 12.1 QEI Control and Status Registers

| R/W-0         | U-0                                                                                                | R/W-0                                                                                                                                 | R/W-0                                                                                       | R/W-0                                                                                             | R/W-0                                                  | R/W-0                                                                     | R/W-0          |

|---------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------|----------------|

| QEIEN         | —                                                                                                  | QEISIDL                                                                                                                               | PIMOD2                                                                                      | PIMOD1                                                                                            | PIMOD0                                                 | IMV1                                                                      | IMV0           |

| bit 15        |                                                                                                    |                                                                                                                                       |                                                                                             | •                                                                                                 | •                                                      |                                                                           | bit 8          |

| U-0           | R/W-0                                                                                              | R/W-0                                                                                                                                 | R/W-0                                                                                       | R/W-0                                                                                             | R/W-0                                                  | R/W-0                                                                     | R/W-0          |

| 0-0           |                                                                                                    | 1                                                                                                                                     |                                                                                             |                                                                                                   |                                                        | -                                                                         |                |

| <br>bit 7     | INTDIV2                                                                                            | INTDIV1                                                                                                                               | INTDIV0                                                                                     | CNTPOL                                                                                            | GATEN                                                  | CCM1                                                                      | CCM0           |

|               |                                                                                                    |                                                                                                                                       |                                                                                             |                                                                                                   |                                                        |                                                                           | DIL            |

| Legend:       |                                                                                                    |                                                                                                                                       |                                                                                             |                                                                                                   |                                                        |                                                                           |                |

| R = Readable  | e bit                                                                                              | W = Writable                                                                                                                          | bit                                                                                         | U = Unimplen                                                                                      | nented bit, read                                       | d as '0'                                                                  |                |

| -n = Value at | POR                                                                                                | '1' = Bit is set                                                                                                                      |                                                                                             | '0' = Bit is clea                                                                                 | ared                                                   | x = Bit is unkn                                                           | iown           |

| bit 15        | 1 = QEI modu                                                                                       | drature Encode<br>ule is enabled<br>ule is disabled;                                                                                  |                                                                                             |                                                                                                   | or written                                             |                                                                           |                |

| bit 14        | Unimplemen                                                                                         | ted: Read as '                                                                                                                        | )'                                                                                          |                                                                                                   |                                                        |                                                                           |                |

| bit 13        | QEISIDL: QE                                                                                        | I Stop in Idle M                                                                                                                      | ode bit                                                                                     |                                                                                                   |                                                        |                                                                           |                |

|               |                                                                                                    | ues module ope<br>s module opera                                                                                                      |                                                                                             |                                                                                                   | le mode                                                |                                                                           |                |

| bit 12-10     | PIMOD<2:0>                                                                                         | : Position Cour                                                                                                                       | ter Initializatio                                                                           | n Mode Select                                                                                     | bits                                                   |                                                                           |                |

|               | 101 = Resets<br>100 = Secon<br>QEIxIC<br>011 = First Ir<br>registe<br>010 = Next Ir<br>001 = Every | d Index event a<br>C register<br>ndex event after<br>er                                                                               | ounter when th<br>after Home event<br>Home event in<br>t initializes the<br>nt resets the p | e position coun<br>ent initializes th<br>itializes the pos<br>position counter<br>osition counter | ne position cou<br>sition counter w<br>er with the con | QEIxGEC regis<br>unter with the c<br>vith the contents<br>tents of the QE | ontents of the |

| bit 9-8       |                                                                                                    | dex Match Valu                                                                                                                        |                                                                                             | position count                                                                                    | .01                                                    |                                                                           |                |

|               | 11 = Index m<br>10 = Index m<br>01 = Index m<br>00 = Index m                                       | atch occurs wh<br>atch occurs wh<br>atch occurs wh<br>atch occurs wh                                                                  | en QEBx = 1 a<br>en QEBx = 1 a<br>en QEBx = 0 a<br>en QEBx = 0 a                            | and QEAx = $0$<br>and QEAx = $1$                                                                  |                                                        |                                                                           |                |

| bit 7         | -                                                                                                  | ted: Read as '                                                                                                                        |                                                                                             |                                                                                                   |                                                        |                                                                           |                |

| bit 6-4       | velocity count                                                                                     | ter and Index of<br>prescale value<br>rescale value<br>rescale value<br>rescale value<br>escale value<br>escale value<br>escale value |                                                                                             |                                                                                                   |                                                        | nain timer (pos                                                           | ition counter) |

| bit 3         | -                                                                                                  | sition, Velocity                                                                                                                      | and Index Cou                                                                               | inter/Timer Dire                                                                                  | ection Select bi                                       | t                                                                         |                |

|               |                                                                                                    | direction is nega                                                                                                                     |                                                                                             |                                                                                                   |                                                        |                                                                           |                |

## REGISTER 12-1: QEIXCON: QEIX CONTROL REGISTER

## REGISTER 13-14: UXRXCHK: UARTX RECEIVE CHECKSUM REGISTER

| U-0                             | U-0                                                      | U-0               | U-0             | U-0                | U-0              | U-0             | U-0   |  |  |

|---------------------------------|----------------------------------------------------------|-------------------|-----------------|--------------------|------------------|-----------------|-------|--|--|

|                                 | —                                                        | —                 | —               | —                  | —                | —               | —     |  |  |

| bit 15                          |                                                          |                   |                 |                    |                  |                 | bit 8 |  |  |

|                                 |                                                          |                   |                 |                    |                  |                 |       |  |  |

| R/W-0                           | R/W-0                                                    | R/W-0             | R/W-0           | R/W-0              | R/W-0            | R/W-0           | R/W-0 |  |  |

|                                 |                                                          |                   | RXCH            | K<7:0>             |                  |                 |       |  |  |

| bit 7                           |                                                          |                   |                 |                    |                  |                 | bit 0 |  |  |

|                                 |                                                          |                   |                 |                    |                  |                 |       |  |  |

| Legend:                         |                                                          |                   |                 |                    |                  |                 |       |  |  |

| R = Reada                       | ble bit                                                  | W = Writable      | bit             | U = Unimplem       | nented bit, read | as '0'          |       |  |  |

| -n = Value a                    | at POR                                                   | '1' = Bit is set  |                 | '0' = Bit is clea  | ared             | x = Bit is unkr | nown  |  |  |

|                                 |                                                          |                   |                 |                    |                  |                 |       |  |  |

| bit 15-8                        | Unimplemen                                               | ted: Read as '0   | 3               |                    |                  |                 |       |  |  |

| bit 7-0                         | RXCHK<7:0>                                               | : Receive Cheo    | cksum bits (cal | culated from RX    | K words)         |                 |       |  |  |

|                                 | LIN Modes:                                               |                   |                 |                    |                  |                 |       |  |  |

|                                 |                                                          |                   |                 | ion carries, inclu |                  |                 |       |  |  |

|                                 | C0EN = 0: Su                                             | im of all receive | ed data + addit | ion carries, excl  | uding PID.       |                 |       |  |  |

|                                 | LIN Slave:                                               |                   |                 |                    |                  |                 |       |  |  |

| Cleared when Break is detected. |                                                          |                   |                 |                    |                  |                 |       |  |  |

|                                 | LIN Master/Slave:                                        |                   |                 |                    |                  |                 |       |  |  |

|                                 | Cleared when Break is detected.                          |                   |                 |                    |                  |                 |       |  |  |

|                                 | Other Modes:                                             |                   |                 |                    |                  |                 |       |  |  |

|                                 | C0EN = 1: Sum of every byte received + addition carries. |                   |                 |                    |                  |                 |       |  |  |

C0EN = 0: Value remains unchanged.

NOTES:

## REGISTER 21-6: FWDT CONFIGURATION REGISTER

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R/PO-1 | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  |

|--------|---------|---------|---------|---------|---------|---------|---------|

| FWDTEN | SWDTPS4 | SWDTPS3 | SWDTPS2 | SWDTPS1 | SWDTPS0 | WDTWIN1 | WDTWIN0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| R/PO-1 | R/PO-1   | R/PO-1   | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  |

|--------|----------|----------|---------|---------|---------|---------|---------|

| WINDIS | RCLKSEL1 | RCLKSEL0 | RWDTPS4 | RWDTPS3 | RWDTPS2 | RWDTPS1 | RWDTPS0 |

| bit 7  |          |          |         |         |         |         | bit 0   |

| Legend:           | PO = Program Once bit             |                      |                    |

|-------------------|-----------------------------------|----------------------|--------------------|

| R = Readable bit  | R = Readable bit W = Writable bit |                      | d as '0'           |

| -n = Value at POR | '1' = Bit is set                  | '0' = Bit is cleared | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                 |

|-----------|----------------------------------------------------------------------------------------------------------------------------|

| bit 15    | FWDTEN: Watchdog Timer Enable bit                                                                                          |

|           | 1 = WDT is enabled in hardware                                                                                             |

|           | 0 = WDT controller via the ON bit (WDTCONL<15>)                                                                            |

| bit 14-10 | SWDTPS<4:0>: Sleep Mode Watchdog Timer Period Select bits                                                                  |

|           | 11111 = Divide by 2 ^ 30 = 1,073,741,824                                                                                   |

|           | 11110 = Divide by 2 ^ 29 = 526,870,912                                                                                     |

|           | 00001 = Divide by 2 ^ 2, 4                                                                                                 |

|           | 00000 = Divide by 2 ^ 1, 2                                                                                                 |

| bit 9-8   | WDTWIN<1:0>: Watchdog Timer Window Select bits                                                                             |

|           | 11 = WDT window is 25% of the WDT period                                                                                   |

|           | 10 = WDT window is 37.5% of the WDT period                                                                                 |

|           | 01 = WDT window is 50% of the WDT period<br>00 = WDT Window is 75% of the WDT period                                       |

| bit 7     | WINDIS: Watchdog Timer Window Enable bit                                                                                   |

|           | 1 = Watchdog Timer is in Non-Window mode                                                                                   |

|           | 0 = Watchdog Timer is in Window mode                                                                                       |

| bit 6-5   | RCLKSEL<1:0>: Watchdog Timer Clock Select bits                                                                             |

|           | 11 = LPRC clock                                                                                                            |

|           | 10 = Uses FRC when WINDIS = 0, system clock is not INTOSC/LPRC and device is not in Sleep;                                 |

|           | otherwise, uses INTOSC/LPRC<br>01 = Uses peripheral clock when system clock is not INTOSC/LPRC and device is not in Sleep; |

|           | otherwise, uses INTOSC/LPRC                                                                                                |

|           | 00 = Reserved                                                                                                              |

| bit 4-0   | RWDTPS<4:0>: Run Mode Watchdog Timer Period Select bits                                                                    |

|           | 11111 = Divide by 2 ^ 30 = 1,073,741,824                                                                                   |

|           | 11110 = Divide by 2 ^ 29 = 526,870,912                                                                                     |

|           | 00001 = Divide by 2 ^ 2, 4                                                                                                 |

|           | 00000 = Divide by 2 ^ 1, 2                                                                                                 |

|           |                                                                                                                            |

| REGISTER 21-9: FDMTIVTL CONFIGURATION REGISTER |

|------------------------------------------------|

|------------------------------------------------|

| U-1          | U-1    | U-1    | U-1    | U-1    | U-1    | U-1    | U-1    |  |

|--------------|--------|--------|--------|--------|--------|--------|--------|--|

| _            | —      | —      |        | —      | —      | —      | —      |  |

| bit 23       |        | •      |        |        |        | •      | bit 16 |  |

|              |        |        |        |        |        |        |        |  |

| R/PO-1       | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |  |

| DMTIVT<15:8> |        |        |        |        |        |        |        |  |

| bit 15 |

|--------|

|--------|

| R/PO-1      | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |  |

|-------------|--------|--------|--------|--------|--------|--------|--------|--|

| DMTIVT<7:0> |        |        |        |        |        |        |        |  |

| bit 7 b     |        |        |        |        |        |        |        |  |

| Legend:           | PO = Program Once bit |                       |                    |  |

|-------------------|-----------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared  | x = Bit is unknown |  |

bit 23-16Unimplemented: Read as '1'bit 15-0DMTIVT<15:0>: DMT Window Interval Lower 16 bits

## **REGISTER 21-10: FDMTIVTH CONFIGURATION REGISTER**

| U-1    | U-1    | U-1    | U-1    | U-1     | U-1    | U-1    | U-1    |

|--------|--------|--------|--------|---------|--------|--------|--------|

|        |        | —      |        | —       |        |        | —      |

| bit 23 |        |        |        |         |        |        | bit 16 |

|        |        |        |        |         |        |        |        |

| R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1  | R/PO-1 | R/PO-1 | R/PO-1 |

|        |        |        | DMTIVT | <31:24> |        |        |        |

| bit 15 |        |        |        |         |        |        | bit 8  |

| R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1  | R/PO-1 | R/PO-1 | R/PO-1 |

|        |        |        | DMTIVT | <23:16> |        |        |        |

| bit 7  |        |        |        |         |        |        | bit 0  |

| Legend:           | PO = Program Once bit |                                    |                    |  |

|-------------------|-----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 23-16 **Unimplemented:** Read as '1'

bit 15-0 DMTIVT<31:16>: DMT Window Interval Higher 16 bits

bit 8

### **REGISTER 21-15: FALTREG CONFIGURATION REGISTER (CONTINUED)**

- bit 2-0 **CTXT1<2:0>:** Specifies the Alternate Working Register Set #1 with Interrupt Priority Levels (IPL) bits 111 = Not assigned

- 110 = Alternate Register Set #1 is assigned to IPL Level 7

- 101 = Alternate Register Set #1 is assigned to IPL Level 6

- 100 = Alternate Register Set #1 is assigned to IPL Level 5

- 011 = Alternate Register Set #1 is assigned to IPL Level 4

- 010 =Alternate Register Set #1 is assigned to IPL Level 3

- 001 = Alternate Register Set #1 is assigned to IPL Level 2

- 000 = Alternate Register Set #1 is assigned to IPL Level 1

## **REGISTER 21-16: FMBXM CONFIGURATION REGISTER**

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     | •   |     |     |     | bit 16 |

| R/PO-1 | R/PO-1 | R/PO-1                                    | R/PO-1                                                          | R/PO-1                                                                                | R/PO-1                                                                                                      | R/PO-1                                                                                                                           |

|--------|--------|-------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| MBXM14 | MBXM13 | MBXM12                                    | MBXM11                                                          | MBXM10                                                                                | MBXM9                                                                                                       | MBXM8                                                                                                                            |

|        |        |                                           |                                                                 |                                                                                       |                                                                                                             | bit 8                                                                                                                            |

|        |        |                                           |                                                                 |                                                                                       |                                                                                                             |                                                                                                                                  |

| R/PO-1 | R/PO-1 | R/PO-1                                    | R/PO-1                                                          | R/PO-1                                                                                | R/PO-1                                                                                                      | R/PO-1                                                                                                                           |

| MBXM6  | MBXM5  | MBXM4                                     | MBXM3                                                           | MBXM2                                                                                 | MBXM1                                                                                                       | MBXM0                                                                                                                            |

|        | R/PO-1 | MBXM14     MBXM13       R/PO-1     R/PO-1 | MBXM14     MBXM13     MBXM12       R/PO-1     R/PO-1     R/PO-1 | MBXM14     MBXM13     MBXM12     MBXM11       R/PO-1     R/PO-1     R/PO-1     R/PO-1 | MBXM14     MBXM13     MBXM12     MBXM11     MBXM10       R/PO-1     R/PO-1     R/PO-1     R/PO-1     R/PO-1 | MBXM14     MBXM13     MBXM12     MBXM11     MBXM10     MBXM9       R/PO-1     R/PO-1     R/PO-1     R/PO-1     R/PO-1     R/PO-1 |

| Legend:           | PO = Program Once bit |                           |                    |

|-------------------|-----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared      | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                                                                                                            |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | MBXM15: Mailbox Data Register Channel Direction Fuses bits                                                                                                                                                            |

|           | <ul> <li>1 = Mailbox Register #15 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #15 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 14    | MBXM14: Mailbox Data Register Channel Direction Fuses bits                                                                                                                                                            |

|           | <ul> <li>1 = Mailbox Register #14 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #14 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 13    | MBXM13: Mailbox Data Register Channel Direction Fuses bits                                                                                                                                                            |

|           | <ul> <li>1 = Mailbox Register #13 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #13 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 12    | MBXM12: Mailbox Data Register Channel Direction Fuses bits                                                                                                                                                            |

|           | <ul> <li>1 = Mailbox Register #12 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #12 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 11    | MBXM11: Mailbox Data Register Channel Direction Fuses bits                                                                                                                                                            |

|           | <ul> <li>1 = Mailbox Register #11 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #11 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 10    | MBXM10: Mailbox Data Register Channel Direction Fuses bits                                                                                                                                                            |

|           | <ul> <li>1 = Mailbox Register #10 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #10 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

bit 7

bit 0

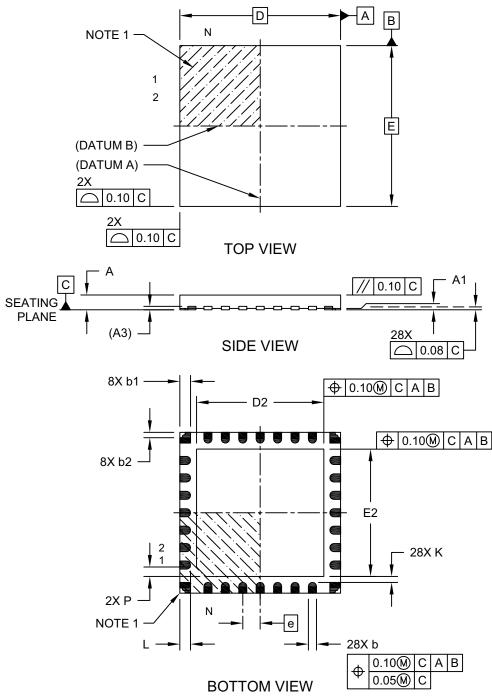

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (2N) - 6x6x0.55 mm Body [UQFN] With 4.65x4.65 mm Exposed Pad and Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-385B Sheet 1 of 2

## **Worldwide Sales and Service**

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160

Japan - Tokyo Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301 Korea - Seoul

Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

Tel: 31-416-690399 Fax: 31-416-690340

EUROPE

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4450-2828

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Israel - Ra'anana

Italy - Milan

Italy - Padova

Tel: 972-9-744-7705

Tel: 39-0331-742611

Fax: 39-0331-466781

Tel: 39-049-7625286

**Netherlands - Drunen**

Tel: 49-7131-67-3636

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

Denmark - Copenhagen

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820