Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit Dual-Core                                                                  |

| Speed                      | 180MHz, 200MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 152KB (152K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                       |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 20K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 23x12b; D/A 4x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-UQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-UQFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch128mp202t-i-2n |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

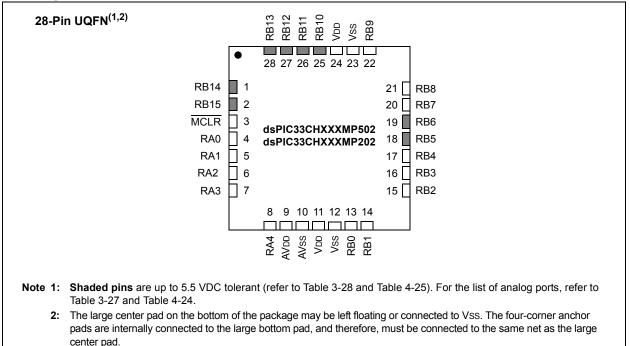

## **Pin Diagrams (Continued)**

#### TABLE 5: 28-PIN UQFN

| Pin # | Master Core                    | Slave Core                                                              |

|-------|--------------------------------|-------------------------------------------------------------------------|

| 1     | RP46/PWM1H/RB14                | S1RP46/S1PWM1H/S1RB14                                                   |

| 2     | <b>RP47</b> /PWM1L/RB15        | S1RP47/S1PWM6H/S1PWM1L/S1RB15                                           |

| 3     | MCLR                           | _                                                                       |

| 4     | AN0/CMP1A/RA0                  | S1RA0                                                                   |

| 5     | AN1/RA1                        | S1AN15/S1RA1                                                            |

| 6     | AN2/RA2                        | S1AN16/S1RA2                                                            |

| 7     | AN3/IBIAS0/RA3                 | S1AN0/S1CMP1A/S1PGA1P1/S1RA3                                            |

| 8     | AN4/IBIAS1/RA4                 | S1MCLR3/S1AN1/S1CMP2A/S1PGA2P1/S1PGA3P2/S1RA4                           |

| 9     | AVDD                           | AVDD                                                                    |

| 10    | AVss                           | AVss                                                                    |

| 11    | VDD                            | VDD                                                                     |

| 12    | Vss                            | Vss                                                                     |

| 13    | OSCI/CLKI/AN5/RP32/RB0         | S1AN5/ <b>S1RP32</b> /S1RB0                                             |

| 14    | OSCO/CLKO/AN6/IBIAS2/RP33/RB1  | S1AN4/ <b>S1RP33</b> /S1RB1                                             |

| 15    | DACOUT/AN7/CMP1D/RP34/INT0/RB2 | S1MCLR2/S1AN3/S1ANC0/S1ANC1/S1CMP1D/S1CMP2D/S1CMP3D/S1RP34/S1INT0/S1RB2 |

| 16    | PGD2/AN8/ <b>RP35</b> /RB3     | S1PGD2/S1AN18/S1CMP3A/S1PGA3P1/S1RP35/S1RB3                             |

| 17    | PGC2/ <b>RP36</b> /RB4         | S1PGC2/S1AN9/S1RP36/S1PWM5L/S1RB4                                       |

| 18    | PGD3/ <b>RP37</b> /SDA2/RB5    | S1PGD3/ <b>S1RP37</b> /S1RB5                                            |

| 19    | PGC3/RP38/SCL2/RB6             | S1PGC3/ <b>S1RP38</b> /S1RB6                                            |

| 20    | TDO/AN9/ <b>RP39</b> /RB7      | S1MCLR1/S1AN6/S1RP39/S1PWM5H/S1RB7                                      |

| 21    | PGD1/AN10/RP40/SCL1/RB8        | S1PGD1/S1AN7/ <b>S1RP40</b> /S1SCL1/S1RB8                               |

| 22    | PGC1/AN11/RP41/SDA1/RB9        | S1PGC1/S1RP41/S1SDA1/S1RB9                                              |

| 23    | Vss                            | Vss                                                                     |

| 24    | VDD                            | Vdd                                                                     |

| 25    | TMS/RP42/PWM3H/RB10            | S1RP42/S1PWM3H/S1RB10                                                   |

| 26    | TCK/RP43/PWM3L/RB11            | S1RP43/S1PWM8H/S1PWM3L/S1RB11                                           |

| 27    | TDI/RP44/PWM2H/RB12            | S1RP44/S1PWM2H/S1RB12                                                   |

| 28    | RP45/PWM2L/RB13                | S1RP45/S1PWM7H/S1PWM2L/S1RB13                                           |

Legend: RPn and S1RPn represent remappable pins for Peripheral Pin Select functions.

## **Table of Contents**

| 1.0   | Device Overview                                                       | 21    |

|-------|-----------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers | 29    |

| 3.0   | Master Modules                                                        | 35    |

| 4.0   | Slave Modules                                                         |       |

| 5.0   | Master Slave Interface (MSI)                                          | . 417 |

| 6.0   | Oscillator with High-Frequency PLL                                    | . 431 |

| 7.0   | Power-Saving Features (Master and Slave)                              | . 471 |

| 8.0   | Direct Memory Access (DMA) Controller                                 |       |

| 9.0   | High-Resolution PWM (HSPWM) with Fine Edge Placement                  |       |

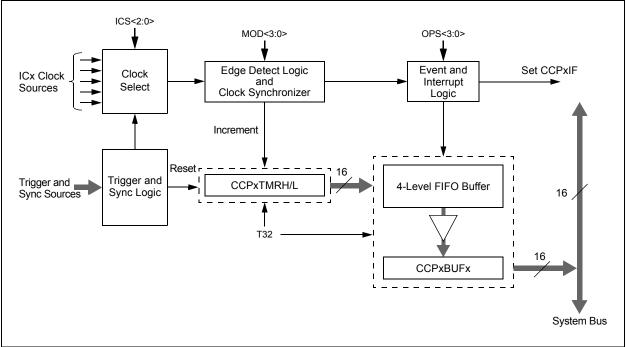

| 10.0  | Capture/Compare/PWM/Timer Modules (SCCP)                              | . 535 |

| 11.0  | High-Speed Analog Comparator with Slope Compensation DAC              | . 553 |

| 12.0  | Quadrature Encoder Interface (QEI) (Master/Slave)                     |       |

| 13.0  | Universal Asynchronous Receiver Transmitter (UART)                    | . 583 |

| 14.0  | Serial Peripheral Interface (SPI)                                     |       |

| 15.0  | Inter-Integrated Circuit (I <sup>2</sup> C)                           | . 623 |

| 16.0  | Single-Edge Nibble Transmission (SENT)                                | . 633 |

|       | Timer1                                                                |       |

|       | Configurable Logic Cell (CLC)                                         |       |

| 19.0  | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator           | . 659 |

| 20.0  | Current Bias Generator (CBG)                                          | . 663 |

| 21.0  | Special Features                                                      | . 667 |

| 22.0  | Instruction Set Summary                                               | . 713 |

| 23.0  | Development Support                                                   | . 723 |

| 24.0  | Electrical Characteristics                                            | . 727 |

| 25.0  | Packaging Information                                                 | . 767 |

| Appe  | ndix A: Revision History                                              | . 791 |

| Index |                                                                       | 793   |

| The M | /licrochip Web Site                                                   | . 803 |

| Custo | mer Change Notification Service                                       | . 803 |

| Custo | mer Support                                                           | . 803 |

| Produ | Ict Identification System                                             | . 805 |

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 3.2 "Master Memory Organization" and Section 4.2 "Slave Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33CH128MP508 Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33CH128MP508 devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

Figure 1-2 shows a general block diagram of the cores and peripheral modules of the Master and Slave. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

The Master core and Slave core can operate independently, and can be programmed and debugged separately during the application development. Both processor (Master and Slave) subsystems have their own interrupt controllers, clock generators, ICD, port logic, I/O MUXes and PPS. The device is equivalent to having two complete dsPIC<sup>®</sup> DSCs on a single die.

The Master core will execute the code from Program Flash Memory (PFM) and the Slave core will operate from Program RAM Memory (PRAM). Once the code development is complete, the Master Flash will be programmed with the Master code, as well as the Slave code. After a Power-on Reset (POR), the Slave code from Master Flash will be loaded to the PRAM (program memory of the Slave) and the Slave can execute the code independently of the Master. The Master and Slave can communicate with each other using the Master Slave Interface (MSI) peripheral, and can exchange data between them.

Figure 1-1 shows the block diagram of the device operation during a POR and the process of transferring the Slave code from the Master to Slave PRAM.

The I/O ports are shared between the Master and Slave. Table 1 shows the number of peripherals and the shared peripherals that the Master and Slave own. There are Configuration bits in the Flash memory that specify the ownership (Master or Slave) of each device pin.

The default (erased) state of the Flash assigns all of the device pins to the Master.

The two cores (Master and Slave) can both be connected to debug tools, which support independent and simultaneous debugging. When the Slave core or <u>Master core</u> is debugged (non-Dual Debug mode), the S1MCLRx is not used. MCLR is used for programming and <u>debugging</u> both the Master core and the Slave core. S1MCLRx is only used when debugging both the cores at the same time.

In normal operation, the "owner" of a device pin is responsible for full control of that pin; this includes both the digital and analog functionality.

The pin owner's GPIO registers control all aspects of the I/O pad, including the ANSELx, CNPUx, CNPDx, ODCx registers and slew rate control.

**Note:** Both the Master and Slave cores can monitor a pin as an input, regardless of pin ownership. Pin ownership is valid only for the output functionality of the port.

| Register              | Address | All Resets                              | Register | Address | All Resets                              | Register | Address | All Resets                              |

|-----------------------|---------|-----------------------------------------|----------|---------|-----------------------------------------|----------|---------|-----------------------------------------|

| I/O Ports (Continued) |         |                                         | CNCONB   | E2A     | 00                                      | LATD     | E5A     | *****                                   |

| ANSELA                | E00     | 11111                                   | CNEN0B   | E2C     | 000000000000000000000000000000000000000 | ODCD     | E5C     | 000000000000000000000000000000000000000 |

| TRISA                 | E02     | 11111                                   | CNSTATB  | E2E     | 000000000000000000000000000000000000000 | CNPUD    | E5E     | 000000000000000000000000000000000000000 |

| PORTA                 | E04     | xxxxx                                   | CNEN1B   | E30     | 000000000000000000000000000000000000000 | CNPDD    | E60     | 0000000000000000000                     |

| LATA                  | E06     | xxxxx                                   | CNFB     | E32     | 000000000000000000000000000000000000000 | CNCOND   | E62     | 00                                      |

| ODCA                  | E08     | 00000                                   | ANSELC   | E38     | 11111                                   | CNEN0D   | E64     | 0000000000000000000                     |

| CNPUA                 | E0A     | 00000                                   | TRISC    | E3A     | 111111111111111111                      | CNSTATD  | E66     | 0000000000000000000                     |

| CNPDA                 | E0C     | 00000                                   | PORTC    | E3C     | *****                                   | CNEN1D   | E68     | 0000000000000000000                     |

| CNCONA                | E0E     | 00                                      | LATC     | E3E     | *****                                   | CNFD     | E6A     | 0000000000000000000                     |

| CNEN0A                | E10     | 00000                                   | ODCC     | E40     | 000000000000000000000000000000000000000 | TRISE    | E72     | 111111111111111111                      |

| CNSTATA               | E12     | 00000                                   | CNPUC    | E42     | 000000000000000000000000000000000000000 | PORTE    | E74     | *****                                   |

| CNEN1A                | E14     | 00000                                   | CNPDC    | E44     | 000000000000000000000000000000000000000 | LATE     | E76     | *****                                   |

| CNFA                  | E16     | 00000                                   | CNCONC   | E46     | 00                                      | ODCE     | E78     | 0000000000000000000                     |

| ANSELB                | E1C     | 1111111                                 | CNEN0C   | E48     | 000000000000000000000000000000000000000 | CNPUE    | E7A     | 0000000000000000000                     |

| TRISB                 | E1E     | 111111111111111111                      | CNSTATC  | E4A     | 000000000000000000000000000000000000000 | CNPDE    | E7C     | 0000000000000000000                     |

| PORTB                 | E20     | *****                                   | CNEN1C   | E4C     | 000000000000000000000000000000000000000 | CNCONE   | E7E     | 00                                      |

| LATB                  | E22     | *****                                   | CNFC     | E4E     | 000000000000000000000000000000000000000 | CNEN0E   | E80     | 0000000000000000000                     |

| ODCB                  | E24     | 000000000000000000000000000000000000000 | ANSELD   | E54     | 1                                       | CNSTATE  | E82     | 0000000000000000000                     |

| CNPUB                 | E26     | 000000000000000000000000000000000000000 | TRISD    | E56     | 11111111111111111                       | CNEN1E   | E84     | 0000000000000000000                     |

| CNPDB                 | E28     | 000000000000000000000000000000000000000 | PORTD    | E58     | *****                                   | CNFE     | E86     | 000000000000000000000000000000000000000 |

## TABLE 3-17: MASTER SFR BLOCK E00h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address and Reset values are in hexadecimal and binary, respectively.

## 3.2.7 MODULO ADDRESSING

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 3.2.7.1 Start and End Address

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 3-4).

| Note: | Y space Modulo Addressing EA calcula- |  |  |  |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|--|--|--|

|       | tions assume word-sized data (LSb of  |  |  |  |  |  |  |  |

|       | every EA is always clear).            |  |  |  |  |  |  |  |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 3.2.7.2 W Address Register Selection

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags, as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W (XWM) register, to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 3.2.1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W (YWM) register, to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit (MODCON<14>) is set.

### FIGURE 3-10: MODULO ADDRESSING OPERATION EXAMPLE

| Byte<br>Address |                                                                   | MOV<br>MOV<br>MOV | #0x1100, W0<br>W0, XMODSRT<br>#0x1163, W0 | ;set modulo start address     |

|-----------------|-------------------------------------------------------------------|-------------------|-------------------------------------------|-------------------------------|

| 0x1100          |                                                                   | MOV<br>MOV        | #0x1105, W0<br>W0, MODEND<br>#0x8001, W0  | ;set modulo end address       |

|                 |                                                                   | MOV               | W0, MODCON                                | ;enable W1, X AGU for modulo  |

|                 | ↓ ( )                                                             | MOV               | #0x0000, W0                               | ;WO holds buffer fill value   |

| 0x1163          |                                                                   | MOV               | #0x1110, W1                               | ;point Wl to buffer           |

|                 |                                                                   | DO                | AGAIN, #0x31                              | ;fill the 50 buffer locations |

|                 | , ,                                                               | MOV               | WO, [W1++]                                | ;fill the next location       |

|                 | Start Addr = 0x1100<br>End Addr = 0x1163<br>Length = 0x0032 words | AGAIN:            | INC W0, WO                                | ;increment the fill value     |

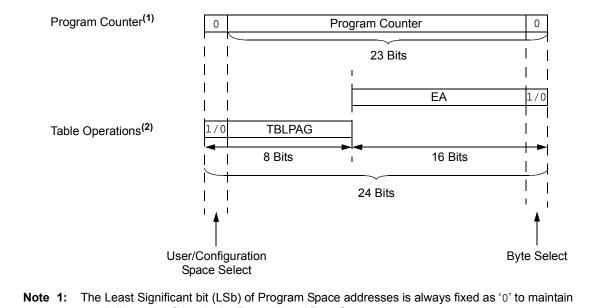

# 3.2.9 INTERFACING PROGRAM AND DATA MEMORY SPACES

The dsPIC33CH128MP508 family architecture uses a 24-bit wide Program Space (PS) and a 16-bit wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33CH128MP508 family devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## TABLE 3-22: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address         |              |                     |               |     |  |  |

|------------------------|---------------|-------------------------------|--------------|---------------------|---------------|-----|--|--|

| Access Type            | Space         | <23>                          | <22:16>      | <15>                | <14:1>        | <0> |  |  |

| Instruction Access     | User          | 0                             | 0 PC<22:1> 0 |                     |               |     |  |  |

| (Code Execution)       |               | 0xxx xxxx xxxx xxxx xxxx xxxx |              |                     |               |     |  |  |

| TBLRD/TBLWT            | User          | TBLPAG<7:0>                   |              |                     | Data EA<15:0> |     |  |  |

| (Byte/Word Read/Write) |               | 02                            | xxx xxxx     | XXXX XXXX XXXX XXXX |               |     |  |  |

|                        | Configuration | TBLPAG<7:0>                   |              | Data EA<15:0>       |               |     |  |  |

|                        |               |                               |              | XXXX XXXX XXXX XXXX |               |     |  |  |

#### FIGURE 3-12: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

- word alignment of data in the Program and Data Spaces.2: Table operations are not required to be word-aligned. Table Read operations are permitted in the

- Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

#### REGISTER 3-51: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| R/W-0      | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |  |  |

|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|

| QEIHOM1R7  | QEIHOM1R6 | QEIHOM1R5 | QEIHOM1R4 | QEIHOM1R3 | QEIHOM1R2 | QEIHOM1R1 | QEIHOM1R0 |  |  |

| bit 15 bit |           |           |           |           |           |           |           |  |  |

| R/W-0       | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |  |  |

|-------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|

| QEINDX1R7   | QEINDX1R6 | QEINDX1R5 | QEINDX1R4 | QEINDX1R3 | QEINDX1R2 | QEINDX1R1 | QEINDX1R0 |  |  |

| bit 7 bit 0 |           |           |           |           |           |           |           |  |  |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

bit 15-8 **QEIHOM1R<7:0>:** Assign QEI Home 1 Input (QEIHOM1) to the Corresponding RPn Pin bits See Table 3-30.

### REGISTER 3-52: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| U1DSRR7 | U1DSRR6 | U1DSRR5 | U1DSRR4 | U1DSRR3 | U1DSRR2 | U1DSRR1 | U1DSRR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| U1RXR7 | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 **U1DSRR<7:0>:** Assign UART1 Data-Set-Ready (U1DSR) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **U1RXR<7:0>:** Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **QEINDX1R<7:0>:** Assign QEI Index 1 Input (QEINDX1) to the Corresponding RPn Pin bits See Table 3-30.

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —      | _   | RP181R5 <sup>(1)</sup> | RP181R4 <sup>(1)</sup> | RP181R3 <sup>(1)</sup> | RP181R2 <sup>(1)</sup> | RP181R1 <sup>(1)</sup> | RP181R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —     | —   | RP180R5 <sup>(1)</sup> | RP180R4 <sup>(1)</sup> | RP180R3 <sup>(1)</sup> | RP180R2 <sup>(1)</sup> | RP180R1 <sup>(1)</sup> | RP180R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

| bit 13-8 | <b>RP181R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP181 Output Pin bits (see Table 3-33 for peripheral function numbers) |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                                 |

bit 5-0 **RP180R<5:0>:** Peripheral Output Function is Assigned to RP180 Output Pin bits (see Table 3-33 for peripheral function numbers)

Note 1: These are virtual output ports.

## 4.2.5.3 Move and Accumulator Instructions

Move instructions, and the DSP accumulator class of instructions, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing<br>mode specified in the instruction can differ<br>for the source and destination EA. How-<br>ever, the 4-bit Wb (Register Offset) field is |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                      |

|       | shared by both source and destination (but                                                                                                                                           |

|       | typically only used by one).                                                                                                                                                         |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.2.5.4 MAC Instructions

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.2.5.5 Other Instructions

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

#### 4.3.7 SLAVE PROGRAM MEMORY CONTROL/STATUS REGISTERS

....

#### REGISTER 4-4: NVMCON: PROGRAM MEMORY SLAVE CONTROL REGISTER

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0                  | R/C-0                   | R/C-0                   | R/W-0                   | R/C-0                   |  |  |

|-----------------------|----------------------|----------------------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--|--|

| WR                    | WREN                 | WRERR                | NVMSIDL <sup>(2)</sup> | SFTSWP                  | P2ACTIV                 | RPDF                    | URERR                   |  |  |

| bit 15                | bit 15 bit 8         |                      |                        |                         |                         |                         |                         |  |  |

|                       |                      |                      |                        |                         |                         |                         |                         |  |  |

| U-0                   | U-0                  | U-0                  | U-0                    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    |  |  |

| _                     | _                    | _                    | —                      | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4)</sup> |  |  |

| bit 7                 |                      |                      |                        |                         |                         |                         | bit 0                   |  |  |

| Legend:           | C = Clearable bit | SO = Settable Only bit | SO = Settable Only bit |  |  |  |  |

|-------------------|-------------------|------------------------|------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'            |  |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown     |  |  |  |  |

| bit 15  | WR: Write Control bit <sup>(1)</sup>                                                                                                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Initiates a PRAM memory program or erase operation; the operation is self-timed and the bit is<br/>cleared by hardware once the operation is complete</li> </ul>         |

|         | 0 = Program or erase operation is complete and inactive                                                                                                                               |

| bit 14  | WREN: Write Enable bit <sup>(1)</sup>                                                                                                                                                 |

|         | <ul> <li>1 = Enables program/erase operations</li> <li>0 = Inhibits program/erase operations</li> </ul>                                                                               |

| bit 13  | WRERR: Write Sequence Error Flag bit <sup>(1)</sup>                                                                                                                                   |

|         | <ul> <li>1 = An improper program or erase sequence attempt, or termination has occurred (bit is set automatically<br/>on any set attempt of the WR bit)</li> </ul>                    |

|         | 0 = The program or erase operation completed normally                                                                                                                                 |

| bit 12  | NVMSIDL: PRAM Stop in Idle Control bit <sup>(2)</sup>                                                                                                                                 |

|         | <ul> <li>1 = PRAM voltage regulator goes into Standby mode during Idle mode</li> <li>0 = PRAM voltage regulator is active during Idle mode</li> </ul>                                 |

| bit 11  | SFTSWP: Soft Swap Status bit                                                                                                                                                          |

|         | <ul> <li>1 = Panels have been successfully swapped using the BOOTSWP instruction</li> <li>0 = Awaiting for panels to be successfully swapped using the BOOTSWP instruction</li> </ul> |

| bit 10  | P2ACTIV: Dual Boot Active Region Status bit                                                                                                                                           |

|         | <ul> <li>1 = Panel 2 PRAM is mapped into the active region</li> <li>0 = Panel 1 PRAM is mapped into the active region</li> </ul>                                                      |

| bit 9   | RPDF: Row Programming Data Format bit                                                                                                                                                 |

|         | <ul> <li>1 = Row data to be stored in PRAM is in compressed format</li> <li>0 = Row data to be stored in PRAM is in uncompressed format</li> </ul>                                    |

| bit 8   | URERR: Row Programming Data Underrun Error bit                                                                                                                                        |

|         | <ul> <li>1 = Indicates row programming operation has been terminated</li> <li>0 = No data underrun error is detected</li> </ul>                                                       |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                            |

| Note 1: | These bits can only be reset on a POR.                                                                                                                                                |

| 2:      | If this bit is set, there will be minimal power savings (IIDLE) and upon exiting Idle mode, there is a delay (TVREG) before PRAM memory becomes operational.                          |

| 3:      | All other combinations of NVMOP<3:0> are unimplemented.                                                                                                                               |

- 4: Execution of the PWRSAV instruction is ignored while any of the NVM operations are in progress.

- 5: Two adjacent words on a 4-word boundary are programmed during execution of this operation.

| Register | Bit 15    | Bit 14    | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     |

|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| RPCONL   | —         | —         | —         | —         | IOLOCK    | —         | —         | —         | —         | —         | —         | —         | _         | —         | —         | _         |

| RPINR0   | INT1R7    | INT1R6    | INT1R5    | INT1R4    | INT1R3    | INT1R2    | INT1R1    | INT1R0    |           | —         | _         |           |           |           | —         | —         |

| RPINR1   | INT3R7    | INT3R6    | INT3R5    | INT3R4    | INT3R3    | INT3R2    | INT3R1    | INT3R0    | INT2R7    | INT2R6    | INT2R5    | INT2R4    | INT2R3    | INT2R2    | INT2R1    | INT2R0    |

| RPINR2   | T1CKR7    | T1CKR6    | T1CKR5    | T1CKR4    | T1CKR3    | T1CKR2    | T1CKR1    | T1CKR0    |           | —         | _         |           |           |           | —         | —         |

| RPINR3   | ICM1R7    | ICM1R6    | ICM1R5    | ICM1R4    | ICM1R3    | ICM1R2    | ICM1R1    | ICM1R0    | TCKI1R7   | TCKI1R6   | TCKI1R5   | TCKI1R4   | TCKI1R3   | TCKI1R2   | TCKI1R1   | TCKI1R0   |

| RPINR4   | ICM2R7    | ICM2R6    | ICM2R5    | ICM2R4    | ICM2R3    | ICM2R2    | ICM2R1    | ICM2R0    | TCKI2R7   | TCKI2R6   | TCKI2R5   | TCKI2R4   | TCKI2R3   | TCKI2R2   | TCKI2R1   | TCKI2R0   |

| RPINR5   | ICM3R7    | ICM3R6    | ICM3R5    | ICM3R4    | ICM3R3    | ICM3R2    | ICM3R1    | ICM3R0    | TCKI3R7   | TCKI3R6   | TCKI3R5   | TCKI3R4   | TCKI3R3   | TCKI3R2   | TCKI3R1   | TCKI3R0   |

| RPINR6   | ICM4R7    | ICM4R6    | ICM4R5    | ICM4R4    | ICM4R3    | ICM4R2    | ICM4R1    | ICM4R0    | TCKI4R7   | TCKI4R6   | TCKI4R5   | TCKI4R4   | TCKI4R3   | TCKI4R2   | TCKI4R1   | TCKI4R0   |

| RPINR11  | OCFBR7    | OCFBR6    | OCFBR5    | OCFBR4    | OCFBR3    | OCFBR2    | OCFBR1    | OCFBR0    | OCFAR7    | OCFAR6    | OCFAR5    | OCFAR4    | OCFAR3    | OCFAR2    | OCFAR1    | OCFAR0    |

| RPINR12  | PCI9R7    | PCI9R6    | PCI9R5    | PCI9R4    | PCI9R3    | PCI9R2    | PCI9R1    | PCI9R0    | PCI8R7    | PCI8R6    | PCI8R5    | PCI8R4    | PCI8R3    | PCI8R2    | PCI8R1    | PCI8R0    |

| RPINR13  | PCI11R7   | PCI11R6   | PCI11R5   | PCI11R4   | PCI11R3   | PCI11R2   | PCI11R1   | PCI11R0   | PCI10R7   | PCI10R6   | PCI10R5   | PCI10R4   | PCI10R3   | PCI10R2   | PCI10R1   | PCI10R0   |

| RPINR14  | QEIB1R7   | QEIB1R6   | QEIB1R5   | QEIB1R4   | QEIB1R3   | QEIB1R2   | QEIB1R1   | QEIB1R0   | QEIA1R7   | QEIA1R6   | QEIA1R5   | QEIA1R4   | QEIA1R3   | QEIA1R2   | QEIA1R1   | QEIA1R0   |

| RPINR15  | QEIHOM1R7 | QEIHOM1R6 | QEIHOM1R5 | QEIHOM1R4 | QEIHOM1R3 | QEIHOM1R2 | QEIHOM1R1 | QEIHOM1R0 | QEINDX1R7 | QEINDX1R6 | QEINDX1R5 | QEINDX1R4 | QEINDX1R3 | QEINDX1R2 | QEINDX1R1 | QEINDX1R0 |

| RPINR18  | U1DSRR7   | U1DSRR6   | U1DSRR5   | U1DSRR4   | U1DSRR3   | U1DSRR2   | U1DSRR1   | U1DSRR0   | U1RXR7    | U1RXR6    | U1RXR5    | U1RXR4    | U1RXR3    | U1RXR2    | U1RXR1    | U1RXR0    |

| RPINR20  | SCK1R7    | SCK1R6    | SCK1R5    | SCK1R4    | SCK1R3    | SCK1R2    | SCK1R1    | SCK1R0    | SDI1R7    | SDI1R6    | SDI1R5    | SDI1R4    | SDI1R3    | SDI1R2    | SDI1R1    | SDI1R0    |

| RPINR21  | REFOIR7   | REFOIR6   | REFOIR5   | REFOIR4   | REFOIR3   | REFOIR2   | REFOIR1   | REFOIR0   | SS1R7     | SS1R6     | SS1R5     | SS1R4     | SS1R3     | SS1R2     | SS1R1     | SS1R0     |

| RPINR23  | U1CTSR7   | U1CTSR6   | U1CTSR5   | U1CTSR4   | U1CTSR3   | U1CTSR2   | U1CTSR1   | U1CTSR0   | -         | —         | _         | -         | -         | _         | _         | —         |

| RPINR37  | PCI17R7   | PCI17R6   | PCI17R5   | PCI17R4   | PCI17R3   | PCI17R2   | PCI17R1   | PCI17R0   | _         | _         | _         | _         | _         | _         | _         | _         |

| RPINR38  | _         | _         | _         | _         | _         | _         | _         | _         | PCI18R7   | PCI18R6   | PCI18R5   | PCI18R4   | PCI18R3   | PCI18R2   | PCI18R1   | PCI18R0   |

| RPINR42  | PCI13R7   | PCI13R6   | PCI13R5   | PCI13R4   | PCI13R3   | PCI13R2   | PCI13R1   | PCI13R0   | PCI12R7   | PCI12R6   | PWM12R5   | PWM12R4   | PWM12R3   | PWM12R2   | PWM12R1   | PWM12R0   |

| RPINR43  | PCI15R7   | PCI15R6   | PCI15R5   | PCI15R4   | PCI15R3   | PCI15R2   | PCI15R1   | PCI15R0   | PCI14R7   | PCI14R6   | PCI14R5   | PCI14R4   | PCI14R3   | PCI14R2   | PCI14R1   | PCI14R0   |

| RPINR44  | _         | _         | _         | _         | _         | _         | _         | _         | PCI16R7   | PCI16R6   | PCI16R5   | PCI16R4   | PCI16R3   | PCI16R2   | PCI16R1   | PCI16R0   |

| RPINR45  | CLCINAR7  | CLCINAR6  | CLCINAR5  | CLCINAR4  | CLCINAR3  | CLCINAR2  | CLCINAR1  | CLCINAR0  | _         | _         | _         | —         | _         | —         | _         | —         |

| RPINR46  | CLCINCR7  | CLCINCR6  | CLCINCR5  | CLCINCR4  | CLCINCR3  | CLCINCR2  | CLCINCR1  | CLCINCR0  | CLCINBR7  | CLCINBR6  | CLCINBR5  | CLCINBR4  | CLCINBR3  | CLCINBR2  | CLCINBR1  | CLCINBR0  |

| RPINR47  | ADCTRGR7  | ADCTRGR6  | ADCTRGR5  | ADCTRGR4  | ADCTRGR3  | ADCTRGR2  | ADCTRGR1  | ADCTRGR0  | CLCINDR7  | CLCINDR6  | CLCINDR5  | CLCINDR4  | CLCINDR3  | CLCINDR2  | CLCINDR1  | CLCINDR0  |

|          |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |

## TABLE 4-29: SLAVE PPS INPUT CONTROL REGISTERS

## 6.3 Slave Oscillator Configuration Registers

Table 6-2 lists the configuration settings that select the device's Slave core oscillator source and operating mode at a POR.

| Oscillator<br>Source | Oscillator Mode                               | S1FNOSC<2:0><br>Value | POSCMD<1:0><br>Value <sup>(3)</sup> | Notes |

|----------------------|-----------------------------------------------|-----------------------|-------------------------------------|-------|

| S0                   | Fast RC Oscillator (FRC)                      | 000                   | xx                                  | 1     |

| S1                   | Fast RC Oscillator with PLL (FRCPLL)          | 001                   | XX                                  | 1     |

| S2                   | Primary Oscillator (EC)                       | 010                   | 00                                  | 1     |

| S2                   | Primary Oscillator (XT)                       | 010                   | 01                                  |       |

| S2                   | Primary Oscillator (HS)                       | 010                   | 10                                  |       |

| S3                   | Primary Oscillator with PLL (ECPLL)           | 011                   | 00                                  | 1     |

| S3                   | Primary Oscillator with PLL (XTPLL)           | 011                   | 01                                  |       |

| S3                   | Primary Oscillator with PLL (HSPLL)           | 011                   | 10                                  |       |

| S4                   | Reserved                                      | 100                   | xx                                  | 1     |

| S5                   | Low-Power RC Oscillator (LPRC)                | 101                   | xx                                  | 1     |

| S6                   | Backup FRC (BFRC)                             | 110                   | XX                                  | 1     |

| S7                   | Fast RC Oscillator with + N Divider (FRCDIVN) | 111                   | xx                                  | 1, 2  |

#### TABLE 6-2: CONFIGURATION BIT VALUES FOR CLOCK SELECTION FOR THE SLAVE

**Note 1:** The OSCO pin function is determined by the S1OSCIOFNC Configuration bit. If both the Master core OSCIOFNC and Slave core S1OSCIOFNC bits are set, the Master core OSCIOFNC bit has priority.

2: This is the default oscillator mode for an unprogrammed (erased) device.

**3:** The POSCMD<1:0> bits are only available in the Master Oscillator Configuration register, FOSC. This setting configures the Primary Oscillator for use by either core.

## REGISTER 6-15: PLLDIV: PLL OUTPUT DIVIDER REGISTER (SLAVE)

| U-0                                                                        | U-0                                                                                                                                                                                              | U-0              | U-0             | U-0                         | U-0            | R/W-0             | R/W-0          |  |  |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-----------------------------|----------------|-------------------|----------------|--|--|--|

| _                                                                          | —                                                                                                                                                                                                | —                | —               | — — VCODIV<1:0>             |                |                   |                |  |  |  |

| bit 15                                                                     |                                                                                                                                                                                                  | -                |                 |                             |                |                   | bit            |  |  |  |

|                                                                            |                                                                                                                                                                                                  |                  |                 |                             |                |                   |                |  |  |  |

| U-0                                                                        | R/W-1                                                                                                                                                                                            | R/W-0            | R/W-0           | U-0                         | R/W-0          | R/W-0             | R/W-1          |  |  |  |

| —                                                                          | – POST1DIV<2:0> <sup>(1,2)</sup> – POST2DIV<2:0> <sup>(1,2)</sup>                                                                                                                                |                  |                 |                             |                |                   |                |  |  |  |

| bit 7                                                                      |                                                                                                                                                                                                  |                  |                 |                             |                |                   | bit            |  |  |  |

|                                                                            |                                                                                                                                                                                                  |                  |                 |                             |                |                   |                |  |  |  |

| Legend:                                                                    |                                                                                                                                                                                                  |                  |                 |                             |                |                   |                |  |  |  |

| R = Readabl                                                                | le bit                                                                                                                                                                                           | W = Writable     | bit             | U = Unimple                 | emented bit, r | ead as '0'        |                |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                                                                                                                                                                  |                  |                 |                             |                |                   |                |  |  |  |

|                                                                            |                                                                                                                                                                                                  |                  |                 |                             |                |                   |                |  |  |  |

| bit 15-10                                                                  | Unimpleme                                                                                                                                                                                        | nted: Read as '  | )'              |                             |                |                   |                |  |  |  |

| bit 9-8                                                                    | VCODIV<1:0                                                                                                                                                                                       | )>: PLL VCO Ou   | utput Divider S | Select bits                 |                |                   |                |  |  |  |

|                                                                            | 11 = Fvco                                                                                                                                                                                        |                  |                 |                             |                |                   |                |  |  |  |

|                                                                            | 10 = Fvco/2<br>01 = Fvco/3                                                                                                                                                                       |                  |                 |                             |                |                   |                |  |  |  |

|                                                                            | 01 = FVCO/3<br>00 = FVCO/4                                                                                                                                                                       |                  |                 |                             |                |                   |                |  |  |  |

| bit 7                                                                      | Unimpleme                                                                                                                                                                                        | nted: Read as '  | )'              |                             |                |                   |                |  |  |  |

| bit 6-4                                                                    | •                                                                                                                                                                                                | 2:0>: PLL Outpu  |                 | Ratio bits <sup>(1,2)</sup> |                |                   |                |  |  |  |

|                                                                            |                                                                                                                                                                                                  |                  |                 |                             | POST1DIVx v    | alue should be    | greater than o |  |  |  |

|                                                                            |                                                                                                                                                                                                  |                  |                 | ·                           |                | to operate at hig | 0              |  |  |  |

|                                                                            | than the POS                                                                                                                                                                                     | ST2DIVx divider  | -               |                             |                |                   |                |  |  |  |

| bit 3                                                                      | Unimpleme                                                                                                                                                                                        | nted: Read as '  | כי              |                             |                |                   |                |  |  |  |

| bit 2-0                                                                    | POST2DIV<                                                                                                                                                                                        | 2:0>: PLL Output | ut Divider #2 F | Ratio bits <sup>(1,2)</sup> |                |                   |                |  |  |  |

|                                                                            | POST2DIV<2:0> can have a valid value, from 1 to 7 (POST2DIVx value should be less than or equal to the POST1DIVx value). The POST1DIVx divider is designed to operate at higher clock rates than |                  |                 |                             |                |                   |                |  |  |  |

the POST2DIVx divider.

- Note 1: The POST1DIVx and POST2DIVx divider values must not be changed while the PLL is operating.

- 2: The default values for POST1DIVx and POST2DIVx are 4 and 1, respectively, yielding a 150 MHz system source clock.

## 7.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification on the I/O ports or peripherals that use an External Clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into standby when Sleep mode is entered by clearing the VREGS (RCON<8>) bit.

## 7.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 7.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the SIDL bit in the Timer1 Control register (T1CON<13>).

#### 7.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

| R/W-0        | R/W-0                                                                                                                                                               | R/W-0                                                                                                                                                              | R/W-0                                                                                                                                        | U-0                                           | U-0                               | U-0                     | U-0                     |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------|-------------------------|-------------------------|--|--|--|

| EVTyOE       | N EVTyPOL                                                                                                                                                           | EVTySTRD                                                                                                                                                           | EVTySYNC                                                                                                                                     | —                                             |                                   | —                       | —                       |  |  |  |

| bit 15       |                                                                                                                                                                     | •                                                                                                                                                                  |                                                                                                                                              | •                                             |                                   |                         | bit 8                   |  |  |  |

|              |                                                                                                                                                                     |                                                                                                                                                                    |                                                                                                                                              |                                               |                                   |                         |                         |  |  |  |

| R/W-0        | R/W-0                                                                                                                                                               | R/W-0                                                                                                                                                              | R/W-0                                                                                                                                        | U-0                                           | R/W-0                             | R/W-0                   | R/W-0                   |  |  |  |

| EVTySEL      | 3 EVTySEL2                                                                                                                                                          | EVTySEL1                                                                                                                                                           | EVTySEL0                                                                                                                                     | _                                             | EVTyPGS2(2)                       | EVTyPGS1 <sup>(2)</sup> | EVTyPGS0 <sup>(2)</sup> |  |  |  |

| bit 7        |                                                                                                                                                                     |                                                                                                                                                                    |                                                                                                                                              |                                               |                                   |                         | bit 0                   |  |  |  |

|              |                                                                                                                                                                     |                                                                                                                                                                    |                                                                                                                                              |                                               |                                   |                         |                         |  |  |  |

| Legend:      |                                                                                                                                                                     |                                                                                                                                                                    |                                                                                                                                              |                                               |                                   |                         |                         |  |  |  |

| R = Readat   |                                                                                                                                                                     | W = Writable                                                                                                                                                       |                                                                                                                                              | •                                             | mented bit, read                  | d as '0'                |                         |  |  |  |

| -n = Value a | at POR                                                                                                                                                              | '1' = Bit is set                                                                                                                                                   |                                                                                                                                              | '0' = Bit is cle                              | eared                             | x = Bit is unkn         | own                     |  |  |  |

| bit 15       | 1 = Event ou                                                                                                                                                        | WM Event Out<br>tput signal is o<br>tput signal is ir                                                                                                              | utput on PWM                                                                                                                                 |                                               |                                   |                         |                         |  |  |  |

| bit 14       | <ul> <li>0 = Event output signal is internal only</li> <li>EVTyPOL: PWM Event Output Polarity bit</li> <li>1 = Event output signal is active-low</li> </ul>         |                                                                                                                                                                    |                                                                                                                                              |                                               |                                   |                         |                         |  |  |  |

| oit 13       | <ul> <li>0 = Event output signal is active-high</li> <li>EVTySTRD: PWM Event Output Stretch Disable bit</li> </ul>                                                  |                                                                                                                                                                    |                                                                                                                                              |                                               |                                   |                         |                         |  |  |  |

| 511 15       | •                                                                                                                                                                   |                                                                                                                                                                    | •                                                                                                                                            |                                               |                                   |                         |                         |  |  |  |

|              |                                                                                                                                                                     | <ul> <li>1 = Event output signal pulse width is not stretched</li> <li>0 = Event output signal is stretched to 8 PWM clock cycles minimum<sup>(1)</sup></li> </ul> |                                                                                                                                              |                                               |                                   |                         |                         |  |  |  |

| oit 12       | EVTySYNC: PWM Event Output Sync bit                                                                                                                                 |                                                                                                                                                                    |                                                                                                                                              |                                               |                                   |                         |                         |  |  |  |

|              | 0 = Event ou                                                                                                                                                        | tput signal is s<br>tput is not sync<br>signal pulse wi                                                                                                            | chronized to th                                                                                                                              | e system cloo                                 |                                   | and EVTvSTRD            | ) = 1                   |  |  |  |

| bit 11-8     | -                                                                                                                                                                   | ted: Read as '                                                                                                                                                     | -                                                                                                                                            |                                               |                                   |                         | 1.                      |  |  |  |

| bit 7-4      | -                                                                                                                                                                   | 0>: PWM Ever                                                                                                                                                       |                                                                                                                                              | s                                             |                                   |                         |                         |  |  |  |

|              | 1111 = High-<br>1110-1010 =<br>1001 = ADC<br>1000 = ADC<br>0111 = STEE<br>0110 = CAH/<br>0101 = PCI F<br>0100 = PCI C<br>0011 = PCI F<br>0010 = PCI S<br>0011 = PWM | resolution erro                                                                                                                                                    | r event signal<br>al<br>lable in Push-F<br>ailable in Cente<br>put signal<br>ive output sign<br>tive output sig<br>put signal<br>tput signal | Pull Output me<br>er-Aligned mo<br>nal<br>nal | odes only) <sup>(4)</sup>         |                         |                         |  |  |  |

| bit 3        |                                                                                                                                                                     | ted: Read as '                                                                                                                                                     | -                                                                                                                                            |                                               |                                   |                         |                         |  |  |  |