Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit Dual-Core                                                                  |

| Speed                      | 180MHz, 200MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 39                                                                                |

| Program Memory Size        | 152KB (152K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                       |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 20K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 31x12b; D/A 4x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

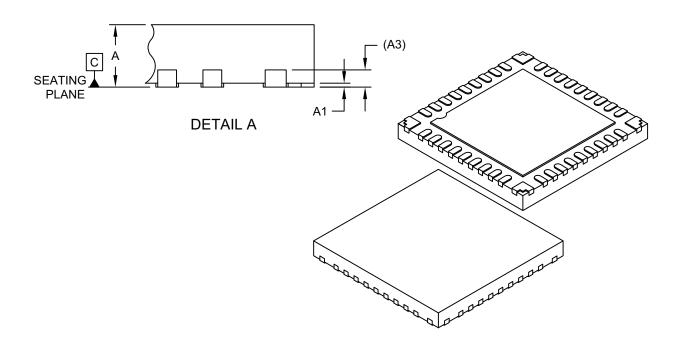

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-TQFP                                                                           |

| Supplier Device Package    | 48-TQFP (7x7)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch128mp205t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Advanced Analog Features**

- · Four ADC Modules:

- One module for Master core

- Three modules for Slave core

- 12-bit, 3.5 Msps ADC

- Up to 18 conversion channels

- Four DAC/Analog Comparator Modules:

- One module for Master core

- Three modules for Slave core

- 12-bit DACs with hardware slope compensation

- 15 ns analog comparators

- Three PGA Modules:

- Three modules for Slave core

- Can be read by Master ADC

- Option to interface with Master ADC

- Shared DAC/Analog Output:

- DAC/analog comparator outputs

- PGA outputs

## **Communication Interfaces**

- Three UART Modules:

- Two modules for Master core

- One module for Slave core

- Support for DMX, LIN/J2602 protocols and  $\ensuremath{\text{IrDA}}^{\ensuremath{\mathbb{R}}}$

- Three 4-Wire SPI/I<sup>2</sup>S Modules:

- Two modules for Master core

- One module for Slave core

- CAN Flexible Data-Rate (FD) Module for the Master Core

- Three I<sup>2</sup>C Modules:

- Two modules for Master

- One module for Slave

- Support for SMBus

### **Other Features**

- · PPS to Allow Function Remap

- Programmable Cyclic Redundancy Check (CRC) for the Master

- Two SENT Modules for the Master

## **Direct Memory Access (DMA)**

- Eight DMA Channels:

- Six DMA channels available for the Master core

- Two DMA channels available for the Slave core

#### **Debugger Development Support**

- In-Circuit and In-Application Programming

- Simultaneous Debugging Support for Master and Slave Cores

- Master Only Debug and Slave Only Debug Support

- Master with Three Complex, Five Simple Breakpoints and Slave with One Complex, Two Simple Breakpoints

- IEEE 1149.2 Compatible (JTAG) Boundary Scan

- Trace Buffer and Run-Time Watch

## **Safety Features**

- DMT (Deadman Timer)

- ECC (Error Correcting Code)

- WDT (Watchdog Timer)

- CodeGuard<sup>™</sup> Security

- CRC (Cyclic Redundancy Check)

- Two-Speed Start-up

- Fail-Safe Clock Monitoring

- Backup FRC (BFRC)

- · Capless Internal Voltage Regulator

- · Virtual Pins for Redundancy and Monitoring

#### 3.2 Master Memory Organization

Note: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33CH128MP508 family architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

#### 3.2.1 PROGRAM ADDRESS SPACE

The program address memory space of the dsPIC33CH128MP508 family devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 3.2.9 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to permit access to calibration data and Device ID sections of the configuration memory space.

The program memory maps for the Master dsPIC33CHXXXMPX08 device are shown in Figure 3-3 and Figure 3-4.

#### FIGURE 3-3: PROGRAM MEMORY MAP FOR MASTER dsPIC33CH128MPXXX DEVICES<sup>(1)</sup>

| <b>≜</b>                  | GOTO Instruction                                   | 0x000000             |

|---------------------------|----------------------------------------------------|----------------------|

|                           | Reset Address                                      | 0x000002             |

| Ð                         | Interrupt Vector Table                             | 0x000004<br>0x0001FE |

| Jser Memory Space         | User Program<br>Flash Memory<br>(44K instructions) | 0x000200<br>0x015EFE |

| r Mem                     | Device Configuration                               | 0x015F00<br>0x015FFE |

| Use                       | Unimplemented<br>(Read '0's)                       | 0x016000             |

| Ť                         | Reserved                                           | 0x800000<br>0x800FFE |

|                           | Calibration Data <sup>(2,3)</sup>                  | 0x801000             |

| pace                      | User OTP Memory                                    | 0x8016FC<br>0x801700 |

| Comiguration Memory Space | Reserved                                           | 0x8017FE<br>0x801800 |

|                           | Write Latches                                      | 0xF9FFFE<br>0xFA0000 |

| ligurat                   |                                                    | 0xFA0002<br>0xFA0004 |

| Con                       | Reserved                                           |                      |

|                           | DEVID                                              | 0xFEFFFE<br>0xFF0000 |

|                           |                                                    | 0xFF0002<br>0xFF0004 |

| <b>↓</b>                  | Reserved                                           | 0xFFFFFE             |

Note 1: Memory areas are not shown to scale.

- 2: Calibration data area must be maintained during programming.

- **3:** Calibration data area includes UDID locations.

# 3.2.6 INSTRUCTION ADDRESSING MODES

The addressing modes shown in Table 3-20 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 3.2.6.1 File Register Instructions

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 3.2.6.2 MCU Instructions

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 3-20: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

#### TABLE 3-23: MASTER INTERRUPT VECTOR DETAILS (CONTINUED)

|                                      | Vector IRQ |       | Interrupt Bit Location |          |          |              |

|--------------------------------------|------------|-------|------------------------|----------|----------|--------------|

| Interrupt Source                     | #          | #     | IVT Address            | Flag     | Enable   | Priority     |

| QEI1 – QEI Position Counter Compare  | 56         | 48    | 0x000074               | IFS3<0>  | IEC3<0>  | IPC12<2:0>   |

| U1E – UART1 Error                    | 57         | 49    | 0x000076               | IFS3<1>  | IEC3<1>  | IPC12<6:4>   |

| U2E – UART2 Error                    | 58         | 50    | 0x000078               | IFS3<2>  | IEC3<2>  | IPC12<10:8>  |

| CRC – CRC Generator                  | 59         | 51    | 0x00007A               | IFS3<3>  | IEC3<3>  | IPC12<14:12> |

| C1TX – CAN1 TX Data Request          | 60         | 52    | 0x00007C               | IFS3<4>  | IEC3<4>  | IPC13<2:0>   |

| Reserved                             | 61-68      | 53-68 | 0x00007E-0x00008C      | —        | _        | _            |

| ICD – In-Circuit Debugger            | 69         | 61    | 0x00008E               | IFS3<13> | IEC3<13> | IPC15<6:4>   |

| JTAG – JTAG Programming              | 70         | 62    | 0x000090               | IFS3<14> | IEC3<14> | IPC15<10:8>  |

| PTGSTEP – PTG Step                   | 71         | 63    | 0x000092               | IFS3<15> | IEC3<15> | IPC15<14:12> |

| I2C1BC – I2C1 Bus Collision          | 72         | 64    | 0x000094               | IFS4<0>  | IEC4<0>  | IPC16<2:0>   |

| I2C2BC – I2C2 Bus Collision          | 73         | 65    | 0x000096               | IFS4<1>  | IEC4<1>  | IPC16<6:4>   |

| Reserved                             | 74         | 66    | 0x000098               | —        | _        | _            |

| PWM1 – PWM Generator 1               | 75         | 67    | 0x00009A               | IFS4<3>  | IEC4<3>  | IPC16<14:12> |

| PWM2 – PWM Generator 2               | 76         | 68    | 0x00009C               | IFS4<4>  | IEC4<4>  | IPC17<2:0>   |

| PWM3 – PWM Generator 3               | 77         | 69    | 0x00009E               | IFS4<5>  | IEC4<5>  | IPC17<6:4>   |

| PWM4 – PWM Generator 4               | 78         | 70    | 0x0000A0               | IFS4<6>  | IEC4<6>  | IPC17<10:8>  |

| Reserved                             | 79-82      | 71-74 | 0x0000A2               | —        | _        | _            |

| CND – Change Notice D                | 83         | 75    | 0x0000AA               | IFS4<11> | IEC4<11> | IPC18<14:12> |

| CNE – Change Notice E                | 84         | 76    | 0x0000AC               | IFS4<12> | IEC4<12> | IPC19<2:0>   |

| CMP1 – Comparator 1                  | 85         | 77    | 0x0000AE               | IFS4<13> | IEC4<13> | IPC19<6:4>   |

| Reserved                             | 86-88      | 78-80 | 0x0000B0-0x0000B4      | _        | _        | —            |

| PTGWDT – PTG Watchdog Timer Time-out | 89         | 81    | 0x0000B6               | IFS5<1>  | IEC5<1>  | IPC20<6:4>   |

| PTG0 – PTG Trigger 0                 | 90         | 82    | 0x0000B8               | IFS5<2>  | IEC5<2>  | IPC20<10:8>  |

| PTG1 – PTG Trigger 1                 | 91         | 83    | 0x0000BA               | IFS5<3>  | IEC5<3>  | IPC20<14:12> |

| PTG2 – PTG Trigger 2                 | 92         | 84    | 0x0000BC               | IFS5<4>  | IEC5<4>  | IPC21<2:0>   |

| PTG3 – PTG Trigger 3                 | 93         | 85    | 0x0000BE               | IFS5<5>  | IEC5<6>  | IPC21<6:4>   |

| SENT1 – SENT1 TX/RX                  | 94         | 86    | 0x0000C0               | IFS5<6>  | IEC5<6>  | IPC21<10:8>  |

| SENT1E – SENT1 Error                 | 95         | 87    | 0x0000C2               | IFS5<7>  | IEC5<7>  | IPC21<14:12> |

| SENT2 – SENT2 TX/RX                  | 96         | 88    | 0x0000C4               | IFS5<8>  | IEC5<8>  | IPC22<2:0>   |

| SENT2E – SENT2 Error                 | 97         | 89    | 0x0000C6               | IFS5<9>  | IEC5<9>  | IPC22<6:4>   |

| ADC – ADC Global Interrupt           | 98         | 90    | 0x0000C8               | IFS5<10> | IEC5<10> | IPC22<10:8>  |

| ADCAN0 – ADC AN0 Interrupt           | 99         | 91    | 0x0000CA               | IFS5<11> | IEC5<11> | IPC22<14:12> |

| ADCAN1 – ADC AN1 Interrupt           | 100        | 92    | 0x0000CC               | IFS5<12> | IEC5<12> | IPC23<2:0>   |

| ADCAN2 – ADC AN2 Interrupt           | 101        | 93    | 0x0000CE               | IFS5<13> | IEC5<13> | IPC23<6:4>   |

| ADCAN3 – ADC AN3 Interrupt           | 102        | 94    | 0x0000D0               | IFS5<14> | IEC5<14> | IPC23<10:8>  |

| ADCAN4 – ADC AN4 Interrupt           | 103        | 95    | 0x0000D2               | IFS5<15> | IEC5<15> | IPC23<14:12> |

| ADCAN5 – ADC AN5 Interrupt           | 104        | 96    | 0x0000D4               | IFS6<0>  | IEC6<0>  | IPC24<2:0>   |

| ADCAN6 – ADC AN6 Interrupt           | 105        | 97    | 0x0000D6               | IFS6<1>  | IEC6<1>  | IPC24<6:4>   |

| ADCAN7 – ADC AN7 Interrupt           | 106        | 98    | 0x0000D8               | IFS6<2>  | IEC6<2>  | IPC24<10:8>  |

| ADCAN8 – ADC AN8 Interrupt           | 107        | 99    | 0x0000DA               | IFS6<3>  | IEC6<3>  | IPC24<14:12> |

| ADCAN9 – ADC AN9 Interrupt           | 108        | 100   | 0x0000DC               | IFS6<4>  | IEC6<4>  | IPC25<2:0>   |

| ADCAN10 – ADC AN10 Interrupt         | 109        | 101   | 0x0000DE               | IFS6<5>  | IEC6<5>  | IPC25<6:4>   |

| ADCAN11 – ADC AN11 Interrupt         | 110        | 102   | 0x0000E0               | IFS6<6>  | IEC6<6>  | IPC25<10:8>  |

| ADCAN12 – ADC AN12 Interrupt         | 111        | 103   | 0x0000E2               | IFS6<7>  | IEC6<7>  | IPC25<14:12> |

| ADCAN13 – ADC AN13 Interrupt         | 112        | 100   | 0x0000E4               | IFS6<8>  | IEC6<8>  | IPC26<2:0>   |

| ADCAN14 – ADC AN14 Interrupt         | 112        | 104   | 0x0000E6               | IFS6<9>  | IEC6<9>  | IPC26<6:4>   |

| ADCAN15 – ADC AN15 Interrupt         | 110        | 106   | 0x0000E8               | IFS6<10> | IEC6<10> | IPC26<10:8>  |

| R/W-0                 | U-0                                                                           | R/W-0                                                          | R/W-0                      | R/W-0                    | R/W-1            | R/W-1          | R/W-1                 |  |  |  |

|-----------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------|--------------------------|------------------|----------------|-----------------------|--|--|--|

| CON                   | —                                                                             | SIDL                                                           | BRSDIS                     | BUSY                     | WFT1             | WFT0           | WAKFIL <sup>(1)</sup> |  |  |  |

| bit 15                |                                                                               |                                                                |                            |                          |                  |                | bit 8                 |  |  |  |

| R/W-0                 | R/W-1                                                                         | R/W-1                                                          | R/W-0                      | R/W-0                    | R/W-0            | R/W-0          | R/W-0                 |  |  |  |

| CLKSEL <sup>(1)</sup> | PXEDIS <sup>(1)</sup>                                                         | ISOCRCEN <sup>(1)</sup>                                        | DNCNT4                     | DNCNT3                   | DNCNT2           | DNCNT1         | DNCNT0                |  |  |  |

| bit 7                 |                                                                               |                                                                |                            | 1                        |                  |                | bit 0                 |  |  |  |

| Legend:               |                                                                               |                                                                |                            |                          |                  |                |                       |  |  |  |

| R = Readable          | bit                                                                           | W = Writable bit                                               |                            | U = Unimpler             | mented bit, read | d as '0'       |                       |  |  |  |

| -n = Value at F       | POR                                                                           | '1' = Bit is set                                               |                            | '0' = Bit is cle         | ared             | x = Bit is unk | nown                  |  |  |  |

| bit 15                | CON: CAN E                                                                    | nable bit                                                      |                            |                          |                  |                |                       |  |  |  |

|                       | 1 = CAN mod                                                                   | ule is enabled<br>ule is disabled                              |                            |                          |                  |                |                       |  |  |  |

| bit 14                | Unimplemen                                                                    | ted: Read as '0'                                               |                            |                          |                  |                |                       |  |  |  |

| bit 13                | SIDL: CAN S                                                                   | top in Idle Contro                                             | l bit                      |                          |                  |                |                       |  |  |  |

|                       |                                                                               | dule operation in<br>stop module ope                           |                            | mode                     |                  |                |                       |  |  |  |

| bit 12                |                                                                               | Rate Switching (E                                              | ,                          |                          |                  |                |                       |  |  |  |

|                       |                                                                               | Switching is disab<br>Switching depend                         |                            |                          |                  | ssage object   |                       |  |  |  |

| bit 11                |                                                                               | Nodule is Busy bi                                              | t                          |                          |                  |                |                       |  |  |  |

|                       |                                                                               | module is active<br>module is inactiv                          | e                          |                          |                  |                |                       |  |  |  |

| bit 10-9              |                                                                               | electable Wake-ι                                               | ip Filter Time             | e bits                   |                  |                |                       |  |  |  |

|                       | 11 = T11FILTE<br>10 = T10FILTE<br>01 = T01FILTE<br>00 = T00FILTE              | R                                                              |                            |                          |                  |                |                       |  |  |  |

| bit 8                 | WAKFIL: Ena                                                                   | able CAN Bus Lin                                               | e Wake-up F                | ilter bit <sup>(1)</sup> |                  |                |                       |  |  |  |

|                       |                                                                               | N bus line filter fo<br>line filter is not us                  |                            | ·up                      |                  |                |                       |  |  |  |

| bit 7                 | CLKSEL: Mo                                                                    | dule Clock Sourc                                               | e Select bit <sup>(1</sup> | )                        |                  |                |                       |  |  |  |

|                       |                                                                               | selected as the selected as the selected as the sol            |                            |                          |                  |                |                       |  |  |  |

| bit 6                 | <b>PXEDIS:</b> Protocol Exception Event Detection Disabled bit <sup>(1)</sup> |                                                                |                            |                          |                  |                |                       |  |  |  |

|                       | 1 = Protocol E                                                                | eserved bit" follo<br>Exception is treat<br>col Exception is d | ed as a form               | error                    |                  |                |                       |  |  |  |

| bit 5                 |                                                                               | Enable ISO CRC                                                 |                            |                          |                  | gotato         |                       |  |  |  |

|                       | 1 = Includes s                                                                | stuff bit count in C<br>include stuff bit c                    | RC field and               | l uses non-zer           |                  |                | all zeros             |  |  |  |

| bit 4-0               | DNCNT<4:0>                                                                    | : DeviceNet™ Fi                                                | lter Bit Numb              | er bits                  |                  |                |                       |  |  |  |

|                       |                                                                               | 1 = Invalid select<br>pares up to Data                         |                            |                          | s of data with E | ID)            |                       |  |  |  |

|                       |                                                                               | pares up to Data<br>s not compare da                           |                            | with EID0                |                  |                |                       |  |  |  |

#### REGISTER 3-103: C1CONL: CAN CONTROL REGISTER LOW

**Note 1:** These bits can only be modified in Configuration mode (OPMOD<2:0> = 100).

## REGISTER 3-120: C1RXOVIFH: CAN RECEIVE OVERFLOW INTERRUPT STATUS REGISTER HIGH<sup>(1)</sup>

| R-0             | R-0 | R-0              | R-0    | R-0                 | R-0         | R-0                | R-0   |

|-----------------|-----|------------------|--------|---------------------|-------------|--------------------|-------|

|                 |     |                  | RFOVIF | <31:24>             |             |                    |       |

| bit 15          |     |                  |        |                     |             |                    | bit 8 |

|                 |     |                  |        |                     |             |                    |       |

| R-0             | R-0 | R-0              | R-0    | R-0                 | R-0         | R-0                | R-0   |

|                 |     |                  | RFOVIF | <23:16>             |             |                    |       |

| bit 7           |     |                  |        |                     |             |                    | bit 0 |

|                 |     |                  |        |                     |             |                    |       |

| Legend:         |     |                  |        |                     |             |                    |       |

| R = Readable I  | bit | W = Writable bit |        | U = Unimplemen      | ted bit, re | ad as '0'          |       |

| -n = Value at P | OR  | '1' = Bit is set |        | '0' = Bit is cleare | d           | x = Bit is unknowr | 1     |

bit 15-0 RFOVIF<31:16>: Unimplemented

Note 1: C1RXOVIFH: FIFO: RFOVIFx (flag needs to be cleared in the FIFO register).

#### REGISTER 3-121: C1RXOVIFL: CAN RECEIVE OVERFLOW INTERRUPT STATUS REGISTER LOW<sup>(1)</sup>

| R-0                                | R-0 | R-0 | R-0              | R-0            | R-0            | R-0  | R-0   |

|------------------------------------|-----|-----|------------------|----------------|----------------|------|-------|

|                                    |     |     | RFOV             | ′IF<15:8>      |                |      |       |

| bit 15                             |     |     |                  |                |                |      | bit 8 |

|                                    |     |     |                  |                |                |      |       |

| R-0                                | R-0 | R-0 | R-0              | R-0            | R-0            | R-0  | U-0   |

|                                    |     | I   | RFOVIF<7:1       | >              |                |      | —     |

| bit 7                              |     |     |                  |                |                |      | bit ( |

| Legend:                            |     |     |                  |                |                |      |       |

| R = Readable bit W = Writable bit  |     | oit | U = Unimpler     | nented bit, re | ad as '0'      |      |       |

| -n = Value at POR '1' = Bit is set |     |     | '0' = Bit is cle | ared           | x = Bit is unk | nown |       |

bit 15-8 **RFOVIF<15:8>:** Unimplemented

bit 7-1 **RFOVIF<7:1>:** Receive FIFO Overflow Interrupt Pending bits

1 = Interrupt is pending

0 = Interrupt is not pending

bit 0 Unimplemented: Read as '0'

Note 1: C1RXOVIFL: FIFO: RFOVIFx (flag needs to be cleared in the FIFO register).

## REGISTER 3-139: C1FIFOUAHx: CAN FIFO USER ADDRESS REGISTER x (x = 1 TO 7) HIGH<sup>(1)</sup>

| R-x     | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|---------|-----|-----|--------|---------|-----|-----|-------|

|         |     |     | FIFOUA | <31:24> |     |     |       |

| bit 15  |     |     |        |         |     |     | bit 8 |

|         |     |     |        |         |     |     |       |

| R-x     | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|         |     |     | FIFOUA | <23:16> |     |     |       |

| bit 7   |     |     |        |         |     |     | bit 0 |

|         |     |     |        |         |     |     |       |

| Legend: |     |     |        |         |     |     |       |

| Legenu.           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

bit 15-0

FIFOUA<31:16>: FIFO User Address bits

TXEN = 1 (FIFO configured as a transmit buffer):

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0 (FIFO configured as a receive buffer):

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

#### **REGISTER 3-140:** C1FIFOUALX: CAN FIFO USER ADDRESS REGISTER x (x = 1 TO 7) $LOW^{(1)}$

| R-x             | R-x | R-x              | R-x    | R-x                 | R-x          | R-x                | R-x   |

|-----------------|-----|------------------|--------|---------------------|--------------|--------------------|-------|

|                 |     |                  | FIFOUA | \<15:8>             |              |                    |       |

| bit 15          |     |                  |        |                     |              |                    | bit 8 |

|                 |     |                  |        |                     |              |                    |       |

| R-x             | R-x | R-x              | R-x    | R-x                 | R-x          | R-x                | R-x   |

|                 |     |                  | FIFOU  | A<7:0>              |              |                    |       |

| bit 7           |     |                  |        |                     |              |                    | bit 0 |

|                 |     |                  |        |                     |              |                    |       |

| Legend:         |     |                  |        |                     |              |                    |       |

| R = Readable I  | bit | W = Writable bit |        | U = Unimpleme       | nted bit, re | ad as '0'          |       |

| -n = Value at P | OR  | '1' = Bit is set |        | '0' = Bit is cleare | ed           | x = Bit is unknowr | ı     |

bit 15-0

FIFOUA<15:0>: FIFO User Address bits

TXEN = 1 (FIFO configured as a transmit buffer):

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0 (FIFO configured as a receive buffer):

A read of this register will return the address where the next message is to be read (FIFO tail).

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

### 4.6.5.4 Input Mapping

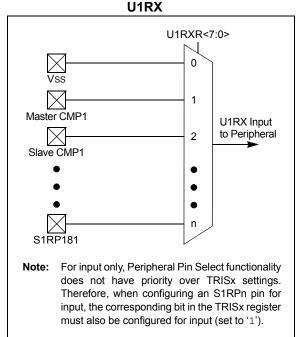

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 4-36 through Register 4-59). Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit index value maps the S1RPn pin with the corresponding value, or internal signal, to that peripheral. See Table 4-27 for a list of available inputs.

For example, Figure 4-18 illustrates remappable pin selection for the U1RX input.

## FIGURE 4-18: REMAPPABLE INPUT FOR

#### 4.7.3 ADC CONTROL/STATUS REGISTERS

#### REGISTER 4-83: ADCON1L: ADC CONTROL REGISTER 1 LOW

| R/W-0               | U-0 | R/W-0  | U-0 | r-0 | U-0 | U-0 | U-0   |

|---------------------|-----|--------|-----|-----|-----|-----|-------|

| ADON <sup>(1)</sup> | —   | ADSIDL | —   | r   | —   | —   | —     |

| bit 15              |     |        |     |     |     |     | bit 8 |

|                     |     |        |     |     |     |     |       |

| U-0                 | U-0 | U-0    | U-0 | U-0 | U-0 | U-0 | U-0   |

| —                   | —   | —      | —   | —   | —   | —   | —     |

| bit 7               |     |        |     |     |     |     | bit 0 |

|                     |     |        |     |     |     |     |       |

| Legend:           | r = Reserved bit |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 11<br>bit 10-0 | Reserved: Maintain as '0'<br>Unimplemented: Read as '0'                                                                                 |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 12             | Unimplemented: Read as '0'                                                                                                              |

|                    | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |

| bit 13             | ADSIDL: ADC Stop in Idle Mode bit                                                                                                       |

| bit 14             | Unimplemented: Read as '0'                                                                                                              |

| bit 15             | ADON: ADC Enable bit <sup>(1)</sup><br>1 = ADC module is enabled<br>0 = ADC module is off                                               |

**Note 1:** Set the ADON bit only after the ADC module has been configured. Changing ADC Configuration bits when ADON = 1 will result in unpredictable behavior.

x = Bit is unknown

'1' = Bit is set

| HS/R/W-0                           | U-0 | U-0            | U-0            | U-0                                | r-0 | R/W-0  | R/W-0   |

|------------------------------------|-----|----------------|----------------|------------------------------------|-----|--------|---------|

| CSHRRDY                            | _   | —              | —              | —                                  | —   | CSHREN | CSHRRUN |

| bit 15                             |     |                |                |                                    |     |        | bit 8   |

|                                    |     |                |                |                                    |     |        |         |

| U-0                                | U-0 | U-0            | U-0            | U-0                                | U-0 | U-0    | U-0     |

| —                                  | —   | —              | —              | _                                  | —   | —      | —       |

| bit 7                              |     |                |                |                                    |     |        | bit 0   |

|                                    |     |                |                |                                    |     |        |         |

| Legend: HS = Hardware Settable bit |     |                | e Settable bit | r = Reserved                       | bit |        |         |

| R = Readable                       | bit | W = Writable b | bit            | U = Unimplemented bit, read as '0' |     |        |         |

|                                    |     |                |                |                                    |     |        |         |

'0' = Bit is cleared

| bit 15    | CSHRRDY: Shared ADC Core Calibration Status Flag bit                                                      |

|-----------|-----------------------------------------------------------------------------------------------------------|

|           | 1 = Shared ADC core calibration is finished                                                               |

|           | 0 = Shared ADC core calibration is in progress                                                            |

| bit 14-11 | Unimplemented: Read as '0'                                                                                |

| bit 10    | Reserved: Maintain as '0'                                                                                 |

| bit 9     | CSHREN: Shared ADC Core Calibration Enable bit                                                            |

|           | 1 = Shared ADC core calibration bits (CSHRRDY and CSHRRUN) can be accessed by software                    |

|           | 0 = Shared ADC core calibration bits are disabled                                                         |

| bit 8     | CSHRRUN: Shared ADC Core Calibration Start bit                                                            |

|           | 1 = If this bit is set by software, the shared ADC core calibration cycle is started; this bit is cleared |

|           | automatically by hardware                                                                                 |

|           | 0 = Software can start the next calibration cycle                                                         |

| bit 7-0   | Unimplemented: Read as '0'                                                                                |

-n = Value at POR

| U-0     | U-0 | U-0 | U-0 | U-0    | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|--------|-----|-----|-------|

| —       | —   | —   | —   | —      | —   | —   |       |

| bit 15  |     | •   |     |        |     |     | bit 8 |

|         |     |     |     |        |     |     |       |

| U-0     | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

| —       | —   | —   | —   | REFOMD | —   |     | —     |

| bit 7   |     |     |     |        |     |     | bit 0 |

|         |     |     |     |        |     |     |       |

| Legend: |     |     |     |        |     |     |       |

|         |     |     |     |        |     |     |       |

#### REGISTER 7-5: PMD4: MASTER PERIPHERAL MODULE DISABLE 4 CONTROL REGISTER

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

bit 3 **REFOMD:** Reference Clock Module Disable bit

1 = Reference clock module is disabled

0 = Reference clock module is enabled

bit 2-0 Unimplemented: Read as '0'

# dsPIC33CH128MP508 FAMILY

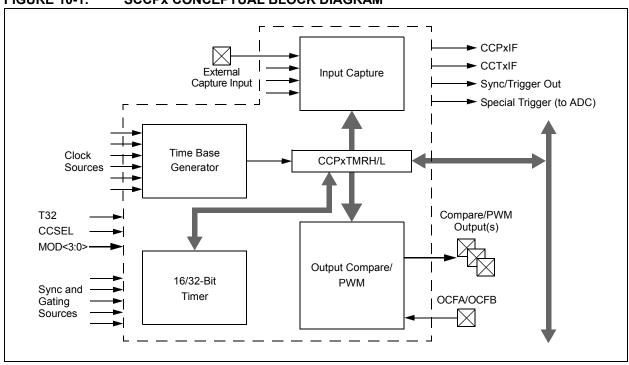

#### FIGURE 10-1: SCCPx CONCEPTUAL BLOCK DIAGRAM

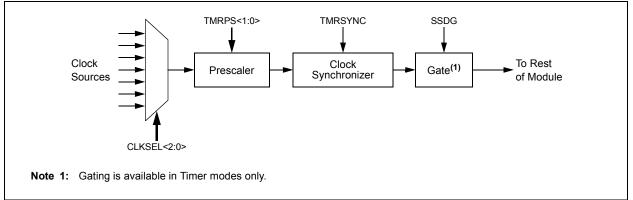

## 10.1 Time Base Generator

The Timer Clock Generator (TCG) generates a clock for the module's internal time base, using one of the clock signals already available on the microcontroller. This is used as the time reference for the module in its three major modes. The internal time base is shown in Figure 10-2. There are eight inputs available to the clock generator, which are selected using the CLKSEL<2:0> bits (CCPxCON1L<10:8>). Available sources include the FRC and LPRC, the Secondary Oscillator and the TCLKI External Clock inputs. The system clock is the default source (CLKSEL<2:0> = 000).

| R/W-0            | R/W-0                                                                                                                                                              | R/W-0                                                                                   | R/W-0                                                                               | U-0                                                                   | U-0                                           | U-0              | U-0         |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------|------------------|-------------|--|--|

| OETRIG           | OSCNT2                                                                                                                                                             | OSCNT1                                                                                  | OSCNT0                                                                              | —                                                                     | —                                             | —                |             |  |  |

| bit 15           |                                                                                                                                                                    |                                                                                         |                                                                                     |                                                                       |                                               |                  | bit         |  |  |

|                  |                                                                                                                                                                    |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

| U-0              | U-0                                                                                                                                                                | R/W-0                                                                                   | U-0                                                                                 | R/W-0                                                                 | R/W-0                                         | R/W-0            | R/W-0       |  |  |

| _                | —                                                                                                                                                                  | POLACE                                                                                  | —                                                                                   | PSSACE1                                                               | PSSACE0                                       | PSSBDF1          | PSSBDF0     |  |  |

| bit 7            |                                                                                                                                                                    |                                                                                         |                                                                                     |                                                                       |                                               |                  | bit         |  |  |

| Legend:          |                                                                                                                                                                    |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

| R = Readab       | ole bit                                                                                                                                                            | W = Writable                                                                            | bit                                                                                 | U = Unimplem                                                          | nented bit, read                              | l as '0'         |             |  |  |

| -n = Value a     | t POR                                                                                                                                                              | '1' = Bit is set                                                                        |                                                                                     | '0' = Bit is clea                                                     |                                               | x = Bit is unkr  | iown        |  |  |

|                  |                                                                                                                                                                    |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

| bit 15           | OETRIG: CCI                                                                                                                                                        | Px Dead-Time                                                                            | Select bit                                                                          |                                                                       |                                               |                  |             |  |  |

|                  | 1 = For Trigg                                                                                                                                                      | ered mode (TR                                                                           | IGEN = 1): Mo                                                                       | odule does not                                                        | drive enabled o                               | output pins unti | l triggered |  |  |

|                  | 0 = Normal o                                                                                                                                                       | utput pin opera                                                                         | tion                                                                                |                                                                       |                                               |                  |             |  |  |

| bit 14-12        | OSCNT<2:0>: One-Shot Event Count bits                                                                                                                              |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

|                  | 111 = Extends one-shot event by 7 time base periods (8 time base periods total)                                                                                    |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

|                  | 110 = Extends one-shot event by 6 time base periods (7 time base periods total)                                                                                    |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

|                  | 101 = Extends one-shot event by 5 time base periods (6 time base periods total)                                                                                    |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

|                  | 100 = Extends one-shot event by 4 time base periods (5 time base periods total)<br>011 = Extends one-shot event by 3 time base periods (4 time base periods total) |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

|                  | 010 = Extends one-shot event by 2 time base periods (3 time base periods total)                                                                                    |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

|                  |                                                                                                                                                                    |                                                                                         | •                                                                                   | ase period (2 tin                                                     | ne base period                                | s total)         |             |  |  |

|                  |                                                                                                                                                                    | ot extend one-                                                                          |                                                                                     | ent                                                                   |                                               |                  |             |  |  |

| bit 11-6         | •                                                                                                                                                                  | ted: Read as '                                                                          |                                                                                     |                                                                       |                                               |                  |             |  |  |

| bit 5            |                                                                                                                                                                    | •                                                                                       |                                                                                     | C and OCxE, Po                                                        | olarity Control I                             | bit              |             |  |  |

|                  |                                                                                                                                                                    | n polarity is acti<br>n polarity is acti                                                |                                                                                     |                                                                       |                                               |                  |             |  |  |

|                  | Unimplemen                                                                                                                                                         | ted: Read as '0                                                                         | )'                                                                                  |                                                                       |                                               |                  |             |  |  |

| bit 4            | <b>PSSACE&lt;1:0&gt;:</b> PWMx Output Pins, OCxA, OCxC and OCxE, Shutdown State Control bits                                                                       |                                                                                         |                                                                                     |                                                                       |                                               |                  |             |  |  |

| bit 4<br>bit 3-2 | PSSACE<1:0                                                                                                                                                         | >: PWMx Outp                                                                            | ut Pins, OCXA                                                                       | , OCXC and OC                                                         | JXE, SHULUOWH                                 | State Control    | bits        |  |  |

|                  |                                                                                                                                                                    |                                                                                         |                                                                                     | wn event occurs                                                       |                                               |                  | bits        |  |  |

|                  | 11 = Pins are<br>10 = Pins are                                                                                                                                     | driven active v<br>driven inactive                                                      | vhen a shutdov<br>when a shutd                                                      | wn event occurs<br>own event occu                                     | S<br>Irs                                      |                  | bits        |  |  |

| bit 3-2          | 11 = Pins are<br>10 = Pins are<br>0x = Pins are                                                                                                                    | driven active v<br>driven inactive<br>in high-impeda                                    | when a shutdow<br>when a shutd<br>ance state whe                                    | wn event occurs<br>own event occu<br>n a shutdown e                   | s<br>irs<br>event occurs                      |                  |             |  |  |

| bit 3-2          | 11 = Pins are<br>10 = Pins are<br>0x = Pins are<br><b>PSSBDF&lt;1:0</b>                                                                                            | driven active v<br>driven inactive<br>in high-impeda<br>>: PWMx Outp                    | when a shutdow<br>when a shutd<br>ance state whe<br>ut Pins, OCM>                   | wn event occurs<br>own event occu<br>n a shutdown e<br>kB, OCMxD, and | s<br>irs<br>event occurs<br>d OCMxF, Shu      |                  |             |  |  |

|                  | 11 = Pins are<br>10 = Pins are<br>0x = Pins are<br><b>PSSBDF&lt;1:0</b><br>11 = Pins are                                                                           | driven active v<br>driven inactive<br>in high-impeda<br>>: PWMx Outp<br>driven active v | when a shutdow<br>when a shutd<br>ance state whe<br>ut Pins, OCM><br>when a shutdow | wn event occurs<br>own event occu<br>n a shutdown e                   | s<br>irs<br>event occurs<br>d OCMxF, Shu<br>s |                  |             |  |  |

#### REGISTER 10-5: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

### 13.1 Architectural Overview

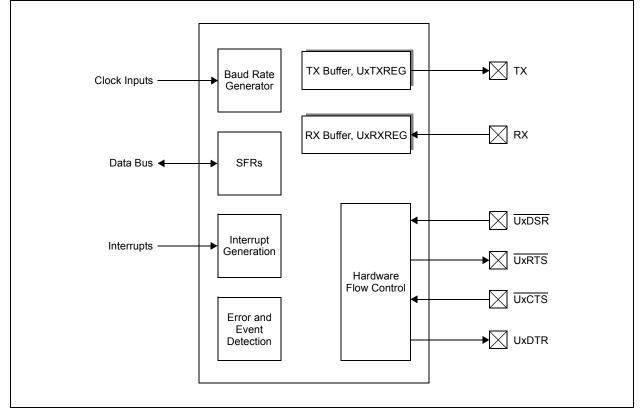

The UART transfers bytes of data, to and from device pins, using First-In First-Out (FIFO) buffers up to eight bytes deep. The status of the buffers and data is made available to user software through Special Function Registers (SFRs). The UART implements multiple interrupt channels for handling transmit, receive and error events. A simplified block diagram of the UART is shown in Figure 13-1.

## REGISTER 18-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER (CONTINUED)

| bit 3 | <b>G1D2T:</b> Gate 1 Data Source 2 True Enable bit<br>1 = Data Source 2 signal is enabled for Gate 1<br>0 = Data Source 2 signal is disabled for Gate 1 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | G1D2N: Gate 1 Data Source 2 Negated Enable bit                                                                                                          |

|       | 1 = Data Source 2 inverted signal is enabled for Gate 1<br>0 = Data Source 2 inverted signal is disabled for Gate 1                                     |

| bit 1 | G1D1T: Gate 1 Data Source 1 True Enable bit                                                                                                             |

|       | <ul><li>1 = Data Source 1 signal is enabled for Gate 1</li><li>0 = Data Source 1 signal is disabled for Gate 1</li></ul>                                |

| bit 0 | G1D1N: Gate 1 Data Source 1 Negated Enable bit                                                                                                          |

|       | <ul> <li>1 = Data Source 1 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 1 inverted signal is disabled for Gate 1</li> </ul>           |

### REGISTER 21-6: FWDT CONFIGURATION REGISTER

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R/PO-1 | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  |

|--------|---------|---------|---------|---------|---------|---------|---------|

| FWDTEN | SWDTPS4 | SWDTPS3 | SWDTPS2 | SWDTPS1 | SWDTPS0 | WDTWIN1 | WDTWIN0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| R/PO-1 | R/PO-1   | R/PO-1   | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  |

|--------|----------|----------|---------|---------|---------|---------|---------|

| WINDIS | RCLKSEL1 | RCLKSEL0 | RWDTPS4 | RWDTPS3 | RWDTPS2 | RWDTPS1 | RWDTPS0 |

| bit 7  |          |          |         |         |         |         | bit 0   |

| Legend: PO = Program Once bit |                  |                             |                    |

|-------------------------------|------------------|-----------------------------|--------------------|

| R = Readable bit              | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR             | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                 |

|-----------|----------------------------------------------------------------------------------------------------------------------------|

| bit 15    | FWDTEN: Watchdog Timer Enable bit                                                                                          |

|           | 1 = WDT is enabled in hardware                                                                                             |

|           | 0 = WDT controller via the ON bit (WDTCONL<15>)                                                                            |

| bit 14-10 | SWDTPS<4:0>: Sleep Mode Watchdog Timer Period Select bits                                                                  |

|           | 11111 = Divide by 2 ^ 30 = 1,073,741,824                                                                                   |

|           | 11110 = Divide by 2 ^ 29 = 526,870,912                                                                                     |

|           | 00001 = Divide by 2 ^ 2, 4                                                                                                 |

|           | 00000 = Divide by 2 ^ 1, 2                                                                                                 |

| bit 9-8   | WDTWIN<1:0>: Watchdog Timer Window Select bits                                                                             |

|           | 11 = WDT window is 25% of the WDT period                                                                                   |

|           | 10 = WDT window is 37.5% of the WDT period                                                                                 |

|           | 01 = WDT window is 50% of the WDT period<br>00 = WDT Window is 75% of the WDT period                                       |

| bit 7     | WINDIS: Watchdog Timer Window Enable bit                                                                                   |

| 2         | 1 = Watchdog Timer is in Non-Window mode                                                                                   |

|           | 0 = Watchdog Timer is in Window mode                                                                                       |

| bit 6-5   | RCLKSEL<1:0>: Watchdog Timer Clock Select bits                                                                             |

|           | 11 = LPRC clock                                                                                                            |

|           | 10 = Uses FRC when WINDIS = 0, system clock is not INTOSC/LPRC and device is not in Sleep;                                 |

|           | otherwise, uses INTOSC/LPRC<br>01 = Uses peripheral clock when system clock is not INTOSC/LPRC and device is not in Sleep; |

|           | otherwise, uses INTOSC/LPRC                                                                                                |

|           | 00 = Reserved                                                                                                              |

| bit 4-0   | RWDTPS<4:0>: Run Mode Watchdog Timer Period Select bits                                                                    |

|           | 11111 = Divide by 2 ^ 30 = 1,073,741,824                                                                                   |

|           | 11110 = Divide by 2 ^ 29 = 526,870,912                                                                                     |

|           | 00001 = Divide by 2 ^ 2, 4                                                                                                 |

|           | 00000 = Divide by 2 ^ 1, 2                                                                                                 |

|           |                                                                                                                            |

| REGISTER 21-18: | FMBXHS2 | CONFIGURATION | REGISTER |

|-----------------|---------|---------------|----------|

|-----------------|---------|---------------|----------|

| U-1           | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 |

|---------------|-----|-----|-----|-----|-----|-----|-----|

| —             | —   | —   | —   | —   | —   | —   | —   |

| bit 23 bit 16 |     |     |     |     |     |     |     |

| R/PO-1  |

|---------|---------|---------|---------|---------|---------|---------|---------|

| MBXHSH3 | MBXHSH2 | MBXHSH1 | MBXHSH0 | MBXHSG3 | MBXHSG2 | MBXHSG1 | MBXHSG0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/PO-1  |

|---------|---------|---------|---------|---------|---------|---------|---------|

| MBXHSF3 | MBXHSF2 | MBXHSF1 | MBXHSF0 | MBXHSE3 | MBXHSE2 | MBXHSE1 | MBXHSE0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | PO = Program Once bit |                            |                    |  |  |

|-------------------|-----------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, rea | ad as '0'          |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared       | x = Bit is unknown |  |  |

| bit 23-16 | Unimplemented: Read as '1'                                               |

|-----------|--------------------------------------------------------------------------|

| bit 15-12 | MBXHSH<3:0>: Mailbox Handshake Protocol Block H Register Assignment bits |

|           | 1111 = MSIxMBXD15 is assigned to Mailbox Handshake Protocol Block H      |

|           | •••                                                                      |

|           | 0001 = MSIxMBXD1 is assigned to Mailbox Handshake Protocol Block H       |

|           | 0000 = MSIxMBXD0 is assigned to Mailbox Handshake Protocol Block H       |

| bit 11-8  | MBXHSG<3:0>: Mailbox Handshake Protocol Block G Register Assignment bits |

|           | 1111 = MSIxMBXD15 is assigned to Mailbox Handshake Protocol Block G      |

|           |                                                                          |

|           | 0001 = MSIxMBXD1 is assigned to Mailbox Handshake Protocol Block G       |

|           | 0000 = MSIxMBXD0 is assigned to Mailbox Handshake Protocol Block G       |

| bit 7-4   | MBXHSF<3:0>: Mailbox Handshake Protocol Block F Register Assignment bits |

|           | 1111 = MSIxMBXD15 is assigned to Mailbox Handshake Protocol Block F      |

|           | •••                                                                      |

|           | 0001 = MSIxMBXD1 is assigned to Mailbox Handshake Protocol Block F       |

|           | 0000 = MSIxMBXD0 is assigned to Mailbox Handshake Protocol Block F       |

| bit 3-0   | MBXHSE<3:0>: Mailbox Handshake Protocol Block E Register Assignment bits |

|           | 1111 = MSIxMBXD15 is assigned to Mailbox Handshake Protocol Block E      |

|           |                                                                          |

|           | 0001 = MSIxMBXD1 is assigned to Mailbox Handshake Protocol Block E       |

|           | 0000 = MSIxMBXD0 is assigned to Mailbox Handshake Protocol Block E       |

#### TABLE 24-4: OPERATING VOLTAGE SPECIFICATIONS

| -            | -         | tions: 3.0V to 3.6V (unless other ature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Ind $-40^{\circ}C \le TA \le +125^{\circ}C$ for E | ustrial | ted) <sup>(1)</sup> |      |       |               |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|------|-------|---------------|

| Param<br>No. | Symbol    | Characteristic                                                                                                                       | Min.    | Тур.                | Max. | Units | Conditions    |

| Operati      | ng Voltag | e                                                                                                                                    |         |                     |      |       |               |

| DC10         | Vdd       | Supply Voltage                                                                                                                       | 3.0     | _                   | 3.6  | V     |               |

| DC12         | Vdr       | RAM Retention Voltage <sup>(2)</sup>                                                                                                 | 1.8     | _                   |      | V     |               |

| DC16         | VPOR      | <b>VDD Start Voltage</b><br>to Ensure Internal<br>Power-on Reset Signal                                                              | _       | _                   | Vss  | V     |               |

| DC17         | SVDD      | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal                                                                  | 1.0     | _                   | _    | V/ms  | 0V-3V in 3 ms |

| BO10         | VBOR      | BOR Event on VDD Transition<br>High-to-Low <sup>(3)</sup>                                                                            | 2.68    | 2.84                | 2.99 | V     |               |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC and comparators) may have degraded performance.

2: This is the limit to which VDD may be lowered and the RAM contents will always be retained.

**3:** Parameters are characterized but not tested.

|                                     |      | (Idle) +<br>(Sleep) | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |        |       |                         |  |  |

|-------------------------------------|------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------------------------|--|--|

| Parameter No.                       | Тур. | Max.                | Units Conditions                                                                                                                                                                                                                                                                        |        |       |                         |  |  |

| Idle Current (IIDLE) <sup>(1)</sup> |      |                     |                                                                                                                                                                                                                                                                                         |        |       |                         |  |  |

| DC40a                               | 6.6  | 8.4                 | mA                                                                                                                                                                                                                                                                                      | -40°C  |       | 10 MIPS (N = 1, N2 = 5, |  |  |

|                                     | 6.7  | 11.9                | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V  | N3 = 2, M = 50,         |  |  |

|                                     | 6.9  | 17.9                | mA                                                                                                                                                                                                                                                                                      | +85°C  | 5.5V  | Fvco = 400 MHz,         |  |  |