Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit Dual-Core                                                                  |

| Speed                      | 180MHz, 200MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 152KB (152K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                       |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 20K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 34x12b; D/A 4x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

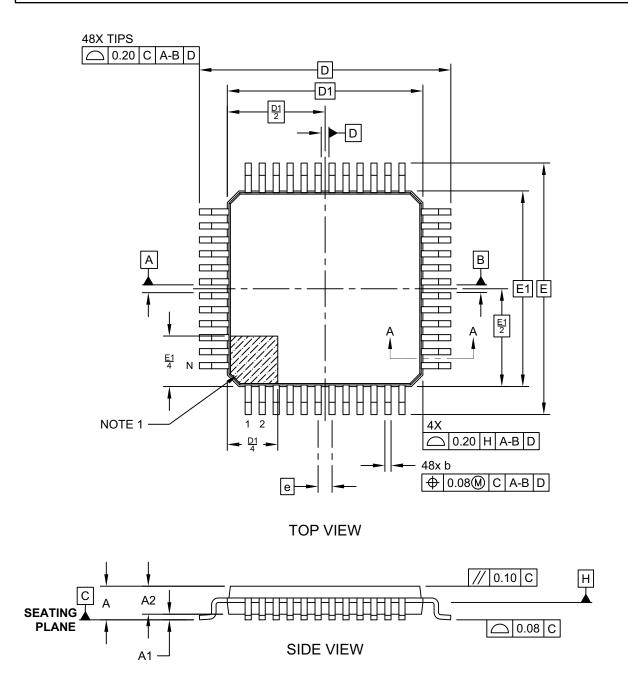

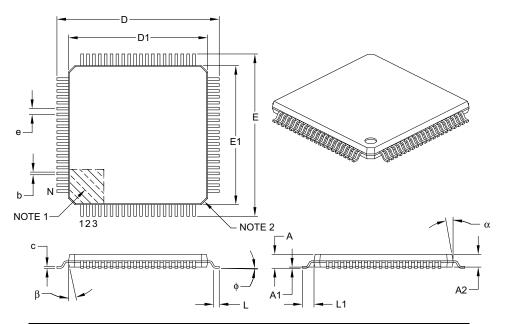

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch128mp206t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.5.5 INTERRUPT STATUS/CONTROL REGISTERS

#### REGISTER 3-16: SR: CPU STATUS REGISTER<sup>(1)</sup>

| OB SA                                             |                    |       |       |       |       |

|---------------------------------------------------|--------------------|-------|-------|-------|-------|

|                                                   | SB                 | OAB   | SAB   | DA    | DC    |

|                                                   |                    |       |       |       | bit 8 |

|                                                   |                    |       |       |       |       |

| W-0 <sup>(3)</sup> R/W-0                          | <sup>(3)</sup> R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| <sup>2</sup> L1 <sup>(2)</sup> IPL0 <sup>(2</sup> | 2) RA              | N     | OV    | Z     | С     |

|                                                   |                    | ż     | ·     |       | bit 0 |

|                                                   |                    |       |       |       |       |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11)

- 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

| R/W-0   | U-0   | R/W-0         | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|---------|-------|---------------|--------|---------------------|-----|-------|-------|

| VAR     | —     | US1           | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15  |       |               |        |                     |     |       | bit 8 |

|         |       |               |        |                     |     |       |       |

| R/W-0   | R/W-0 | R/W-1         | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA    | SATB  | SATDW         | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7   |       |               |        |                     |     |       | bit 0 |

|         |       |               |        |                     |     |       |       |

| Legend: |       | C = Clearable | e bit  |                     |     |       |       |

## REGISTER 3-17: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit

1 = Variable exception processing is enabled

0 = Fixed exception processing is enabled

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| TABLE 3-27: PIN     | AND  | ANSE | ELX A | VAIL | ABILI | TY   |     |     |     |     |     |     |     |     |     |     |

|---------------------|------|------|-------|------|-------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Device              | Rx15 | Rx14 | Rx13  | Rx12 | Rx11  | Rx10 | Rx9 | Rx8 | Rx7 | Rx6 | Rx5 | Rx4 | Rx3 | Rx2 | Rx1 | Rx0 |

|                     |      |      |       |      |       | POR  | TA  |     |     |     |     |     |     |     |     |     |

| dsPIC33XXXMP508/208 | —    | —    | —     | —    | —     | —    | —   | —   | _   | _   | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 |      | _    | _     | _    | _     | _    | _   | _   | _   | _   | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP505/205 |      | —    |       |      |       | —    |     | —   |     |     | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP503/203 | _    | —    |       |      | _     | —    | _   |     | _   | _   |     | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP502/202 | _    | —    |       |      | —     | —    | _   |     | _   | _   |     | Х   | Х   | Х   | Х   | Х   |

| ANSELA              |      | —    |       |      | —     | —    | —   | _   |     |     | —   | Х   | Х   | Х   | Х   | Х   |

| PORTB               |      |      |       |      |       |      |     |     |     |     |     |     |     |     |     |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP505/205 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP503/203 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP502/202 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| ANSELB              |      | —    | —     | —    | —     | Х    | Х   | Х   | _   | _   | —   | Х   | Х   | Х   | Х   | Х   |

|                     | -    | -    |       |      |       | POR  | тс  | -   | -   | -   |     |     | -   | -   | -   |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP505/205 | _    | —    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP503/203 | —    | —    | —     | —    | —     | —    | —   | —   | —   | —   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP502/202 | —    | —    | —     | —    | —     | —    | —   | —   | —   | —   | —   | —   | —   | —   | —   | —   |

| ANSELC              | —    | —    | —     | —    | —     | —    | —   | —   | Х   |     |     | —   | Х   | Х   | Х   | Х   |

|                     | -    | -    |       |      |       | POR  | TD  | -   | -   | -   |     |     | -   | -   | -   |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP505/205 | —    | —    | Х     | —    | —     | Х    | —   | Х   | —   | —   | —   | —   | —   | —   | Х   | —   |

| dsPIC33XXXMP503/203 | —    | —    | —     | —    | —     | —    | —   | —   | —   | —   | —   | —   | —   | —   | —   | —   |

| dsPIC33XXXMP502/202 | _    | —    | —     | —    | —     | —    | —   | _   | —   | —   | _   | —   | —   | —   | —   | —   |

| ANSELD              |      | —    |       |      |       | Х    | —   | _   |     |     |     | —   | —   | —   | _   |     |

|                     | -    |      |       |      | •     | POR  | TE  | -   | -   |     |     |     | -   | -   | -   |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Х     | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | —    |      | _     | _    | _     |      | —   | —   | _   | _   | _   | —   |     |     |     | —   |

| dsPIC33XXXMP505/205 | —    | —    |       | —    | —     | —    | —   | —   | —   | —   |     | —   | —   | —   | —   | —   |

| dsPIC33XXXMP503/203 | _    | —    | —     | —    | —     | —    | —   | —   | —   | —   |     | —   | —   | —   | —   | —   |

| dsPIC33XXXMP502/202 |      | —    | —     | —    | —     | —    | —   | —   | —   | —   | —   | —   | —   | —   | —   | —   |

# TABLE 3-27: PIN AND ANSELx AVAILABILITY

#### TABLE 3-28: 5V INPUT TOLERANT PORTS

| PORTA |      | Ι    |      | _    | _    | _    | _   | _   | Ι   |     | Ι   | RA4 | RA3 | RA2 | RA1 | RA0 |

|-------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| PORTB | RB15 | RB14 | RB13 | RB12 | RB11 | RB10 | RB9 | RB8 | RB7 | RB6 | RB5 | RB4 | RB3 | RB2 | RB1 | RB0 |

| PORTC | RC15 | RC14 | RC13 | RC12 | RC11 | RC10 | RC9 | RC8 | RC7 | RC6 | RC5 | RC4 | RC3 | RC2 | RC1 | RC0 |

| PORTD | RD15 | RD14 | RD13 | RD12 | RD11 | RD10 | RD9 | RD8 | RD7 | RD6 | RD5 | RD4 | RD3 | RD2 | RD1 | RD0 |

| PORTE | RE15 | RE14 | RE13 | RE12 | RE11 | RE10 | RE9 | RE8 | RE7 | RE6 | RE5 | RE4 | RE3 | RE2 | RE1 | RE0 |

Legend: Shaded pins are up to 5.5 VDC input tolerant.

| Function     | RPnR<5:0> | Output Name                        |

|--------------|-----------|------------------------------------|

| Default PORT | 000000    | RPn tied to Default Pin            |

| U1TX         | 000001    | RPn tied to UART1 Transmit         |

| U1RTS        | 000010    | RPn tied to UART1 Request-to-Send  |

| U2TX         | 000011    | RPn tied to UART2 Transmit         |

| U2RTS        | 000100    | RPn tied to UART2 Request-to-Send  |

| SDO1         | 000101    | RPn tied to SPI1 Data Output       |

| SCK1         | 000110    | RPn tied to SPI1 Clock Output      |

| SS1          | 000111    | RPn tied to SPI1 Slave Select      |

| SDO2         | 001000    | RPn tied to SPI2 Data Output       |

| SCK2         | 001001    | RPn tied to SPI2 Clock Output      |

| SS2          | 001010    | RPn tied to SPI2 Slave Select      |

| REFCLKO      | 001110    | RPn tied to Reference Clock Output |

| OCM1         | 001111    | RPn tied to SCCP1 Output           |

| OCM2         | 010000    | RPn tied to SCCP2 Output           |

| OCM3         | 010001    | RPn tied to SCCP3 Output           |

| OCM4         | 010010    | RPn tied to SCCP4 Output           |

| OCM5         | 010011    | RPn tied to SCCP5 Output           |

| OCM6         | 010100    | RPn tied to SCCP6 Output           |

| CAN1         | 010101    | RPn tied to CAN1 Output            |

| CMP1         | 010111    | RPn tied to Comparator 1 Output    |

| PWM4H        | 100010    | RPn tied to PWM4H Output           |

| PWM4L        | 100011    | RPn tied to PWM4L Output           |

| PWMEA        | 100100    | RPn tied to PWM Event A Output     |

| PWMEB        | 100101    | RPn tied to PWM Event B Output     |

| QEICMP       | 100110    | RPn tied to QEI Comparator Output  |

| CLC1OUT      | 101000    | RPn tied to CLC1 Output            |

| CLC2OUT      | 101001    | RPn tied to CLC2 Output            |

| OCM7         | 101010    | RPn tied to SCCP7 Output           |

| OCM8         | 101011    | RPn tied to SCCP8 Output           |

| PWMEC        | 101100    | RPn tied to PWM Event C Output     |

| PWMED        | 101101    | RPn tied to PWM Event D Output     |

| PTGTRG24     | 101110    | PTG Trigger Output 24              |

| PTGTRG25     | 101111    | PTG Trigger Output 25              |

| SENT1OUT     | 110000    | RPn tied to SENT1 Output           |

| SENT2OUT     | 110001    | RPn tied to SENT2 Output           |

| CLC3OUT      | 110010    | RPn tied to CLC3 Output            |

| CLC4OUT      | 110011    | RPn tied to CLC4 Output            |

| U1DTR        | 110100    | Data Terminal Ready Output 1       |

| U2DTR        | 110101    | Data Terminal Ready Output 2       |

#### TABLE 3-33: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| R/W-0                 | U-0                                                              | R/W-0                                                          | R/W-0                      | R/W-0                    | R/W-1            | R/W-1          | R/W-1                 |

|-----------------------|------------------------------------------------------------------|----------------------------------------------------------------|----------------------------|--------------------------|------------------|----------------|-----------------------|

| CON                   | —                                                                | SIDL                                                           | BRSDIS                     | BUSY                     | WFT1             | WFT0           | WAKFIL <sup>(1)</sup> |

| bit 15                |                                                                  |                                                                |                            |                          |                  |                | bit 8                 |

| R/W-0                 | R/W-1                                                            | R/W-1                                                          | R/W-0                      | R/W-0                    | R/W-0            | R/W-0          | R/W-0                 |

| CLKSEL <sup>(1)</sup> | PXEDIS <sup>(1)</sup>                                            | ISOCRCEN <sup>(1)</sup>                                        | DNCNT4                     | DNCNT3                   | DNCNT2           | DNCNT1         | DNCNT0                |

| bit 7                 |                                                                  |                                                                |                            | 1                        |                  |                | bit 0                 |

| Legend:               |                                                                  |                                                                |                            |                          |                  |                |                       |

| R = Readable          | bit                                                              | W = Writable bit                                               |                            | U = Unimpler             | mented bit, read | d as '0'       |                       |

| -n = Value at F       | POR                                                              | '1' = Bit is set                                               |                            | '0' = Bit is cle         | ared             | x = Bit is unk | nown                  |

| bit 15                | CON: CAN E                                                       | nable bit                                                      |                            |                          |                  |                |                       |

|                       | 1 = CAN mod                                                      | ule is enabled<br>ule is disabled                              |                            |                          |                  |                |                       |

| bit 14                | Unimplemen                                                       | ted: Read as '0'                                               |                            |                          |                  |                |                       |

| bit 13                | SIDL: CAN S                                                      | top in Idle Contro                                             | l bit                      |                          |                  |                |                       |

|                       |                                                                  | dule operation in<br>stop module ope                           |                            | mode                     |                  |                |                       |

| bit 12                |                                                                  | Rate Switching (E                                              | ,                          |                          |                  |                |                       |

|                       |                                                                  | Switching is disab<br>Switching depend                         |                            |                          |                  | ssage object   |                       |

| bit 11                |                                                                  | Nodule is Busy bi                                              | t                          |                          |                  |                |                       |

|                       |                                                                  | module is active<br>module is inactiv                          | e                          |                          |                  |                |                       |

| bit 10-9              |                                                                  | electable Wake-ι                                               | ip Filter Time             | e bits                   |                  |                |                       |

|                       | 11 = T11FILTE<br>10 = T10FILTE<br>01 = T01FILTE<br>00 = T00FILTE | R<br>R                                                         |                            |                          |                  |                |                       |

| bit 8                 | WAKFIL: Ena                                                      | able CAN Bus Lin                                               | e Wake-up F                | ilter bit <sup>(1)</sup> |                  |                |                       |

|                       |                                                                  | N bus line filter fo<br>line filter is not us                  |                            | ·up                      |                  |                |                       |

| bit 7                 | CLKSEL: Mo                                                       | dule Clock Sourc                                               | e Select bit <sup>(1</sup> | )                        |                  |                |                       |

|                       |                                                                  | selected as the selected as the selected as the sol            |                            |                          |                  |                |                       |

| bit 6                 | PXEDIS: Prot                                                     | ocol Exception E                                               | vent Detection             | on Disabled bit          | (1)              |                |                       |

|                       | 1 = Protocol E                                                   | eserved bit" follo<br>Exception is treat<br>col Exception is d | ed as a form               | error                    |                  | -              |                       |

| bit 5                 |                                                                  | Enable ISO CRC                                                 |                            |                          |                  | gotato         |                       |

|                       | 1 = Includes s                                                   | stuff bit count in C<br>include stuff bit c                    | RC field and               | l uses non-zer           |                  |                | all zeros             |

| bit 4-0               | DNCNT<4:0>                                                       | : DeviceNet™ Fi                                                | lter Bit Numb              | er bits                  |                  |                |                       |

|                       |                                                                  | 1 = Invalid select<br>pares up to Data                         |                            |                          | s of data with E | ID)            |                       |

|                       |                                                                  | pares up to Data<br>s not compare da                           |                            | with EID0                |                  |                |                       |

#### REGISTER 3-103: C1CONL: CAN CONTROL REGISTER LOW

**Note 1:** These bits can only be modified in Configuration mode (OPMOD<2:0> = 100).

## REGISTER 3-139: C1FIFOUAHx: CAN FIFO USER ADDRESS REGISTER x (x = 1 TO 7) HIGH<sup>(1)</sup>

| R-x     | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|---------|-----|-----|--------|---------|-----|-----|-------|

|         |     |     | FIFOUA | <31:24> |     |     |       |

| bit 15  |     |     |        |         |     |     | bit 8 |

|         |     |     |        |         |     |     |       |

| R-x     | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|         |     |     | FIFOUA | <23:16> |     |     |       |

| bit 7   |     |     |        |         |     |     | bit 0 |

|         |     |     |        |         |     |     |       |

| Legend: |     |     |        |         |     |     |       |

| Legenu.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

FIFOUA<31:16>: FIFO User Address bits

TXEN = 1 (FIFO configured as a transmit buffer):

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0 (FIFO configured as a receive buffer):

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

#### **REGISTER 3-140:** C1FIFOUALX: CAN FIFO USER ADDRESS REGISTER x (x = 1 TO 7) $LOW^{(1)}$

| R-x             | R-x | R-x              | R-x    | R-x                 | R-x          | R-x                | R-x   |

|-----------------|-----|------------------|--------|---------------------|--------------|--------------------|-------|

|                 |     |                  | FIFOUA | \<15:8>             |              |                    |       |

| bit 15          |     |                  |        |                     |              |                    | bit 8 |

|                 |     |                  |        |                     |              |                    |       |

| R-x             | R-x | R-x              | R-x    | R-x                 | R-x          | R-x                | R-x   |

|                 |     |                  | FIFOU  | A<7:0>              |              |                    |       |

| bit 7           |     |                  |        |                     |              |                    | bit 0 |

|                 |     |                  |        |                     |              |                    |       |

| Legend:         |     |                  |        |                     |              |                    |       |

| R = Readable I  | bit | W = Writable bit |        | U = Unimpleme       | nted bit, re | ad as '0'          |       |

| -n = Value at P | OR  | '1' = Bit is set |        | '0' = Bit is cleare | ed           | x = Bit is unknowr | ı     |

bit 15-0

FIFOUA<15:0>: FIFO User Address bits

TXEN = 1 (FIFO configured as a transmit buffer):

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0 (FIFO configured as a receive buffer):

A read of this register will return the address where the next message is to be read (FIFO tail).

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

## 4.2.2 DATA ADDRESS SPACE (SLAVE)

The dsPIC33CH128MP508S1 family CPU has a separate 16-bit wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory map is shown in Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes or 32K words.

The lower half of the data memory space (i.e., when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV).

The dsPIC33CH128MP508S1 family devices implement up to 4 Kbytes of data memory. If an EA points to a location outside of this area, an all-zero word or byte is returned.

#### 4.2.2.1 Data Space Width

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2.2 Data Memory Organization and Alignment

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33CH128MP508S1 family instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through wordaligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

#### 4.2.2.3 SFR Space

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33CH128MP508S1 family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

#### 4.2.2.4 Near Data Space

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

| Input Name <sup>(1)</sup>                | Function Name | Register | Configuration Bits |

|------------------------------------------|---------------|----------|--------------------|

| External Interrupt 1                     | S1INT1        | RPINR0   | INT1R<7:0>         |

| External Interrupt 2                     | S1INT2        | RPINR1   | INT2R<7:0>         |

| External Interrupt 3                     | S1INT3        | RPINR1   | INT3R<7:0>         |

| Timer1 External Clock                    | S1T1CK        | RPINR2   | T1CKR<7:0>         |

| SCCP Timer1                              | S1TCKI1       | RPINR3   | TCKI1R<7:0>        |

| SCCP Capture 1                           | S1ICM1        | RPINR3   | ICM1R<7:0>         |

| SCCP Timer2                              | S1TCKI2       | RPINR4   | TCKI2R<7:0>        |

| SCCP Capture 2                           | S1ICM2        | RPINR4   | ICM2R<7:0>         |

| SCCP Timer3                              | S1TCKI3       | RPINR5   | TCKI3R<7:0>        |

| SCCP Capture 3                           | S1ICM3        | RPINR5   | ICM3R<7:0>         |

| SCCP Timer4                              | S1TCKI4       | RPINR6   | TCKI4R<7:0>        |

| SCCP Capture 4                           | S1ICM4        | RPINR6   | ICM4R<7:0>         |

| Output Compare Fault A                   | S10CFA        | RPINR11  | OCFAR<7:0>         |

| Output Compare Fault B                   | S10CFB        | RPINR11  | OCFBR<7:0>         |

| PWM Input 8                              | S1PCI8        | RPINR12  | PCI8R<7:0>         |

| PWM Input 9                              | S1PCI9        | RPINR12  | PCI9R<7:0>         |

| PWM Input 10                             | S1PCI10       | RPINR13  | PCI10R<7:0>        |

| PWM Input 11                             | S1PCI11       | RPINR13  | PCI11R<7:0>        |

| QEI Input A                              | S1QEIA1       | RPINR14  | QEIA1R<7:0>        |

| QEI Input B                              | S1QEIB1       | RPINR14  | QEIB1R<7:0>        |

| QEI Index 1 Input                        | S1QEINDX1     | RPINR15  | QEINDX1R<7:0>      |

| QEI Home 1 Input                         | S1QEIHOM1     | RPINR15  | QEIHOM1R<7:0>      |

| UART1 Receive                            | S1U1RX        | RPINR18  | U1RXR<7:0>         |

| UART1 Data-Set-Ready                     | S1U1DSR       | RPINR18  | U1DSRR<7:0>        |

| SPI1 Data Input                          | S1SDI1        | RPINR20  | SDI1R<7:0>         |

| SPI1 Clock Input                         | S1SCK1        | RPINR20  | SCK1R<7:0>         |

| SPI1 Slave Select                        | S1SS1         | RPINR21  | SS1R<7:0>          |

| Reference Clock Input                    | S1REFOI       | RPINR21  | REFOIR<7:0>        |

| UART1 Clear-to-Send                      | S1U1CTS       | RPINR23  | U1CTSR<7:0>        |

| PWM Input 17                             | S1PCI17       | RPINR37  | PCI17R<7:0>        |

| PWM Input 18                             | S1PCI18       | RPINR38  | PCI18R<7:0>        |

| PWM Input 12                             | S1PCI12       | RPINR42  | PCI12R<7:0>        |

| PWM Input 13                             | S1PCI13       | RPINR42  | PCI13R<7:0>        |

| PWM Input 14                             | S1PCI14       | RPINR43  | PCI14R<7:0>        |

| PWM Input 15                             | S1PCI15       | RPINR43  | PCI15R<7:0>        |

| PWM Input 16                             | S1PCI16       | RPINR44  | PCI16R<7:0>        |

| CLC Input A                              | S1CLCINA      | RPINR45  | CLCINAR<7:0>       |

| CLC Input B                              | S1CLCINB      | RPINR46  | CLCINBR<7:0>       |

| CLC Input C                              | S1CLCINC      | RPINR46  | CLCINCR<7:0>       |

| CLC Input D                              | S1CLCIND      | RPINR47  | CLCINDR<7:0>       |

| ADC External Trigger Input<br>(ADTRIG31) | S1ADCTRG      | RPINR47  | ADCTRGR<7:0>       |

#### TABLE 4-28: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

|  | REGISTER 4-89: | ADCON4L: ADC CONTROL REGISTER 4 LOW |

|--|----------------|-------------------------------------|

|--|----------------|-------------------------------------|

| U-0     | U-0 | U-0          | U-0 | U-0 | U-0 | r-0     | r-0     |

|---------|-----|--------------|-----|-----|-----|---------|---------|

| —       | —   | —            | —   | —   | —   | —       | —       |

| bit 15  |     |              |     |     |     |         | bit 8   |

|         |     |              |     |     |     |         |         |

| U-0     | U-0 | U-0          | U-0 | U-0 | U-0 | R/W-0   | R/W-0   |

| —       | —   | —            | —   | —   | —   | SAMC1EN | SAMC0EN |

| bit 7   |     |              |     |     |     |         | bit 0   |

|         |     |              |     |     |     |         |         |

| Legend: |     | r = Reserved | bit |     |     |         |         |

| Legend:           | r = Reserved bit |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

- bit 15-10 Unimplemented: Read as '0'

- bit 9-8 Reserved: Must be written as '0'

- bit 7-2 Unimplemented: Read as '0'

- bit 1 SAMC1EN: Dedicated ADC Core 1 Conversion Delay Enable bit

- 1 = After trigger, the conversion will be delayed and the ADC core will continue sampling during the time specified by the SAMC<9:0> bits in the ADCORE1L register

- 0 = After trigger, the sampling will be stopped immediately and the conversion will be started on the next core clock cycle

- bit 0 SAMCOEN: Dedicated ADC Core 0 Conversion Delay Enable bit

- 1 = After trigger, the conversion will be delayed and the ADC core will continue sampling during the time specified by the SAMC<9:0> bits in the ADCORE0L register

- 0 = After trigger, the sampling will be stopped immediately and the conversion will be started on the next core clock cycle

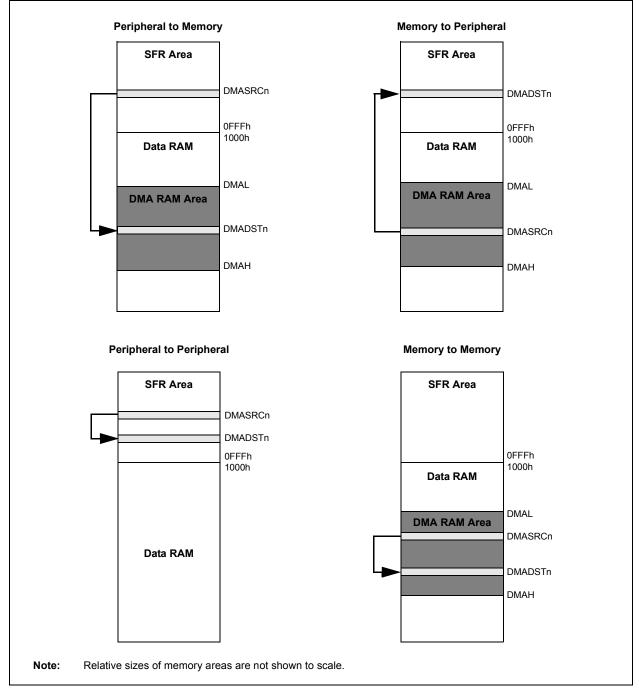

## FIGURE 8-2: TYPES OF DMA DATA TRANSFERS

## **REGISTER 9-10: PWMEVTy: PWM EVENT OUTPUT CONTROL REGISTER y<sup>(5)</sup> (CONTINUED)**

bit 2-0 EVTyPGS<2:0>: PWM Event Source Selection bits<sup>(2)</sup>

- 111 = PG8 110 = PG7 101 = PG6 100 = PG5 011 = PG4 010 = PG3 001 = PG2 000 = PG1

- **Note 1:** The event signal is stretched using the peripheral clock because different PGs may be operating from different clock sources. The leading edge of the event pulse is produced in the clock domain of the PWM Generator. The trailing edge of the stretched event pulse is produced in the peripheral clock domain.

- 2: No event will be produced if the selected PWM Generator is not present.

- 3: This is the PWM Generator output signal prior to output mode logic and any output override logic.

- 4: This signal should be the PGx\_clk domain signal prior to any synchronization into the system clock domain.

- **5:** 'y' denotes a common instance (A-F).

## REGISTER 9-18: PGxyPCIH: PWM GENERATOR xy PCI REGISTER HIGH (x = PWM GENERATOR #; y = F, CL, FF OR S)

|                     | <u> </u>                                                                                                                                                                                                                                        |                       |                                      | , ,               | /                                        |                 |       |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------|-------------------|------------------------------------------|-----------------|-------|--|

| R/W-0               | R/W-0                                                                                                                                                                                                                                           | R/W-0                 | R/W-0                                | U-0               | R/W-0                                    | R/W-0           | R/W-0 |  |

| BPEN                | BPSEL2 <sup>(1)</sup>                                                                                                                                                                                                                           | BPSEL1 <sup>(1)</sup> | BPSEL0 <sup>(1)</sup>                | —                 | ACP2                                     | ACP1            | ACP0  |  |

| bit 15              | ·                                                                                                                                                                                                                                               |                       |                                      |                   |                                          |                 | bit 8 |  |

|                     |                                                                                                                                                                                                                                                 |                       |                                      |                   |                                          |                 |       |  |

| R/W-0               | R/W-0                                                                                                                                                                                                                                           | R/W-0                 | R/W-0                                | R/W-0             | R/W-0                                    | R/W-0           | R/W-0 |  |

| SWPCI               | SWPCIM1                                                                                                                                                                                                                                         | SWPCIM0               | LATMOD                               | TQPS              | TQSS2                                    | TQSS1           | TQSS0 |  |

| bit 7               |                                                                                                                                                                                                                                                 |                       |                                      |                   |                                          |                 | bit 0 |  |

| -                   |                                                                                                                                                                                                                                                 |                       |                                      |                   |                                          |                 |       |  |

| Legend:             |                                                                                                                                                                                                                                                 |                       |                                      |                   |                                          |                 |       |  |

| R = Reada           | ble bit                                                                                                                                                                                                                                         | W = Writable          | bit                                  | U = Unimplen      | nented bit, read a                       | as '0'          |       |  |

| -n = Value          | at POR                                                                                                                                                                                                                                          | '1' = Bit is set      | t                                    | '0' = Bit is clea | ared                                     | x = Bit is unkn | own   |  |

| bit 15<br>bit 14-12 | <ul> <li>1 = PCI function is enabled and local PCI logic is bypassed; PWM Generator will be controlled by PCI function in the PWM Generator selected by the BPSEL&lt;2:0&gt; bits</li> <li>0 = PCI function is not bypassed</li> </ul>          |                       |                                      |                   |                                          |                 |       |  |

| bit 11              |                                                                                                                                                                                                                                                 | nted: Read as         |                                      |                   | I logic when BPE                         |                 |       |  |

| bit 10-8            | -                                                                                                                                                                                                                                               |                       |                                      | tion bits         |                                          |                 |       |  |

|                     | <pre>it 10-8 ACP&lt;2:0&gt;: PCI Acceptance Criteria Selection bits 111 = Reserved 110 = Reserved 101 = Latched any edge 100 = Latched rising edge 011 = Latched 010 = Any edge 001 = Rising edge 001 = Rising edge 000 = Level-sensitive</pre> |                       |                                      |                   |                                          |                 |       |  |

| bit 7               | SWPCI: Soft                                                                                                                                                                                                                                     | ware PCI Con          | trol bit                             |                   |                                          |                 |       |  |

|                     |                                                                                                                                                                                                                                                 |                       |                                      |                   | <1:0> control bits<br><1:0> control bits |                 |       |  |

| bit 6-5             | SWPCIM<1:0>: Software PCI Control Mode bits<br>11 = Reserved<br>10 = SWPCI bit is assigned to termination qualifier logic<br>01 = SWPCI bit is assigned to acceptance qualifier logic<br>00 = SWPCI bit is assigned to PCI acceptance logic     |                       |                                      |                   |                                          |                 |       |  |

| bit 4               | LATMOD: PO                                                                                                                                                                                                                                      | CI SR Latch M         | ode bit                              |                   |                                          |                 |       |  |

|                     |                                                                                                                                                                                                                                                 |                       | inant in Latcheo<br>ant in Latched A |                   |                                          |                 |       |  |

| Note 1:             | Selects '0' if se                                                                                                                                                                                                                               | elected PWM (         | Generator is not                     | present.          |                                          |                 |       |  |

**Note 1:** Selects '0' if selected PWM Generator is not present.

| R/W-0         | R/W-0                                                 | R/W-0                                  | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

|---------------|-------------------------------------------------------|----------------------------------------|------------------|-------------------|------------------|-----------------|-------|--|--|

| G4D4T         | G4D4N                                                 | G4D3T                                  | G4D3N            | G4D2T             | G4D2N            | G4D1T           | G4D1N |  |  |

| bit 15        |                                                       |                                        |                  |                   |                  |                 | bit 8 |  |  |

| R/W-0         | R/W-0                                                 | R/W-0                                  | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

| G3D4T         | G3D4N                                                 | G3D3T                                  | G3D3N            | G3D2T             | G3D2N            | G3D1T           | G3D1N |  |  |

| bit 7         |                                                       | 00201                                  | CODON            | CODET             | CODEN            | 00011           | bit 0 |  |  |

| Legend:       |                                                       |                                        |                  |                   |                  |                 |       |  |  |

| R = Readable  | e bit                                                 | W = Writable                           | bit              | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |

| -n = Value at | POR                                                   | '1' = Bit is set                       |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |

|               |                                                       |                                        |                  |                   |                  |                 |       |  |  |

| bit 15        | G4D4T: Gate                                           | 4 Data Source                          | 4 True Enable    | e bit             |                  |                 |       |  |  |

|               |                                                       | rce 4 signal is e                      |                  |                   |                  |                 |       |  |  |

| bit 14        |                                                       | rce 4 signal is o                      |                  |                   |                  |                 |       |  |  |

| DIL 14        |                                                       | e 4 Data Source<br>rce 4 inverted s    | -                |                   |                  |                 |       |  |  |

|               |                                                       | rce 4 inverted s                       |                  |                   |                  |                 |       |  |  |

| bit 13        | G4D3T: Gate                                           | 4 Data Source                          | 3 True Enable    | e bit             |                  |                 |       |  |  |

|               |                                                       | rce 3 signal is o<br>rce 3 signal is o |                  |                   |                  |                 |       |  |  |

| bit 12        |                                                       | 4 Data Source                          |                  |                   |                  |                 |       |  |  |

|               | 1 = Data Sou                                          | rce 3 inverted s<br>rce 3 inverted s   | signal is enable | ed for Gate 4     |                  |                 |       |  |  |

| bit 11        |                                                       | 4 Data Source                          | •                |                   |                  |                 |       |  |  |

|               |                                                       | rce 2 signal is e<br>rce 2 signal is e |                  |                   |                  |                 |       |  |  |

| bit 10        | G4D2N: Gate                                           | 4 Data Source                          | e 2 Negated Er   | nable bit         |                  |                 |       |  |  |

|               |                                                       | rce 2 inverted s                       |                  |                   |                  |                 |       |  |  |

| bit 9         | G4D1T: Gate                                           | 4 Data Source                          | 1 True Enable    | e bit             |                  |                 |       |  |  |

|               |                                                       | rce 1 signal is o<br>rce 1 signal is o |                  |                   |                  |                 |       |  |  |

| bit 8         |                                                       | 4 Data Source                          |                  |                   |                  |                 |       |  |  |

|               | 1 = Data Sou                                          | rce 1 inverted s                       | signal is enable | ed for Gate 4     |                  |                 |       |  |  |

| bit 7         |                                                       | 3 Data Source                          | •                |                   |                  |                 |       |  |  |

|               |                                                       | rce 4 signal is e<br>rce 4 signal is e |                  |                   |                  |                 |       |  |  |

| bit 6         | <b>G3D4N:</b> Gate 3 Data Source 4 Negated Enable bit |                                        |                  |                   |                  |                 |       |  |  |

|               |                                                       | rce 4 inverted s<br>rce 4 inverted s   |                  |                   |                  |                 |       |  |  |

| bit 5         |                                                       | 3 Data Source                          | -                |                   |                  |                 |       |  |  |

|               |                                                       | rce 3 signal is e<br>rce 3 signal is e |                  |                   |                  |                 |       |  |  |

| bit 4         |                                                       | 3 Data Source                          |                  |                   |                  |                 |       |  |  |

|               |                                                       | rce 3 inverted s                       | -                |                   |                  |                 |       |  |  |

#### REGISTER 18-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER

| U-1             | U-1                                            | U-1              | U-1 | U-1                                | U-1  | U-1            | U-1    |

|-----------------|------------------------------------------------|------------------|-----|------------------------------------|------|----------------|--------|

| _               | _                                              | —                | —   | —                                  | —    | —              | —      |

| bit 23          |                                                |                  |     |                                    |      |                | bit 16 |

|                 |                                                |                  |     |                                    |      |                |        |

| RP/0-1          | U-1                                            | R/PO-1           | U-1 | U-1                                | U-1  | U-1            | U-1    |

| S1NOBTSWP       | —                                              | S1ISOLAT         | _   | —                                  | —    | —              | —      |

| bit 15          |                                                |                  |     |                                    |      |                | bit 8  |

|                 |                                                |                  |     |                                    |      |                |        |

| r-1             | U-1                                            | U-1              | U-1 | U-1                                | U-1  | R/PO-1         | R/PO-1 |

| —               | _                                              | —                | —   | _                                  | —    | S1ICS1         | S1ICS0 |

| bit 7           |                                                |                  |     |                                    |      |                | bit 0  |

|                 |                                                |                  |     |                                    |      |                |        |

| Legend:         | Legend: PO = Program Once bit r = Reserved bit |                  |     |                                    |      |                |        |

| R = Readable b  | oit                                            | W = Writable     | bit | U = Unimplemented bit, read as '0' |      |                |        |

| -n = Value at P | OR                                             | '1' = Bit is set |     | '0' = Bit is clea                  | ared | x = Bit is unk | nown   |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | S1NOBTSWP: BOOTSWP Instruction Disable bit                                                                                                                                                                                                       |

|           | 1 = BOOTSWP instruction is disabled<br>0 = BOOTSWP instruction is enabled                                                                                                                                                                        |

| bit 14    | Unimplemented: Read as '1'                                                                                                                                                                                                                       |

| bit 13    | S1ISOLAT: Slave Core Isolation bit                                                                                                                                                                                                               |

|           | <ul> <li>1 = The Slave can operate (in Debug mode), even if the SLVEN bit in the MSI is zero</li> <li>0 = The Slave can only operate if the SLVEN bit in the MSI is set</li> </ul>                                                               |

| bit 12-8  | Unimplemented: Read as '1'                                                                                                                                                                                                                       |

| bit 7     | Reserved: Maintain as '1'                                                                                                                                                                                                                        |

| bit 6-2   | Unimplemented: Read as '1'                                                                                                                                                                                                                       |

| bit 1-0   | S1ICS<1:0>: ICD Pin Placement Select bits                                                                                                                                                                                                        |

|           | 11 = Slave ICD pins are S1PGC1/S1PGD1/ <u>S1MCLR1</u><br>10 = Slave ICD pins are S1PGC2/S1PGD2/ <u>S1MCLR2</u><br>01 = Slave I <u>CD pins ar</u> e S1PGC3/S1PGD3/S1MCLR3<br>00 = None (S1MCLR1 pin is released and can be used as a regular I/O) |

| DEVID<7:0>          | Device Name         | Core   |  |  |  |  |  |

|---------------------|---------------------|--------|--|--|--|--|--|

| Devices with CAN FD |                     |        |  |  |  |  |  |

| 0x40                | dsPIC33CH64MP502    | Master |  |  |  |  |  |

| 0xC0                | dsPIC33CH64MP502S1  | Slave  |  |  |  |  |  |

| 0x50                | dsPIC33CH128MP502   | Master |  |  |  |  |  |

| 0xD0                | dsPIC33CH128MP502S1 | Slave  |  |  |  |  |  |

| 0x41                | dsPIC33CH64MP503    | Master |  |  |  |  |  |

| 0xC1                | dsPIC33CH64MP503S1  | Slave  |  |  |  |  |  |

| 0x51                | dsPIC33CH128MP503   | Master |  |  |  |  |  |

| 0xD1                | dsPIC33CH128MP503S1 | Slave  |  |  |  |  |  |

| 0x42                | dsPIC33CH64MP505    | Master |  |  |  |  |  |

| 0xC2                | dsPIC33CH64MP505S1  | Slave  |  |  |  |  |  |

| 0x52                | dsPIC33CH128MP505   | Master |  |  |  |  |  |

| 0xD2                | dsPIC33CH128MP505S1 | Slave  |  |  |  |  |  |

| 0x43                | dsPIC33CH64MP506    | Master |  |  |  |  |  |

| 0xC3                | dsPIC33CH64MP506S1  | Slave  |  |  |  |  |  |

| 0x53                | dsPIC33CH128MP506   | Master |  |  |  |  |  |

| 0xD3                | dsPIC33CH128MP506S1 | Slave  |  |  |  |  |  |

| 0x44                | dsPIC33CH64MP508    | Master |  |  |  |  |  |

| 0xC4                | dsPIC33CH64MP508S1  | Slave  |  |  |  |  |  |

| 0x54                | dsPIC33CH128MP508   | Master |  |  |  |  |  |

| 0xD4                | dsPIC33CH128MP508S1 | Slave  |  |  |  |  |  |

#### TABLE 21-5: DEVICE VARIANTS

# REGISTER 21-37: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0        | R/W-0              | U-0                                                                                                                              | U-0              | U-0               | U-0              | R/W-0           | R/W-0           |  |  |  |  |

|--------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|------------------|-----------------|-----------------|--|--|--|--|

| TRAPR        | IOPUWR             | _                                                                                                                                | _                | _                 | _                | СМ              | VREGS           |  |  |  |  |

| bit 15       |                    |                                                                                                                                  |                  |                   |                  |                 | bit 8           |  |  |  |  |

|              |                    |                                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

| R/W-0        | R/W-0              | U-0                                                                                                                              | R/W-0            | R/W-0             | R/W-0            | R/W-1           | R/W-1           |  |  |  |  |

| EXTR         | SWR                | —                                                                                                                                | WDTO             | SLEEP             | IDLE             | BOR             | POR             |  |  |  |  |

| bit 7 bit 0  |                    |                                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

| <b>F</b>     |                    |                                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

| Legend:      |                    |                                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

| R = Readab   |                    | W = Writable                                                                                                                     | bit              | •                 | nented bit, read |                 |                 |  |  |  |  |

| -n = Value a | t POR              | '1' = Bit is set                                                                                                                 |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown            |  |  |  |  |

| hit 1E       |                    | Deast Flag bit                                                                                                                   |                  |                   |                  |                 |                 |  |  |  |  |

| bit 15       |                    | Reset Flag bit<br>onflict Reset hat                                                                                              |                  |                   |                  |                 |                 |  |  |  |  |

|              |                    | onflict Reset ha                                                                                                                 |                  | t                 |                  |                 |                 |  |  |  |  |

| bit 14       | IOPUWR: Ille       | gal Opcode or                                                                                                                    | Uninitialized V  | V Register Acce   | ess Reset Flag   | bit             |                 |  |  |  |  |

|              | -                  | •                                                                                                                                | on, an illegal a | address mode c    | or Uninitialized | W register used | d as an Address |  |  |  |  |

|              |                    | aused a Reset                                                                                                                    | initialized W/r  | egister Reset h   | as not occurro   | d               |                 |  |  |  |  |

| bit 13-10    |                    | ited: Read as '                                                                                                                  |                  | egister Reset fi  |                  | u               |                 |  |  |  |  |

| bit 9        | -                  | ation Mismatch                                                                                                                   |                  |                   |                  |                 |                 |  |  |  |  |

| bit 5        | •                  |                                                                                                                                  | •                | occurred          |                  |                 |                 |  |  |  |  |

|              | •                  | <ul> <li>1 = A Configuration Mismatch Reset has occurred</li> <li>0 = A Configuration Mismatch Reset has not occurred</li> </ul> |                  |                   |                  |                 |                 |  |  |  |  |

| bit 8        | VREGS: Volta       | age Regulator                                                                                                                    | Standby Durin    | g Sleep bit       |                  |                 |                 |  |  |  |  |

|              |                    | egulator is activ                                                                                                                |                  |                   |                  |                 |                 |  |  |  |  |

| h:+ 7        | -                  |                                                                                                                                  |                  | ode during Slee   | ер               |                 |                 |  |  |  |  |

| bit 7        |                    | nal Reset (MCL<br>Clear (pin) Res                                                                                                | ,                | ed                |                  |                 |                 |  |  |  |  |

|              |                    | Clear (pin) Res                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

| bit 6        |                    | re RESET (instr                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

|              |                    | instruction has                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

|              |                    | instruction has                                                                                                                  |                  | cuted             |                  |                 |                 |  |  |  |  |

| bit 5        | -                  | ted: Read as '                                                                                                                   |                  |                   |                  |                 |                 |  |  |  |  |

| bit 4        |                    | hdog Timer Tin                                                                                                                   |                  |                   |                  |                 |                 |  |  |  |  |

|              |                    | e-out has occur<br>e-out has not o                                                                                               |                  |                   |                  |                 |                 |  |  |  |  |

| bit 3        |                    | e from Sleep Fl                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

|              |                    | as in Sleep mo                                                                                                                   | -                |                   |                  |                 |                 |  |  |  |  |

|              | 0 = Device wa      | as not in Sleep                                                                                                                  | mode             |                   |                  |                 |                 |  |  |  |  |

| bit 2        |                    | rom Idle Flag b                                                                                                                  | it               |                   |                  |                 |                 |  |  |  |  |

|              |                    | as in Idle mode<br>as not in Idle m                                                                                              | ode              |                   |                  |                 |                 |  |  |  |  |

| bit 1        |                    | out Reset Flag                                                                                                                   |                  |                   |                  |                 |                 |  |  |  |  |

|              |                    | it Reset has oc                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

|              |                    | it Reset has no                                                                                                                  |                  |                   |                  |                 |                 |  |  |  |  |

| Noto 1: A    | Il of the Reset of | (                                                                                                                                |                  | 1                 |                  |                 |                 |  |  |  |  |

**Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

## 23.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.