Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit Dual-Core                                                                  |

| Speed                      | 180MHz, 200MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 69                                                                                |

| Program Memory Size        | 152KB (152K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                       |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 20K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 34x12b; D/A 4x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

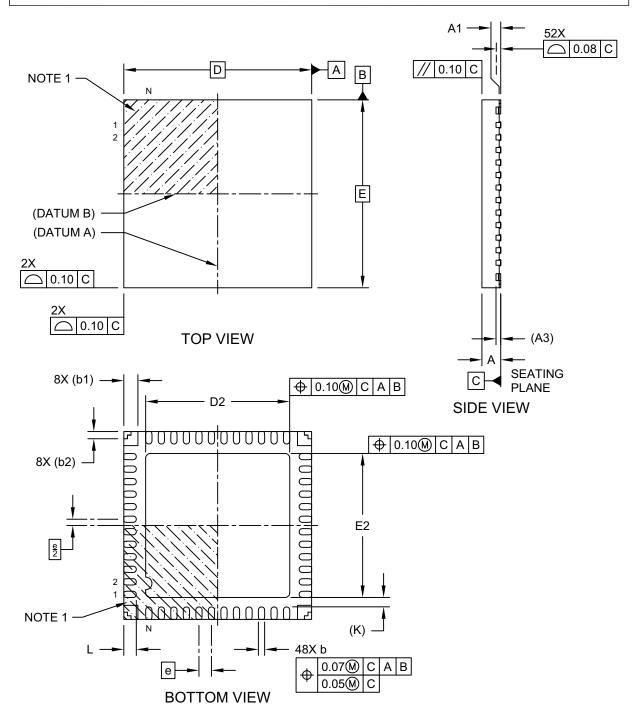

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch128mp208t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.6 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to a certain frequency (see Section 6.0 "Oscillator with High-Frequency PLL") to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

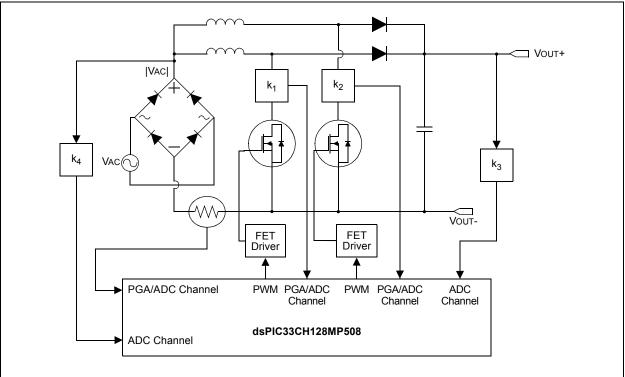

# FIGURE 2-4: INTERLEAVED PFC

#### 2.8 Targeted Applications

- Power Factor Correction (PFC):

- Interleaved PFC

- Critical Conduction PFC

- Bridgeless PFC

- DC/DC Converters:

- Buck, Boost, Forward, Flyback, Push-Pull

- Half/Full-Bridge

- Phase-Shift Full-Bridge

- Resonant Converters

- · DC/AC:

- Half/Full-Bridge Inverter

- Resonant Inverter

- Motor Control

- BLDC

- PMSM

- SR

- ACIM

Examples of typical application connections are shown in Figure 2-4 through Figure 2-6.

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2   | SFA: Stack Frame Active Status bit                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG</li> <li>0 = Stack frame is not active; W14 and W15 address the base Data Space</li> </ul> |

| bit 1   | RND: Rounding Mode Select bit                                                                                                                                                             |

|         | <ul> <li>1 = Biased (conventional) rounding is enabled</li> <li>0 = Unbiased (convergent) rounding is enabled</li> </ul>                                                                  |

| bit 0   | IF: Integer or Fractional Multiplier Mode Select bit                                                                                                                                      |

|         | <ul> <li>1 = Integer mode is enabled for DSP multiply</li> <li>0 = Fractional mode is enabled for DSP multiply</li> </ul>                                                                 |

| Note 1: | This bit is always read as '0'.                                                                                                                                                           |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## REGISTER 3-3: CTXTSTAT: CPU W REGISTER CONTEXT STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    | R-0    |

|--------|-----|-----|-----|-----|--------|--------|--------|

| —      |     |     |     | —   | CCTXI2 | CCTXI1 | CCTXI0 |

| bit 15 |     |     |     |     |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    | R-0    |

|-------|-----|-----|-----|-----|--------|--------|--------|

| —     | _   | _   | —   | _   | MCTXI2 | MCTXI1 | MCTXI0 |

| bit 7 |     |     |     |     |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-11 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10-8  | CCTXI<2:0>: Current (W Register) Context Identifier bits                                                                                                                                                                                                                                                                                                                               |

|           | 111 = Reserved                                                                                                                                                                                                                                                                                                                                                                         |

|           | •                                                                                                                                                                                                                                                                                                                                                                                      |

|           | •                                                                                                                                                                                                                                                                                                                                                                                      |

|           | •                                                                                                                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>100 = Alternate Working Register Set 4 is currently in use</li> <li>011 = Alternate Working Register Set 3 is currently in use</li> <li>010 = Alternate Working Register Set 2 is currently in use</li> <li>001 = Alternate Working Register Set 1 is currently in use</li> <li>000 = Default register set is currently in use</li> </ul>                                     |

| bit 7-3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                             |

| bit 2-0   | MCTXI<2:0>: Manual (W Register) Context Identifier bits                                                                                                                                                                                                                                                                                                                                |

|           | 111 = Reserved                                                                                                                                                                                                                                                                                                                                                                         |

|           | •                                                                                                                                                                                                                                                                                                                                                                                      |

|           | •                                                                                                                                                                                                                                                                                                                                                                                      |

|           | •                                                                                                                                                                                                                                                                                                                                                                                      |

|           | 100 = Alternate Working Register Set 4 was most recently manually selected<br>011 = Alternate Working Register Set 3 was most recently manually selected<br>010 = Alternate Working Register Set 2 was most recently manually selected<br>001 = Alternate Working Register Set 1 was most recently manually selected<br>000 = Default register set was most recently manually selected |

## TABLE 3-23: MASTER INTERRUPT VECTOR DETAILS (CONTINUED)

|                                                       | Vector  | IRQ     |                   | In       | terrupt Bit Lo | cation       |

|-------------------------------------------------------|---------|---------|-------------------|----------|----------------|--------------|

| Interrupt Source                                      | #       | #       | IVT Address       | Flag     | Enable         | Priority     |

| ADCAN16 – ADC AN16 Interrupt                          | 115     | 107     | 0x0000EA          | IFS6<11> | IEC6<11>       | IPC26<14:12> |

| ADCAN17 – ADC AN17 Interrupt                          | 116     | 108     | 0x0000EC          | IFS6<12> | IEC6<12>       | IPC27<2:0>   |

| ADCAN18 – ADC AN18 Interrupt                          | 117     | 109     | 0x0000EE          | IFS6<13> | IEC6<13>       | IPC27<6:4>   |

| ADCAN19 – ADC AN19 Interrupt                          | 118     | 110     | 0x0000F0          | IFS6<14> | IEC6<14>       | IPC27<10:8>  |

| ADCAN20 – ADC AN20 Interrupt                          | 119     | 111     | 0x0000F2          | IFS6<15> | IEC6<15>       | IPC27<14:12> |

| Reserved                                              | 120-122 | 112-114 | 0x0000F4-0x0000F8 | _        | _              | _            |

| ADFLT – ADC Fault                                     | 123     | 115     | 0x0000FA          | IFS7<3>  | IEC7<3>        | IPC28<14:12> |

| ADCMP0 – ADC Digital Comparator 0                     | 124     | 116     | 0x0000FC          | IFS7<4>  | IEC7<4>        | IPC29<2:0>   |

| ADCMP1 – ADC Digital Comparator 1                     | 125     | 117     | 0x0000FE          | IFS7<5>  | IEC7<5>        | IPC29<6:4>   |

| ADCMP2 – ADC Digital Comparator 2                     | 126     | 118     | 0x000100          | IFS7<6>  | IEC7<6>        | IPC29<10:8>  |

| ADCMP3 – ADC Digital Comparator 3                     | 127     | 119     | 0x000102          | IFS7<7>  | IEC7<7>        | IPC29<14:12> |

| ADFLTR0 – ADC Oversample Filter 0                     | 128     | 120     | 0x000104          | IFS7<8>  | IEC7<8>        | IPC30<2:0>   |

| ADFLTR1 – ADC Oversample Filter 1                     | 129     | 121     | 0x000106          | IFS7<9>  | IEC7<9>        | IPC30<6:4>   |

| ADFLTR2 – ADC Oversample Filter 2                     | 130     | 122     | 0x000108          | IFS7<10> | IEC7<10>       | IPC30<10:8>  |

| ADFLTR3 – ADC Oversample Filter 3                     | 131     | 123     | 0x00010A          | IFS7<11> | IEC7<11>       | IPC30<14:12> |

| CLC1P – CLC1 Positive Edge                            | 132     | 124     | 0x00010C          | IFS7<12> | IEC7<12>       | IPC31<2:0>   |

| CLC2P – CLC2 Positive Edge                            | 133     | 125     | 0x00010E          | IFS7<13> | IEC7<13>       | IPC31<6:4>   |

| SPI1G – SPI1 Error                                    | 134     | 126     | 0x000110          | IFS7<14> | IEC7<14>       | IPC31<10:8>  |

| SPI2G – SPI2 Error                                    | 135     | 127     | 0x000112          | IFS7<15> | IEC7<15>       | IPC31<14:12> |

| Reserved                                              | 136     | 128     | 0x000114          | —        | _              | —            |

| MSIS1 – MSI Slave Initiated Interrupt                 | 137     | 129     | 0x000116          | IFS8<1>  | IEC8<1>        | IPC32<6:4>   |

| MSIA – MSI Protocol A                                 | 138     | 130     | 0x000118          | IFS8<2>  | IEC8<2>        | IPC32<10:8>  |

| MSIB – MSI Protocol B                                 | 139     | 131     | 0x00011A          | IFS8<3>  | IEC8<3>        | IPC32<14:12> |

| MSIC – MSI Protocol C                                 | 140     | 132     | 0x00011C          | IFS8<4>  | IEC8<4>        | IPC33<2:0>   |

| MSID – MSI Protocol D                                 | 141     | 133     | 0x00011E          | IFS8<5>  | IEC8<5>        | IPC33<6:4>   |

| MSIE – MSI Protocol E                                 | 142     | 134     | 0x000120          | IFS8<6>  | IEC8<6>        | IPC33<10:8>  |

| MSIF – MSI Protocol F                                 | 143     | 135     | 0x000122          | IFS8<7>  | IEC8<7>        | IPC33<14:12> |

| MSIG – MSI Protocol G                                 | 144     | 136     | 0x000124          | IFS8<8>  | IEC8<8>        | IPC34<2:0>   |

| MSIH – MSI Protocol H                                 | 145     | 137     | 0x000126          | IFS8<9>  | IEC8<9>        | IPC34<6:4>   |

| MSIDT – Master Read FIFO Data Ready                   | 146     | 138     | 0x000128          | IFS8<10> | IEC8<10>       | IPC34<10:8>  |

| MSIWFE – Master Write FIFO Empty                      | 147     | 139     | 0x00012A          | IFS8<11> | IEC8<11>       | IPC34<14:12> |

| MSIFLT – Read or Write FIFO Fault<br>(Over/Underflow) | 148     | 140     | 0x00012C          | IFS8<12> | IEC8<12>       | IPC35<2:0>   |

| S1SRST – MSI Slave Reset                              | 149     | 141     | 0x00012E          | IFS8<13> | IEC8<13>       | IPC35<6:4>   |

| Reserved                                              | 150-153 | 142-145 | 0x000130-0x000136 | —        | —              | —            |

| S1BRK – Slave Break                                   | 154     | 146     | 0x000138          | IFS9<2>  | IEC9<2>        | IPC36<10:8>  |

| Reserved                                              | 155-156 | 147-148 | 0x00013A-0x00013C | —        | —              | —            |

| CCP7 – Input Capture/Output Compare 7                 | 157     | 149     | 0x00013E          | IFS9<5>  | IEC9<5>        | IPC37<6:4>   |

| CCT7 – CCP7 Timer                                     | 158     | 150     | 0x000140          | IFS9<6>  | IEC9<6>        | IPC37<10:8>  |

| Reserved                                              | 159     | 151     | 0x000142          | —        |                | —            |

| CCP8 – Input Capture/Output Compare 8                 | 160     | 152     | 0x000144          | IFS9<8>  | IEC9<8>        | IPC38<2:0>   |

| CCT8 – CCP8 Timer                                     | 161     | 153     | 0x000146          | IFS9<9>  | IEC9<9>        | IPC38<6:4>   |

| Reserved                                              | 162-164 | 154-156 | 0x000148-0x00014C | —        |                | —            |

| S1CLKF – Slave Clock Fail                             | 165     | 157     | 0x00014E          | IFS9<13> | IEC9<13>       | IPC39<6:4>   |

| Reserved                                              | 166-175 | 158-167 | 0x000150-0x000162 | —        | —              | —            |

| ADFIFO – ADC FIFO Ready                               | 176     | 168     | 0x000164          | IFS10<8> | IEC10<8>       | IPC42<2:0>   |

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/Os and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

# 3.6.8 CONTROLLING CONFIGURATION CHANGES

Because peripheral mapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. The dsPIC33CH128MP508 devices have implemented the control register lock sequence.

# 3.6.8.1 CONTROL REGISTER LOCK

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (RPCON<11>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, the NVMKEY unlock sequence must be executed:

- 1. Write 0x55 to NVMKEY.

- 2. Write 0xAA to NVMKEY.

- 3. Clear (or set) IOLOCK as a single operation.

IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all of the control registers. Then, IOLOCK can be set with a second lock sequence.

Note: MPLAB<sup>®</sup> C30 provides a built-in C language function for unlocking and modifying the RPCON register: \_\_builtin\_write\_RPCON(value); For more information, see the MPLAB C30 Help files.

### 3.6.9 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control Peripheral Pin Selection introduces several considerations into application design that most users would never think of otherwise. This is particularly true for several common peripherals, which are only available as remappable peripherals.

The main consideration is that the Peripheral Pin Selects are not available on default pins in the device's default (Reset) state. More specifically, because all RPINRx registers reset to '1's and RPORx registers reset to '0's, this means all PPS inputs are tied to Vss, while all PPS outputs are disconnected. This means that before any other application code is executed, the user must initialize the device with the proper peripheral configuration. Because the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset. For application safety, however, it is always better to set IOLOCK and lock the configuration after writing to the control registers.

The NVMKEY unlock sequence must be executed as an Assembly language routine. If the bulk of the application is written in C, or another high-level language, the unlock sequence should be performed by writing in-line assembly or by using the \_\_builtin\_write\_RPCON(value) function provided by the compiler.

Choosing the configuration requires a review of all Peripheral Pin Selects and their pin assignments, particularly those that will not be used in the application. In all cases, unused pin-selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output.

# 3.6.10 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping. Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit index value maps the RPn pin with the corresponding value, or internal signal, to that peripheral. See Table 3-30 for a list of available inputs.

For example, Figure 3-20 illustrates remappable pin selection for the U1RX input.

#### REGISTER 3-51: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| R/W-0      | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |  |

|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|

| QEIHOM1R7  | QEIHOM1R6 | QEIHOM1R5 | QEIHOM1R4 | QEIHOM1R3 | QEIHOM1R2 | QEIHOM1R1 | QEIHOM1R0 |  |

| bit 15 bit |           |           |           |           |           |           |           |  |

| R/W-0       | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |  |

|-------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|

| QEINDX1R7   | QEINDX1R6 | QEINDX1R5 | QEINDX1R4 | QEINDX1R3 | QEINDX1R2 | QEINDX1R1 | QEINDX1R0 |  |

| bit 7 bit 0 |           |           |           |           |           |           |           |  |

| Legend:           |                                                                    |                      |                    |  |  |

|-------------------|--------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                   | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-8 **QEIHOM1R<7:0>:** Assign QEI Home 1 Input (QEIHOM1) to the Corresponding RPn Pin bits See Table 3-30.

#### REGISTER 3-52: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| U1DSRR7 | U1DSRR6 | U1DSRR5 | U1DSRR4 | U1DSRR3 | U1DSRR2 | U1DSRR1 | U1DSRR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| U1RXR7 | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 **U1DSRR<7:0>:** Assign UART1 Data-Set-Ready (U1DSR) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **U1RXR<7:0>:** Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **QEINDX1R<7:0>:** Assign QEI Index 1 Input (QEINDX1) to the Corresponding RPn Pin bits See Table 3-30.

# TABLE 3-40: MASTER PPS OUTPUT CONTROL REGISTERS

| Register | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|----------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|

| RPOR0    | _      | —      | RP33R5  | RP33R4  | RP33R3  | RP33R2  | RP33R1  | RP33R0  | —     | —     | RP32R5  | RP32R4  | RP32R3  | RP32R2  | RP32R1  | RP32R0  |

| RPOR1    | _      | _      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | _     | _     | RP34R5  | RP34R4  | RP34R3  | RP34R2  | RP34R1  | RP34R0  |

| RPOR2    | _      | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  | _     | _     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  |

| RPOR3    | _      | —      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  | —     | —     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  |

| RPOR4    | —      | —      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | —     | —     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  |

| RPOR5    | —      | —      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | —     | _     | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  |

| RPOR6    | —      | —      | RP45R5  | RP45R4  | RP45R3  | RP45R2  | RP45R1  | RP45R0  | —     | —     | RP44R5  | RP44R4  | RP44R3  | RP44R2  | RP44R1  | RP44R0  |

| RPOR7    | —      | —      | RP47R5  | RP47R4  | RP47R3  | RP47R2  | RP47R1  | RP47R0  | —     | —     | RP46R5  | RP46R4  | RP46R3  | RP46R2  | RP46R1  | RP46R0  |

| RPOR8    | —      | _      | RP49R5  | RP49R4  | RP49R3  | RP49R2  | RP49R1  | RP49R0  | _     | —     | RP48R5  | RP48R4  | RP48R3  | RP48R2  | RP48R1  | RP48R0  |

| RPOR9    | _      | —      | RP51R5  | RP51R4  | RP51R3  | RP51R2  | RP51R1  | RP51R0  | _     | —     | RP50R5  | RP50R4  | RP50R3  | RP50R2  | RP50R1  | RP50R0  |

| RPOR10   | _      | —      | RP53R5  | RP53R4  | RP53R3  | RP53R2  | RP53R1  | RP53R0  | _     | —     | RP52R5  | RP52R4  | RP52R3  | RP52R2  | RP52R1  | RP52R0  |

| RPOR11   | _      | —      | RP55R5  | RP55R4  | RP55R3  | RP55R2  | RP55R1  | RP55R0  | _     | —     | RP54R5  | RP54R4  | RP54R3  | RP54R2  | RP54R1  | RP54R0  |

| RPOR12   | _      | —      | RP57R5  | RP57R4  | RP57R3  | RP57R2  | RP57R1  | RP57R0  | _     | —     | RP56R5  | RP56R4  | RP56R3  | RP56R2  | RP56R1  | RP56R0  |

| RPOR13   | —      | _      | RP59R5  | RP59R4  | RP59R3  | RP59R2  | RP59R1  | RP59R0  | _     | —     | RP58R5  | RP58R4  | RP58R3  | RP58R2  | RP58R1  | RP58R0  |

| RPOR14   | —      | —      | RP61R5  | RP61R4  | RP61R3  | RP61R2  | RP61R1  | RP61R0  | —     | —     | RP60R5  | RP60R4  | RP60R3  | RP60R2  | RP60R1  | RP60R0  |

| RPOR15   | —      | —      | RP63R5  | RP63R4  | RP63R3  | RP63R2  | RP63R1  | RP63R0  | —     | —     | RP62R5  | RP62R4  | RP62R3  | RP62R2  | RP62R1  | RP62R0  |

| RPOR16   | —      | —      | RP65R5  | RP65R4  | RP65R3  | RP65R2  | RP65R1  | RP65R0  | —     | —     | RP64R5  | RP64R4  | RP64R3  | RP64R2  | RP64R1  | RP64R0  |

| RPOR17   | —      | —      | RP67R5  | RP67R4  | RP67R3  | RP67R2  | RP67R1  | RP67R0  | —     | —     | RP66R5  | RP66R4  | RP66R3  | RP66R2  | RP66R1  | RP66R0  |

| RPOR18   | —      | —      | RP69R5  | RP69R4  | RP69R3  | RP69R2  | RP69R1  | RP69R0  | —     | —     | RP68R5  | RP68R4  | RP68R3  | RP68R2  | RP68R1  | RP68R0  |

| RPOR19   | —      | —      | RP71R5  | RP71R4  | RP71R3  | RP71R2  | RP71R1  | RP71R0  | —     | —     | RP70R5  | RP70R4  | RP70R3  | RP70R2  | RP70R1  | RP70R0  |

| RPOR20   | —      | —      | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 | —     | _     | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 |

| RPOR21   | —      | —      | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 | —     | _     | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |

| RPOR22   | _      | _      | RP181R5 | RP181R4 | RP181R3 | RP181R2 | RP181R1 | RP181R0 | _     | _     | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 |

| R/W-0         | R/W-0        | R/W-0                                  | R/W-0           | R/W-0            | R/W-0           | U-0             | U-0   |

|---------------|--------------|----------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| IVMIE         | WAKIE        | CERRIE                                 | SERRIE          | RXOVIE           | TXATIE          |                 |       |

| bit 15        |              |                                        |                 |                  |                 |                 | bit 8 |

|               |              |                                        |                 |                  |                 |                 |       |

| U-0           | U-0          | U-0                                    | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| _             | —            | —                                      | TEFIE           | MODIE            | TBCIE           | RXIE            | TXIE  |

| bit 7         |              |                                        |                 |                  |                 |                 | bit 0 |

|               |              |                                        |                 |                  |                 |                 |       |

| Legend:       |              |                                        |                 |                  |                 |                 |       |

| R = Readable  |              | W = Writable b                         | bit             | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at | POR          | '1' = Bit is set                       |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|               |              |                                        |                 |                  |                 |                 |       |

| bit 15        |              | d Message Inter                        | -               | it               |                 |                 |       |

|               |              | essage interrup                        |                 |                  |                 |                 |       |

| bit 14        |              | Wake-up Activit                        |                 | abla bit         |                 |                 |       |

| DIL 14        |              | activity interrup                      | •               | able bit         |                 |                 |       |

|               |              | Activity Interrup                      |                 |                  |                 |                 |       |

| bit 13        | CERRIE: CA   | N Bus Error Inte                       | errupt Enable b | bit              |                 |                 |       |

|               | 1 = CAN bus  | error interrupt is                     | s enabled       |                  |                 |                 |       |

|               | 0 = CAN bus  | error interrupt is                     | s disabled      |                  |                 |                 |       |

| bit 12        | -            | stem Error Interr                      | -               |                  |                 |                 |       |

|               |              | error interrupt is                     |                 |                  |                 |                 |       |

| bit 11        | -            | error interrupt is                     |                 | t Enchlo hit     |                 |                 |       |

| bit 11        |              | ceive Buffer Ove<br>buffer overflow i  | •               |                  |                 |                 |       |

|               |              | buffer overflow i                      | •               |                  |                 |                 |       |

| bit 10        | TXATIE: Trai | nsmit Attempt In                       | terrupt Enable  | e bit            |                 |                 |       |

|               | 1 = Transmit | attempt interrup                       | t is enabled    |                  |                 |                 |       |

|               | 0 = Transmit | attempt interrup                       | t is disabled   |                  |                 |                 |       |

| bit 9-5       | Unimplemer   | nted: Read as '0                       | )'              |                  |                 |                 |       |

| bit 4         |              | smit Event FIFO                        | •               |                  |                 |                 |       |

|               |              | event FIFO inte<br>event FIFO inte     |                 |                  |                 |                 |       |

| bit 3         |              | le Change Interr                       | •               |                  |                 |                 |       |

| DIL 3         |              | ange interrupt is                      | -               |                  |                 |                 |       |

|               |              | ange interrupt is                      |                 |                  |                 |                 |       |

| bit 2         |              | Timer Interrupt                        |                 |                  |                 |                 |       |

|               | 1 = CAN time | er interrupt is en                     | abled           |                  |                 |                 |       |

|               | 0 = CAN time | er interrupt is dis                    | abled           |                  |                 |                 |       |

| bit 1         |              | ve Object Interru                      | -               |                  |                 |                 |       |

|               |              | object interrupt i                     |                 |                  |                 |                 |       |

| hit 0         |              | object interrupt i                     |                 |                  |                 |                 |       |

| bit 0         |              | nit Object Interru<br>object interrupt |                 |                  |                 |                 |       |

|               |              |                                        |                 |                  |                 |                 |       |

### REGISTER 3-116: C1INTH: CAN INTERRUPT REGISTER HIGH

# 4.2.2 DATA ADDRESS SPACE (SLAVE)

The dsPIC33CH128MP508S1 family CPU has a separate 16-bit wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory map is shown in Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes or 32K words.

The lower half of the data memory space (i.e., when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV).

The dsPIC33CH128MP508S1 family devices implement up to 4 Kbytes of data memory. If an EA points to a location outside of this area, an all-zero word or byte is returned.

#### 4.2.2.1 Data Space Width

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2.2 Data Memory Organization and Alignment

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33CH128MP508S1 family instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through wordaligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

### 4.2.2.3 SFR Space

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33CH128MP508S1 family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

### 4.2.2.4 Near Data Space

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

#### REGISTER 4-28: CNPUX: CHANGE NOTIFICATION PULL-UP ENABLE FOR PORTX REGISTER

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|------------------------------------|-------|----------------|-------|-----------------------------------------|-------|-------|-------|--|--|--|

|                                    |       |                | CNPL  | Jx<15:8>                                |       |       |       |  |  |  |

| bit 15                             |       |                |       |                                         |       |       | bit 8 |  |  |  |

|                                    |       |                |       |                                         |       |       |       |  |  |  |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                                    |       |                | CNP   | Ux<7:0>                                 |       |       |       |  |  |  |

| bit 7                              |       |                |       |                                         |       |       | bit 0 |  |  |  |

|                                    |       |                |       |                                         |       |       |       |  |  |  |

| Legend:                            |       |                |       |                                         |       |       |       |  |  |  |

| R = Readable                       | bit   | W = Writable b | it    | U = Unimplemented bit, read as '0'      |       |       |       |  |  |  |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |  |

bit 15-0

0 **CNPUx<15:0>:** Change Notification Pull-up Enable for PORTx bits

1 = The pull-up for PORTx[n] is enabled – takes precedence over pull-down selection

0 = The pull-up for PORTx[n] is disabled

#### REGISTER 4-29: CNPDx: CHANGE NOTIFICATION PULL-DOWN ENABLE FOR PORTx REGISTER

| R/W-0                                                                     | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0                          | R/W-0 | R/W-0 |  |  |

|---------------------------------------------------------------------------|-------|----------------|-------|--------------|--------------------------------|-------|-------|--|--|

|                                                                           |       |                | CNPE  | )x<15:8>     |                                |       |       |  |  |

| bit 15                                                                    |       |                |       |              |                                |       | bit 8 |  |  |

| R/W-0                                                                     | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0                          | R/W-0 | R/W-0 |  |  |

|                                                                           |       |                | CNPI  | Dx<7:0>      |                                |       |       |  |  |

| bit 7                                                                     |       |                |       |              |                                |       | bit 0 |  |  |

|                                                                           |       |                |       |              |                                |       |       |  |  |

| Legend:                                                                   |       |                |       |              |                                |       |       |  |  |

| R = Readable                                                              | bit   | W = Writable I | bit   | U = Unimpler | Unimplemented bit, read as '0' |       |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |       |                |       |              |                                | nown  |       |  |  |

bit 15-0 CNPDx<15:0>: Change Notification Pull-Down Enable for PORTx bits

1 = The pull-down for PORTx[n] is enabled (if the pull-up for PORTx[n] is not enabled)

0 = The pull-down for PORTx[n] is disabled

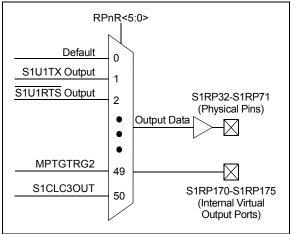

## 4.6.5.7 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains sets of 6-bit fields, with each set associated with one S1RPn pin (see Register 4-60 through Register 4-82). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 4-31 and Figure 4-19).

A null output is associated with the PPS Output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 4-19: MULTIPLEXING REMAPPABLE OUTPUTS FOR S1RPn

Note 1: There are six virtual output ports which are not connected to any I/O ports (S1RP170-S1RP175). These virtual ports can be accessed by RPOR20, RPOR21 and RPOR22.

## 4.6.5.8 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings, across any or all of the S1RPn pins, is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs, and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

### 4.6.6 I/O HELPFUL TIPS

- 1. In some cases, certain pins, as defined in Table 24-18 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or lesser than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low-side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins, by default, after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Select for PORTx registers, in the I/O ports module (i.e., ANSELx), by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx =  $0 \times 0$ , while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in Section 24.0 "Electrical Characteristics" of this data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted.

#### REGISTER 10-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS (CONTINUED)

bit 3-0 MOD<3:0>: CCPx Mode Select bits

For CCSEL = 1 (Input Capture modes):

- 1xxx = Reserved

- 011x = Reserved

- 0101 = Capture every 16th rising edge

- 0100 = Capture every 4th rising edge

- 0011 = Capture every rising and falling edge

- 0010 = Capture every falling edge

- 0001 = Capture every rising edge

- 0000 = Capture every rising and falling edge (Edge Detect mode)

#### For CCSEL = 0 (Output Compare/Timer modes):

- 1111 = External Input mode: Pulse generator is disabled, source is selected by ICS<2:0>

- 1110 = Reserved

- 110x = Reserved

- 10xx = Reserved

- 0111 = Reserved

- 0110 = Reserved

- 0101 = Dual Edge Compare mode, buffered

- 0100 = Dual Edge Compare mode

- 0011 = 16-Bit/32-Bit Single Edge mode, toggles output on compare match

- 0010 = 16-Bit/32-Bit Single Edge mode, drives output low on compare match

- 0001 = 16-Bit/32-Bit Single Edge mode, drives output high on compare match

- 0000 = 16-Bit/32-Bit Timer mode, output functions are disabled

- Note 1: Clock selection is the same for the Master and the Slave.

#### REGISTER 13-1: UXMODE: UARTX CONFIGURATION REGISTER (CONTINUED)

- bit 5 UTXEN: UART Transmit Enable bit

- 1 = Transmit enabled except during Auto-Baud Detection

- 0 = Transmit disabled all transmit counters, pointers and state machines are reset; TX buffer is not flushed, status bits are not reset

#### bit 4 URXEN: UART Receive Enable bit

- 1 = Receive enabled except during Auto-Baud Detection

- 0 = Receive disabled all receive counters, pointers and state machines are reset; RX buffer is not flushed, status bits are not reset

#### bit 3-0 MOD<3:0>: UART Mode bits

- Other = Reserved

- 1111 = Smart card<sup>(2)</sup>

- 1110 = IrDA<sup>®(2)</sup>

- 1101 = Reserved

- 1100 = LIN Master/Slave

- 1011 = LIN Slave only

- 1010 = DMX<sup>(2)</sup>

- 1001 = Reserved

- 1000 = Reserved

- 0111 = Reserved

- 0110 = Reserved

- 0101 = Reserved

- 0100 = Asynchronous 9-bit UART with address detect, ninth bit = 1 signals address

- 0011 = Asynchronous 8-bit UART without address detect, ninth bit is used as an even parity bit

- 0010 = Asynchronous 8-bit UART without address detect, ninth bit is used as an odd parity bit

- 0001 = Asynchronous 7-bit UART

- 0000 = Asynchronous 8-bit UART

Note 1: R/HS/HC in DMX and LIN mode.

2: These modes are not available on all devices.

# REGISTER 21-4: FOSCSEL CONFIGURATION REGISTER

| U-1                           | U-1                                                                                              | U-1                                                                                   | U-1              | U-1                               | U-1              | U-1             | U-1    |  |  |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------|-----------------------------------|------------------|-----------------|--------|--|--|--|--|--|

| _                             | _                                                                                                | _                                                                                     |                  | _                                 |                  | —               | _      |  |  |  |  |  |

| bit 23                        | ·                                                                                                |                                                                                       |                  | ·                                 |                  | •               | bit 16 |  |  |  |  |  |

|                               |                                                                                                  |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

| U-1                           | U-1                                                                                              | U-1                                                                                   | U-1              | U-1                               | U-1              | U-1             | U-1    |  |  |  |  |  |

|                               | —                                                                                                | —                                                                                     | —                | —                                 |                  | —               | —      |  |  |  |  |  |

| bit 15                        |                                                                                                  |                                                                                       |                  |                                   |                  |                 | bit 8  |  |  |  |  |  |

|                               |                                                                                                  |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

| R/PO-1                        | U-1                                                                                              | U-1                                                                                   | U-1              | U-1                               | R/PO-1           | R/PO-1          |        |  |  |  |  |  |

| IESO                          | —                                                                                                | —                                                                                     |                  | —                                 | FNOSC0           |                 |        |  |  |  |  |  |

| bit 7                         |                                                                                                  | bit C                                                                                 |                  |                                   |                  |                 |        |  |  |  |  |  |

|                               |                                                                                                  |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

| Legend: PO = Program Once bit |                                                                                                  |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

| R = Readab                    | le bit                                                                                           | W = Writable                                                                          | bit              | U = Unimplen                      | nented bit, read | l as '0'        |        |  |  |  |  |  |

| -n = Value a                  | t POR                                                                                            | '1' = Bit is set                                                                      |                  | '0' = Bit is clea                 | ared             | x = Bit is unkr | iown   |  |  |  |  |  |

|                               |                                                                                                  |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

| bit 23-8                      | Unimplemen                                                                                       | ted: Read as '1                                                                       | L'               |                                   |                  |                 |        |  |  |  |  |  |

| bit 7                         | IESO: Interna                                                                                    | I External Swite                                                                      | chover bit       |                                   |                  |                 |        |  |  |  |  |  |

|                               |                                                                                                  |                                                                                       |                  | nabled (Two-Sp<br>isabled (Two-Sp |                  |                 |        |  |  |  |  |  |

| bit 6-3                       |                                                                                                  | ted: Read as '1                                                                       |                  |                                   | ·                | ,               |        |  |  |  |  |  |

| bit 2-0                       | •                                                                                                | : Initial Oscillat                                                                    |                  | ection bits                       |                  |                 |        |  |  |  |  |  |

|                               | 111 = Interna                                                                                    | I Fast RC (FRC                                                                        | C) Oscillator wi | th Postscaler                     |                  |                 |        |  |  |  |  |  |

|                               | 110 = Backup Fast RC (BFRC)                                                                      |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

|                               | 101 = LPRC Oscillator                                                                            |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

|                               | 100 = Reserved                                                                                   |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

|                               | 011 = Primary Oscillator with PLL (XTPLL, HSPLL, ECPLL)<br>010 = Primary (XT, HS, EC) Oscillator |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

|                               |                                                                                                  |                                                                                       |                  |                                   |                  |                 |        |  |  |  |  |  |

|                               |                                                                                                  | 001 = Internal Fast RC Oscillator with PLL (FRCPLL)<br>000 = Fast RC (FRC) Oscillator |                  |                                   |                  |                 |        |  |  |  |  |  |

000 = Fast RC (FRC) Oscillator

#### REGISTER 21-32: DEVREV: DEVICE REVISION REGISTER

| Legend: | R = Read-only bit |   |        | U = Unimpler | nented bit |   |        |

|---------|-------------------|---|--------|--------------|------------|---|--------|

| bit 7   |                   |   |        |              |            |   | bit 0  |

|         |                   |   | DEVRE  | V<7:0>       |            |   |        |

| R       | R                 | R | R      | R            | R          | R | R      |

| bit 15  |                   |   |        |              |            |   | bit 8  |

|         |                   |   | DEVRE  | V<15:8>      |            |   |        |

| R       | R                 | R | R      | R            | R          | R | R      |

| bit 23  |                   |   |        |              |            |   | bit 16 |

|         |                   |   | DEVREV | /<23:16>     |            |   |        |

| R       | R                 | R | R      | R            | R          | R | R      |

bit 23-0 **DEVREV<23:0>:** Device Revision bits

#### **REGISTER 21-33: DEVID: DEVICE ID REGISTERS**

| U-1                 |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| —                   | —                   |                     |                     | —                   |                     |                     | —                   |

| bit 23              |                     |                     |                     |                     |                     |                     | bit 16              |

|                     |                     |                     |                     |                     |                     |                     |                     |

| R                   | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

| FAMID7              | FAMID6              | FAMID5              | FAMID4              | FAMID3              | FAMID2              | FAMID1              | FAMID0              |

| bit 15              |                     |                     |                     |                     |                     |                     | bit 8               |

|                     |                     |                     |                     |                     |                     |                     |                     |

| R                   | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

| DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> | DEV2 <sup>(1)</sup> | DEV1 <sup>(1)</sup> | DEV0 <sup>(1)</sup> |

| bit 7               |                     |                     |                     |                     |                     |                     | bit 0               |

|                     |                     |                     |                     |                     |                     |                     |                     |

| Legend: R =         | Read-only bit       |                     |                     | U = Unimpler        | nented bit          |                     |                     |

|                     |                     |                     |                     |                     |                     |                     |                     |

| bit 23-16           | Unimplement         | ted: Read as ':     | L'                  |                     |                     |                     |                     |

bit 15-8 **FAMID<7:0>:** Device Family Identifier bits 1000 0111 = dsPIC33CH128MP508 family

bit 7-0 DEV<7:0>: Individual Device Identifier bits<sup>(1)</sup>

Note 1: See Table 21-5 for the list of Device Identifier bits.

# 22.0 INSTRUCTION SET SUMMARY

**Note:** This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33CH instruction set is almost identical to that of the dsPIC30F and dsPIC33F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 22-1 lists the general symbols used in describing the instructions.

The dsPIC33 instruction set summary in Table 22-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

# 23.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 23.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 23.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 23.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

#### TABLE 24-20: I/O PIN INPUT INJECTION CURRENT SPECIFICATIONS

| -            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                |      |                     |       |                                                                                                                               |  |  |  |  |  |

|--------------|------------------------------------------------------|--------------------------------------------------------------------------------|------|---------------------|-------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Param<br>No. | Symbol                                               | Characteristic                                                                 | Min. | Max.                | Units | Conditions                                                                                                                    |  |  |  |  |  |

| DI60a        | licl                                                 | Input Low Injection Current                                                    | 0    | -5 <sup>(1,4)</sup> | mA    | All pins                                                                                                                      |  |  |  |  |  |

| DI60b        | Іісн                                                 | Input High Injection Current                                                   | 0    | +5(2,3,4)           | mA    | All pins, excepting all 5V tolerant pins and SOSCI                                                                            |  |  |  |  |  |