#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit Dual-Core                                                                 |

| Speed                      | 180MHz, 200MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 152KB (152K x 8)                                                                 |

| Program Memory Type        | FLASH, PRAM                                                                      |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 20K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 23x12b; D/A 4x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch128mp502-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Feature                      | Master Core       | Slave Core                      | Shared |

|------------------------------|-------------------|---------------------------------|--------|

| Core Frequency               | 90 MIPS @ 180 MHz | 100 MIPS @ 200 MHz              | _      |

| Program Memory               | 64K-128 Kbytes    | 24 Kbytes (PRAM) <sup>(2)</sup> | _      |

| Internal Data RAM            | 16 Kbytes         | 4 Kbytes                        | _      |

| 16-Bit Timer                 | 1                 | 1                               | _      |

| DMA                          | 6                 | 2                               | _      |

| SCCP (Capture/Compare/Timer) | 8                 | 4                               | _      |

| UART                         | 2                 | 1                               | _      |

| SPI/I <sup>2</sup> S         | 2                 | 1                               | _      |

| I <sup>2</sup> C             | 2                 | 1                               | _      |

| CAN FD                       | 1                 | _                               | _      |

| SENT                         | 2                 | _                               | _      |

| CRC                          | 1                 | _                               | _      |

| QEI                          | 1                 | 1                               | _      |

| PTG                          | 1                 | _                               | _      |

| CLC                          | 4                 | 4                               | _      |

| 16-Bit High-Speed PWM        | 4                 | 8                               | _      |

| ADC 12-Bit                   | 1                 | 3                               | _      |

| Digital Comparator           | 4                 | 4                               | _      |

| 12-Bit DAC/Analog CMP Module | 1                 | 3                               | _      |

| Watchdog Timer               | 1                 | 1                               | _      |

| Deadman Timer                | 1                 | —                               | _      |

| Input/Output                 | 69                | 69                              | 69     |

| Simple Breakpoints           | 5                 | 2                               | _      |

| PGAs <sup>(1)</sup>          | —                 | 3                               | 3      |

| DAC Output Buffer            | —                 |                                 | 1      |

| Oscillator                   | 1                 | 1                               | 1      |

#### TABLE 1: MASTER AND SLAVE CORE FEATURES

Note 1: Slave owns the peripheral/feature, but it is shared with the Master.

2: Dual Partition feature is available on Slave PRAM.

#### 3.2.7.3 Modulo Addressing Applicability

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

| The modulo corrected Effective Address       |

|----------------------------------------------|

| is written back to the register only when    |

| Pre-Modify or Post-Modify Addressing         |

| mode is used to compute the Effective        |

| Address. When an address offset (such as     |

| [W7 + W2]) is used, Modulo Addressing        |

| correction is performed, but the contents of |

| the register remain unchanged.               |

|                                              |

## 3.2.8 BIT-REVERSED ADDRESSING

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

#### 3.2.8.1 Bit-Reversed Addressing Implementation

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed        |

|-------|-------------------------------------------|

|       | Addressing can be enabled simultaneously  |

|       | using the same W register, but Bit-       |

|       | Reversed Addressing operation will always |

|       | take precedence for data writes when      |

|       | enabled.                                  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### TABLE 3-23: MASTER INTERRUPT VECTOR DETAILS (CONTINUED)

|                                      | Vector | or IRQ<br># | IVT Address       | Interrupt Bit Location |          |              |

|--------------------------------------|--------|-------------|-------------------|------------------------|----------|--------------|

| Interrupt Source                     | #      |             |                   | Flag                   | Enable   | Priority     |

| QEI1 – QEI Position Counter Compare  | 56     | 48          | 0x000074          | IFS3<0>                | IEC3<0>  | IPC12<2:0>   |

| U1E – UART1 Error                    | 57     | 49          | 0x000076          | IFS3<1>                | IEC3<1>  | IPC12<6:4>   |

| U2E – UART2 Error                    | 58     | 50          | 0x000078          | IFS3<2>                | IEC3<2>  | IPC12<10:8>  |

| CRC – CRC Generator                  | 59     | 51          | 0x00007A          | IFS3<3>                | IEC3<3>  | IPC12<14:12> |

| C1TX – CAN1 TX Data Request          | 60     | 52          | 0x00007C          | IFS3<4>                | IEC3<4>  | IPC13<2:0>   |

| Reserved                             | 61-68  | 53-68       | 0x00007E-0x00008C | —                      | _        | _            |

| ICD – In-Circuit Debugger            | 69     | 61          | 0x00008E          | IFS3<13>               | IEC3<13> | IPC15<6:4>   |

| JTAG – JTAG Programming              | 70     | 62          | 0x000090          | IFS3<14>               | IEC3<14> | IPC15<10:8>  |

| PTGSTEP – PTG Step                   | 71     | 63          | 0x000092          | IFS3<15>               | IEC3<15> | IPC15<14:12> |

| I2C1BC – I2C1 Bus Collision          | 72     | 64          | 0x000094          | IFS4<0>                | IEC4<0>  | IPC16<2:0>   |

| I2C2BC – I2C2 Bus Collision          | 73     | 65          | 0x000096          | IFS4<1>                | IEC4<1>  | IPC16<6:4>   |

| Reserved                             | 74     | 66          | 0x000098          | —                      | _        | _            |

| PWM1 – PWM Generator 1               | 75     | 67          | 0x00009A          | IFS4<3>                | IEC4<3>  | IPC16<14:12> |

| PWM2 – PWM Generator 2               | 76     | 68          | 0x00009C          | IFS4<4>                | IEC4<4>  | IPC17<2:0>   |

| PWM3 – PWM Generator 3               | 77     | 69          | 0x00009E          | IFS4<5>                | IEC4<5>  | IPC17<6:4>   |

| PWM4 – PWM Generator 4               | 78     | 70          | 0x0000A0          | IFS4<6>                | IEC4<6>  | IPC17<10:8>  |

| Reserved                             | 79-82  | 71-74       | 0x0000A2          | —                      | _        | _            |

| CND – Change Notice D                | 83     | 75          | 0x0000AA          | IFS4<11>               | IEC4<11> | IPC18<14:12> |

| CNE – Change Notice E                | 84     | 76          | 0x0000AC          | IFS4<12>               | IEC4<12> | IPC19<2:0>   |

| CMP1 – Comparator 1                  | 85     | 77          | 0x0000AE          | IFS4<13>               | IEC4<13> | IPC19<6:4>   |

| Reserved                             | 86-88  | 78-80       | 0x0000B0-0x0000B4 | _                      | _        | —            |

| PTGWDT – PTG Watchdog Timer Time-out | 89     | 81          | 0x0000B6          | IFS5<1>                | IEC5<1>  | IPC20<6:4>   |

| PTG0 – PTG Trigger 0                 | 90     | 82          | 0x0000B8          | IFS5<2>                | IEC5<2>  | IPC20<10:8>  |

| PTG1 – PTG Trigger 1                 | 91     | 83          | 0x0000BA          | IFS5<3>                | IEC5<3>  | IPC20<14:12> |

| PTG2 – PTG Trigger 2                 | 92     | 84          | 0x0000BC          | IFS5<4>                | IEC5<4>  | IPC21<2:0>   |

| PTG3 – PTG Trigger 3                 | 93     | 85          | 0x0000BE          | IFS5<5>                | IEC5<6>  | IPC21<6:4>   |

| SENT1 – SENT1 TX/RX                  | 94     | 86          | 0x0000C0          | IFS5<6>                | IEC5<6>  | IPC21<10:8>  |

| SENT1E – SENT1 Error                 | 95     | 87          | 0x0000C2          | IFS5<7>                | IEC5<7>  | IPC21<14:12> |

| SENT2 – SENT2 TX/RX                  | 96     | 88          | 0x0000C4          | IFS5<8>                | IEC5<8>  | IPC22<2:0>   |

| SENT2E – SENT2 Error                 | 97     | 89          | 0x0000C6          | IFS5<9>                | IEC5<9>  | IPC22<6:4>   |

| ADC – ADC Global Interrupt           | 98     | 90          | 0x0000C8          | IFS5<10>               | IEC5<10> | IPC22<10:8>  |

| ADCAN0 – ADC AN0 Interrupt           | 99     | 91          | 0x0000CA          | IFS5<11>               | IEC5<11> | IPC22<14:12> |

| ADCAN1 – ADC AN1 Interrupt           | 100    | 92          | 0x0000CC          | IFS5<12>               | IEC5<12> | IPC23<2:0>   |

| ADCAN2 – ADC AN2 Interrupt           | 101    | 93          | 0x0000CE          | IFS5<13>               | IEC5<13> | IPC23<6:4>   |

| ADCAN3 – ADC AN3 Interrupt           | 102    | 94          | 0x0000D0          | IFS5<14>               | IEC5<14> | IPC23<10:8>  |

| ADCAN4 – ADC AN4 Interrupt           | 103    | 95          | 0x0000D2          | IFS5<15>               | IEC5<15> | IPC23<14:12> |

| ADCAN5 – ADC AN5 Interrupt           | 104    | 96          | 0x0000D4          | IFS6<0>                | IEC6<0>  | IPC24<2:0>   |

| ADCAN6 – ADC AN6 Interrupt           | 105    | 97          | 0x0000D6          | IFS6<1>                | IEC6<1>  | IPC24<6:4>   |

| ADCAN7 – ADC AN7 Interrupt           | 106    | 98          | 0x0000D8          | IFS6<2>                | IEC6<2>  | IPC24<10:8>  |

| ADCAN8 – ADC AN8 Interrupt           | 107    | 99          | 0x0000DA          | IFS6<3>                | IEC6<3>  | IPC24<14:12> |

| ADCAN9 – ADC AN9 Interrupt           | 108    | 100         | 0x0000DC          | IFS6<4>                | IEC6<4>  | IPC25<2:0>   |

| ADCAN10 – ADC AN10 Interrupt         | 109    | 101         | 0x0000DE          | IFS6<5>                | IEC6<5>  | IPC25<6:4>   |

| ADCAN11 – ADC AN11 Interrupt         | 110    | 102         | 0x0000E0          | IFS6<6>                | IEC6<6>  | IPC25<10:8>  |

| ADCAN12 – ADC AN12 Interrupt         | 111    | 103         | 0x0000E2          | IFS6<7>                | IEC6<7>  | IPC25<14:12> |

| ADCAN13 – ADC AN13 Interrupt         | 112    | 100         | 0x0000E4          | IFS6<8>                | IEC6<8>  | IPC26<2:0>   |

| ADCAN14 – ADC AN14 Interrupt         | 112    | 104         | 0x0000E6          | IFS6<9>                | IEC6<9>  | IPC26<6:4>   |

| ADCAN15 – ADC AN15 Interrupt         | 110    | 106         | 0x0000E8          | IFS6<10>               | IEC6<10> | IPC26<10:8>  |

## REGISTER 3-18: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 6 | DIV0ERR: Divide-by-Zero Error Status bit               |

|-------|--------------------------------------------------------|

|       | 1 = Math error trap was caused by a divide-by-zero     |

|       | 0 = Math error trap was not caused by a divide-by-zero |

| bit 5 | DMACERR: DMA Controller Trap Status bit                |

|       | 1 = DMAC error trap has occurred                       |

|       | 0 = DMAC error trap has not occurred                   |

| bit 4 | MATHERR: Math Error Status bit                         |

|       | 1 = Math error trap has occurred                       |

|       | 0 = Math error trap has not occurred                   |

| bit 3 | ADDRERR: Address Error Trap Status bit                 |

|       | 1 = Address error trap has occurred                    |

|       | 0 = Address error trap has not occurred                |

| bit 2 | STKERR: Stack Error Trap Status bit                    |

|       | 1 = Stack error trap has occurred                      |

|       | 0 = Stack error trap has not occurred                  |

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit            |

|       | 1 = Oscillator failure trap has occurred               |

|       | 0 = Oscillator failure trap has not occurred           |

| bit 0 | Unimplemented: Read as '0'                             |

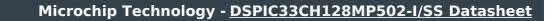

## FIGURE 3-19: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

| U-0          | U-0                 | U-0                                                                                                                 | R-0         | R-0              | R-0              | R-0             | R-0      |  |  |

|--------------|---------------------|---------------------------------------------------------------------------------------------------------------------|-------------|------------------|------------------|-----------------|----------|--|--|

| _            | _                   | —                                                                                                                   |             |                  | FILHIT<4:0>      |                 |          |  |  |

| bit 15       |                     |                                                                                                                     |             |                  |                  |                 | bit 8    |  |  |

|              |                     |                                                                                                                     |             |                  |                  |                 |          |  |  |

| U-0          | R-1                 | R-0                                                                                                                 | R-0         | R-0              | R-0              | R-0             | R-0      |  |  |

|              |                     |                                                                                                                     |             | ICODE<6:0>       |                  |                 |          |  |  |

| bit 7        |                     |                                                                                                                     |             |                  |                  |                 | bit 0    |  |  |

| Legend:      |                     |                                                                                                                     |             |                  |                  |                 |          |  |  |

| R = Readab   | le bit              | W = Writable bit                                                                                                    |             | U = Unimpler     | nented bit, read | d as '0'        |          |  |  |

| -n = Value a | t POR               | '1' = Bit is set                                                                                                    |             | '0' = Bit is cle |                  | x = Bit is unkr | nown     |  |  |

|              |                     |                                                                                                                     |             |                  |                  |                 |          |  |  |

| bit 15-13    | Unimpleme           | nted: Read as '0'                                                                                                   |             |                  |                  |                 |          |  |  |

| bit 12-8     | FILHIT<4:0>         | : Filter Hit Number                                                                                                 | r bits      |                  |                  |                 |          |  |  |

|              | 01111 = Filt        |                                                                                                                     |             |                  |                  |                 |          |  |  |

|              | 01110 <b>= Filt</b> | er 14                                                                                                               |             |                  |                  |                 |          |  |  |

|              | <br>00001 = Filt    | er 1                                                                                                                |             |                  |                  |                 |          |  |  |

|              | 00000 = Filt        | -                                                                                                                   |             |                  |                  |                 |          |  |  |

| bit 7        | Unimpleme           | nted: Read as '0'                                                                                                   |             |                  |                  |                 |          |  |  |

| bit 6-0      | ICODE<6:0>          | Interrupt Flag Co                                                                                                   | de bits     |                  |                  |                 |          |  |  |

|              |                     | 111111 <b>= Reserve</b>                                                                                             |             |                  |                  |                 |          |  |  |

|              |                     | Transmit attempt in                                                                                                 |             |                  |                  |                 |          |  |  |

|              |                     | Transmit event FIF<br>Invalid message of                                                                            | •           |                  | EFSTA IS Set)    |                 |          |  |  |

|              |                     | CAN module mode                                                                                                     |             |                  | -/IE)            |                 |          |  |  |

|              |                     | CAN timer overflow                                                                                                  |             |                  | ,                |                 |          |  |  |

|              |                     | RX/TX MAB overfl                                                                                                    |             |                  |                  |                 |          |  |  |

|              |                     | saved to memory;                                                                                                    |             |                  |                  |                 | nt data) |  |  |

|              |                     | Address error inter                                                                                                 |             |                  |                  |                 |          |  |  |

|              |                     | 1000011 = Receive FIFO overflow interrupt (any bit in C1RXOVIF is set)<br>1000010 = Wake-up interrupt (WAKIF/WAKIE) |             |                  |                  |                 |          |  |  |

|              |                     | Error interrupt (CE                                                                                                 |             | ,                |                  |                 |          |  |  |

|              | 1000000 =           |                                                                                                                     |             |                  |                  |                 |          |  |  |

|              |                     | 111111 = Reserve<br>FIFO 7 interrupt (T                                                                             |             | IE7 is sot)      |                  |                 |          |  |  |

|              | 0000111 =           |                                                                                                                     |             | ir i is selj     |                  |                 |          |  |  |

|              |                     | FIFO 1 interrupt (T                                                                                                 | FIF1 or RF  | IF1 is set)      |                  |                 |          |  |  |

|              | 0000000 =           | FIFO 0 interrupt (T                                                                                                 | FIF0 is set | )                |                  |                 |          |  |  |

|              |                     |                                                                                                                     |             |                  |                  |                 |          |  |  |

## REGISTER 3-115: C1VECL: CAN INTERRUPT CODE REGISTER LOW

| HS/C-0               | HS/C-0               | HS/C-0                                   | HS/C-0                | R-0                  | R-0                  | U-0             | U-0      |

|----------------------|----------------------|------------------------------------------|-----------------------|----------------------|----------------------|-----------------|----------|

| IVMIF <sup>(1)</sup> | WAKIF <sup>(1)</sup> | CERRIF <sup>(1)</sup>                    | SERRIF <sup>(1)</sup> | RXOVIF               | TXATIF               |                 |          |

| bit 15               |                      |                                          |                       |                      |                      |                 | bit 8    |

|                      |                      |                                          |                       |                      |                      |                 |          |

| U-0                  | U-0                  | U-0                                      | R-0                   | HS/C-0               | HS/C-0               | R-0             | R-0      |

| —                    |                      |                                          | TEFIF                 | MODIF <sup>(1)</sup> | TBCIF <sup>(1)</sup> | RXIF            | TXIF     |

| bit 7                |                      |                                          |                       |                      |                      |                 | bit C    |

|                      |                      |                                          |                       |                      |                      |                 |          |

| Legend:              |                      | C = Clearable                            |                       |                      | are Settable bit     |                 |          |

| R = Readable         |                      | W = Writable b                           | it                    |                      | mented bit, read     |                 |          |

| -n = Value at F      | POR                  | '1' = Bit is set                         |                       | '0' = Bit is cle     | ared                 | x = Bit is unkr | nown     |

|                      |                      |                                          |                       |                      |                      |                 |          |

| bit 15               |                      | Message Inter                            |                       |                      |                      |                 |          |

|                      |                      | essage interrupt<br>I message interr     |                       |                      |                      |                 |          |

| bit 14               |                      | Wake-up Activity                         | •                     | a bit <sup>(1)</sup> |                      |                 |          |

|                      |                      | activity interrupt                       | , ,                   |                      |                      |                 |          |

|                      | 0 = No wake-         | up activity interr                       | upt                   |                      |                      |                 |          |

| bit 13               |                      | N Bus Error Inte                         |                       | 1)                   |                      |                 |          |

|                      |                      | error interrupt o                        |                       |                      |                      |                 |          |

| h:: 40               |                      | ous error interru                        |                       |                      |                      |                 |          |

| bit 12               |                      | tem Error Interro<br>rror interrupt occ  |                       |                      |                      |                 |          |

|                      | •                    | n error interrupt                        | Juneu                 |                      |                      |                 |          |

| bit 11               | •                    | eive Buffer Ove                          | rflow Interrupt       | Flag bit             |                      |                 |          |

|                      |                      | ouffer overflow in                       | -                     | -                    |                      |                 |          |

|                      | 0 = No receiv        | e buffer overflow                        | v interrupt           |                      |                      |                 |          |

| bit 10               |                      | smit Attempt Int                         |                       | t                    |                      |                 |          |

|                      |                      | attempt interrup<br>mit Attempt Inte     |                       |                      |                      |                 |          |

| bit 9-5              |                      | ted: Read as '0                          | -                     |                      |                      |                 |          |

| bit 4                | -                    | mit Event FIFO                           |                       | hit                  |                      |                 |          |

|                      |                      | event FIFO inter                         |                       |                      |                      |                 |          |

|                      |                      | nit event FIFO ir                        |                       |                      |                      |                 |          |

| bit 3                | MODIF: CAN           | Mode Change                              | Interrupt Flag        | bit <sup>(1)</sup>   |                      |                 |          |

|                      |                      | ule mode chang                           |                       | )PMOD<2:0>           | have changed t       | o reflect REQC  | )P<2:0>) |

|                      |                      | change occurre                           |                       | (1)                  |                      |                 |          |

| bit 2                | 1 = TBC has          | Timer Overflow                           | Interrupt Flag        | bit                  |                      |                 |          |

|                      |                      | not overflowed                           |                       |                      |                      |                 |          |

| bit 1                |                      | e Object Interru                         | pt Flag bit           |                      |                      |                 |          |

|                      |                      | bject interrupt is                       | -                     |                      |                      |                 |          |

|                      |                      | e object interrup                        | -                     | g                    |                      |                 |          |

| bit 0                |                      | it Object Interru                        | -                     |                      |                      |                 |          |

|                      |                      | object interrupt i<br>nit object interru |                       | ng l                 |                      |                 |          |

|                      | v - i v v u a n S n  |                                          | pis are perioli       | IY                   |                      |                 |          |

#### REGISTER 3-117: C1INTL: CAN INTERRUPT REGISTER LOW

| R/W-0         | R/W-0         | R/W-0            | R/W-0                             | R/W-0            | HSC/R-0                             | R/W-0            | HSC/R-0          |

|---------------|---------------|------------------|-----------------------------------|------------------|-------------------------------------|------------------|------------------|

| REFSEL2       | REFSEL1       | REFSEL0          | SUSPEND                           | SUSPCIE          | SUSPRDY                             | SHRSAMP          | CNVRTCH          |

| bit 15        |               |                  | I                                 | I                |                                     |                  | bit 8            |

|               |               |                  |                                   |                  |                                     |                  |                  |

| R/W-0         | HSC/R-0       | R/W-0            | R/W-0                             | R/W-0            | R/W-0                               | R/W-0            | R/W-0            |

| SWLCTRG       | SWCTRG        | CNVCHSEL5        | CNVCHSEL4                         | CNVCHSEL3        | CNVCHSEL2                           | CNVCHSEL1        | CNVCHSELO        |

| bit 7         |               |                  |                                   |                  |                                     |                  | bit C            |

|               |               |                  |                                   |                  |                                     |                  |                  |

| Legend:       |               | U = Unimplen     | nented bit, read                  | as '0'           |                                     |                  |                  |

| R = Readable  |               | W = Writable     |                                   |                  | vare Settable/C                     |                  |                  |

| -n = Value at | POR           | '1' = Bit is set |                                   | '0' = Bit is cle | ared                                | x = Bit is unkr  | nown             |

| bit 15-13     | REFSEL<2:0    | >: ADC Refere    | nce Voltage Se                    | lection bits     |                                     |                  |                  |

|               | Value         | VREFH            | VREFL                             |                  |                                     |                  |                  |

|               | 000           | AVDD             | AVss                              |                  |                                     |                  |                  |

|               |               |                  |                                   |                  |                                     |                  |                  |

| hit 10        |               | nimplemented     |                                   | hit.             |                                     |                  |                  |

| bit 12        |               |                  | iggers Disable<br>r all ADC cores |                  |                                     |                  |                  |

|               |               | ores can be tri  |                                   |                  |                                     |                  |                  |

| bit 11        | SUSPCIE: Su   | spend All ADC    | Cores Commo                       | on Interrupt En  | able bit                            |                  |                  |

|               | 1 = Common    | interrupt will b | e generated wh                    | en ADC core      | triggers are sus                    | pended (SUSF     | PEND bit = 1)    |

|               |               |                  |                                   | •                | bit becomes se                      | et)              |                  |

| hit 10        |               | -                | t generated for                   | -                | cores event                         |                  |                  |

| bit 10        |               |                  | Suspended Flag                    |                  | no conversions                      | in progress      |                  |

|               |               | •                | is conversions i                  | ,                |                                     | in progress      |                  |

| bit 9         | SHRSAMP: S    | Shared ADC Co    | ore Sampling Di                   | irect Control bi | it                                  |                  |                  |

|               |               |                  |                                   |                  | rsion trigger co                    |                  |                  |

|               |               |                  |                                   |                  | 5:0> bits, to the<br>y hardware and |                  |                  |

|               |               |                  | VRTCH to '1').                    |                  | y naruware and                      | i must be clea   |                  |

|               | 1 = Shared Al | DC core sampl    | es an analog in                   | put specified b  | by the CNVCHS                       | SEL<5:0> bits    |                  |

|               |               |                  | y the shared AD                   |                  |                                     |                  |                  |

| bit 8         |               |                  | lual Channel Co                   |                  |                                     |                  |                  |

|               |               |                  |                                   |                  | ed by the CNVC<br>next instruction  |                  | ts; when the bit |

|               |               | •                | conversion trigg                  |                  |                                     | cycic            |                  |

| bit 7         |               |                  | Sensitive Com                     |                  |                                     |                  |                  |

|               |               |                  |                                   |                  | s with the softv                    | vare; level-sen  | sitive common    |

|               |               |                  |                                   |                  | DTRIGnH regist                      | ers              |                  |

| 1.1.0         |               |                  | itive common tr                   | iggers are gen   | ierated                             |                  |                  |

| bit 6         |               | oftware Commo    |                                   | als with the co  | oftware; commo                      | n trigger coloct | ad as a source   |

|               | in the AD     |                  | ADTRIGnH reg                      |                  | the bit is set, i                   |                  |                  |

|               |               |                  | next software co                  | ommon trigger    |                                     |                  |                  |

| bit 5-0       | -             | -                |                                   |                  | re Individual Ch                    | annel Convers    | ion Trigger bits |

|               | These bits de | fine a channel   | to be converted                   | I when the CN    | VRTCH bit is se                     | et.              |                  |

|               |               |                  |                                   |                  |                                     |                  |                  |

## REGISTER 3-161: ADCON3L: ADC CONTROL REGISTER 3 LOW

#### REGISTER 4-32: CNSTATX: INTERRUPT CHANGE NOTIFICATION STATUS FOR PORTX REGISTER

| R-0    | R-0 | R-0 | R-0   | R-0      | R-0 | R-0 | R-0   |

|--------|-----|-----|-------|----------|-----|-----|-------|

|        |     |     | CNSTA | Гх<15:8> |     |     |       |

| bit 15 |     |     |       |          |     |     | bit 8 |

| R-0    | R-0 | R-0 | R-0   | R-0      | R-0 | R-0 | R-0   |

|        |     |     | CNSTA | Tx<7:0>  |     |     |       |

| bit 7  |     |     |       |          |     |     | bit 0 |

|        |     |     |       |          |     |     |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 **CNSTAT<15:0>:** Interrupt Change Notification Status for PORTx bits When CNSTYLE (CNCONx<11>) = 0:

1 = Change occurred on PORTx[n] since last read of PORTx[n]

0 = Change did not occur on PORTx[n] since last read of PORTx[n]

# REGISTER 4-33: CNEN1x: INTERRUPT CHANGE NOTIFICATION EDGE SELECT FOR PORTX REGISTER

| R/W-0                              | R/W-0 | R/W-0          | R/W-0            | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|------------------------------------|-------|----------------|------------------|--------------|-----------------|-----------|-------|

|                                    |       |                | CNEN             | 1x<15:8>     |                 |           |       |

| bit 15                             |       |                |                  |              |                 |           | bit 8 |

|                                    |       |                |                  |              |                 |           |       |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0            | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|                                    |       |                | CNE              | N1x<7:0>     |                 |           |       |

| bit 7                              |       |                |                  |              |                 |           | bit 0 |

|                                    |       |                |                  |              |                 |           |       |

| Legend:                            |       |                |                  |              |                 |           |       |

| R = Readable                       | bit   | W = Writable b | pit              | U = Unimpler | mented bit, rea | ad as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cle | ared         | x = Bit is unk  | nown      |       |

bit 15-0 **CNEN1x<15:0>:** Interrupt Change Notification Edge Select for PORTx bits

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a Built-In Self-Test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRISx setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRISx settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned.

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Select for PORTx (ANSELx) registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Select for PORTx registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 4.6.7 I/O PORTS RESOURCES

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 4.6.7.1 Key Resources

- "I/O Ports with Edge Detect" (DS70005322) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 4.6.8 PERIPHERAL PIN SELECT REGISTERS

#### REGISTER 4-35: RPCON: PERIPHERAL REMAPPING CONFIGURATION REGISTER

| U-0 | U-0 | U-0 | R/W-0  | U-0          | U-0          | U-0              |

|-----|-----|-----|--------|--------------|--------------|------------------|

| —   |     | —   | IOLOCK | —            | —            | —                |

|     |     |     |        |              |              | bit 8            |

|     |     |     |        |              |              |                  |

| U-0 | U-0 | U-0 | U-0    | U-0          | U-0          | U-0              |

| —   | _   | —   | _      | _            | —            | —                |

|     |     |     |        |              |              | bit 0            |

|     | _   |     |        | — — — IOLOCK | — — IOLOCK — | — — — IOLOCK — — |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-12 | Unimplemented: Read as '0'                                              |

|-----------|-------------------------------------------------------------------------|

| bit 11    | IOLOCK: Peripheral Remapping Register Lock bit                          |

|           | 1 = All Peripheral Remapping registers are locked and cannot be written |

|           | 0 = All Peripheral Remapping registers are unlocked and can be written  |

| bit 10-0  | Unimplemented: Read as '0'                                              |

#### REGISTER 4-36: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| R/W-0                              | R/W-0  | R/W-0        | R/W-0                                  | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

|------------------------------------|--------|--------------|----------------------------------------|--------------|------------------|----------|--------|

| INT1R7                             | INT1R6 | INT1R5       | INT1R4                                 | INT1R3       | INT1R2           | INT1R1   | INT1R0 |

| bit 15                             | ·      |              |                                        |              |                  |          | bit 8  |

|                                    |        |              |                                        |              |                  |          |        |

| U-0                                | U-0    | U-0          | U-0                                    | U-0          | U-0              | U-0      | U-0    |

| —                                  | —      | —            | _                                      | —            | —                | _        | —      |

| bit 7                              |        |              |                                        |              |                  |          | bit 0  |

|                                    |        |              |                                        |              |                  |          |        |

| Legend:                            |        |              |                                        |              |                  |          |        |

| R = Readable                       | bit    | W = Writable | bit                                    | U = Unimpler | nented bit, read | l as '0' |        |

| -n = Value at POR '1' = Bit is set |        |              | '0' = Bit is cleared x = Bit is unknow |              |                  | nown     |        |

|                                    |        |              |                                        |              |                  |          |        |

bit 15-8 **INT1R<7:0>:** Assign External Interrupt 1 (S1INT1) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 Unimplemented: Read as '0'

## 6.5 Slave Special Function Registers

These Special Function Registers provide run-time control and status of the Slave core's oscillator system.

6.5.1 SLAVE OSCILLATOR CONTROL REGISTERS

#### **REGISTER 6-12:** OSCCON: OSCILLATOR CONTROL REGISTER (SLAVE)<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| —      | COSC2 | COSC1 | COSC0 | —   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSC0 <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0   | U-0 | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |

|---------|-----|------|-----|-------------------|-----|-----|-------|

| CLKLOCK | —   | LOCK | —   | CF <sup>(3)</sup> | —   | —   | OSWEN |

| bit 7   |     |      |     |                   |     |     | bit 0 |

| Legend:           | y = Value Set from Configuration bits on POR |                                    |                    |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15        | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12     | COSC<2:0>: Current Oscillator Selection bits (read-only)                                                                                                                                                                                                                                                                                                                                                            |

|               | <ul> <li>111 = Fast RC Oscillator (FRC) with Divide-by-n (FRCDIVN)</li> <li>110 = Backup FRC (BFRC)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Reserved</li> <li>011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> </ul>                                                                                                   |

|               | 001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)                                                                                                                                                                                                                                                                                                                                                                    |

|               | 000 = Fast RC Oscillator (FRC)                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 11        | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 10-8      | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                             |

|               | <ul> <li>111 = Fast RC Oscillator (FRC) with Divide-by-n (FRCDIVN)</li> <li>110 = Backup FRC (BFRC)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Reserved</li> <li>011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)</li> <li>000 = Fast RC Oscillator (FRC)</li> </ul> |

| bit 7         | CLKLOCK: Clock Lock Enable bit                                                                                                                                                                                                                                                                                                                                                                                      |

|               | <ul> <li>1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and PLL configurations may be modified</li> <li>0 = Clock and PLL selections are not locked, configurations may be modified</li> </ul>                                                                                                                                                                      |

| bit 6         | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                          |

| Note 1:<br>2: | Writes to this register require an unlock sequence.<br>Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permit-<br>ted. This applies to clock switches in either direction. In these instances, the application must switch to                                                                                                                                            |

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

#### REGISTER 9-18: PGxyPCIH: PWM GENERATOR xy PCI REGISTER HIGH (x = PWM GENERATOR #; y = F, CL, FF OR S) (CONTINUED)

- bit 3 **TQPS:** Termination Qualifier Polarity Select bit

- 1 = Inverted

- 0 = Not inverted

- bit 2-0 **TQSS<2:0>:** Termination Qualifier Source Selection bits

- 111 = SWPCI control bit only (qualifier forced to '0')

- 110 = Selects PCI Source #9

- 101 = Selects PCI Source #8

- 100 = Selects PCI Source #1 (PWM Generator output selected by the PWMPCI<2:0> bits)

- 011 = PWM Generator is triggered

- 010 = LEB is active

- 001 = Duty cycle is active (base PWM Generator signal)

- 000 = No termination qualifier used (qualifier forced to '1')

- Note 1: Selects '0' if selected PWM Generator is not present.

|               |                                               |                                      |                                         | ·                         | -                                     | R/W-0                   | R/W-0                  |

|---------------|-----------------------------------------------|--------------------------------------|-----------------------------------------|---------------------------|---------------------------------------|-------------------------|------------------------|

| —             | UTXISEL2                                      | UTXISEL1                             | UTXISEL0                                | —                         | URXISEL2 <sup>(1)</sup>               | URXISEL1 <sup>(1)</sup> | URXISEL0 <sup>(1</sup> |

| bit 15        |                                               |                                      |                                         |                           |                                       |                         | bit 8                  |

| HS/R/W-0      | R/W-0                                         | R/S-1                                | R-0                                     | R-1                       | R-1                                   | R/S-1                   | R-0                    |

| TXWRE         | STPMD                                         | UTXBE                                | UTXBF                                   | RIDLE                     | XON                                   | URXBE                   | URXBF                  |

| bit 7         |                                               |                                      |                                         |                           |                                       |                         | bit (                  |

| Legend:       |                                               | HS = Hardwar                         | e Settable bit                          | S = Settable              | bit                                   |                         |                        |

| R = Readable  | e bit                                         | W = Writable                         | bit                                     | U = Unimple               | mented bit, read                      | d as '0'                |                        |

| -n = Value at | POR                                           | '1' = Bit is set                     |                                         | '0' = Bit is cl           |                                       | x = Bit is unkr         | nown                   |

|               |                                               |                                      |                                         |                           |                                       |                         |                        |

| bit 15        | Unimplement                                   | ed: Read as 'o                       | )'                                      |                           |                                       |                         |                        |

| bit 14-12     | UTXISEL<2:0                                   | >: UART Trans                        | smit Interrupt S                        | elect bits                |                                       |                         |                        |

|               | 111 = Sets tra                                | insmit interrupt                     | when there is                           | one empty slo             | ot left in the buffe                  | er                      |                        |

|               | <br>010 - Soto tro                            | nomit intorrunt                      | when there are                          | o iv omntv ol             | ots or more in th                     | o buffor                |                        |

|               |                                               |                                      |                                         |                           | y slots or more ii                    |                         |                        |

|               |                                               |                                      |                                         |                           | slots in the buffe                    |                         | empty                  |

| bit 11        | Unimplement                                   | ed: Read as 'o                       | )'                                      |                           |                                       |                         |                        |

| bit 10-8      | URXISEL<2:0                                   | >: UART Rece                         | eive Interrupt Se                       | elect bits <sup>(1)</sup> |                                       |                         |                        |

|               | 111 = Triggers                                | s receive interr                     | upt when there                          | are eight wo              | ds in the buffer;                     | RX buffer is fu         | II                     |

|               |                                               |                                      |                                         |                           | s or more in the<br>or more in the bu |                         |                        |

| bit 7         |                                               |                                      | Error Status bit                        |                           |                                       |                         |                        |

|               | LIN and Parity                                |                                      |                                         |                           |                                       |                         |                        |

|               |                                               |                                      | /hen the buffer                         | was full or wh            | en P2<8:0> = 0 (                      | must be cleare          | d by software          |

|               | by softwar                                    | te was written w                     | vhen the buffer                         | was full or to            | P1<8:0> when F                        | P1x was full (m         | ust be cleare          |

|               | 0 = No error                                  |                                      |                                         |                           |                                       |                         |                        |

|               | Other Modes:<br>1 = A new byt<br>0 = No error | te was written v                     | when the buffer                         | was full (mu              | st be cleared by                      | software)               |                        |

| bit 6         | STPMD: Stop                                   | Bit Detection N                      | /lode bit                               |                           |                                       |                         |                        |

|               |                                               |                                      | of the last Stop<br>dle of the first (d |                           | pending on the §                      | STSEL<1:0> se           | etting) Stop b         |

| bit 5         | UTXBE: UAR                                    | T TX Buffer Err                      | npty Status bit                         |                           |                                       |                         |                        |

|               |                                               | ouffer is empty;<br>ouffer is not em | -                                       | n UTXEN = 0               | will reset the TX                     | FIFO Pointers           | and counter            |

| bit 4         | UTXBF: UART                                   | T TX Buffer Ful                      | ll Status bit                           |                           |                                       |                         |                        |

|               | 1 = Transmit b<br>0 = Transmit b              |                                      |                                         |                           |                                       |                         |                        |

| bit 3         | RIDLE: Receiv                                 | ve Idle bit                          |                                         |                           |                                       |                         |                        |

|               | 1 = UART RX                                   | line is in the Id                    | le state                                |                           |                                       |                         |                        |

## REGISTER 13-4: UxSTAH: UARTx STATUS REGISTER HIGH

Note 1: The receive watermark interrupt is not set if PERIF or FERIF is set and the corresponding IE bit is set.

#### REGISTER 21-32: DEVREV: DEVICE REVISION REGISTER

| Legend: | R = Read-only bit |   |        | U = Unimpler | nented bit |   |        |

|---------|-------------------|---|--------|--------------|------------|---|--------|

| bit 7   |                   |   |        |              |            |   | bit 0  |

| 1.1.7   |                   |   | DEVRE  | V<7:0>       |            |   | h:: 0  |

| R       | R                 | R | R      | R            | R          | R | R      |

| bit 15  |                   |   |        |              |            |   | bit 8  |

|         |                   |   | DEVRE  | /<15:8>      |            |   |        |

| R       | R                 | R | R      | R            | R          | R | R      |

| bit 23  |                   |   |        |              |            |   | bit 16 |

|         |                   |   | DEVREV | /<23:16>     |            |   |        |

| R       | R                 | R | R      | R            | R          | R | R      |

bit 23-0 **DEVREV<23:0>:** Device Revision bits

#### **REGISTER 21-33: DEVID: DEVICE ID REGISTERS**

| U-1                 |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| —                   | —                   |                     |                     | —                   |                     |                     | —                   |

| bit 23              |                     |                     |                     |                     |                     |                     | bit 16              |

|                     |                     |                     |                     |                     |                     |                     |                     |

| R                   | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

| FAMID7              | FAMID6              | FAMID5              | FAMID4              | FAMID3              | FAMID2              | FAMID1              | FAMID0              |

| bit 15              |                     |                     |                     |                     |                     |                     | bit 8               |

|                     |                     |                     |                     |                     |                     |                     |                     |

| R                   | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

| DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> | DEV2 <sup>(1)</sup> | DEV1 <sup>(1)</sup> | DEV0 <sup>(1)</sup> |

| bit 7               |                     |                     |                     |                     |                     |                     | bit 0               |

|                     |                     |                     |                     |                     |                     |                     |                     |

| Legend: R =         | Read-only bit       |                     |                     | U = Unimpler        | nented bit          |                     |                     |

|                     |                     |                     |                     |                     |                     |                     |                     |

| bit 23-16           | Unimplement         | ted: Read as 'a     | L'                  |                     |                     |                     |                     |

bit 15-8 **FAMID<7:0>:** Device Family Identifier bits 1000 0111 = dsPIC33CH128MP508 family

bit 7-0 DEV<7:0>: Individual Device Identifier bits<sup>(1)</sup>

Note 1: See Table 21-5 for the list of Device Identifier bits.

## **REGISTER 21-37: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = Power-on Reset has occurred

- 0 = Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

| Base<br>Instr<br># | Assembly<br>Mnemonic |         |                   | Description                                         | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|---------|-------------------|-----------------------------------------------------|---------------|-------------------------------|--------------------------|

| 1                  | ADD                  | ADD Acc |                   | Add Accumulators                                    | 1             | 1                             | OA,OB,SA,SB              |

|                    |                      | ADD     | f                 | f = f + WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD     | f,WREG            | WREG = f + WREG                                     | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD     | #lit10,Wn         | Wd = lit10 + Wd                                     | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD     | Wb,Ws,Wd          | Wd = Wb + Ws                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD     | Wb,#lit5,Wd       | Wd = Wb + lit5                                      | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD     | Wso,#Slit4,Acc    | 16-bit Signed Add to Accumulator                    | 1             | 1                             | OA,OB,SA,SB              |