Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit Dual-Core                                                                 |

| Speed                      | 180MHz, 200MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 152KB (152K x 8)                                                                 |

| Program Memory Type        | FLASH, PRAM                                                                      |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 20K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 34x12b; D/A 4x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch128mp506-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33CH128MP508 FAMILY

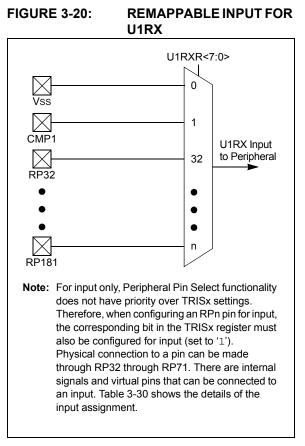

Example 3-2 provides a configuration for bidirectional communication with flow control using UART1. The following input and output functions are used:

- Input Functions: U1RX, U1CTS

- Output Functions: U1TX, U1RTS

## EXAMPLE 3-2: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS

| //                                             |

|------------------------------------------------|

| * * * * * * * * * * * * * * * * * * * *        |

| // Unlock Registers                            |

| //*************************************        |

| <pre>builtin_write_RPCON(0x0000);</pre>        |

| //**************                               |

| // Configure Input Functions (See Table 3-31)  |

| // Assign UlRx To Pin RP35                     |

| / / **************                             |

| _U1RXR = 35;                                   |

| // Assign UlCTS To Pin RP36                    |

| / / ************                               |

| _U1CTSR = 36;                                  |

| //*************************************        |

| // Configure Output Functions (See Table 3-33) |

| / / ***********************************        |

| // Assign UlTx To Pin RP37                     |

| / / *************                              |

| _RP37 = 1;                                     |

| / / ***********                                |

| // Assign UlRTS To Pin RP38                    |

| / / *************                              |

| _RP38 = 2;                                     |

| //*************************************        |

| // Lock Registers                              |

| / / ***********************************        |

| builtin_write_RPCON(0x0800);                   |

|                                                |

## REGISTER 3-135: C1FIFOSTAX: CAN FIFO STATUS REGISTER x (x = 1 TO 7) (CONTINUED)

| bit 2 | <b>TFERFFIF:</b> Transmit/Receive FIFO Empty/Full Interrupt Flag bit<br><u>TXEN = 1 (FIFO configured as a transmit FIFO):</u><br>Transmit FIFO Empty Interrupt Flag<br>1 = FIFO is empty<br>0 = FIFO is not empty, at least one message is queued to be transmitted<br><u>TXEN = 0 (FIFO configured as a receive FIFO):</u><br>Receive FIFO Full Interrupt Flag<br>1 = FIFO is full<br>0 = FIFO is not full                                                                                                       |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>TFHRFHIF:</b> Transmit/Receive FIFO Half Empty/Half Full Interrupt Flag bit $\underline{TXEN = 1}$ (FIFO configured as a transmit FIFO):<br>Transmit FIFO Half Empty Interrupt Flag $1 = FIFO$ is $\leq$ half full $0 = FIFO$ is $>$ half full $\underline{TXEN = 0}$ (FIFO configured as a receive FIFO):<br>Receive FIFO Half Full Interrupt Flag $1 = FIFO$ is $\geq$ half full $0 = FIFO$ is $\geq$ half full $0 = FIFO$ is $\geq$ half full $0 = FIFO$ is $\leq$ half full $0 = FIFO$ is $\leq$ half full |

| bit 0 | <b>TFNRFNIF:</b> Transmit/Receive FIFO Not Full/Not Empty Interrupt Flag bit<br><u>TXEN = 1 (FIFO configured as a transmit FIFO):</u><br>Transmit FIFO Not Full Interrupt Flag<br>1 = FIFO is not full<br>0 = FIFO is full<br><u>TXEN = 0 (FIFO configured as a receive FIFO):</u><br>Receive FIFO Not Empty Interrupt Flag<br>1 = FIFO is not empty, has at least one message<br>0 = FIFO is empty                                                                                                               |

- **Note 1:** FIFOCI<4:0> gives a zero-indexed value to the message in the FIFO. If the FIFO is four messages deep (FSIZE<4:0> = 3), FIFOCIx will take on a value of 0 to 3, depending on the state of the FIFO.

- 2: These bits are updated when a message completes (or aborts) or when the FIFO is reset.

- **3:** This bit is reset on any read of this register or when the TXQ is reset. The bits are cleared when TXREQ is set or using an SPI write.

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | Legend: |     |      |      |      |        |        |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|------|------|--------|--------|-------|

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | bit 7   |     |      |      |      |        |        | bit 0 |

| <br>bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | —   | ТХВО | TXBP | RXBP | TXWARN | RXWARN | EWARN |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0     | U-0 | R-1  | R-0  | R-0  | R-0    | R-0    | R-0   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |     |      |      |      |        |        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15  |     |      |      |      |        |        | bit 8 |

| U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —       | _   | —    | _    | _    | —      | —      | _     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0     | U-0 | U-0  | U-0  | U-0  | U-0    | U-0    | U-0   |

| - <b>J</b>        |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-6 | Unimplemented: Read as '0'                                                   |

|----------|------------------------------------------------------------------------------|

| bit 5    | <b>TXBO:</b> Transmitter in Error State Bus Off bit (TERRCNT<7:0> > 255)     |

|          | In Configuration mode, TXBO is set since the module is not on the bus.       |

| bit 4    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit (TERRCNT<7:0> > 127) |

| bit 3    | <b>RXBP:</b> Receiver in Error State Bus Passive bit (RERRCNT<7:0> > 127)    |

| bit 2    | TXWARN: Transmitter in Error State Warning bit (128 > TERRCNT<7:0> > 95)     |

| bit 1    | <b>RXWARN:</b> Receiver in Error State Warning bit (128 > RERRCNT<7:0> > 95) |

| bit 0    | EWARN: Transmitter or Receiver in Error State Warning bit                    |

## REGISTER 3-146: C1TRECL: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER LOW

| R-0     | R-0 | R-0 | R-0    | R-0     | R-0 | R-0 | R-0   |

|---------|-----|-----|--------|---------|-----|-----|-------|

|         |     |     | TERRCI | NT<7:0> |     |     |       |

| bit 15  |     |     |        |         |     |     | bit 8 |

| <b></b> |     |     |        |         |     |     |       |

| R-0     | R-0 | R-0 | R-0    | R-0     | R-0 | R-0 | R-0   |

|         |     |     | RERRCI | NT<7:0> |     |     |       |

| bit 7   |     |     |        |         |     |     | bit 0 |

|         |     |     |        |         |     |     |       |

| Legend: |     |     |        |         |     |     |       |

| Legenu.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-8 | TERRCNT<7:0>: Transmit Error Counter bits |

|----------|-------------------------------------------|

| bit 7-0  | RERRCNT<7:0>: Receive Error Counter bits  |

## REGISTER 3-158: ADCON1H: ADC CONTROL REGISTER 1 HIGH

| U-0             | U-0                                                                                                  | U-0              | U-0                                               | U-0               | U-0  | U-0             | U-0              |  |

|-----------------|------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|-------------------|------|-----------------|------------------|--|

| —               | —                                                                                                    | —                | —                                                 | —                 | —    | —               | —                |  |

| bit 15          |                                                                                                      |                  |                                                   |                   |      |                 | bit 8            |  |

|                 |                                                                                                      |                  |                                                   |                   |      |                 |                  |  |

| R/W-0           | R/W-1                                                                                                | R/W-1            | U-0                                               | U-0               | U-0  | U-0             | U-0              |  |

| FORM            | SHRRES1                                                                                              | SHRRES0          | _                                                 | —                 |      |                 |                  |  |

| bit 7           |                                                                                                      |                  |                                                   |                   |      |                 | bit 0            |  |

|                 |                                                                                                      |                  |                                                   |                   |      |                 |                  |  |

| Legend:         |                                                                                                      |                  |                                                   |                   |      |                 |                  |  |

| R = Readable    | bit                                                                                                  | W = Writable     | = Writable bit U = Unimplemented bit, read as '0' |                   |      |                 |                  |  |

| -n = Value at F | POR                                                                                                  | '1' = Bit is set |                                                   | '0' = Bit is clea | ared | x = Bit is unkr | = Bit is unknown |  |

|                 |                                                                                                      |                  |                                                   |                   |      |                 |                  |  |

| bit 15-8        | Unimplemen                                                                                           | ted: Read as 'd  | )'                                                |                   |      |                 |                  |  |

| bit 7           | FORM: Fracti                                                                                         | onal Data Outp   | out Format bit                                    |                   |      |                 |                  |  |

|                 | 1 = Fractional<br>0 = Integer                                                                        |                  |                                                   |                   |      |                 |                  |  |

| bit 6-5         | SHRRES<1:0>: Shared ADC Core Resolution Selection bits                                               |                  |                                                   |                   |      |                 |                  |  |

|                 | <pre>11 = 12-bit resolution 10 = 10-bit resolution 01 = 8-bit resolution 00 = 6-bit resolution</pre> |                  |                                                   |                   |      |                 |                  |  |

| bit 4-0         | Unimplemen                                                                                           | ted: Read as 'o  | )'                                                |                   |      |                 |                  |  |

| HSC/R-0         | HSC/R-0                                                                                          | U-0                              | U-0             | U-0               | U-0            | R/W-0           | R/W-0    |

|-----------------|--------------------------------------------------------------------------------------------------|----------------------------------|-----------------|-------------------|----------------|-----------------|----------|

| REFRDY          | REFERR                                                                                           | —                                | —               | —                 | —              | SHRSAMC9        | SHRSAMC8 |

| bit 15          |                                                                                                  | ·                                |                 | ·                 |                | •               | bit 8    |

|                 |                                                                                                  |                                  |                 |                   |                |                 |          |

| R/W-0           | R/W-0                                                                                            | R/W-0                            | R/W-0           | R/W-0             | R/W-0          | R/W-0           | R/W-0    |

| SHRSAMC7        | SHRSAMC6                                                                                         | SHRSAMC5                         | SHRSAMC4        | SHRSAMC3          | SHRSAMC2       | SHRSAMC1        | SHRSAMC0 |

| bit 7           |                                                                                                  |                                  |                 |                   |                |                 | bit 0    |

|                 |                                                                                                  |                                  |                 |                   |                |                 |          |

| Legend:         |                                                                                                  | U = Unimplem                     | ented bit, read | l as '0'          |                |                 |          |

| R = Readable    | bit                                                                                              | W = Writable I                   | oit             | HSC = Hardwa      | are Settable/C | earable bit     |          |

| -n = Value at I | POR                                                                                              | '1' = Bit is set                 |                 | '0' = Bit is clea | ared           | x = Bit is unkn | own      |

|                 |                                                                                                  |                                  |                 |                   |                |                 |          |

| bit 15          |                                                                                                  | nd Gap and Re                    | ference Voltage | e Ready Flag b    | it             |                 |          |

|                 | 1 = Band gap<br>0 = Band gap                                                                     | •                                |                 |                   |                |                 |          |

| bit 14          | •                                                                                                | nd Gap or Refe                   | rence Voltage   | Error Elag bit    |                |                 |          |

|                 |                                                                                                  | was removed a                    | •               | •                 | abled (ADON =  | = 1)            |          |

|                 |                                                                                                  | ap error was d                   |                 |                   |                | _,              |          |

| bit 13-10       | Unimplement                                                                                      | ted: Read as 'd                  | )'              |                   |                |                 |          |

| bit 9-0         | SHRSAMC<9:0>: Shared ADC Core Sample Time Selection bits                                         |                                  |                 |                   |                |                 |          |

|                 | These bits specify the number of shared ADC Core Clock Periods (TADCORE) for the shared ADC core |                                  |                 |                   |                |                 |          |

|                 |                                                                                                  | Sample Time = (<br>= 1025 Tadcor | •               | 0> + 2) * TADCC   | PRE).          |                 |          |

|                 |                                                                                                  | - 1023 TADCON                    | χ <u>ε</u>      |                   |                |                 |          |

|                 | 000000001 = 3 TADCORE                                                                            |                                  |                 |                   |                |                 |          |

|                 | 000000000 = 2 TADCORE                                                                            |                                  |                 |                   |                |                 |          |

|                 |                                                                                                  |                                  |                 |                   |                |                 |          |

## REGISTER 3-160: ADCON2H: ADC CONTROL REGISTER 2 HIGH

## REGISTER 3-185: PTGBTE: PTG BROADCAST TRIGGER ENABLE LOW REGISTER<sup>(1)</sup>

| R/W-0            | R/W-0 | R/W-0                | R/W-0   | R/W-0  | R/W-0          | R/W-0    | R/W-0 |

|------------------|-------|----------------------|---------|--------|----------------|----------|-------|

|                  |       |                      | PTGBTE< | <15:8> |                |          |       |

| bit 15           |       |                      |         |        |                |          | bit 8 |

|                  |       |                      |         |        |                |          |       |

| R/W-0            | R/W-0 | R/W-0                | R/W-0   | R/W-0  | R/W-0          | R/W-0    | R/W-0 |

|                  |       |                      | PTGBTE  | <7:0>  |                |          |       |

| bit 7            |       |                      |         |        |                |          | bit 0 |

|                  |       |                      |         |        |                |          |       |

| Legend:          |       |                      |         |        |                |          |       |

| D - Doodoblo hit |       | \// = \//ritable bit |         |        | ontod hit room | 1 00 '0' |       |

| Eogona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 **PTGBTE<15:0>:** PTG Broadcast Trigger Enable bits

1 = Generates trigger when the broadcast command is executed

0 = Does not generate trigger when the broadcast command is executed

Note 1: These bits are read-only when the module is executing Step commands.

## REGISTER 3-186: PTGBTEH: PTG BROADCAST TRIGGER ENABLE HIGH REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|----------|-------|-------|-------|

|        |       |       | PTGBT | E<31:24> |       |       |       |

| bit 15 |       |       |       |          |       |       | bit 8 |

|        |       |       |       |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

| R/W-U | R/W-U | R/ W-U | R/W-U | R/W-U    | R/W-U | R/W-U | R/ W-U |

|-------|-------|--------|-------|----------|-------|-------|--------|

|       |       |        | PTGBT | E<23:16> |       |       |        |

| bit 7 |       |        |       |          |       |       | bit 0  |

|       |       |        |       |          |       |       |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 PTGBTE<31:16>: PTG Broadcast Trigger Enable bits

1 = Generates trigger when the broadcast command is executed

0 = Does not generate trigger when the broadcast command is executed

Note 1: These bits are read-only when the module is executing Step commands.

## 4.2.2 DATA ADDRESS SPACE (SLAVE)

The dsPIC33CH128MP508S1 family CPU has a separate 16-bit wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory map is shown in Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes or 32K words.

The lower half of the data memory space (i.e., when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV).

The dsPIC33CH128MP508S1 family devices implement up to 4 Kbytes of data memory. If an EA points to a location outside of this area, an all-zero word or byte is returned.

#### 4.2.2.1 Data Space Width

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2.2 Data Memory Organization and Alignment

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33CH128MP508S1 family instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through wordaligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

### 4.2.2.3 SFR Space

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33CH128MP508S1 family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

### 4.2.2.4 Near Data Space

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

| Register  | Address | All Resets                              | Register         | Address | All Resets                              | Register  | Address | All Resets                              |

|-----------|---------|-----------------------------------------|------------------|---------|-----------------------------------------|-----------|---------|-----------------------------------------|

| Register  | Audress | All Resets                              | Register         | Audress | All Resets                              | Register  | Auuress | All Resets                              |

| ССР       |         |                                         | CCP2STATL        | 980     | 000xx0000                               | CCP3RAL   | 9B0     | 000000000000000000000000000000000000000 |

| CCP1CON1L | 950     | 0-00000000000000                        | CCP2STATH        | 982     | 00000                                   | CCP3RBL   | 9B4     | 000000000000000000000000000000000000000 |

| CCP1CON1H | 952     | 00000000000000                          | CCP2TMRL         | 984     | 000000000000000000000000000000000000000 | CCP3BUFL  | 9B8     | 000000000000000000000000000000000000000 |

| CCP1CON2L | 954     | 00-000000000                            | CCP2TMRH         | 986     | 000000000000000000000000000000000000000 | CCP3BUFH  | 9BA     | 000000000000000000000000000000000000000 |

| CCP1CON2H | 956     | 0100-00000                              | CCP2PRL          | 988     | 111111111111111111                      | CCP4CON1L | 9BC     | 0-00000000000000                        |

| CCP1CON3H | 95A     | 00000-00                                | CCP2PRH          | 98A     | 111111111111111111                      | CCP4CON1H | 9BE     | 00000000000000                          |

| CCP1STATL | 95C     | 000xx0000                               | CCP2RAL          | 98C     | 000000000000000000000000000000000000000 | CCP4CON2L | 9C0     | 00-000000000                            |

| CCP1STATH | 95E     | 00000                                   | CCP2RBL          | 990     | 000000000000000000000000000000000000000 | CCP4CON2H | 9C2     | 0100-00000                              |

| CCP1TMRL  | 960     | 000000000000000000000000000000000000000 | CCP2BUFL         | 994     | 000000000000000000000000000000000000000 | CCP4CON3H | 9C6     | 00000-00                                |

| CCP1TMRH  | 962     | 000000000000000000000000000000000000000 | CCP2BUFH         | 996     | 000000000000000000000000000000000000000 | CCP4STATL | 9C8     | 000xx0000                               |

| CCP1PRL   | 964     | 111111111111111111                      | CCP3CON1L        | 998     | 0-00000000000000                        | CCP4STATH | 9CA     | 00000                                   |

| CCP1PRH   | 966     | 111111111111111111                      | CCP3CON1H        | 99A     | 00000000000000                          | CCP4TMRL  | 9CC     | 000000000000000000000000000000000000000 |

| CCP1RAL   | 968     | 000000000000000000000000000000000000000 | CCP3CON2L        | 99C     | 00-000000000                            | CCP4TMRH  | 9CE     | 000000000000000000000000000000000000000 |

| CCP1RBL   | 96C     | 000000000000000000000000000000000000000 | CCP3CON2H        | 99E     | 0100-00000                              | CCP4PRL   | 9D0     | 111111111111111111                      |

| CCP1BUFL  | 970     | 000000000000000000000000000000000000000 | CCP3CON3H        | 9A2     | 00000-00                                | CCP4PRH   | 9D2     | 111111111111111111                      |

| CCP1BUFH  | 972     | 000000000000000000000000000000000000000 | <b>CCP3STATL</b> | 9A4     | 000xx0000                               | CCP4RAL   | 9D4     | 000000000000000000000000000000000000000 |

| CCP2CON1L | 974     | 0-00000000000000                        | CCP3STATH        | 9A6     | 00000                                   | CCP4RBL   | 9D8     | 000000000000000000000000000000000000000 |

| CCP2CON1H | 976     | 00000000000000                          | CCP3TMRL         | 9A8     | 000000000000000000000000000000000000000 | CCP4BUFL  | 9DC     | 000000000000000000000000000000000000000 |

| CCP2CON2L | 978     | 00-000000000                            | CCP3TMRH         | 9AA     | 000000000000000000                      | CCP4BUFH  | 9DE     | 0000000000000000000                     |

| CCP2CON2H | 97A     | 0100-00000                              | CCP3PRL          | 9AC     | 11111111111111111                       |           |         |                                         |

| CCP2CON3H | 97E     | 00000-00                                | CCP3PRH          | 9AE     | 11111111111111111                       |           |         |                                         |

#### TABLE 4-9:SLAVE SFR BLOCK 900h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address and Reset values are in hexadecimal and binary, respectively.

## TABLE 4-10: SLAVE SFR BLOCK A00h

| Register | Address | All Resets                              | Register | Address | All Resets                              | Register | Address | All Resets                              |

|----------|---------|-----------------------------------------|----------|---------|-----------------------------------------|----------|---------|-----------------------------------------|

| DMA      |         |                                         | DMACH0   | AC4     | 0-00000000000                           | DMACH1   | ACE     | 0-00000000000                           |

| DMACON   | ABC     | 0-00                                    | DMAINT0  | AC6     | 0000000000000000                        | DMAINT1  | AD0     | 0000000000000000                        |

| DMABUF   | ABE     | 000000000000000000000000000000000000000 | DMASRC0  | AC8     | 000000000000000000000000000000000000000 | DMASRC1  | AD2     | 000000000000000000000000000000000000000 |

| DMAL     | AC0     | 0001000000000000                        | DMADST0  | ACA     | 000000000000000000000000000000000000000 | DMADST1  | AD4     | 000000000000000000000000000000000000000 |

| DMAH     | AC2     | 0001000000000000                        | DMACNT0  | ACC     | 0000000000000001                        | DMACNT1  | AD6     | 0000000000000001                        |

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address and Reset values are in hexadecimal and binary, respectively.

#### 4.3.8 SLAVE ECC CONTROL/STATUS REGISTERS

### REGISTER 4-9: ECCCONL: ECC FAULT INJECTION CONFIGURATION REGISTER LOW

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0     |

|--------|-----|-----|-----|-----|-----|-----|---------|

| _      | —   | _   | —   | _   | —   | —   | _       |

| bit 15 |     |     |     |     |     | •   | bit 8   |

|        |     |     |     |     |     |     |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

| —      | —   | _   | —   | —   | —   | —   | FLTINMJ |

| bit 7  |     |     |     |     |     | •   | bit 0   |

|        |     |     |     |     |     |     |         |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

FLTINJ: Fault Injection Sequence Enable bit

1 = Enabled

bit 0

0 = Disabled

## REGISTER 4-10: ECCCONH: ECC FAULT INJECTION CONFIGURATION REGISTER HIGH

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|----------|-------|-------|-------|----------|-------|-------|-------|

|          |       |       | FLT2F | PTR<7:0> |       |       |       |

| bit 15   |       |       |       |          |       |       | bit 8 |

| <b>F</b> |       |       |       |          |       |       |       |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|          |       |       | FLT1F | PTR<7:0> |       |       |       |

| bit 7    |       |       |       |          |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-8 | FLT2PTR<7:0>: ECC Fault Injection Bit Pointer 2                              |

|----------|------------------------------------------------------------------------------|

|          | 11111111-00111000 = No Fault injection occurs                                |

|          | 00110111 = Fault injection (bit inversion) occurs on bit 55 of ECC bit order |

|          |                                                                              |

|          | 00000001 = Fault injection (bit inversion) occurs on bit 1 of ECC bit order  |

|          | 0000000 = Fault injection (bit inversion) occurs on bit 0 of ECC bit order   |

| bit 7-0  | FLT1PTR<7:0>: ECC Fault Injection Bit Pointer 1                              |

|          | 1111111-00111000 = No Fault injection occurs                                 |

|          | 00110111 = Fault injection occurs on bit 55 of ECC bit order                 |

|          | •••                                                                          |

|          | 00000001 = Fault injection occurs on bit 1 of ECC bit order                  |

|          | 0000000 = Fault injection occurs on bit 0 of ECC bit order                   |

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —      | —   | RP175R5 <sup>(1)</sup> | RP175R4 <sup>(1)</sup> | RP175R3 <sup>(1)</sup> | RP175R2 <sup>(1)</sup> | RP175R1 <sup>(1)</sup> | RP175R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —     | —   | RP174R5 <sup>(1)</sup> | RP174R4 <sup>(1)</sup> | RP174R3 <sup>(1)</sup> | RP174R2 <sup>(1)</sup> | RP174R1 <sup>(1)</sup> | RP174R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

| bit 13-8 | <b>RP175R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP175 Output Pin bits <sup>(1)</sup> |

|----------|------------------------------------------------------------------------------------------------------------|

|          | (see Table 4-31 for peripheral function numbers)                                                           |

| bit 7-6  | Unimplemented: Read as '0'                                                                                 |

bit 5-0 **RP174R<5:0>:** Peripheral Output Function is Assigned to S1RP174 Output Pin bits<sup>(1)</sup> (see Table 4-31 for peripheral function numbers)

Note 1: These are virtual output ports.

#### EXAMPLE 6-1: CODE EXAMPLE FOR USING MASTER PRIMARY PLL WITH 8 MHz INTERNAL FRC

```

//code example for 50 MIPS system clock using 8MHz FRC

// Select FRC on POR

#pragma config FNOSC = FRC

// Oscillator Source Selection (Internal Fast RC (FRC))

#pragma config IESO = OFF

// Enable Clock Switching

#pragma config FCKSM = CSECMD

int

main()

// Configure PLL prescaler, both PLL postscalers, and PLL feedback divider

CLKDIVbits.PLLPRE = 1;

// N1=1

PLLFBDbits.PLLFBDIV = 125;

// M = 125

PLLDIVbits.POST1DIV = 5;

// N2=5

PLLDIVbits.POST2DIV = 1;

// N3=1

// Initiate Clock Switch to FRC with PLL (NOSC=0b001)

_builtin_write_OSCCONH(0x01);

__builtin_write_OSCCONL(OSCCON | 0x01);

// Wait for Clock switch to occur

while (OSCCONbits.OSWEN!= 0);

}

Note: FPLLO = FPLLI * M/(N1 * N2 * N3); FPLLI = 8; M = 125; N1 = 1; N2 = 5; N3 = 1;

so FPLLO = 8 * 125/(1 * 5 * 1) = 200 MHz or 50 MIPS.

```

#### EXAMPLE 6-2: CODE EXAMPLE FOR USING SLAVE PRIMARY PLL WITH 8 MHz INTERNAL FRC

```

//code example for 60 MIPS system clock using 8MHz FRC

// Select Internal FRC at POR

// Select FRC on POR

// Oscillator Source Selection (Internal Fast RC (FRC))

#pragma config S1FNOSC = FRC

#pragma config SllESO = OFF

// Two-speed Oscillator Start-up Enable bit (Start up with

user-selected oscillator source)

// Enable Clock Switching

#pragma config S1FCKSM = CSECMD

int

main()

// Configure PLL prescaler, both PLL postscalers, and PLL feedback divider

CLKDIVbits.PLLPRE = 1;

// N1=1

PLLFBDbits.PLLFBDIV = 150;

// M = 150

PLLDIVbits.POST1DIV = 5;

// N2=5

PLLDIVbits.POST2DIV = 1;

// N3=1

// Initiate Clock Switch to FRC with PLL (NOSC=0b001)

__builtin_write_OSCCONH(0x01);

builtin write OSCCONL(OSCCON | 0x01);

// Wait for Clock switch to occur

while (OSCCONbits.OSWEN!= 0);

}

Note: FPLLO = FPLLI * M/(N1 * N2 * N3); FPLLI = 8; M = 150; N1 = 1; N2 = 5; N3 = 1;

so FPLLO = 8 * 150/(1 * 5 * 1) = 240 MHz or 60 MIPS.

```

| REGISTE             | ER 6-13: CLKL                                                                                                               |                                                                                                                                                                                 |                                 | GISTER (SLA                          | VE)                    |                        |                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------|------------------------|------------------------|-----------------------|

| R/W-0               |                                                                                                                             | R/W-1                                                                                                                                                                           | R/W-1                           | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                 |

| ROI                 | DOZE2 <sup>(1)</sup>                                                                                                        | DOZE1 <sup>(1)</sup>                                                                                                                                                            | DOZE0 <sup>(1)</sup>            | DOZEN <sup>(2,3)</sup>               | FRCDIV2                | FRCDIV1                | FRCDIV0               |

| bit 15              |                                                                                                                             |                                                                                                                                                                                 |                                 |                                      |                        |                        | bit                   |

| U-0                 | U-0                                                                                                                         | r-0                                                                                                                                                                             | r-0                             | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                 |

| _                   | _                                                                                                                           | _                                                                                                                                                                               | _                               | PLLPRE3 <sup>(4)</sup>               | PLLPRE2 <sup>(4)</sup> | PLLPRE1 <sup>(4)</sup> | PLLPRE0 <sup>(4</sup> |

| bit 7               |                                                                                                                             |                                                                                                                                                                                 |                                 |                                      |                        |                        | bit                   |

| Logondi             |                                                                                                                             | r = Reserved                                                                                                                                                                    | hit                             |                                      |                        |                        |                       |

| Legend:<br>R = Read | abla bit                                                                                                                    | W = Writable                                                                                                                                                                    |                                 |                                      | nented bit, read       | 1 22 (0)               |                       |

| -n = Value          |                                                                                                                             | '1' = Bit is set                                                                                                                                                                | UIL                             | '0' = Bit is clea                    |                        | x = Bit is unkn        |                       |

|                     | alFOR                                                                                                                       |                                                                                                                                                                                 |                                 |                                      | aleu                   |                        | IOWIT                 |

| bit 15<br>bit 14-12 | 1 = Interrupts<br>0 = Interrupts                                                                                            | on Interrupt bi<br>will clear the D<br>have no effect<br>Processor Cloc                                                                                                         | OZEN bit and t<br>t on the DOZE |                                      | ock, and the pe        | ripheral clock ra      | itio is set to 1      |

|                     | 101 = FP divid<br>100 = FP divid<br>011 = FP divid<br>010 = FP divid                                                        | <pre>110 = FP divided by 64<br/>101 = FP divided by 32<br/>100 = FP divided by 16<br/>011 = FP divided by 8 (default)<br/>010 = FP divided by 4<br/>001 = FP divided by 2</pre> |                                 |                                      |                        |                        |                       |

| bit 11              | DOZEN: Doze                                                                                                                 | e Mode Enable                                                                                                                                                                   | bit <sup>(2,3)</sup>            |                                      |                        |                        |                       |

|                     |                                                                                                                             |                                                                                                                                                                                 |                                 | ween the peripl<br>atio is forced to |                        | d the processo         | r clocks              |

| bit 10-8            | FRCDIV<2:0><br>111 = FRC di<br>110 = FRC di<br>101 = FRC di<br>100 = FRC di<br>011 = FRC di<br>010 = FRC di<br>001 = FRC di | Internal Fast<br>vided by 256<br>vided by 64<br>vided by 32<br>vided by 16<br>vided by 8<br>vided by 4                                                                          | RC Oscillator                   | Postscaler bits                      |                        |                        |                       |

| bit 7-6             |                                                                                                                             | ted: Read as '                                                                                                                                                                  | -                               |                                      |                        |                        |                       |

| bit 5-4             | Reserved: Re                                                                                                                |                                                                                                                                                                                 |                                 |                                      |                        |                        |                       |

| Note 1:             | The DOZE<2:0><br>DOZE<2:0> are ig                                                                                           | -                                                                                                                                                                               | e written to wh                 | en the DOZEN                         | bit is clear. If D     | OZEN = 1, any          | writes to             |

| 2:                  | This bit is cleared                                                                                                         | when the ROI                                                                                                                                                                    | bit is set and a                | an interrupt occ                     | urs.                   |                        |                       |

| 3:                  | The DOZEN bit ca<br>set the DOZEN bit                                                                                       |                                                                                                                                                                                 | DOZE<2:0> =                     | 000. If DOZE<2                       | 2:0> = 000, an         | y attempt by us        | er software t         |

|                     |                                                                                                                             |                                                                                                                                                                                 |                                 |                                      |                        |                        |                       |

## REGISTER 6-13: CLKDIV: CLOCK DIVIDER REGISTER (SLAVE)

4: PLLPRE<3:0> may be updated while the PLL is operating, but the VCO may overshoot.

## REGISTER 6-15: PLLDIV: PLL OUTPUT DIVIDER REGISTER (SLAVE)

|              |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |                 |                                         | . ,            |                   |                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------|-----------------------------------------|----------------|-------------------|----------------|

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                           | U-0             | U-0                                     | U-0            | R/W-0             | R/W-0          |

| _            |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |                 |                                         | VCOD           | VCODIV<1:0>       |                |

| bit 15       |                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                             |                 |                                         |                |                   | bit            |

|              |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |                 |                                         |                |                   |                |

| U-0          | R/W-1                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                         | R/W-0           | U-0                                     | R/W-0          | R/W-0             | R/W-1          |

| —            | P                                                                                                                                                                                                                                                                                                                                                                                     | OST1DIV<2:0>(                                                                 | 1,2)            | —                                       | F              | POST2DIV<2:0>     | .(1,2)         |

| bit 7        |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |                 |                                         |                |                   | bit            |

|              |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |                 |                                         |                |                   |                |

| Legend:      |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |                 |                                         |                |                   |                |

| R = Readab   | le bit                                                                                                                                                                                                                                                                                                                                                                                | W = Writable                                                                  | bit             | U = Unimple                             | emented bit, r | ead as '0'        |                |

| -n = Value a | t POR                                                                                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set                                                              |                 | '0' = Bit is cleared x = Bit is unknown |                |                   |                |

|              |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |                 |                                         |                |                   |                |

| bit 15-10    | Unimpleme                                                                                                                                                                                                                                                                                                                                                                             | nted: Read as '                                                               | כ'              |                                         |                |                   |                |

| bit 9-8      | VCODIV<1:0                                                                                                                                                                                                                                                                                                                                                                            | )>: PLL VCO Ou                                                                | utput Divider S | Select bits                             |                |                   |                |

|              | 11 = Fvco                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                 |                                         |                |                   |                |

|              | 10 = Fvco/2<br>01 = Fvco/3                                                                                                                                                                                                                                                                                                                                                            |                                                                               |                 |                                         |                |                   |                |

|              | 01 = FVCO/3<br>00 = FVCO/4                                                                                                                                                                                                                                                                                                                                                            |                                                                               |                 |                                         |                |                   |                |

| bit 7        | Unimpleme                                                                                                                                                                                                                                                                                                                                                                             | nted: Read as '                                                               | )'              |                                         |                |                   |                |

| bit 6-4      | •                                                                                                                                                                                                                                                                                                                                                                                     | <b>POST1DIV&lt;2:0&gt;:</b> PLL Output Divider #1 Ratio bits <sup>(1,2)</sup> |                 |                                         |                |                   |                |

|              |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |                 |                                         | POST1DIVx v    | alue should be    | greater than o |