Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

|                            |                                                                                  |

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit Dual-Core                                                                 |

| Speed                      | 180MHz, 200MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 152KB (152K x 8)                                                                 |

| Program Memory Type        | FLASH, PRAM                                                                      |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 20K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 34x12b; D/A 4x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch128mp506-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(1)</sup>                                         | Pin<br>Type | Buffer<br>Type | PPS | Description                                                       |

|-----------------------------------------------------------------|-------------|----------------|-----|-------------------------------------------------------------------|

| TMS                                                             | - 1         | ST             | No  | JTAG Test mode select pin                                         |

| TCK                                                             | - 1         | ST             | No  | JTAG test clock input pin                                         |

| TDI                                                             | - 1         | ST             | No  | JTAG test data input pin                                          |

| TDO                                                             | 0           | _              | No  | JTAG test data output pin                                         |

| PCI8-PCI18/<br>S1PCI8-S1PCI18                                   | ı           | ST             | Yes | PWM Inputs 8 through 18                                           |

| PWMEA-PWMED/<br>S1PWMEA-S1PWMED                                 | 0           | _              | Yes | PWM Event Outputs A through D                                     |

| PCI19-PCI22/<br>S1PCI19-S1PCI22 <sup>(3)</sup>                  | ı           | ST             | No  | PWM Inputs 19 through 22                                          |

| PWM1L-PWM4L/S1PWM1L/<br>S1PWM8L <sup>(3)</sup>                  | 0           | _              | No  | PWM Low Outputs 1 through 8                                       |

| PWM1H-PWM4H/<br>S1PWM1H-S1PWM8H <sup>(2,3)</sup>                | 0           | _              |     | PWM High Outputs 1 through 8                                      |

| CLCINA-CLCIND/<br>S1CLCINA-S1CLCIND <sup>(3)</sup>              | I           | ST             | Yes | CLC Inputs A through D                                            |

| CLC1OUT-CLC4OUT                                                 | 0           | _              | Yes | CLC Outputs 1 through 4                                           |

| CMP1                                                            | 0           | _              | Yes | Comparator 1 output                                               |

| CMP1A/                                                          | - 1         | Analog         | No  | Comparator Channels 1A through 3A inputs                          |

| S1CMP1A-S1CMP3A <sup>(3)</sup>                                  |             |                |     |                                                                   |

| CMP1B/                                                          | - 1         | Analog         | No  | Comparator Channels 1B through 3B inputs                          |

| S1CMP1B-S1CMP3B <sup>(3)</sup>                                  |             |                |     |                                                                   |

| CMP1D/                                                          | I           | Analog         | No  | Comparator Channels 1D through 3D inputs                          |

| S1CMP1D-S1CMP3D <sup>(3)</sup>                                  | _           |                | NI- | DAG autout valle va                                               |

| DACOUT                                                          | 0           |                |     | DAC output voltage                                                |

| IBIAS3, IBIAS2, IBIAS1,<br>IBIAS0/ISRC3, ISRC2,<br>ISRC1, ISRC0 | 0           | Analog         | No  | Constant-Current Outputs 0 through 3                              |

| S1PGA1P2                                                        | -           | Analog         | No  | PGA1 Positive Input 2                                             |

| S1PGA1N2                                                        | - 1         | Analog         | No  | PGA1 Negative Input 2                                             |

| S1PGA2P2                                                        | I           | Analog         | No  | PGA2 Positive Input 2                                             |

| S1PGA2N2                                                        | I           | Analog         | No  | PGA2 Negative Input 2                                             |

| S1PGA3P1-S1PGA3P2                                               | I           | Analog         | No  | PGA3 Positive Inputs 1 through 2                                  |

| S1PGA3N2                                                        | I           | Analog         | No  | PGA3 Negative Input 2                                             |

| PGD1/S1PGD1 <sup>(3)</sup>                                      | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 1    |

| PGC1/S1PGC1 <sup>(3)</sup>                                      | ı           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 1 |

| PGD2/S1PGD2 <sup>(3)</sup>                                      | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 2    |

| PGC2/S1PGC2 <sup>(3)</sup>                                      | ı           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 2 |

| PGD3/S1PGD3 <sup>(3)</sup>                                      | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 3    |

| PGC3/S1PGC3 <sup>(3)</sup>                                      | ı           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 3 |

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levels<br/>PPS = Peripheral Pin SelectAnalog = Analog input<br/>O = Output<br/>TTL = TTL input bufferP = Power<br/>I = Input

- Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

- 2: These pins are remappable as well as dedicated. Some of the pins are associated with the Slave function and have S1 attached to the beginning of the name. For example, AN0 for the Slave is S1AN0.

- **3:** S1 attached to the beginning of the name indicates the Slave feature for that function. For example, AN0 for the Slave is S1AN0.

TABLE 3-27: PIN AND ANSELX AVAILABILITY

| Device              | Rx15 | Rx14 | Rx13 | Rx12 | Rx11 | Rx10 | Rx9 | Rx8 | Rx7 | Rx6 | Rx5 | Rx4 | Rx3 | Rx2 | Rx1 | Rx0 |

|---------------------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                     | •    | •    |      |      |      | POR  | ГА  |     |     |     |     | •   | •   |     |     |     |

| dsPIC33XXXMP508/208 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP505/205 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   |     | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP503/203 | _    | _    | _    | _    |      | _    | _   | _   | _   | _   | 1   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP502/202 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | 1   | Х   | Х   | Х   | Х   | Х   |

| ANSELA              | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | _   | Х   | Х   | Х   | Х   | Х   |

|                     |      |      |      |      |      | POR  | ГВ  |     |     |     |     |     |     |     |     |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Χ   | Х   | Χ   | Χ   | Х   | Χ   | Χ   | Χ   | Х   |

| dsPIC33XXXMP506/206 | Х    | Х    | Χ    | Χ    | Χ    | Х    | Χ   | Χ   | Χ   | Χ   | Χ   | Х   | Х   | Χ   | Χ   | Х   |

| dsPIC33XXXMP505/205 | Х    | Х    | Х    | Χ    | Χ    | Х    | Х   | Χ   | Х   | Χ   | Χ   | Х   | Х   | Χ   | Х   | Х   |

| dsPIC33XXXMP503/203 | Х    | Х    | Х    | Χ    | Χ    | Х    | Χ   | Χ   | Χ   | Χ   | Χ   | Х   | Х   | Χ   | Х   | Х   |

| dsPIC33XXXMP502/202 | Х    | Х    | Х    | Χ    | Χ    | Х    | Х   | Χ   | Х   | Χ   | Χ   | Х   | Х   | Χ   | Х   | Х   |

| ANSELB              | _    | _    |      | _    | 1    | Х    | Х   | Χ   | -   |     | l   | Х   | Х   | Χ   | Х   | Х   |

|                     |      |      |      |      |      | POR  | ГС  |     |     |     |     |     |     |     |     |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Χ    | Χ    | Χ    | Χ    | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Х   |

| dsPIC33XXXMP506/206 | Х    | Х    | Χ    | Χ    | Χ    | Х    | Χ   | Χ   | Χ   | Х   | Χ   | Х   | Х   | Χ   | Χ   | Х   |

| dsPIC33XXXMP505/205 | _    | _    | Χ    | Χ    | Χ    | Χ    | Χ   | Χ   | Χ   | Χ   | Χ   | Х   | Χ   | Χ   | Χ   | Х   |

| dsPIC33XXXMP503/203 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | Χ   | Χ   | Χ   | Χ   | Χ   | Х   |

| dsPIC33XXXMP502/202 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | -   | _   | _   | _   | _   | —   |

| ANSELC              | _    | _    | _    | _    | _    | _    | _   | _   | Χ   | _   | _   | _   | Χ   | Χ   | Χ   | Х   |

|                     |      |      |      |      |      | POR  | ΓD  |     |     |     |     |     |     |     |     |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Χ    | Χ    | Χ    | Χ    | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Х   |

| dsPIC33XXXMP506/206 | Х    | Х    | Χ    | Χ    | Χ    | Χ    | Χ   | Х   | Χ   | Χ   | Χ   | Х   | Χ   | Χ   | Х   | Х   |

| dsPIC33XXXMP505/205 | _    | _    | Х    | _    | _    | Х    | _   | Χ   | _   | _   | -   | _   | _   | _   | Χ   | —   |

| dsPIC33XXXMP503/203 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | -   | _   | _   | _   | _   | —   |

| dsPIC33XXXMP502/202 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   |

| ANSELD              | _    | _    | _    | _    | _    | Χ    | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   |

|                     |      |      |      |      |      | POR  | ΓΕ  |     |     |     |     |     | _   |     |     |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Χ    | Х    | Χ    | Χ    | Χ   | Χ   | Χ   | Х   | Χ   | Х   | Χ   | Χ   | Χ   | Х   |

| dsPIC33XXXMP506/206 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   |

| dsPIC33XXXMP505/205 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   |

| dsPIC33XXXMP503/203 | _    | _    | _    | _    | -    | _    | _   | _   | _   | _   | -   | _   | _   | _   | _   | _   |

| dsPIC33XXXMP502/202 | _    | _    | _    | _    |      | _    | _   | _   | _   | _   |     | _   | _   | _   | _   | _   |

**TABLE 3-28: 5V INPUT TOLERANT PORTS**

| PORTA | _    | _    | _    | _    | _    | _    |     | _   | _   | _   |     | RA4 | RA3 | RA2 | RA1 | RA0 |

|-------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| PORTB | RB15 | RB14 | RB13 | RB12 | RB11 | RB10 | RB9 | RB8 | RB7 | RB6 | RB5 | RB4 | RB3 | RB2 | RB1 | RB0 |

| PORTC | RC15 | RC14 | RC13 | RC12 | RC11 | RC10 | RC9 | RC8 | RC7 | RC6 | RC5 | RC4 | RC3 | RC2 | RC1 | RC0 |

| PORTD | RD15 | RD14 | RD13 | RD12 | RD11 | RD10 | RD9 | RD8 | RD7 | RD6 | RD5 | RD4 | RD3 | RD2 | RD1 | RD0 |

| PORTE | RE15 | RE14 | RE13 | RE12 | RE11 | RE10 | RE9 | RE8 | RE7 | RE6 | RE5 | RE4 | RE3 | RE2 | RE1 | RE0 |

**Legend:** Shaded pins are up to 5.5 VDC input tolerant.

### 3.6.11 VIRTUAL CONNECTIONS

The dsPIC33CH128MP508 devices support six Master virtual RPn pins (RP176-RP181), which are identical in functionality to all other RPn pins, with the exception of pinouts. These six pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP176 and the PWM Fault input can be configured for RP176 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

# 3.6.12 SLAVE PPS INPUTS TO MASTER CORE PPS

The dsPIC33CH128MP508 Slave core subsystem PPS has connections to the Master core subsystem virtual PPS (RPV5-RPV0) output blocks. These inputs are mapped as S1RP175, S1RP174, S1RP173, S1RP172, S1RP171 and S1RP170.

The RPn inputs, RP1-RP13, are connected to internal signals from both the Master and Slave core subsystems. Additionally, the Master core virtual output PPS blocks (RPV5-RPV0) are connected to the Slave core PPS circuitry.

There are virtual pins in PPS to share between Master and Slave:

- RP181 is for Master input (RPV5)

- · RP180 is for Master input (RPV4)

- RP179 is for Master input (RPV3)

- RP178 is for Master input (RPV2)

- RP177 is for Master input (RPV1)

- RP176 is for Master input (RPV0)

- RP175 is for Slave input (S1RPV5)

- · RP174 is for Slave input (S1RPV4)

- RP173 is for Slave input (S1RPV3)

- RP172 is for Slave input (S1RPV2)

- · RP171 is for Slave input (S1RPV1)

- RP170 is for Slave input (S1RPV0)

The idea of the RPVn (Remappable Pin Virtual) is to interconnect between the Master and Slave without an I/O pin. For example, the Master UART receiver can be connected to the Slave UART transmit using RPVn and data communication can happen from Slave to Master without using any physical pin.

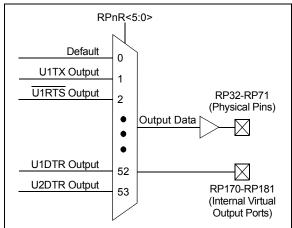

### 3.6.13 OUTPUT MAPPING

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 3-68 through Register 3-90). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 3-33 and Figure 3-21).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

FIGURE 3-21: MULTIPLEXING REMAPPABLE OUTPUTS FOR RPn

Note 1: There are six virtual output ports which are not connected to any I/O ports (RP176-RP181). These virtual ports can be accessed by RPOR20, RPOR21 and RPOR22.

### 3.6.14 MAPPING LIMITATIONS

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally, any combination of peripheral mappings, across any or all of the RPn pins, is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs, and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view (see Table 3-32).

TABLE 3-32: MASTER REMAPPABLE OUTPUT PIN REGISTERS

| RPOR0<5:0> RPOR0<13:8> RPOR1<5:0> RPOR1<13:8> RPOR2<5:0> RPOR2<13:8> RPOR2<13:8> RPOR3<5:0> RPOR3<5:0> RPOR3<13:8> RPOR3<13:8> | RP32<br>RP33<br>RP34<br>RP35<br>RP36<br>RP37<br>RP38<br>RP38<br>RP39 | Port Pin RB0 Port Pin RB1 Port Pin RB2 Port Pin RB3 Port Pin RB4 Port Pin RB5 Port Pin RB6 |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| RPOR0<13:8> RPOR1<5:0> RPOR1<13:8> RPOR2<5:0> RPOR2<13:8> RPOR3<5:0> RPOR3<5:0>                                                | RP33<br>RP34<br>RP35<br>RP36<br>RP37<br>RP38<br>RP39                 | Port Pin RB1 Port Pin RB2 Port Pin RB3 Port Pin RB4 Port Pin RB5                           |

| RPOR1<5:0> RPOR1<13:8> RPOR2<5:0> RPOR2<13:8> RPOR3<5:0> RPOR3<5:0>                                                            | RP34<br>RP35<br>RP36<br>RP37<br>RP38<br>RP39                         | Port Pin RB2 Port Pin RB3 Port Pin RB4 Port Pin RB5                                        |

| RPOR1<13:8> RPOR2<5:0> RPOR2<13:8> RPOR3<5:0> RPOR3<5:0>                                                                       | RP35<br>RP36<br>RP37<br>RP38<br>RP39                                 | Port Pin RB3 Port Pin RB4 Port Pin RB5                                                     |

| RPOR2<5:0> RPOR2<13:8> RPOR3<5:0> RPOR3<13:8>                                                                                  | RP36<br>RP37<br>RP38<br>RP39                                         | Port Pin RB4<br>Port Pin RB5                                                               |

| RPOR2<13:8><br>RPOR3<5:0><br>RPOR3<13:8>                                                                                       | RP37<br>RP38<br>RP39                                                 | Port Pin RB5                                                                               |

| RPOR3<5:0><br>RPOR3<13:8>                                                                                                      | RP38<br>RP39                                                         |                                                                                            |

| RPOR3<13:8>                                                                                                                    | RP39                                                                 | 1 OIL I III NEO                                                                            |

|                                                                                                                                |                                                                      | Port Pin RB7                                                                               |

| DEUR450 UZ                                                                                                                     | 111 10                                                               | Port Pin RB8                                                                               |

| RPOR4<13:8>                                                                                                                    | RP41                                                                 | Port Pin RB9                                                                               |

| RPOR5<5:0>                                                                                                                     | RP42                                                                 | Port Pin RB10                                                                              |

| RPOR5<13:8>                                                                                                                    | RP43                                                                 | Port Pin RB11                                                                              |

| RPOR6<5:0>                                                                                                                     | RP44                                                                 | Port Pin RB12                                                                              |

| RPOR6<13:8>                                                                                                                    | RP45                                                                 | Port Pin RB13                                                                              |

| RPOR7<5:0>                                                                                                                     | RP46                                                                 | Port Pin RB14                                                                              |

| RPOR7<13:8>                                                                                                                    | RP47                                                                 | Port Pin RB15                                                                              |

| RPOR8<5:0>                                                                                                                     | RP48                                                                 | Port Pin RC0                                                                               |

| RPOR8<13:8>                                                                                                                    | RP49                                                                 | Port Pin RC1                                                                               |

| RPOR9<5:0>                                                                                                                     | RP50                                                                 | Port Pin RC2                                                                               |

| RPOR9<13:8>                                                                                                                    | RP51                                                                 | Port Pin RC3                                                                               |

| RPOR10<5:0>                                                                                                                    | RP52                                                                 | Port Pin RC4                                                                               |

| RPOR10<13:8>                                                                                                                   | RP53                                                                 | Port Pin RC5                                                                               |

| RPOR11<5:0>                                                                                                                    | RP54                                                                 | Port Pin RC6                                                                               |

| RPOR11<13:8>                                                                                                                   | RP55                                                                 | Port Pin RC7                                                                               |

| RPOR12<5:0>                                                                                                                    | RP56                                                                 | Port Pin RC8                                                                               |

| RPOR12<13:8>                                                                                                                   | RP57                                                                 | Port Pin RC9                                                                               |

| RPOR13<5:0>                                                                                                                    | RP58                                                                 | Port Pin RC10                                                                              |

| RPOR13<13:8>                                                                                                                   | RP59                                                                 | Port Pin RC11                                                                              |

| RPOR14<5:0>                                                                                                                    | RP60                                                                 | Port Pin RC12                                                                              |

| RPOR14<13:8>                                                                                                                   | RP61                                                                 | Port Pin RC13                                                                              |

| RPOR15<5:0>                                                                                                                    | RP62                                                                 | Port Pin RC14                                                                              |

| RPOR15<13:8>                                                                                                                   | RP63                                                                 | Port Pin RC15                                                                              |

| RPOR16<5:0>                                                                                                                    | RP64                                                                 | Port Pin RD0                                                                               |

| RPOR16<13:8>                                                                                                                   | RP65                                                                 | Port Pin RD1                                                                               |

| RPOR17<5:0>                                                                                                                    | RP66                                                                 | Port Pin RD2                                                                               |

| RPOR17<13:8>                                                                                                                   | RP67                                                                 | Port Pin RD3                                                                               |

| RPOR18<5:0>                                                                                                                    | RP68                                                                 | Port Pin RD4                                                                               |

| RPOR18<13:8>                                                                                                                   | RP69                                                                 | Port Pin RD5                                                                               |

| RPOR19<5:0>                                                                                                                    | RP70                                                                 | Port Pin RD6                                                                               |

| RPOR19<13:8>                                                                                                                   | RP71                                                                 | Port Pin RD7                                                                               |

| 14 51(10 - 10.0*                                                                                                               | RP175-RP169                                                          | Reserved                                                                                   |

| RPOR20<5:0>                                                                                                                    | RP176                                                                | Virtual Pin RPV0                                                                           |

| RPOR20<13:8>                                                                                                                   | RP177                                                                | Virtual Pin RPV1                                                                           |

| RPOR21<5:0>                                                                                                                    | RP178                                                                | Virtual Pin RPV2                                                                           |

| RPOR21<13:8>                                                                                                                   | RP179                                                                | Virtual Pin RPV3                                                                           |

| RPOR22<5:0>                                                                                                                    | RP180                                                                | Virtual Pin RPV4                                                                           |

| RPOR22<13:8>                                                                                                                   | RP181                                                                | Virtual Pin RPV5                                                                           |

## 3.6.15 I/O HELPFUL TIPS

- 1. In some cases, certain pins, as defined in Table 24-18 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or lesser than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low-side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins, by default, after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Select for PORTx registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

Note: Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN14/ISRC1/RP50/RC2; this indicates that AN14 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in Section 24.0 "Electrical Characteristics" of this data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 25.0 "DC and AC Device Characteristics Graphs" for additional information.

TABLE 3-39: MASTER PPS INPUT CONTROL REGISTERS

| Register | Bit 15    | Bit 14    | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     |

|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| RPCON    | _         | _         | -         | -         | IOLOCK    | -         | -         | _         | _         | _         | _         | 1         | _         | _         | _         | _         |

| RPINR0   | INT1R7    | INT1R6    | INT1R5    | INT1R4    | INT1R3    | INT1R2    | INT1R1    | INT1R0    | _         | _         | _         | _         | _         | _         | _         | _         |

| RPINR1   | INT3R7    | INT3R6    | INT3R5    | INT3R4    | INT3R3    | INT3R2    | INT3R1    | INT3R0    | INT2R7    | INT2R6    | INT2R5    | INT2R4    | INT2R3    | INT2R2    | INT2R1    | INT2R0    |

| RPINR2   | T1CKR7    | T1CKR6    | T1CKR5    | T1CKR4    | T1CKR3    | T1CKR2    | T1CKR1    | T1CKR0    | 1         | _         | _         | 1         | _         | _         | _         | _         |

| RPINR3   | ICM1R7    | ICM1R6    | ICM1R5    | ICM1R4    | ICM1R3    | ICM1R2    | ICM1R1    | ICM1R0    | TCKI1R7   | TCKI1R6   | TCKI1R5   | TCKI1R4   | TCKI1R3   | TCKI1R2   | TCKI1R1   | TCKI1R0   |

| RPINR4   | ICM2R7    | ICM2R6    | ICM2R5    | ICM2R4    | ICM2R3    | ICM2R2    | ICM2R1    | ICM2R0    | TCKI2R7   | TCKI2R6   | TCKI2R5   | TCKI2R4   | TCKI2R3   | TCKI2R2   | TCKI2R1   | TCKI2R0   |

| RPINR5   | ICM3R7    | ICM3R6    | ICM3R5    | ICM3R4    | ICM3R3    | ICM3R2    | ICM3R1    | ICM3R0    | TCKI3R7   | TCKI3R6   | TCKI3R5   | TCKI3R4   | TCKI3R3   | TCKI3R2   | TCKI3R1   | TCKI3R0   |

| RPINR6   | ICM4R7    | ICM4R6    | ICM4R5    | ICM4R4    | ICM4R3    | ICM4R2    | ICM4R1    | ICM4R0    | TCKI4R7   | TCKI4R    | TCKI4R5   | TCKI4R4   | TCKI4R3   | TCKI4R2   | TCKI4R1   | TCKI4R0   |

| RPINR7   | ICM5R7    | ICM5R6    | ICM5R5    | ICM5R4    | ICM5R3    | ICM5R2    | ICM5R1    | ICM5R0    | TCKI5R7   | TCKI5R6   | TCKI5R5   | TCKI5R4   | TCKI5R3   | TCKI5R2   | TCKI5R1   | TCKI5R0   |

| RPINR8   | ICM6R7    | ICM6R6    | ICM6R5    | ICM6R4    | ICM6R3    | ICM6R2    | ICM6R1    | ICM6R0    | TCKI6R7   | TCKI6R6   | TCKI6R5   | TCKI6R4   | TCKI6R3   | TCKI6R2   | TCKI6R1   | TCKI6R0   |

| RPINR9   | ICM7R7    | ICM7R6    | ICM7R5    | ICM7R4    | ICM7R3    | ICM7R2    | ICM7R1    | ICM7R0    | TCKI7R7   | TCKI7R6   | TCKI7R5   | TCKI7R4   | TCKI7R3   | TCKI7R2   | TCKI7R1   | TCKI7R0   |

| RPINR10  | ICM8R7    | ICM8R6    | ICM8R5    | ICM8R4    | ICM8R3    | ICM8R2    | ICM8R1    | ICM8R0    | TCKI8R7   | TCKI8R6   | TCKI8R5   | TCKI8R4   | TCKI8R3   | TCKI8R2   | TCKI8R1   | TCKI8R0   |

| RPINR11  | OCFBR7    | OCFBR6    | OCFBR5    | OCFBR4    | OCFBR3    | OCFBR2    | OCFBR1    | OCFBR0    | OCFAR7    | OCFAR6    | OCFAR5    | OCFAR4    | OCFAR3    | OCFAR2    | OCFAR1    | OCFAR0    |

| RPINR12  | PCI9R7    | PCI9R6    | PCI9R5    | PCI9R4    | PCI9R3    | PCI9R2    | PCI9R1    | PCI9R0    | PCI8R7    | PCI8R6    | PCI8R5    | PCI8R4    | PCI8R3    | PCI8R2    | PCI8R1    | PCI8R0    |

| RPINR13  | PCI11R7   | PCI11R6   | PCI11R5   | PCI11R4   | PCI11R3   | PCI11R2   | PCI11R1   | PCI11R0   | PCI10R7   | PCI10R6   | PCI10R5   | PCI10R4   | PCI10R3   | PCI10R2   | PCI10R1   | PCI10R0   |

| RPINR14  | QEIB1R7   | QEIB1R6   | QEIB1R5   | QEIB1R4   | QEIB1R3   | QEIB1R2   | QEIB1R1   | QEIB1R0   | QEIA1R7   | QEIA1R6   | QEIA1R5   | QEIA1R4   | QEIA1R3   | QEIA1R2   | QEIA1R1   | QEIA1R0   |

| RPINR15  | QEIHOM1R7 | QEIHOM1R6 | QEIHOM1R5 | QEIHOM1R4 | QEIHOM1R3 | QEIHOM1R2 | QEIHOM1R1 | QEIHOM1R0 | QEINDX1R7 | QEINDX1R6 | QEINDX1R5 | QEINDX1R4 | QEINDX1R3 | QEINDX1R2 | QEINDX1R1 | QEINDX1R0 |

| RPINR18  | U1DSRR7   | U1DSRR6   | U1DSRR5   | U1DSRR4   | U1DSRR3   | U1DSRR2   | U1DSRR1   | U1DSRR0   | U1RXR7    | U1RXR6    | U1RXR5    | U1RXR4    | U1RXR3    | U1RXR2    | U1RXR1    | U1RXR0    |

| RPINR19  | U2DSRR7   | U2DSRR6   | U2DSRR5   | U2DSRR4   | U2DSRR3   | U2DSRR2   | U2DSRR1   | U2DSRR0   | U2RXR7    | U2RXR6    | U2RXR5    | U2RXR4    | U2RXR3    | U2RXR2    | U2RXR1    | U2RXR0    |

| RPINR20  | SCK1R7    | SCK1R6    | SCK1R5    | SCK1R4    | SCK1R3    | SCK1R2    | SCK1R1    | SCK1R0    | SDI1R7    | SDI1R6    | SDI1R5    | SDI1R4    | SDI1R3    | SDI1R2    | SDI1R1    | SDI1R0    |

| RPINR21  | REFOIR7   | REFOIR6   | REFOIR5   | REFOIR4   | REFOIR3   | REFOIR2   | REFOIR1   | REFOIR0   | SS1R7     | SS1R6     | SS1R5     | SS1R4     | SS1R3     | SS1R2     | SS1R1     | SS1R0     |

| RPINR22  | SCK2R7    | SCK2R6    | SCK2R5    | SCK2R4    | SCK2R3    | SCK2R2    | SCK2R1    | SCK2R0    | SDI2R7    | SDI2R6    | SDI2R5    | SDI2R4    | SDI2R3    | SDI2R2    | SDI2R1    | SDI2R0    |

| RPINR23  | U1CTSR7   | U1CTSR6   | U1CTSR5   | U1CTSR4   | U1CTSR3   | U1CTSR2   | U1CTSR1   | U1CTSR0   | SS2R7     | SS2R6     | SS2R5     | SS2R4     | SS2R3     | SS2R2     | SS2R1     | SS2R0     |

| RPINR26  | _         | _         | _         | _         | -         | -         | _         | _         | CAN1RXR7  | CAN1RXR6  | CAN1RXR5  | CAN1RXR4  | CAN1RXR3  | CAN1RXR2  | CAN1RXR1  | CAN1RXR0  |

| RPINR30  | U2CTSR7   | U2CTSR6   | U2CTSR5   | U2CTSR4   | U2CTSR3   | U2CTSR2   | U2CTSR1   | U2CTSR0   | _         | _         | _         | -         | _         | _         | _         | _         |

| RPINR37  | PCI17R7   | PCI17R6   | PCI17R5   | PCI17R4   | PCI17R3   | PCI17R2   | PCI17R1   | PCI17R0   | _         | _         | _         | -         | _         | _         | _         | _         |

| RPINR38  | _         | _         | _         | _         | -         | -         | _         | _         | PCI18R7   | PCI18R6   | PCI18R5   | PCI18R4   | PCI18R3   | PCI18R2   | PCI18R1   | PCI18R0   |

| RPINR42  | PCI13R7   | PCI13R6   | PCI13R5   | PCI13R4   | PCI13R3   | PCI13R2   | PCI13R1   | PCI13R0   | PCI12R7   | PCI12R6   | PCI12R5   | PCI12R4   | PCI12R3   | PCI12R2   | PCI12R1   | PCI12R0   |

| RPINR43  | PCI15R7   | PCI15R6   | PCI15R5   | PCI15R4   | PCI15R3   | PCI15R2   | PCI15R1   | PCI15R0   | PCI14R7   | PCI14R6   | PCI14R5   | PCI14R4   | PCI14R3   | PCI14R2   | PCI14R1   | PCI14R0   |

| RPINR44  | SENT1R7   | SENT1R6   | SENT1R5   | SENT1R4   | SENT1R3   | SENT1R2   | SENT1R1   | SENT1R0   | PCI16R7   | PCI16R6   | PCI16R5   | PCI16R4   | PCI16R3   | PCI16R2   | PCI16R1   | PCI16R0   |

| RPINR45  | CLCINAR7  | CLCINAR6  | CLCINAR5  | CLCINAR4  | CLCINAR3  | CLCINAR2  | CLCINAR1  | CLCINAR0  | SENT2R7   | SENT2R6   | SENT2R5   | SENT2R4   | SENT2R3   | SENT2R2   | SENT2R1   | SENT2R0   |

| RPINR46  | CLCINCR7  | CLCINCR6  | CLCINCR5  | CLCINCR4  | CLCINCR3  | CLCINCR2  | CLCINCR1  | CLCINCR0  | CLCINBR7  | CLCINBR6  | CLCINBR5  | CLCINBR4  | CLCINBR3  | CLCINBR2  | CLCINBR1  | CLCINBR0  |

| RPINR47  | ADCTRGR7  | ADCTRGR6  | ADCTRGR5  | ADCTRGR4  | ADCTRGR3  | ADCTRGR2  | ADCTRGR1  | ADCTRGR0  | CLCINDR7  | CLCINDR6  | CLCINDR5  | CLCINDR4  | CLCINDR3  | CLCINDR2  | CLCINDR1  | CLCINDR0  |

### REGISTER 3-97: DMTPSCNTL: DMT POST-CONFIGURE COUNT STATUS REGISTER LOW

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| PSCNT<15:8> |       |       |       |       |       |       |       |  |  |  |  |

| bit 15      |       |       |       |       |       |       |       |  |  |  |  |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PSCNT<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7      |       | bit 0 |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **PSCNT<15:0>:** Lower DMT Instruction Count Value Configuration Status bits

This is always the value of the FDMTCNTL Configuration register.

### REGISTER 3-98: DMTPSCNTH: DMT POST-CONFIGURE COUNT STATUS REGISTER HIGH

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| PSCNT<31:24> |       |       |       |       |       |       |       |  |  |  |  |

| bit 15       |       |       |       |       |       |       |       |  |  |  |  |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| PSCNT<23:16> |       |       |       |       |       |       |       |  |  |  |

| bit 7        |       |       |       |       |       |       |       |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **PSCNT<31:16>:** Higher DMT Instruction Count Value Configuration Status bits

This is always the value of the FDMTCNTH Configuration register.

#### REGISTER 3-112: C1TSCONH: CAN TIMESTAMP CONTROL REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | _   | _   | _   | _   | TSRES | TSEOF | TBCEN |

| bit 7 |     |     |     |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 Unimplemented: Read as '0'

bit 2 TSRES: Timestamp Reset bit (CAN FD frames only)

1 = At sample point of the bit following the FDF bit

0 = At sample point of Start-of-Frame (SOF)

bit 1 TSEOF: Timestamp End-of-Frame (EOF) bit

1 = Timestamp when frame is taken valid (11898-1 10.7):

- RX no error until last, but one bit of EOF

- TX no error until the end of EOF

0 = Timestamp at "beginning" of frame:

- Classical Frame: At sample point of SOF

- FD Frame: see TSRES bit

bit 0 TBCEN: Time Base Counter Enable bit

1 = Enables TBC

0 = Stops and resets TBC

### REGISTER 3-113: C1TSCONL: CAN TIMESTAMP CONTROL REGISTER LOW

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0       | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------------|-------|

| _      | _   | _   | _   | _   | _   | TBCPRE<9:8> |       |

| bit 15 |     |     |     |     |     |             | bit 8 |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| TBCPRE<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-0 TBCPRE<9:0>: CAN Time Base Counter Prescaler bits

1023 = TBC increments every 1024 clocks

0 = TBC increments every 1 clock

### REGISTER 3-167: ADEIEL: ADC EARLY INTERRUPT ENABLE REGISTER LOW

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| EIEN<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15     |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| EIEN<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7     |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **EIEN<15:0>:** Early Interrupt Enable for Corresponding Analog Input bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

### REGISTER 3-168: ADEIEH: ADC EARLY INTERRUPT ENABLE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------------|-------|-------|

| _     | _   | _   |       |       | EIEN<20:16> |       |       |

| bit 7 |     |     |       |       |             |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 **EIEN<20:16>:** Early Interrupt Enable for Corresponding Analog Input bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

## 4.3 Slave PRAM Program Memory

Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Dual Partition Flash Program Memory" (DS70005156) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

2: Though the reference to the chapter is "Dual Partition Flash Program Memory" (DS70005156), the program memory for the Slave code is PRAM. Therefore, after each POR, the Master will have to reload the content of the Slave PRAM.

The dsPIC33CH128MP508S1 family devices contain internal PRAM program memory for storing and executing application code. The PRAM program memory array is organized into rows of 128 instructions or 64 double instruction words. Though the PRAM is volatile, it is writable during normal operation over the entire VDD range.

PRAM memory can be programmed in three ways:

- In-Circuit Serial Programming™ (ICSP™)

- Run-Time Self-Programming (RTSP)

- Master to Slave Image Loading (MSIL)

ICSP allows for a dsPIC33CH128MP508S1 family device to be serially programmed in the application circuit. Since the Slave PRAM is volatile, Slave PRAM ICSP programming is supported only as a development and debugging feature.

RTSP allows the Slave PRAM user application code to update itself during run time. This feature is capable of writing a single program memory word (two instructions) or an entire row as needed.

Master to Slave Image Loading allows the Master user code to load the Slave PRAM at run time. A Slave PRAM compatible image is stored in Master Flash memory. At run time, the Master user code is responsible for loading and verifying the contents of the Slave PRAM.

Note: In an actual application mode, the Slave PRAM is loaded by the Master, so the ICSP mode of PRAM operation is valid only for the Debug mode during the code development.

# 4.3.1 PRAM PROGRAMMING OPERATIONS

For ICSP and RTSP programming of the Slave PRAM, TBLWTL and TBLWTH instructions are used to write to the NVM write latches. An NVM write operation then writes the contents of both latches to the PRAM, starting at the address defined in the NVMADR and NVMADRU registers.

For Master to Slave Image Loading (MSIL) of the Slave PRAM, the Master user code is responsible for transferring the Slave image contents stored in the Master Flash to the Slave PRAM. The LDSLV instruction is used along with the DSRPAG and DSWPAG registers to transfer a single 24-bit instruction to the Slave PRAM.

The VFSLV instruction allows the Master user code to verify that the PRAM has been loaded correctly.

Note: Master to Slave Image Loading is the only supported method for programming the Slave PRAM in a final user application.

Regardless of the method used to program the PRAM, a few basic requirements should be met:

- A full 48-bit double instruction word should always be programmed to a PRAM location. Either instruction may simply be a NOP to fulfill this requirement. This ensures a valid ECC value is generated for each pair of instructions written.

- Assuming the above step is followed, the last 24-bit location in implemented program space, or prior to any unprogrammed region in program space, should never be executed. The penultimate instruction in either case must contain a program flow change instruction, such as a RETURN or a BRA instruction.

### REGISTER 4-97: ADEIEL: ADC EARLY INTERRUPT ENABLE REGISTER LOW

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| EIEN<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15     |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| EIEN<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7     |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **EIEN<15:0>:** Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

### REGISTER 4-98: ADEIEH: ADC EARLY INTERRUPT ENABLE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------------|-------|-------|

| _     | _   | _   |       |       | EIEN<20:16> |       |       |

| bit 7 |     |     |       |       |             |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 **EIEN<20:16>:** Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

### REGISTER 14-5: SPIXSTATH: SPIX STATUS REGISTER HIGH

| U-0    | U-0 | HSC/R-0               | HSC/R-0               | HSC/R-0               | HSC/R-0 | HSC/R-0 | HSC/R-0 |

|--------|-----|-----------------------|-----------------------|-----------------------|---------|---------|---------|

| _      | _   | RXELM5 <sup>(3)</sup> | RXELM4 <sup>(2)</sup> | RXELM3 <sup>(1)</sup> | RXELM2  | RXELM1  | RXELM0  |

| bit 15 |     |                       |                       |                       |         |         | bit 8   |

| U-0   | U-0 | HSC/R-0               | HSC/R-0               | HSC/R-0               | HSC/R-0 | HSC/R-0 | HSC/R-0 |

|-------|-----|-----------------------|-----------------------|-----------------------|---------|---------|---------|

| _     | _   | TXELM5 <sup>(3)</sup> | TXELM4 <sup>(2)</sup> | TXELM3 <sup>(1)</sup> | TXELM2  | TXELM1  | TXELM0  |

| bit 7 |     |                       |                       |                       |         |         | bit 0   |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RXELM<5:0>:** Receive Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **TXELM<5:0>:** Transmit Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

**Note 1:** RXELM3 and TXELM3 bits are only present when FIFODEPTH = 8 or higher.

**2:** RXELM4 and TXELM4 bits are only present when FIFODEPTH = 16 or higher.

**3:** RXELM5 and TXELM5 bits are only present when FIFODEPTH = 32.

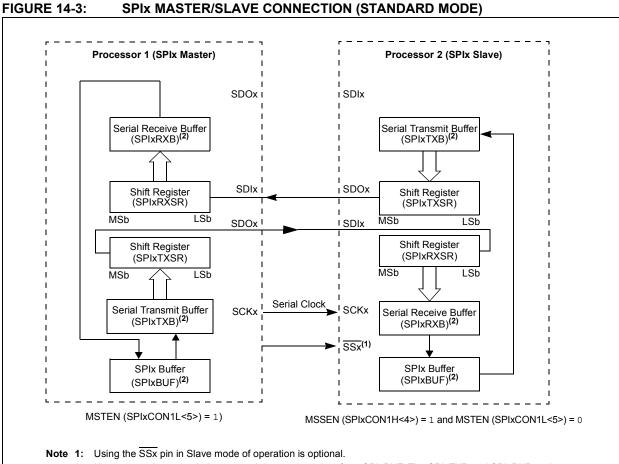

2: User must write transmit data to read the received data from SPIxBUF. The SPIxTXB and SPIxRXB registers are memory-mapped to SPIxBUF.

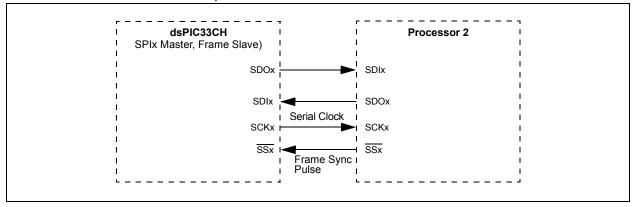

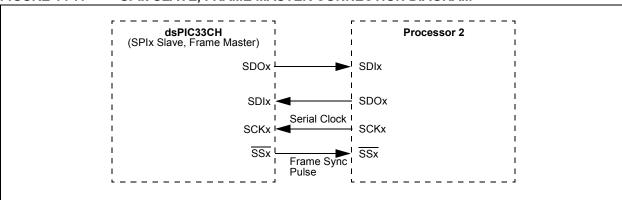

FIGURE 14-6: SPIX MASTER, FRAME SLAVE CONNECTION DIAGRAM

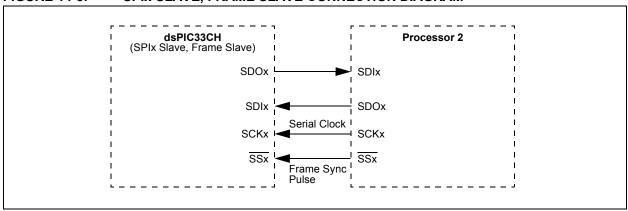

FIGURE 14-7: SPIX SLAVE, FRAME MASTER CONNECTION DIAGRAM

FIGURE 14-8: SPIX SLAVE, FRAME SLAVE CONNECTION DIAGRAM

**EQUATION 14-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED**

$$Baud\ Rate = \frac{FPB}{(2*(SPIxBRG+1))}$$

Where:

FPB is the Peripheral Bus Clock Frequency.

## **REGISTER 21-13: FDMT CONFIGURATION REGISTER**

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   |     | _   |     | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      |     |     | _   | _   | _   |     |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-1   | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | R/PO-1 |

|-------|-----|-----|-----|-----|-----|-----|--------|

| _     | _   | _   | _   | _   | _   | _   | DMTDIS |

| bit 7 |     |     |     |     |     |     | bit 0  |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-1 **Unimplemented:** Read as '1'

bit 0 **DMTDIS:** DMT Disable bit

1 = DMT is disabled 0 = DMT is enabled

## 24.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33CH128MP508 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33CH128MP508 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to +3.6V        |

| Maximum current out of Vss pin                                                    | 300 mA               |

| Maximum current into VDD pin <sup>(2)</sup>                                       | 300 mA               |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2)</sup>                                  | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those, or any other conditions above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 24-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

FIGURE 24-8: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

TABLE 24-35: SPIx MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |      |                     |            |     |                             |  |

|--------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------------|-----|-----------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                    | Min. | Typ. <sup>(2)</sup> | Conditions |     |                             |  |

| SP10               | FscP                  | Maximum SCKx Frequency                                                                                                                                                                                                                           | _    | _                   | 15         | MHz | Using PPS pins              |  |

|                    |                       |                                                                                                                                                                                                                                                  | _    | _                   | 40         | MHz | SPI2 dedicated pins         |  |

| SP20               | TscF                  | SCKx Output Fall Time                                                                                                                                                                                                                            | _    | _                   | _          | ns  | See Parameter DO32 (Note 3) |  |

| SP21               | TscR                  | SCKx Output Rise Time                                                                                                                                                                                                                            | _    | _                   | _          | ns  | See Parameter DO31 (Note 3) |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                                                                                                                                                                                                       | _    | _                   | _          | ns  | See Parameter DO32 (Note 3) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                                                                                                                                                                                                       | _    | _                   | _          | ns  | See Parameter DO31 (Note 3) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After SCKx Edge                                                                                                                                                                                                           | _    | 6                   | 20         | ns  |                             |  |

| SP36               | TdiV2scH,             | -                                                                                                                                                                                                                                                | 30   | _                   |            | ns  | Using PPS pins              |  |

| TdiV2scL           |                       | First SCKx Edge                                                                                                                                                                                                                                  | 3    | _                   | _          | ns  | SPI2 dedicated pins         |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

3: Assumes 50 pF load on all SPIx pins.

## 25.0 PACKAGING INFORMATION

## 25.1 Package Marking Information

28-Lead SSOP (5.30 mm)

### Example

28-Lead UQFN (6x6 mm)

Example

36-Lead UQFN (5x5 mm)

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

**Note:** In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

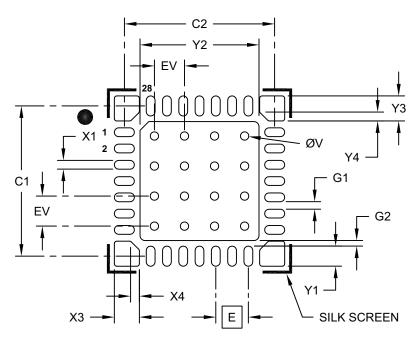

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (2N) - 6x6x0.55 mm Body [UQFN] With 4.65x4.65 mm Exposed Pad and Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |          |      |      |  |

|---------------------------------|-------------|----------|------|------|--|

| Dimension                       | MIN         | NOM      | MAX  |      |  |

| Contact Pitch                   | Е           | 0.65 BSC |      |      |  |

| Optional Center Pad Width       | X2          |          |      | 4.75 |  |

| Optional Center Pad Length      | Y2          |          |      | 4.75 |  |

| Contact Pad Spacing             | C1          |          | 6.00 |      |  |

| Contact Pad Spacing             | C2          |          | 6.00 |      |  |

| Contact Pad Width (X28)         | X1          |          |      | 0.35 |  |

| Contact Pad Length (X28)        | Y1          |          |      | 0.80 |  |

| Corner Anchor (X4)              | Х3          |          |      | 1.00 |  |

| Corner Anchor (X4)              | Y3          |          |      | 1.00 |  |

| Corner Anchor Chamfer (X4)      | X4          |          |      | 0.35 |  |

| Corner Anchor Chamfer (X4)      | Y4          |          |      | 0.35 |  |

| Contact Pad to Pad (X28)        | G1          | 0.20     |      |      |  |

| Contact Pad to Center Pad (X28) | G2          | 0.20     |      |      |  |

| Thermal Via Diameter            | V           |          | 0.33 |      |  |

| Thermal Via Pitch               |             |          | 1.20 |      |  |

### Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2385B