Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit Dual-Core                                                                  |

| Speed                      | 180MHz, 200MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 152KB (152K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                       |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 20K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 34x12b; D/A 4x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch128mp506t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin # | Master Core                      | Slave Core                         |

|-------|----------------------------------|------------------------------------|

| 51    | Vdd                              | Vod                                |

| 52    | RP71/RD7                         | \$1RP71/S1PWM8H/S1RD7              |

| 53    | RP70/RD6                         | \$1RP70/S1PWM6H/S1RD6              |

| 54    | RP69/RD5                         | S1RP69/S1PWM6L/S1RD5               |

| 55    | PGD3/ <b>RP37</b> /SDA2/RB5      | S1PGD3/ <b>S1RP37</b> /S1RB5       |

| 56    | PGC3/ <b>RP38</b> /SCL2/RB6      | S1PGC3/S1RP38/S1RB6                |

| 57    | RE10                             | S1RE10                             |

| 58    | TDO/AN9/ <b>RP39</b> /RB7        | S1MCLR1/S1AN6/S1RP39/S1PWM5H/S1RB7 |

| 59    | RE11                             | S1RE11                             |

| 60    | PGD1/AN10/ <b>RP40</b> /SCL1/RB8 | S1PGD1/S1AN7/S1RP40/S1SCL1/S1RB8   |

| 61    | PGC1/AN11/ <b>RP41</b> /SDA1/RB9 | S1PGC1/S1RP41/S1SDA1/S1RB9         |

| 62    | ASCL2/RE12                       | S1RE12                             |

| 63    | RP52/RC4                         | S1RP52/S1PWM2H/S1RC4               |

| 64    | ASDA2/RE13                       | S1RE13                             |

| 65    | RP53/RC5                         | S1RP53/S1PWM2L/S1RC5               |

| 66    | RP58/RC10                        | S1RP58/S1PWM1H/S1RC10              |

| 67    | RP59/RC11                        | S1RP59/S1PWM1L/S1RC11              |

| 68    | RP68/RD4                         | S1RP68/S1PWM3H/S1RD4               |

| 69    | RP67/RD3                         | S1RP67/S1PWM3L/S1RD3               |

| 70    | Vss                              | Vss                                |

| 71    | Vdd                              | VDD                                |

| 72    | RP66/RD2                         | S1RP66/S1PWM8L/S1RD2               |

| 73    | RP65/RD1                         | S1RP65/S1PWM4H/S1RD1               |

| 74    | RP64/RD0                         | S1RP64/S1PWM4L/S1RD0               |

| 75    | TMS/RP42/PWM3H/RB10              | S1RP42/S1RB10                      |

| 76    | TCK/ <b>RP43</b> /PWM3L/RB11     | <b>S1RP43</b> /S1RB11              |

| 77    | RE14                             | S1RE14                             |

| 78    | TDI/ <b>RP44</b> /PWM2H/RB12     | <b>S1RP44</b> /S1RB12              |

| 79    | RE15                             | S1RE15                             |

| 80    | RP45/PWM2L/RB13                  | <b>S1RP45</b> /S1RB13              |

#### TABLE 9: 80-PIN TQFP (CONTINUED)

Legend: RPn and S1RPn represent remappable pins for Peripheral Pin Select functions.

| U-0                                | U-0 | U-0 | U-0                                | U-0              | U-0   | U-0             | U-0   |

|------------------------------------|-----|-----|------------------------------------|------------------|-------|-----------------|-------|

| —                                  | —   | —   | _                                  | —                | —     | —               | —     |

| bit 15                             |     |     |                                    |                  |       |                 | bit 8 |

|                                    |     |     |                                    |                  |       |                 |       |

| U-0                                | U-0 | U-0 | U-0                                | U-0              | U-0   | R/W-0           | R/W-0 |

| —                                  | —   | —   | -                                  | —                | —     | ECCDBE          | SGHT  |

| bit 7                              |     |     |                                    |                  |       |                 | bit 0 |

|                                    |     |     |                                    |                  |       |                 |       |

| Legend:                            |     |     |                                    |                  |       |                 |       |

| R = Readable bit W = Writable bit  |     |     | U = Unimplemented bit, read as '0' |                  |       |                 |       |

| -n = Value at POR '1' = Bit is set |     |     |                                    | '0' = Bit is cle | eared | x = Bit is unkr | nown  |

## REGISTER 3-21: INTCON4: INTERRUPT CONTROL REGISTER 4

bit 15-2 Unimplemented: Read as '0'

bit 1 ECCDBE: ECC Double-Bit Error Trap bit 1 = ECC double-bit error trap has occurred 0 = ECC double-bit error trap has not occurred

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

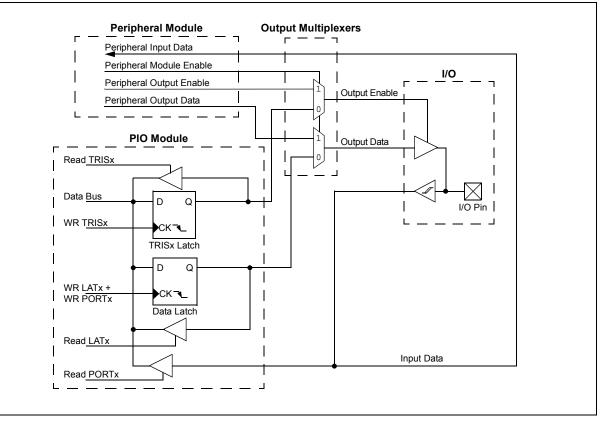

## FIGURE 3-19: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

## REGISTER 3-65: RPINR45: PERIPHERAL PIN SELECT INPUT REGISTER 45

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| CLCINAR7 | CLCINAR6 | CLCINAR5 | CLCINAR4 | CLCINAR3 | CLCINAR2 | CLCINAR1 | CLCINAR0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SENT2R7 | SENT2R6 | SENT2R5 | SENT2R4 | SENT2R3 | SENT2R2 | SENT2R1 | SENT2R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

bit 15-8CLCINAR<7:0>: Assign CLC Input A (CLCINA) to the Corresponding RPn Pin bits<br/>See Table 3-30.bit 7-0SENT2R<7:0>: Assign SENT2 Input (SENT2) to the Corresponding RPn Pin bits

See Table 3-30.

## REGISTER 3-66: RPINR46: PERIPHERAL PIN SELECT INPUT REGISTER 46

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| CLCINCR7 | CLCINCR6 | CLCINCR5 | CLCINCR4 | CLCINCR3 | CLCINCR2 | CLCINCR1 | CLCINCR0 |

| bit 15   | •        |          |          |          |          |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| CLCINBR7 | CLCINBR6 | CLCINBR5 | CLCINBR4 | CLCINBR3 | CLCINBR2 | CLCINBR1 | CLCINBR0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

bit 15-8 **CLCINCR<7:0>:** Assign CLC Input C (CLCINC) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 CLCINBR<7:0>: Assign CLC Input B (CLCINB) to the Corresponding RPn Pin bits See Table 3-30.

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —      | —   | RP177R5 <sup>(1)</sup> | RP177R4 <sup>(1)</sup> | RP177R3 <sup>(1)</sup> | RP177R2 <sup>(1)</sup> | RP177R1 <sup>(1)</sup> | RP177R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _     | —   | RP176R5 <sup>(1)</sup> | RP176R4 <sup>(1)</sup> | RP176R3 <sup>(1)</sup> | RP176R2 <sup>(1)</sup> | RP176R1 <sup>(1)</sup> | RP176R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP177R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP177 Output Pin bits <sup>(1)</sup> (see Table 3-33 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                                |

bit 5-0 **RP176R<5:0>:** Peripheral Output Function is Assigned to RP176 Output Pin bits<sup>(1)</sup> (see Table 3-33 for peripheral function numbers)

Note 1: These are virtual output ports.

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —      | _   | RP179R5 <sup>(1)</sup> | RP179R4 <sup>(1)</sup> | RP179R3 <sup>(1)</sup> | RP179R2 <sup>(1)</sup> | RP179R1 <sup>(1)</sup> | RP179R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —     | —   | RP178R5 <sup>(1)</sup> | RP178R4 <sup>(1)</sup> | RP178R3 <sup>(1)</sup> | RP178R2 <sup>(1)</sup> | RP178R1 <sup>(1)</sup> | RP178R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                                                              |                      |                    |  |

|-------------------|--------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | able bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                             | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP179R<5:0>:** Peripheral Output Function is Assigned to RP179 Output Pin bits<sup>(1)</sup> (see Table 3-33 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits<sup>(1)</sup> (see Table 3-33 for peripheral function numbers)

Note 1: These are virtual output ports.

| U-0          | U-0                 | U-0                                      | R-0         | R-0              | R-0              | R-0             | R-0      |

|--------------|---------------------|------------------------------------------|-------------|------------------|------------------|-----------------|----------|

| _            | _                   | —                                        |             |                  | FILHIT<4:0>      |                 |          |

| bit 15       |                     |                                          |             |                  |                  |                 | bit 8    |

|              |                     |                                          |             |                  |                  |                 |          |

| U-0          | R-1                 | R-0                                      | R-0         | R-0              | R-0              | R-0             | R-0      |

|              |                     |                                          |             | ICODE<6:0>       |                  |                 |          |

| bit 7        |                     |                                          |             |                  |                  |                 | bit 0    |

| Legend:      |                     |                                          |             |                  |                  |                 |          |

| R = Readab   | le bit              | W = Writable bit                         |             | U = Unimpler     | nented bit, read | d as '0'        |          |

| -n = Value a | t POR               | '1' = Bit is set                         |             | '0' = Bit is cle |                  | x = Bit is unkr | nown     |

|              |                     |                                          |             |                  |                  |                 |          |

| bit 15-13    | Unimpleme           | nted: Read as '0'                        |             |                  |                  |                 |          |

| bit 12-8     | FILHIT<4:0>         | : Filter Hit Number                      | r bits      |                  |                  |                 |          |

|              | 01111 = Filt        |                                          |             |                  |                  |                 |          |

|              | 01110 <b>= Filt</b> | er 14                                    |             |                  |                  |                 |          |

|              | <br>00001 = Filt    | er 1                                     |             |                  |                  |                 |          |

|              | 00000 = Filt        | -                                        |             |                  |                  |                 |          |

| bit 7        | Unimpleme           | nted: Read as '0'                        |             |                  |                  |                 |          |

| bit 6-0      | ICODE<6:0>          | Interrupt Flag Co                        | de bits     |                  |                  |                 |          |

|              |                     | 111111 <b>= Reserve</b>                  |             |                  |                  |                 |          |

|              |                     | Transmit attempt in                      |             |                  |                  |                 |          |

|              |                     | Transmit event FIF<br>Invalid message of |             |                  | EFSTA IS Set)    |                 |          |

|              |                     | CAN module mode                          |             |                  | -/IE)            |                 |          |

|              |                     | CAN timer overflow                       |             |                  | ,                |                 |          |

|              |                     | RX/TX MAB overfl                         |             |                  |                  |                 |          |

|              |                     | saved to memory;                         |             |                  |                  |                 | nt data) |

|              |                     | Address error inter<br>Receive FIFO over |             |                  |                  |                 |          |

|              |                     | Wake-up interrupt                        |             |                  |                  | ()              |          |

|              |                     | Error interrupt (CE                      |             | ,                |                  |                 |          |

|              | 1000000 =           |                                          |             |                  |                  |                 |          |

|              |                     | 111111 = Reserve<br>FIFO 7 interrupt (T  |             | IE7 is sof)      |                  |                 |          |

|              | 0000111 =           |                                          |             | ir i is selj     |                  |                 |          |

|              |                     | FIFO 1 interrupt (T                      | FIF1 or RF  | IF1 is set)      |                  |                 |          |

|              | 0000000 =           | FIFO 0 interrupt (T                      | FIF0 is set | )                |                  |                 |          |

|              |                     |                                          |             |                  |                  |                 |          |

## REGISTER 3-115: C1VECL: CAN INTERRUPT CODE REGISTER LOW

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI11R7 | PCI11R6 | PCI11R5 | PCI11R4 | PCI11R3 | PCI11R2 | PCI11R1 | PCI11R0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| R/W-0   |

| PCI10R7 | PCI10R6 | PCI10R5 | PCI10R4 | PCI10R3 | PCI10R2 | PCI10R1 | PCI10R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Lagandi |         |         |         |         |         |         |         |

#### REGISTER 4-45: RPINR13: PERIPHERAL PIN SELECT INPUT REGISTER 13

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8PCI11R<7:0>: Assign PWM Input 11 (S1PCI11) to the Corresponding S1RPn Pin bits<br/>See Table 4-27.bit 7-0PCI10R<7:0>: Assign PWM Input 10 (S1PCI10) to the Corresponding S1RPn Pin bits

See Table 4-27.

## REGISTER 4-46: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| QEIB1R7 | QEIB1R6 | QEIB1R5 | QEIB1R4 | QEIB1R3 | QEIB1R2 | QEIB1R1 | QEIB1R0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| QEIA1R7 | QEIA1R6 | QEIA1R5 | QEIA1R4 | QEIA1R3 | QEIA1R2 | QEIA1R1 | QEIA1R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-8 **QEIB1R<7:0>:** Assign QEI Input B (S1QEIB1) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 **QEIA1R<7:0>:** Assign QEI Input A (S1QEIA1) to the Corresponding S1RPn Pin bits See Table 4-27.

## REGISTER 4-53: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI18R7 | PCI18R6 | PCI18R5 | PCI18R4 | PCI18R3 | PCI18R2 | PCI18R1 | PCI18R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8

Unimplemented: Read as '0'

bit 7-0

PCI18R<7:0>: Assign PWM Input 18 (S1PCI18) to the Corresponding S1RPn Pin bits See Table 4-27.

#### REGISTER 4-54: RPINR42: PERIPHERAL PIN SELECT INPUT REGISTER 42

| PCI13R7         PCI13R6         PCI13R5         PCI13R4         PCI13R3         PCI13R2         PCI13R1         PCI13R0           bit 15         bit | R/W-0   |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| bit 15 bit                                                                                                                                           | PCI13R7 | PCI13R6 | PCI13R5 | PCI13R4 | PCI13R3 | PCI13R2 | PCI13R1 | PCI13R0 |

|                                                                                                                                                      | bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI12R7 | PCI12R6 | PCI12R5 | PCI12R4 | PCI12R3 | PCI12R2 | PCI12R1 | PCI12R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 **PCI13R<7:0>:** Assign PWM Input 13 (S1PCI13) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 PCI12R<7:0>: Assign PWM Input 12 (S1PCI12) to the Corresponding S1RPn Pin bits See Table 4-27.

## REGISTER 4-97: ADEIEL: ADC EARLY INTERRUPT ENABLE REGISTER LOW

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0   | R/W-0                | R/W-0 | R/W-0              |  |

|-----------------------------------|-------|------------------|------------------------------------|---------|----------------------|-------|--------------------|--|

|                                   |       |                  | EIEN                               | N<15:8> |                      |       |                    |  |

| bit 15                            |       |                  |                                    |         |                      |       | bit 8              |  |

|                                   |       |                  |                                    |         |                      |       |                    |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0   | R/W-0                | R/W-0 | R/W-0              |  |

|                                   |       |                  | EIE                                | N<7:0>  |                      |       |                    |  |

| bit 7                             |       |                  |                                    |         |                      |       | bit 0              |  |

|                                   |       |                  |                                    |         |                      |       |                    |  |

| Legend:                           |       |                  |                                    |         |                      |       |                    |  |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |         |                      |       |                    |  |

| -n = Value at POR '1' =           |       | '1' = Bit is set | '1' = Bit is set                   |         | '0' = Bit is cleared |       | x = Bit is unknown |  |

bit 15-0 EIEN<15:0>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

## REGISTER 4-98: ADEIEH: ADC EARLY INTERRUPT ENABLE REGISTER HIGH

| U-0                                      | U-0 | U-0              | U-0                                               | U-0                                | U-0   | U-0   | U-0   |

|------------------------------------------|-----|------------------|---------------------------------------------------|------------------------------------|-------|-------|-------|

| —                                        | —   | —                | _                                                 | —                                  | —     | —     | —     |

| bit 15                                   |     |                  |                                                   |                                    |       |       | bit 8 |

|                                          |     |                  |                                                   |                                    |       |       |       |

| U-0                                      | U-0 | U-0              | R/W-0                                             | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                          |     | —                | EIEN<20:16>                                       |                                    |       |       |       |

| bit 7                                    |     |                  |                                                   |                                    |       |       | bit 0 |

|                                          |     |                  |                                                   |                                    |       |       |       |

| Legend:                                  |     |                  |                                                   |                                    |       |       |       |

| R = Readable bit W = Writable bit U = Un |     |                  | U = Unimplem                                      | J = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at                            | POR | '1' = Bit is set | it is set '0' = Bit is cleared x = Bit is unknown |                                    |       | nown  |       |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 EIEN<20:16>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

## REGISTER 4-101: ADMOD0L: ADC INPUT MODE CONTROL REGISTER 0 LOW

| U-0                                | U-0                                                                  | U-0              | U-0             | U-0                                     | U-0        | U-0   | U-0   |  |  |

|------------------------------------|----------------------------------------------------------------------|------------------|-----------------|-----------------------------------------|------------|-------|-------|--|--|

| —                                  | —                                                                    | —                | —               | —                                       | —          | —     | —     |  |  |

| bit 15                             |                                                                      |                  |                 |                                         |            |       | bit 8 |  |  |

|                                    |                                                                      |                  |                 |                                         |            |       |       |  |  |

| U-0                                | U-0                                                                  | U-0              | U-0             | R/W-0                                   | R/W-0      | R/W-0 | R/W-0 |  |  |

| —                                  | —                                                                    | —                | —               | DIFF1                                   | SIGN1      | DIFF0 | SIGN0 |  |  |

| bit 7 bit 0                        |                                                                      |                  |                 |                                         |            |       |       |  |  |

|                                    |                                                                      |                  |                 |                                         |            |       |       |  |  |

| Legend:                            |                                                                      |                  |                 |                                         |            |       |       |  |  |

| R = Readable                       | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                 |                                         |            |       |       |  |  |

| -n = Value at POR '1' = Bit is set |                                                                      |                  |                 | '0' = Bit is cleared x = Bit is unknown |            |       | iown  |  |  |

|                                    |                                                                      |                  |                 |                                         |            |       |       |  |  |

| bit 15-4                           | Unimplement                                                          | ted: Read as 'd  | )'              |                                         |            |       |       |  |  |

| bit 3 and bit 1                    | DIFF<1:0>: D                                                         | ifferential-Mode | e for Correspoi | nding Analog Ir                         | nputs bits |       |       |  |  |

| (odd)                              | 1 = Channel is differential                                          |                  |                 |                                         |            |       |       |  |  |

|                                    | 0 = Channel is single-ended                                          |                  |                 |                                         |            |       |       |  |  |

| bit 2 and bit 0                    | SIGN<1:0>: (                                                         | Output Data Sig  | n for Correspo  | nding Analog I                          | nputs bits |       |       |  |  |

| (even)                             | 1 = Channel output data is signed                                    |                  |                 |                                         |            |       |       |  |  |

|                                    | 0 = Channel output data is unsigned                                  |                  |                 |                                         |            |       |       |  |  |

## REGISTER 5-3: MSI1KEY: MSI1 MASTER INTERLOCK KEY REGISTER

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |  |  |

|--------------|-----|-----|-----|-----|-----|-----|-------|--|--|

| —            | —   | —   | —   | _   | —   | —   | —     |  |  |

| bit 15       |     |     |     |     |     |     | bit 8 |  |  |

|              |     |     |     |     |     |     |       |  |  |

| W-0          | W-0 | W-0 | W-0 | W-0 | W-0 | W-0 | W-0   |  |  |

| MSI1KEY<7:0> |     |     |     |     |     |     |       |  |  |

| bit 7        |     |     |     |     |     |     | bit 0 |  |  |

|              |     |     |     |     |     |     |       |  |  |

| Legend:      |     |     |     |     |     |     |       |  |  |

| =ogona.           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 MSI1KEY<7:0>: MSI1 Key bits

The MSI1KEYx bits are monitored for specific write values.

#### REGISTER 5-4: MSI1MBXS: MSI1 MASTER MAILBOX DATA TRANSFER STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

|        |     |     |     |     |     |     |       |

| R/W-0             | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| DTRDY <h:a></h:a> |       |       |       |       |       |       |       |  |  |  |  |

| bit 7             |       |       |       |       |       |       | bit 0 |  |  |  |  |

|                   |       |       |       |       |       |       |       |  |  |  |  |

| Legend:           |                  |                                                     |                    |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | <i>W</i> = Writable bit U = Unimplemented bit, read |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 DTRDY<H:A>: Data Ready Status bits

- 1 = Data transmitter has indicated that data is available to be read by data receiver in MSI1MBXnD (DTRDYx is automatically set by a data transmitter processor write to assigned MSI1MBXnD); Meaning when configured as a:

- Transmitter: Data is written. Waiting for receiver to read.

- Receiver: New data is ready to read.

- 0 = No data is available to be read by receiver in MSI1MBXnD (or the handshake protocol logic block is disabled)

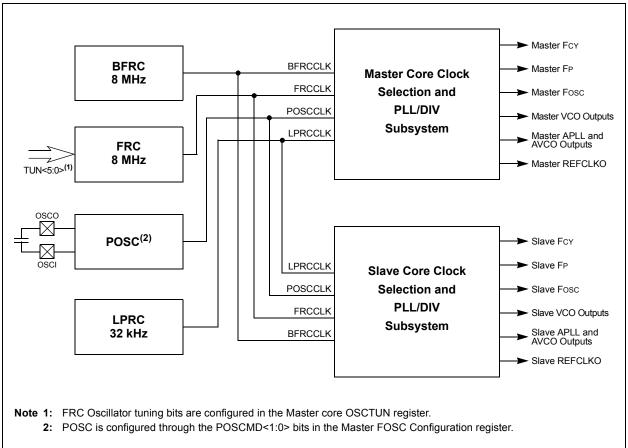

## 6.0 OSCILLATOR WITH HIGH-FREQUENCY PLL

Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator Module with High-Speed PLL" (DS70005255) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33CH128MP508 family oscillator with high-frequency PLL includes these characteristics:

- Master and Core Subsystems

- Internal and External Oscillator Sources Shared between Master and Slave Cores

- Master and Slave Independent On-Chip Phase-Locked Loop (PLL) to Boost Internal Operating Frequency on Select Internal and External Oscillator Sources

- Master and Slave Independent Auxiliary PLL (APLL) Clock Generator to Boost Operating Frequency for Peripherals

- Master and Slave Independent Doze mode for System Power Savings

- Master and Slave Independent Scalable Reference Clock Output (REFCLKO)

- On-the-Fly Clock Switching between Various Clock Sources

- Fail-Safe Clock Monitoring (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

A block diagram of the dsPIC33CH128MP508 oscillator system is shown in Figure 6-1.

## FIGURE 6-1: MASTER AND SLAVE CORE SHARED CLOCK SOURCES BLOCK DIAGRAM

| U-0               | U-0                       | U-0                                 | U-0                                 | U-0                     | U-0                | U-0                | R/W-0        |  |

|-------------------|---------------------------|-------------------------------------|-------------------------------------|-------------------------|--------------------|--------------------|--------------|--|

| _                 | —                         | _                                   | _                                   | —                       | —                  | _                  | P1<8>        |  |

| bit 15            |                           |                                     |                                     |                         |                    |                    | bit 8        |  |

|                   |                           |                                     |                                     |                         |                    |                    |              |  |

| R/W-0             | R/W-0                     | R/W-0                               | R/W-0                               | R/W-0                   | R/W-0              | R/W-0              | R/W-0        |  |

|                   |                           |                                     | P1<                                 | 7:0>                    |                    |                    |              |  |

| bit 7             |                           |                                     |                                     |                         |                    |                    | bit 0        |  |

|                   |                           |                                     |                                     |                         |                    |                    |              |  |

| Legend:           |                           |                                     |                                     |                         |                    |                    |              |  |

| R = Readab        | le bit                    | W = Writable bit                    |                                     | U = Unimpler            | nented bit, read   | d as '0'           |              |  |

| -n = Value at POR |                           | '1' = Bit is set                    |                                     | '0' = Bit is cle        | ared               | x = Bit is unknown |              |  |

|                   |                           |                                     |                                     |                         |                    |                    |              |  |

| bit 15-9          | Unimplemen                | ted: Read as '0                     | ,                                   |                         |                    |                    |              |  |

| bit 8-0           | <b>P1&lt;8:0&gt;:</b> Par | ameter 1 bits                       |                                     |                         |                    |                    |              |  |

|                   | DMX TX:                   |                                     |                                     |                         |                    |                    |              |  |

|                   |                           | tes to Transmit                     | <ul> <li>– 1 (not includ</li> </ul> | ling Start code)        |                    |                    |              |  |

|                   | LIN Master T              |                                     |                                     |                         |                    |                    |              |  |

|                   |                           | nit (bits<5:0>).                    | _                                   |                         |                    |                    |              |  |

|                   |                           | s TX with Addre                     |                                     | a a what a limit a lait | 0 (1):40 (7:0)     |                    |              |  |

|                   |                           | ansmit. A '1' is a<br>Inde:         | iutomatically in                    | iserted into bit        | 9 (DItS< $7:0>$ ). |                    |              |  |

|                   | Smart Card M              | <u>liode:</u><br>Counter bits. This | s counter is on                     | erated on the h         | it clock whose     | neriod is alway    | equal to one |  |

|                   | ETU (bits<8:0             |                                     |                                     |                         |                    | period is diway.   |              |  |

|                   | Other Modes:              | <u>.</u>                            |                                     |                         |                    |                    |              |  |

|                   | Not used.                 |                                     |                                     |                         |                    |                    |              |  |

|                   |                           |                                     |                                     |                         |                    |                    |              |  |

## REGISTER 13-9: UxP1: UARTx TIMING PARAMETER 1 REGISTER

| Slave Address | R/W Bit | Description                            |

|---------------|---------|----------------------------------------|

| 0000 000      | 0       | General Call Address <sup>(2)</sup>    |

| 0000 000      | 1       | Start Byte                             |

| 0000 001      | х       | Cbus Address                           |

| 0000 01x      | х       | Reserved                               |

| 0000 1xx      | х       | HS Mode Master Code                    |

| 1111 0xx      | х       | 10-Bit Slave Upper Byte <sup>(3)</sup> |

| 1111 1xx      | х       | Reserved                               |

Note 1: The address bits listed here will never cause an address match independent of address mask settings.

2: This address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

# 20.1 Current Bias Generator Control Registers

## REGISTER 20-1: BIASCON: CURRENT BIAS GENERATOR CONTROL REGISTER

| R/W-0        | U-0                                | U-0                                    | U-0         | U-0              | U-0             | U-0             | U-0    |  |  |

|--------------|------------------------------------|----------------------------------------|-------------|------------------|-----------------|-----------------|--------|--|--|

| ON           |                                    | —                                      | —           | —                |                 | —               |        |  |  |

| bit 15       |                                    |                                        |             |                  |                 |                 | bit 8  |  |  |

|              |                                    |                                        |             |                  |                 |                 |        |  |  |

| U-0          | U-0                                | U-0                                    | U-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |  |  |

|              | —                                  | —                                      | —           | 110EN3           | I10EN2          | 110EN1          | 110EN0 |  |  |

| bit 7        |                                    |                                        |             |                  |                 |                 | bit 0  |  |  |

|              |                                    |                                        |             |                  |                 |                 |        |  |  |

| Legend:      |                                    |                                        |             |                  |                 |                 |        |  |  |

| R = Readab   | ole bit                            | W = Writable I                         | oit         | U = Unimpler     | nented bit, rea | d as '0'        |        |  |  |

| -n = Value a | at POR                             | '1' = Bit is set                       |             | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |  |  |

|              |                                    |                                        |             |                  |                 |                 |        |  |  |

| bit 15       | ON: Current Bias Module Enable bit |                                        |             |                  |                 |                 |        |  |  |

|              | 1 = Module is                      |                                        |             |                  |                 |                 |        |  |  |

|              | 0 = Module is                      |                                        |             |                  |                 |                 |        |  |  |

| bit 14-4     | Unimplemen                         | ted: Read as '0                        | )'          |                  |                 |                 |        |  |  |

| bit 3        | <b>Ι10ΕΝ3:</b> 10 μ                | I10EN3: 10 µA Enable for Output 3 bit  |             |                  |                 |                 |        |  |  |

|              |                                    | $1 = 10 \mu\text{A}$ output is enabled |             |                  |                 |                 |        |  |  |

|              | •                                  | put is disabled                        |             |                  |                 |                 |        |  |  |

| bit 2        | •                                  | A Enable for Ou                        | utput 2 bit |                  |                 |                 |        |  |  |

|              |                                    | put is enabled put is disabled         |             |                  |                 |                 |        |  |  |

| bit 1        | •                                  | A Enable for O                         | itout 1 bit |                  |                 |                 |        |  |  |

|              | -                                  | put is enabled                         | aiput i bit |                  |                 |                 |        |  |  |

|              |                                    | put is disabled                        |             |                  |                 |                 |        |  |  |

| bit 0        | -                                  | A Enable for Ou                        | utput 0 bit |                  |                 |                 |        |  |  |

|              |                                    | put is enabled                         | •           |                  |                 |                 |        |  |  |

|              | •                                  | ,<br>put is disabled                   |             |                  |                 |                 |        |  |  |

|              |                                    |                                        |             |                  |                 |                 |        |  |  |

# REGISTER 20-2: IBIASCONH: CURRENT BIAS GENERATOR 50 $\mu A$ CURRENT SOURCE CONTROL HIGH REGISTER

|                  | -                                                                                                                                                          |                                                                          |                |                    |                   |                 |        |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|--------------------|-------------------|-----------------|--------|--|--|--|--|

| U-0              | U-0                                                                                                                                                        | R/W-0                                                                    | R/W-0          | R/W-0              | R/W-0             | R/W-0           | R/W-0  |  |  |  |  |

| _                | _                                                                                                                                                          | SHRSRCEN3                                                                | SHRSNKEN3      | GENSRCEN3          | GENSNKEN3         | SRCEN3          | SNKEN3 |  |  |  |  |

| bit 15           |                                                                                                                                                            |                                                                          |                |                    |                   |                 | bit 8  |  |  |  |  |

|                  |                                                                                                                                                            | -                                                                        |                |                    | -                 |                 |        |  |  |  |  |

| U-0              | U-0                                                                                                                                                        | R/W-0                                                                    | R/W-0          | R/W-0              | R/W-0             | R/W-0           | R/W-0  |  |  |  |  |

|                  | _                                                                                                                                                          | SHRSRCEN2                                                                | SHRSNKEN2      | GENSRCEN2          | GENSNKEN2         | SRCEN2          | SNKEN2 |  |  |  |  |

| bit 7            |                                                                                                                                                            |                                                                          |                |                    |                   |                 | bit 0  |  |  |  |  |

| Legend:          |                                                                                                                                                            |                                                                          |                |                    |                   |                 |        |  |  |  |  |

| R = Readable     | e bit                                                                                                                                                      | W = Writable bi                                                          | t              | U = Unimpleme      | ented bit, read a | s '0'           |        |  |  |  |  |

| -n = Value at    | POR                                                                                                                                                        | '1' = Bit is set                                                         |                | '0' = Bit is clear |                   | x = Bit is unkr | nown   |  |  |  |  |

|                  |                                                                                                                                                            |                                                                          |                |                    |                   |                 |        |  |  |  |  |

| bit 15-14        | Unimpleme                                                                                                                                                  | ented: Read as 'C                                                        | 3              |                    |                   |                 |        |  |  |  |  |

| bit 13           |                                                                                                                                                            | N3: Share Source                                                         |                | •                  |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | g Current Mirror r<br>g Current Mirror r                                 |                |                    | ce from another   | source)         |        |  |  |  |  |

| bit 12           | -                                                                                                                                                          | <b>13:</b> Share Sink E                                                  |                |                    |                   |                 |        |  |  |  |  |

|                  | 1 = Sinking                                                                                                                                                | Current Mirror me                                                        | ode is enabled | (uses reference    | e from another s  | ource)          |        |  |  |  |  |

|                  | •                                                                                                                                                          | Current Mirror m                                                         |                |                    |                   |                 |        |  |  |  |  |

| bit 11           |                                                                                                                                                            | N3: Generated So                                                         |                | •                  |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | generates the cu<br>does not generat                                     |                |                    | erence            |                 |        |  |  |  |  |

| bit 10           | <ul> <li>0 = Source does not generate the current source mirror reference</li> <li>GENSNKEN3: Generated Sink Enable for Output #3 bit</li> </ul>           |                                                                          |                |                    |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | generates the cu                                                         |                |                    |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | does not generat                                                         |                | ource mirror refe  | erence            |                 |        |  |  |  |  |

| bit 9            |                                                                                                                                                            | SRCEN3: Source Enable for Output #3 bit<br>1 = Current source is enabled |                |                    |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | source is disable                                                        |                |                    |                   |                 |        |  |  |  |  |

| bit 8            | SNKEN3: S                                                                                                                                                  | ink Enable for Ou                                                        | utput #3 bit   |                    |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | sink is enabled                                                          |                |                    |                   |                 |        |  |  |  |  |

| hit 7 G          |                                                                                                                                                            | sink is disabled                                                         | 3              |                    |                   |                 |        |  |  |  |  |

| bit 7-6<br>bit 5 | •                                                                                                                                                          | ented: Read as '0                                                        |                | itout #2 hit       |                   |                 |        |  |  |  |  |

| DIL O            |                                                                                                                                                            |                                                                          |                | -                  | ce from another   | source)         |        |  |  |  |  |

|                  | <ul> <li>1 = Sourcing Current Mirror mode is enabled (uses reference from another source)</li> <li>0 = Sourcing Current Mirror mode is disabled</li> </ul> |                                                                          |                |                    |                   |                 |        |  |  |  |  |

| bit 4            |                                                                                                                                                            | 12: Share Sink E                                                         | •              |                    |                   |                 |        |  |  |  |  |

|                  | <ul> <li>1 = Sinking Current Mirror mode is enabled (uses reference from another source)</li> <li>0 = Sinking Current Mirror mode is disabled</li> </ul>   |                                                                          |                |                    |                   |                 |        |  |  |  |  |

| bit 3            | •                                                                                                                                                          | N2: Generated So                                                         |                |                    |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | generates the cu<br>does not generat                                     |                |                    | erence            |                 |        |  |  |  |  |

| bit 2            | GENSNKEN                                                                                                                                                   | N2: Generated Si                                                         | nk Enable for  | Output #2 bit      |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | generates the cu<br>does not generat                                     |                |                    | erence            |                 |        |  |  |  |  |

| bit 1            | SRCEN2: S                                                                                                                                                  | ource Enable for                                                         | Output #2 bit  |                    |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | source is enable                                                         |                |                    |                   |                 |        |  |  |  |  |

| bit 0            |                                                                                                                                                            | ink Enable for Ou                                                        |                |                    |                   |                 |        |  |  |  |  |

|                  | 1 = Current                                                                                                                                                | sink is enabled<br>sink is disabled                                      |                |                    |                   |                 |        |  |  |  |  |

|                  |                                                                                                                                                            | SILIN IS UISAULEU                                                        |                |                    |                   |                 |        |  |  |  |  |

## 23.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 23.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 23.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 23.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 23.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

## 24.1 DC Characteristics

| Characteristic | VDD Range<br>(in Volts) | Temperature Range<br>(in °C) | Maximum MIPS<br>dsPIC33CH128MP508 Family |       |  |

|----------------|-------------------------|------------------------------|------------------------------------------|-------|--|

|                | (III Volts)             | (11 0)                       | Master                                   | Slave |  |

|                | 3.0V to 3.6V            | -40°C to +85°C               | 90                                       | 100   |  |

|                | 3.0V to 3.6V            | -40°C to +125°C              | 90                                       | 100   |  |

## TABLE 24-1: OPERATING MIPS vs. VOLTAGE

## TABLE 24-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                            | Symbol | Min.        | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                                    |        |             |             |      |      |

| Operating Junction Temperature Range                                                              | TJ     | -40         |             | +125 | °C   |

| Operating Ambient Temperature Range                                                               | TA     | -40         |             | +85  | °C   |

| Extended Temperature Devices                                                                      |        |             |             |      |      |

| Operating Junction Temperature Range                                                              | TJ     | -40         |             | +140 | °C   |

| Operating Ambient Temperature Range                                                               | TA     | -40         |             | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD \times (IDD - \Sigma IOH)$  | PD     | PINT + PI/O |             | W    |      |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} \times IOH) + \Sigma (VOL \times IOL)$ |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                                 | PDMAX  | (           | TJ — ΤΑ)/θ. | IA   | W    |

## TABLE 24-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                     | Symbol | Тур.  | Max. | Unit | Notes |

|----------------------------------------------------|--------|-------|------|------|-------|

| Package Thermal Resistance, 80-Pin TQFP 12x12x1 mm | θJA    | 50.67 | _    | °C/W | 1     |

| Package Thermal Resistance, 64-Pin TQFP 10x10x1 mm | θJA    | 45.7  | —    | °C/W | 1     |

| Package Thermal Resistance, 64-Pin QFN 9x9 mm      | θJA    | 18.7  | _    | °C/W | 1     |

| Package Thermal Resistance, 48-Pin TQFP 7x7 mm     | θJA    | 62.76 | _    | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN 6x6 mm     | θJA    | 27.6  | _    | °C/W | 1     |

| Package Thermal Resistance, 36-Pin UQFN 5x5 mm     | θJA    | 29.2  | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin UQFN 6x6 mm     | θJA    | 22.41 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP 5.30 mm    | θJA    | 52.84 | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

## TABLE 24-4: OPERATING VOLTAGE SPECIFICATIONS

| -            | -         | tions: 3.0V to 3.6V (unless other ature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Ind $-40^{\circ}C \le TA \le +125^{\circ}C$ for E | ustrial | ted) <sup>(1)</sup> |      |       |               |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|------|-------|---------------|

| Param<br>No. | Symbol    | Characteristic                                                                                                                       | Min.    | Тур.                | Max. | Units | Conditions    |

| Operati      | ng Voltag | e                                                                                                                                    |         |                     |      |       |               |

| DC10         | Vdd       | Supply Voltage                                                                                                                       | 3.0     | _                   | 3.6  | V     |               |

| DC12         | Vdr       | RAM Retention Voltage <sup>(2)</sup>                                                                                                 | 1.8     | _                   |      | V     |               |

| DC16         | VPOR      | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal                                                                     | _       | _                   | Vss  | V     |               |

| DC17         | SVDD      | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal                                                                  | 1.0     | _                   | _    | V/ms  | 0V-3V in 3 ms |

| BO10         | VBOR      | BOR Event on VDD Transition<br>High-to-Low <sup>(3)</sup>                                                                            | 2.68    | 2.84                | 2.99 | V     |               |