Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 23x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-UQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp202-i-2n |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33CH128MP508 FAMILY

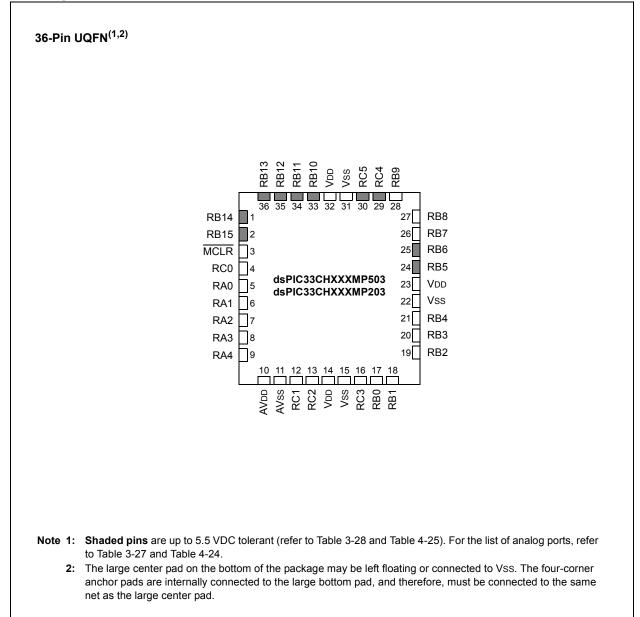

## Pin Diagrams (Continued)

| R/W-0   | U-0   | R/W-0         | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|---------|-------|---------------|--------|---------------------|-----|-------|-------|

| VAR     | —     | US1           | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15  |       |               |        |                     |     |       | bit 8 |

|         |       |               |        |                     |     |       |       |

| R/W-0   | R/W-0 | R/W-1         | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA    | SATB  | SATDW         | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7   |       |               |        |                     |     |       | bit 0 |

|         |       |               |        |                     |     |       |       |

| Legend: |       | C = Clearable | e bit  |                     |     |       |       |

## REGISTER 3-17: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit

1 = Variable exception processing is enabled

0 = Fixed exception processing is enabled

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

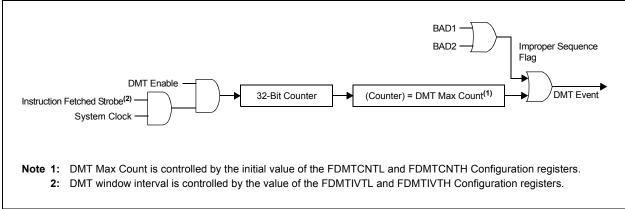

## 3.7 Deadman Timer (DMT) (Master Only)

- Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Deadman Timer (DMT)" (DS70005155) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: The Slave core does not have any DMT module; only the Master has the DMT.

The primary function of the Deadman Timer (DMT) is to interrupt the processor in the event of a software malfunction. The DMT, which works on the system clock, is a free-running instruction fetch timer, which is clocked whenever an instruction fetch occurs, until a count match occurs. Instructions are not fetched when the processor is in Sleep mode.

FIGURE 3-22: DEADMAN TIMER BLOCK DIAGRAM

DMT can be enabled in the Configuration fuse or by software in the DMTCON register by setting the ON bit. The DMT consists of a 32-bit counter with a time-out count match value, as specified by the two 16-bit Configuration Fuse registers: FDMTCNTL and FDMTCNTH.

A DMT is typically used in mission-critical and safetycritical applications, where any single failure of the software functionality and sequencing must be detected. Table 3-41 shows an overview of the DMT module.

| TABLE 3-41: | DMT MODULE OVERVIEW |

|-------------|---------------------|

|-------------|---------------------|

|             | No. of DMT<br>Modules | Identical<br>(Modules) |

|-------------|-----------------------|------------------------|

| Master Core | 1                     | No                     |

| Slave Core  | None                  | NA                     |

Figure 3-22 shows a block diagram of the Deadman Timer module.

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | —   | -   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| HC/R-0 | HC/R-0 | HC/R-0   | U-0 | U-0 | U-0 | U-0 | R-0    |

|--------|--------|----------|-----|-----|-----|-----|--------|

| BAD1   | BAD2   | DMTEVENT | —   | —   | —   | —   | WINOPN |

| bit 7  |        |          |     |     |     |     | bit 0  |

| Legend:           | HC = Hardware Clearable bit |                           |                    |  |

|-------------------|-----------------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                             |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Deadman Timer Bad STEP1<7:0> Value Detect bit                                                                                                                                                                    |

|          | 1 = Incorrect STEP1<7:0> value was detected<br>0 = Incorrect STEP1<7:0> value was not detected                                                                                                                         |

| bit 6    | BAD2: Deadman Timer Bad STEP2<7:0> Value Detect bit                                                                                                                                                                    |

|          | 1 = Incorrect STEP2<7:0> value was detected<br>0 = Incorrect STEP2<7:0> value was not detected                                                                                                                         |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                                                                                                      |

|          | <ul> <li>1 = Deadman Timer event was detected (counter expired, or bad STEP1&lt;7:0&gt; or STEP2&lt;7:0&gt; value was entered prior to counter increment)</li> <li>0 = Deadman Timer event was not detected</li> </ul> |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                                                                                                             |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                                                                                                                 |

|          | 1 = Deadman Timer clear window is open                                                                                                                                                                                 |

|          | 0 = Deadman Timer clear window is not open                                                                                                                                                                             |

|          |                                                                                                                                                                                                                        |

| U-0           | R/W-0                                                        | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |

|---------------|--------------------------------------------------------------|------------------|-------|-----------------------------------------|------------------|----------|-------|--|

| _             | EXIDE                                                        | SID11            | EID17 | EID16                                   | EID15            | EID14    | EID13 |  |

| bit 15        |                                                              |                  |       |                                         |                  |          | bit 8 |  |

|               |                                                              |                  |       |                                         |                  |          |       |  |

| R/W-0         | R/W-0                                                        | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |

| EID12         | EID11                                                        | EID10            | EID9  | EID8                                    | EID7             | EID6     | EID5  |  |

| bit 7         |                                                              |                  |       |                                         |                  |          | bit 0 |  |

|               |                                                              |                  |       |                                         |                  |          |       |  |

| Legend:       |                                                              |                  |       |                                         |                  |          |       |  |

| R = Readable  | e bit                                                        | W = Writable I   | oit   | U = Unimplem                            | nented bit, read | l as '0' |       |  |

| -n = Value at | POR                                                          | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |

|               |                                                              |                  |       |                                         |                  |          |       |  |

| bit 15        | Unimplemented: Read as '0'                                   |                  |       |                                         |                  |          |       |  |

| bit 14        | EXIDE: Extended Identifier Enable bit                        |                  |       |                                         |                  |          |       |  |

|               | <u>If MIDE = 1:</u>                                          |                  |       |                                         |                  |          |       |  |

|               | 1 = Matches only messages with Extended Identifier addresses |                  |       |                                         |                  |          |       |  |

|               | 0 = Matches only messages with Standard Identifier addresses |                  |       |                                         |                  |          |       |  |

### REGISTER 3-153: C1FLTOBJxH: CAN FILTER OBJECT REGISTER x HIGH (x = 0 TO 15)

| bit 13 | SID11: Standard Identifier Filter bit |

|--------|---------------------------------------|

|        |                                       |

| bit 12-0 | EID<17:5>: Extended Identifier Filter bits                                              |  |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          | In DeviceNet <sup>™</sup> mode, these are the filter bits for the first two data bytes. |  |  |  |  |  |  |

### **REGISTER 3-154:** C1FLTOBJxL: CAN FILTER OBJECT REGISTER x LOW (x = 0 TO 15)

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|

| EID4                              | EID3  | EID2             | EID1  | EID0                                    | SID10 | SID9  | SID8  |  |

| bit 15                            |       |                  |       |                                         |       |       | bit 8 |  |

|                                   |       |                  |       |                                         |       |       |       |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

| SID7                              | SID6  | SID5             | SID4  | SID3                                    | SID2  | SID1  | SID0  |  |

| bit 7                             |       |                  |       |                                         |       |       | bit 0 |  |

|                                   |       |                  |       |                                         |       |       |       |  |

| Legend:                           |       |                  |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at                     | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-11 EID<4:0>: Extended Identifier Filter bits

In DeviceNet<sup>™</sup> mode, these are the filter bits for the first two data bytes.

bit 10-0 SID<10:0>: Standard Identifier Filter bits

## 3.10.2 PTG CONTROL/STATUS REGISTERS

## REGISTER 3-183: PTGCST: PTG CONTROL/STATUS LOW REGISTER

| R/W-0                                | U-0                                             | R/W-0                                    | R/W-0                     | U-0              | HC/R/W-0              | R/W-0                  | R/W-0                  |

|--------------------------------------|-------------------------------------------------|------------------------------------------|---------------------------|------------------|-----------------------|------------------------|------------------------|

| PTGEN                                | —                                               | PTGSIDL                                  | PTGTOGL                   | _                | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS                |

| bit 15                               |                                                 |                                          |                           |                  |                       | <u> </u>               | bit 8                  |

|                                      |                                                 |                                          |                           |                  |                       |                        |                        |

| HC/R/W-0                             | HS/R/W-0                                        | HS/HC/R/W-0                              | U-0                       | U-0              | U-0                   | R/W-0                  | R/W-0                  |

| PTGSTRT                              | PTGWDTO                                         | PTGBUSY                                  |                           | _                | _                     | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |

| bit 7                                |                                                 |                                          |                           |                  |                       |                        | bit 0                  |

|                                      |                                                 |                                          |                           |                  |                       |                        |                        |

| Legend:                              |                                                 | HC = Hardware                            | Clearable bit             | HS = Hardwa      | are Settable bit      |                        |                        |

| R = Readal                           | ble bit                                         | W = Writable bit                         |                           | U = Unimple      | mented bit, read      | 1 as '0'               |                        |

| -n = Value a                         |                                                 | '1' = Bit is set                         |                           | '0' = Bit is cle |                       | x = Bit is unkno       | מאור                   |

|                                      |                                                 | I – Dit is set                           |                           |                  |                       |                        | 50011                  |

| bit 15                               | PTGEN: PTG                                      | · Enable bit                             |                           |                  |                       |                        |                        |

| DIL 15                               | 1 = PTG is er                                   |                                          |                           |                  |                       |                        |                        |

|                                      | 0 = PTG is di                                   |                                          |                           |                  |                       |                        |                        |

| bit 14                               |                                                 | ted: Read as '0'                         |                           |                  |                       |                        |                        |

| bit 13                               | -                                               | G Freeze in Debu                         | ua Mode bit               |                  |                       |                        |                        |

|                                      |                                                 | G operation when                         | •                         |                  |                       |                        |                        |

|                                      |                                                 | ation continues w                        |                           | dle              |                       |                        |                        |

| bit 12                               | PTGTOGL: P                                      | TG Toggle Trigge                         | r Output bit              |                  |                       |                        |                        |

|                                      | 1 = Toggles s                                   | tate of TRIG output                      | ut for each exe           | cution of PTG    | TRIG                  |                        |                        |

|                                      | 0 = Generate                                    | s a single TRIG p                        | ulse for each e           | xecution of PI   | GTRIG                 |                        |                        |

| bit 11                               | Unimplemen                                      | ted: Read as '0'                         |                           |                  |                       |                        |                        |

| bit 10                               | PTGSWT: PT                                      | G Software Trigge                        | er bit <sup>(2)</sup>     |                  |                       |                        |                        |

|                                      |                                                 | tate of TRIG outpu<br>s a single TRIG pu |                           |                  |                       |                        |                        |

| bit 9                                | PTGSSEN: P                                      | TG Single-Step C                         | ommand bit <sup>(3)</sup> |                  |                       |                        |                        |

|                                      |                                                 | single step when ir                      |                           |                  |                       |                        |                        |

| bit 8                                |                                                 | G Counter/Timer \                        | /isibility bit            |                  |                       |                        |                        |

| Sit 0                                |                                                 | the PTGSDLIM,                            |                           | PTGTxI IM r      | egisters returns      | s the current va       | alues of their         |

|                                      | correspo                                        | nding Counter/Tim<br>the PTGSDLIM, P     | ner registers (F          | TGSDLIM, P       | GCxLIM and P          | TGTxLIM)               |                        |

| bit 7                                | -                                               | TG Start Sequenc                         |                           | 0                |                       |                        | 0                      |

|                                      |                                                 | sequentially execu                       |                           | nds (Continuo    | us mode)              |                        |                        |

|                                      |                                                 | ecuting the comma                        |                           |                  | ,                     |                        |                        |

| bit 6                                | PTGWDTO: PTG Watchdog Timer Time-out Status bit |                                          |                           |                  |                       |                        |                        |

| 1 = PTG Watchdog Timer has timed out |                                                 |                                          |                           |                  |                       |                        |                        |

|                                      | 0 = PTG Wate                                    | chdog Timer has r                        | ot timed out              |                  |                       |                        |                        |

| bit 5                                | PTGBUSY: P                                      | TG State Machine                         | e Busy bit                |                  |                       |                        |                        |

|                                      | 1 = PTG is r<br>PTGDIV                          | running on the se<br><4:0>               | elected clock             | source; no SF    | R writes are a        | allowed to PTG         | CLK<2:0> or            |

|                                      | 0 = PTG stat                                    | e machine is not r                       | unning                    |                  |                       |                        |                        |

| bit 4-2                              | Unimplemen                                      | ted: Read as '0'                         |                           |                  |                       |                        |                        |

| Note 1:                              | These bits appl                                 | y to the PTGWHI a                        | nd PTGWLO CC              | mmands only.     |                       |                        |                        |

|                                      |                                                 | y<br>used with the pmg                   |                           |                  |                       |                        |                        |

- 2: This bit is only used with the PTGCTRL Step command software trigger option.

- 3: The PTGSSEN bit may only be written when in Debug mode.

## 4.1.5 PROGRAMMER'S MODEL

The programmer's model for the dsPIC33CH128MP508S1 family is shown in Figure 4-2. All registers in the programmer's model are memorymapped and can be manipulated directly by instructions. Table 4-1 lists a description of each register. In addition to the registers contained in the programmer's model, the dsPIC33CH128MP508S1 devices contain control registers for Modulo Addressing, Bit-Reversed Addressing and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Figure 4-3.

| Register(s) Name                                  | Description                                                   |

|---------------------------------------------------|---------------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>                     | Working Register Array                                        |

| W0 through W14 <sup>(1)</sup>                     | Alternate 1 Working Register Array                            |

| W0 through W14 <sup>(1)</sup>                     | Alternate 2 Working Register Array                            |

| W0 through W14 <sup>(1)</sup>                     | Alternate 3 Working Register Array                            |

| W0 through W14 <sup>(1)</sup>                     | Alternate 4 Working Register Array                            |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators (Additional 4 Alternate Accumulators) |

| PC                                                | 23-Bit Program Counter                                        |

| SR                                                | ALU and DSP Engine STATUS Register                            |

| SPLIM                                             | Stack Pointer Limit Value Register                            |

| TBLPAG                                            | Table Memory Page Address Register                            |

| DSRPAG                                            | Extended Data Space (EDS) Read Page Register                  |

| RCOUNT                                            | REPEAT Loop Counter Register                                  |

| DCOUNT                                            | DO Loop Counter Register                                      |

| DOSTARTH <sup>(2)</sup> , DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)                 |

| DOENDH, DOENDL                                    | DO Loop End Address Register (High and Low)                   |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits     |

Note 1: Memory-mapped W0 through W14 represent the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

| TABLE 4-23: | SLAVE INTERRUPT PRIORITY REGISTERS (CONTINUED) |

|-------------|------------------------------------------------|

|-------------|------------------------------------------------|

|          | -      |          |          |          |        |          |          |          |       |           |           |           |       |           |           |           |

|----------|--------|----------|----------|----------|--------|----------|----------|----------|-------|-----------|-----------|-----------|-------|-----------|-----------|-----------|

| Register | Bit 15 | Bit 14   | Bit 13   | Bit 12   | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6     | Bit 5     | Bit 4     | Bit 3 | Bit 2     | Bit 1     | Bit 0     |

| IPC36    | _      | -        | —        | —        |        | _        | -        | —        | —     | MSTBRKIP2 | MSTBRKIP1 | MSTBRKIP0 | _     | —         | -         | —         |

| IPC37    | _      | —        | _        | _        | _      | _        | _        | —        | —     | —         | —         | —         | _     | —         | —         | _         |

| IPC38    | -      | _        | _        | _        | _      | _        | _        | _        | _     | _         | _         | _         |       | _         | _         | _         |

| IPC39    | _      |          | _        | _        | -      | _        | _        | _        | —     | _         | —         | —         |       | MCLKFIP2  | MCLKFIP1  | MCLKFIP0  |

| IPC40    | _      |          | _        | _        | -      | _        | _        | _        | —     | ADC1IP2   | ADC1IP1   | ADC1IP0   | -     | ADC0IP2   | ADC0IP1   | ADC0IP0   |

| IPC41    | _      |          | —        | _        |        | _        |          | —        | —     | —         | —         | —         | -     | —         |           | —         |

| IPC42    | _      | PEVTCIP2 | PEVTCIP1 | PEVTCIP0 |        | PEVTBIP2 | PEVTBIP1 | PEVTBIP0 | —     | PEVTAIP2  | PEVTAIP1  | PEVTAIP0  | _     | ADFIFOIP2 | ADFIFOIP1 | ADFIFOIP0 |

| IPC43    | _      | CLC3PIP2 | CLC3PIP1 | CLC3PIP0 |        | PEVTFIP2 | PEVTFIP1 | PEVTFIP0 | —     | PEVTEIP2  | PEVTEIP1  | PEVTEIP0  | _     | PEVTDIP2  | PEVTDIP1  | PEVTDIP0  |

| IPC44    | _      | CLC3NIP2 | CLC3NIP1 | CLC3NIP0 |        | CLC2NIP2 | CLC2NIP1 | CLC2NIP0 | —     | CLC1NIP2  | CLC1NIP1  | CLC1NIP0  | _     | CLC4PIP2  | CLC4PIP1  | CLC4PIP0  |

| IPC45    | _      |          | —        | _        |        | _        |          | —        | —     | —         | —         | —         | -     | CLC4NIP2  | CLC4NIP1  | CLC4NIP0  |

| IPC46    | _      | _        | _        | _        | -      | _        | _        | _        | —     | _         | _         | _         |       | _         | _         | —         |

| IPC47    | _      |          | —        | _        |        | _        |          | —        | —     | U1EVTIP2  | U1EVTIP1  | U1EVTIP0  | _     | —         |           | —         |

| R/W-1         | R/W-0                                                                                      | R/W-0                                     | U-0          | U-0               | U-0              | U-0             | U-0    |  |  |  |

|---------------|--------------------------------------------------------------------------------------------|-------------------------------------------|--------------|-------------------|------------------|-----------------|--------|--|--|--|

| GIE           | DISI                                                                                       | SWTRAP                                    |              | —                 | _                | —               | —      |  |  |  |

| bit 15        |                                                                                            |                                           |              |                   |                  |                 | bit 8  |  |  |  |

|               |                                                                                            |                                           |              |                   |                  |                 |        |  |  |  |

| U-0           | U-0                                                                                        | U-0                                       | U-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|               |                                                                                            |                                           |              | INT3EP            | INT2EP           | INT1EP          | INT0EP |  |  |  |

| bit 7         |                                                                                            |                                           |              |                   |                  |                 | bit 0  |  |  |  |

| Legend:       |                                                                                            |                                           |              |                   |                  |                 |        |  |  |  |

| R = Readabl   | e bit                                                                                      | W = Writable b                            | oit          | U = Unimpler      | nented bit, read | as '0'          |        |  |  |  |

| -n = Value at |                                                                                            | '1' = Bit is set                          |              | '0' = Bit is cle  |                  | x = Bit is unkr | nown   |  |  |  |

|               |                                                                                            |                                           |              | 0 2.1.0 0.0       |                  |                 |        |  |  |  |

| bit 15        | GIE: Global                                                                                | Interrupt Enable                          | bit          |                   |                  |                 |        |  |  |  |

|               |                                                                                            | s and associated                          |              |                   |                  |                 |        |  |  |  |

|               | 0 = Interrupt                                                                              | ts are disabled, b                        | ut traps are | still enabled     |                  |                 |        |  |  |  |

| bit 14        |                                                                                            | Instruction Status                        |              |                   |                  |                 |        |  |  |  |

|               |                                                                                            | struction is active<br>struction is not a |              |                   |                  |                 |        |  |  |  |

| bit 13        |                                                                                            | Software Trap Sta                         |              |                   |                  |                 |        |  |  |  |

|               |                                                                                            | e trap is enabled                         |              |                   |                  |                 |        |  |  |  |

|               |                                                                                            | e trap is disabled                        |              |                   |                  |                 |        |  |  |  |

| bit 12-4      | Unimpleme                                                                                  | nted: Read as '0                          | )'           |                   |                  |                 |        |  |  |  |

| bit 3         | INT3EP: Ext                                                                                | ternal Interrupt 3                        | Edge Detec   | t Polarity Select | t bit            |                 |        |  |  |  |

|               |                                                                                            | on negative edg                           |              |                   |                  |                 |        |  |  |  |

| <b>h</b> # 0  | 0 = Interrupt on positive edge                                                             |                                           |              |                   |                  |                 |        |  |  |  |

| bit 2         | INT2EP: External Interrupt 2 Edge Detect Polarity Select bit                               |                                           |              |                   |                  |                 |        |  |  |  |

|               | <ul> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul> |                                           |              |                   |                  |                 |        |  |  |  |

| bit 1         | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit                               |                                           |              |                   |                  |                 |        |  |  |  |

|               | 1 = Interrupt on negative edge                                                             |                                           |              |                   |                  |                 |        |  |  |  |

|               | 0 = Interrupt on positive edge                                                             |                                           |              |                   |                  |                 |        |  |  |  |

| bit 0         | INT0EP: External Interrupt 0 Edge Detect Polarity Select bit                               |                                           |              |                   |                  |                 |        |  |  |  |

|               |                                                                                            | t on negative edge<br>t on positive edge  |              |                   |                  |                 |        |  |  |  |

|               |                                                                                            | i on positive edge                        | -            |                   |                  |                 |        |  |  |  |

### REGISTER 4-19: INTCON2: SLAVE INTERRUPT CONTROL REGISTER 2

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —      | —   | RP175R5 <sup>(1)</sup> | RP175R4 <sup>(1)</sup> | RP175R3 <sup>(1)</sup> | RP175R2 <sup>(1)</sup> | RP175R1 <sup>(1)</sup> | RP175R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —     | —   | RP174R5 <sup>(1)</sup> | RP174R4 <sup>(1)</sup> | RP174R3 <sup>(1)</sup> | RP174R2 <sup>(1)</sup> | RP174R1 <sup>(1)</sup> | RP174R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

| bit 13-8 | <b>RP175R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP175 Output Pin bits <sup>(1)</sup> |

|----------|------------------------------------------------------------------------------------------------------------|

|          | (see Table 4-31 for peripheral function numbers)                                                           |

| bit 7-6  | Unimplemented: Read as '0'                                                                                 |

bit 5-0 **RP174R<5:0>:** Peripheral Output Function is Assigned to S1RP174 Output Pin bits<sup>(1)</sup> (see Table 4-31 for peripheral function numbers)

Note 1: These are virtual output ports.

'1' = Bit is set

| U-0                               | U-0   | U-0   | R/W-0  | R/W-0                              | R/W-0  | R/W-0 | R/W-0 |  |

|-----------------------------------|-------|-------|--------|------------------------------------|--------|-------|-------|--|

| _                                 | _     | —     | EISEL2 | EISEL1                             | EISEL0 | RES1  | RES2  |  |

| bit 15                            |       |       |        | ·                                  |        | ·     | bit   |  |

|                                   |       |       |        |                                    |        |       |       |  |

| U-0                               | R/W-0 | R/W-0 | R/W-0  | R/W-0                              | R/W-0  | R/W-0 | R/W-0 |  |

| _                                 | ADCS6 | ADCS5 | ADCS4  | ADCS3                              | ADCS2  | ADCS1 | ADCS0 |  |

| bit 7                             |       |       |        |                                    |        |       | bit   |  |

|                                   |       |       |        |                                    |        |       |       |  |

| Legend:                           |       |       |        |                                    |        |       |       |  |

| R = Readable bit W = Writable bit |       |       | bit    | U = Unimplemented bit, read as '0' |        |       |       |  |

'0' = Bit is cleared

### **REGISTER 4-94:** ADCORExH: DEDICATED ADC CORE x CONTROL REGISTER HIGH (x = 0 TO 1)

### bit 15-13 Unimplemented: Read as '0'

-n = Value at POR

| DIL 10-1 | 5 Uninplemented. Read as 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12-1 | 0 EISEL<2:0>: ADC Core x Early Interrupt Time Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | 111 = Early interrupt is set and an interrupt is generated 8 TADCORE clocks prior to when the data is ready<br>110 = Early interrupt is set and an interrupt is generated 7 TADCORE clocks prior to when the data is ready<br>101 = Early interrupt is set and an interrupt is generated 6 TADCORE clocks prior to when the data is ready<br>100 = Early interrupt is set and an interrupt is generated 5 TADCORE clocks prior to when the data is ready<br>011 = Early interrupt is set and an interrupt is generated 5 TADCORE clocks prior to when the data is ready<br>011 = Early interrupt is set and an interrupt is generated 4 TADCORE clocks prior to when the data is ready<br>010 = Early interrupt is set and an interrupt is generated 3 TADCORE clocks prior to when the data is ready<br>010 = Early interrupt is set and an interrupt is generated 2 TADCORE clocks prior to when the data is ready<br>001 = Early interrupt is set and an interrupt is generated 1 TADCORE clocks prior to when the data is ready<br>000 = Early interrupt is set and an interrupt is generated 1 TADCORE clocks prior to when the data is ready |

| bit 9-8  | RES<1:0>: ADC Core x Resolution Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          | 11 = 12-bit resolution<br>10 = 10-bit resolution<br>01 = 8-bit resolution <sup>(1)</sup><br>00 = 6-bit resolution <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 7    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 6-0  | ADCS<6:0>: ADC Core x Input Clock Divider bits<br>These bits determine the number of Source Clock Periods (TCORESRC) for one Core Clock Period (TADCORE).<br>1111111 = 254 Source Clock Periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | 0000011 = 6 Source Clock Periods<br>0000010 = 4 Source Clock Periods<br>0000001 = 2 Source Clock Periods<br>0000000 = 2 Source Clock Periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

**Note 1:** For the 6-bit ADC core resolution (RES<1:0> = 00), the EISEL<2:0> bits settings, from '100' to '111', are not valid and should not be used. For the 8-bit ADC core resolution (RES<1:0> = 01), the EISEL<2:0> bits settings, '110' and '111', are not valid and should not be used.

x = Bit is unknown

## REGISTER 4-99: ADEISTATL: ADC EARLY INTERRUPT STATUS REGISTER LOW

| Legend: |       |       |        |        |       |       |       |

|---------|-------|-------|--------|--------|-------|-------|-------|

| bit 7   |       |       |        |        |       |       | bit 0 |

|         |       |       | EISTA  | T<7:0> |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       |        |        |       |       | bit 0 |

| bit 15  |       |       |        |        |       |       | bit 8 |

|         |       |       | EISTAT | <15:8> |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

| Logona.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 EISTAT<15:0>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

### REGISTER 4-100: ADEISTATH: ADC EARLY INTERRUPT STATUS REGISTER HIGH

| U-0           | U-0   | U-0              | U-0   | U-0                                     | U-0   | U-0   | U-0   |  |

|---------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|

| —             | —     | —                | —     | _                                       | —     | —     | —     |  |

| bit 15        |       |                  |       |                                         |       |       | bit 8 |  |

|               |       |                  |       |                                         |       |       |       |  |

| U-0           | U-0   | U-0              | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|               | —     | —                |       | EISTAT<20:16>                           |       |       |       |  |

| bit 7         |       |                  |       |                                         |       |       | bit 0 |  |

|               |       |                  |       |                                         |       |       |       |  |

| Legend:       |       |                  |       |                                         |       |       |       |  |

| R = Readable  | e bit | W = Writable I   | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 EISTAT<20:16>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

# REGISTER 4-106: ADTRIGnL/ADTRIGnH: ADC CHANNEL TRIGGER n(x) SELECTION REGISTERS LOW AND HIGH (x = 0 TO 19; n = 0 TO 4)

|        | — | TRGSRC(x+1)4 | TRGSRC(x+1)3 | TRGSRC(x+1)2 | TRGSRC(x+1)1 | TRGSRC(x+1)0 |

|--------|---|--------------|--------------|--------------|--------------|--------------|

| bit 15 |   | •            |              |              |              | bit 8        |

| U-0   | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-------|-----|-----|----------|----------|----------|----------|----------|

|       | —   | —   | TRGSRCx4 | TRGSRCx3 | TRGSRCx2 | TRGSRCx1 | TRGSRCx0 |

| bit 7 |     |     |          |          |          |          | bit 0    |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 15-13 Unimplemented: Read as '0'

bit 12-8 TRGSRC(x+1)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits (TRGSRC1 to TRGSRC19 – Odd) 11111 = ADTRG31 (PPS input) 11110 = Master PTG 11101 = Slave CLC1 11100 = Master CLC1 11011 = Reserved 11010 = Reserved 11001 = Master PWM3 Trigger 2 11000 = Master PWM1 Trigger 2 10111 = Slave SCCP4 PWM/IC interrupt 10110 = Slave SCCP3 PWM/IC interrupt 10101 = Slave SCCP2 PWM/IC interrupt 10100 = Slave SCCP1 PWM/IC interrupt 10011 = Reserved 10010 = Reserved 10001 = Reserved 10000 = Reserved 01111 = Slave PWM8 Trigger 1 01110 = Slave PWM7 Trigger 1 01101 = Slave PWM6 Trigger 1 01100 = Slave PWM5 Trigger 1 01011 = Slave PWM4 Trigger 2 01010 = Slave PWM4 Trigger 1 01001 = Slave PWM3 Trigger 2 01000 = Slave PWM3 Trigger 1 00111 = Slave PWM2 Trigger 2 00110 = Slave PWM2 Trigger 1 00101 = Slave PWM1 Trigger 2 00100 = Slave PWM1 Trigger 1 00011 = Reserved 00010 = Level software trigger 00001 = Common software trigger 00000 = No trigger is enabled

### bit 7-5 Unimplemented: Read as '0'

# REGISTER 9-9: LOGCONY: COMBINATORIAL PWM LOGIC CONTROL REGISTER y<sup>(2)</sup> (CONTINUED)

| bit 6   | <b>S2yPOL:</b> Combinatorial PWM Logic Source #2 Polarity bit<br>1 = Input is inverted<br>0 = Input is positive logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <pre>PWMLFy&lt;1:0&gt;: Combinatorial PWM Logic Function Selection bits<br/>11 = Reserved<br/>10 = PWMS1 ^ PWMS2 (XOR)<br/>01 = PWMS1 &amp; PWMS2 (AND)<br/>00 = PWMS1   PWMS2 (OR)</pre>                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 2-0 | <b>PWMLFyD&lt;2:0&gt;:</b> Combinatorial PWM Logic Destination Selection bits<br>111 = Logic function is assigned to the PWM8H or PWM8L pin<br>110 = Logic function is assigned to the PWM7H or PWM7L pin<br>101 = Logic function is assigned to the PWM6H or PWM6L pin<br>100 = Logic function is assigned to the PWM5H or PWM5Lpin<br>011 = Logic function is assigned to the PWM4H or PWM4Lpin<br>010 = Logic function is assigned to the PWM3H or PWM3Lpin<br>001 = Logic function is assigned to the PWM2H or PWM3Lpin<br>000 = No assignment, combinatorial PWM logic function is disabled |

| N       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

- **Note 1:** Logic function input will be connected to '0' if the PWM channel is not present.

- 2: 'y' denotes a common instance (A-F).

### REGISTER 9-13: PGxCONH: PWM GENERATOR x CONTROL REGISTER HIGH (CONTINUED)

- bit 6 **TRGMOD:** PWM Generator Trigger Mode Selection bit 1 = PWM Generator operates in Retriggerable mode 0 = PWM Generator operates in Single Trigger mode

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 SOCS<3:0>: Start-of-Cycle Selection bits<sup>(1,2,3)</sup> 1111 = TRIG bit or PCI Sync function only (no hardware trigger source is selected) 1110-0101 = Reserved 0100 = PWM4(8) PG1 or PG5 trigger output selected by PGTRGSEL<2:0> (PGxEVT<2:0>) 0011 = PWM3(7) PG1 or PG5 trigger output selected by PGTRGSEL<2:0> (PGxEVT<2:0>) 0010 = PWM2(6) PG1 or PG5 trigger output selected by PGTRGSEL<2:0> (PGxEVT<2:0>) 0001 = PWM1(5) PG1 or PG5 trigger output selected by PGTRGSEL<2:0> (PGxEVT<2:0>) 0001 = PWM1(5) PG1 or PG5 trigger output selected by PGTRGSEL<2:0> (PGxEVT<2:0>) 0000 = Local EOC – PWM Generator is self-triggered

- **Note 1:** The PCI selected Sync signal is always available to be OR'd with the selected SOC signal per the SOCS<3:0> bits if the PCI Sync function is enabled.

- 2: The source selected by the SOCS<3:0> bits MUST operate from the same clock source as the local PWM Generator. If not, the source must be routed through the PCI Sync logic so the trigger signal may be synchronized to the PWM Generator clock domain.

- **3:** PWM Generators are grouped into groups of four: PG1-PG4 and PG5-PG8, if available. Any generator within a group of four may be used to trigger another generator within the same group.

# dsPIC33CH128MP508 FAMILY

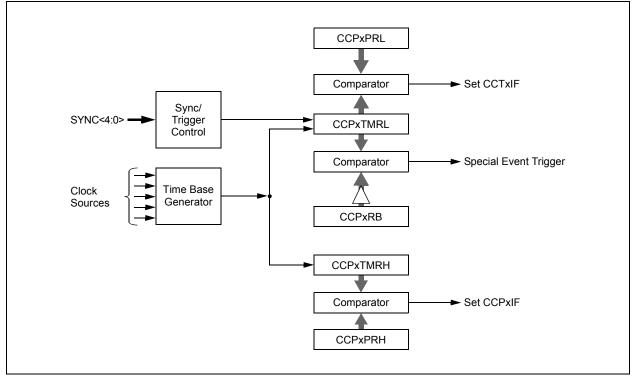

## FIGURE 10-3: DUAL 16-BIT TIMER MODE

## REGISTER 12-19: INDXxHLDL: INDEX x COUNTER HOLD REGISTER LOW

| -                                 |       |                  |                                    |                   |       |                 |       |

|-----------------------------------|-------|------------------|------------------------------------|-------------------|-------|-----------------|-------|

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  | INDXF                              | ILD<15:8>         |       |                 |       |

| bit 15                            |       |                  |                                    |                   |       |                 | bit 8 |

|                                   |       |                  |                                    |                   |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  | INDXI                              | HLD<7:0>          |       |                 |       |

| bit 7                             |       |                  |                                    |                   |       |                 | bit 0 |

|                                   |       |                  |                                    |                   |       |                 |       |

| Legend:                           |       |                  |                                    |                   |       |                 |       |

| R = Readable bit W = Writable bit |       | t                | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| -n = Value at POR                 |       | '1' = Bit is set |                                    | '0' = Bit is clea | ared  | x = Bit is unkr | iown  |

|                                   |       |                  |                                    |                   |       |                 |       |

bit 15-0 INDXHLD<15:0>: Hold for Reading/Writing Index x Counter Register (INDXCNT) bits

## REGISTER 12-20: INDXxHLDH: INDEX x COUNTER HOLD REGISTER HIGH

| R/W-0                             | R/W-0  | R/W-0            | R/W-0                              | R/W-0             | R/W-0          | R/W-0           | R/W-0  |

|-----------------------------------|--------|------------------|------------------------------------|-------------------|----------------|-----------------|--------|

|                                   |        |                  | INDXH                              | LD<31:24>         |                |                 |        |

| bit 15                            |        |                  |                                    |                   |                |                 | bit 8  |

|                                   | 5444.0 | <b>D</b> #44.0   | 5444.0                             | 5444.0            | <b>D</b> 444 o | 54440           | 5444.0 |

| R/W-0                             | R/W-0  | R/W-0            | R/W-0                              | R/W-0             | R/W-0          | R/W-0           | R/W-0  |

|                                   |        |                  | INDXH                              | LD<23:16>         |                |                 |        |

| bit 7                             |        |                  |                                    |                   |                |                 | bit 0  |

| Legend:                           |        |                  |                                    |                   |                |                 |        |

| R = Readable bit W = Writable bit |        | bit              | U = Unimplemented bit, read as '0' |                   |                |                 |        |

| -n = Value at POR                 |        | '1' = Bit is set |                                    | '0' = Bit is clea | ared           | x = Bit is unkr | nown   |

bit 15-0 INDXHLD<31:16>: Hold for Reading/Writing Index x Counter Register (INDXCNT) bits

## **REGISTER 21-14: FDEVOPT CONFIGURATION REGISTER**

| U-1                                                                       | U-1                                                                                                                                                                       | U-1                                                                                           | U-1           | U-1                                | U-1    | U-1 | U-1    |  |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------|------------------------------------|--------|-----|--------|--|

| _                                                                         | —                                                                                                                                                                         | —                                                                                             |               | —                                  | —      |     | —      |  |

| bit 23 b                                                                  |                                                                                                                                                                           |                                                                                               |               |                                    |        |     | bit 16 |  |

| ·                                                                         |                                                                                                                                                                           |                                                                                               |               |                                    |        |     |        |  |

| U-1                                                                       | U-1                                                                                                                                                                       | R/PO-1                                                                                        | U-1           | U-1                                | R/PO-1 | r-1 | r-1    |  |

|                                                                           | —                                                                                                                                                                         | SPI2PIN <sup>(1)</sup>                                                                        |               |                                    | SMBEN  |     | _      |  |

| bit 15                                                                    | bit 15 bit                                                                                                                                                                |                                                                                               |               |                                    |        |     |        |  |

|                                                                           |                                                                                                                                                                           |                                                                                               |               |                                    |        |     |        |  |

| r-1                                                                       | U-1                                                                                                                                                                       | U-1                                                                                           | R/PO-1        | R/PO-1                             | r-1    | U-1 | U-1    |  |

|                                                                           | —                                                                                                                                                                         | —                                                                                             | ALTI2C2       | ALTI2C1                            | —      | —   | —      |  |

| bit 7                                                                     |                                                                                                                                                                           |                                                                                               |               |                                    |        |     | bit 0  |  |

|                                                                           |                                                                                                                                                                           |                                                                                               |               |                                    |        |     | 1      |  |

| Legend:                                                                   |                                                                                                                                                                           | PO = Prograr                                                                                  | n Once bit    | r = Reserved                       |        |     |        |  |

| R = Readal                                                                | ole bit                                                                                                                                                                   | W = Writable                                                                                  | bit           | U = Unimplemented bit, read as '0' |        |     |        |  |