#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit Dual-Core                                                                 |

| Speed                      | 180MHz, 200MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 88KB (88K x 8)                                                                   |

| Program Memory Type        | FLASH, PRAM                                                                      |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 20K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 23x12b; D/A 4x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp202t-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33CH128MP508 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "dsPIC33E Enhanced CPU" (DS70005158)

- "dsPIC33E/PIC24E Program Memory" (DS70000613)

- "Data Memory" (DS70595)

- "Dual Partition Flash Program Memory" (DS70005156)

- "Flash Programming" (DS70609)

- "Reset" (DS70602)

- "Interrupts" (DS70000600)

- "I/O Ports with Edge Detect" (DS70005322)

- "Deadman Timer" (DS70005155)

- "CAN Flexible Data-Rate (FD) Protocol Module" (DS70005340)

- "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (DS70005213)

- "Peripheral Trigger Generator (PTG)" (DS70000669)

- "Programmable Gain Amplifier (PGA)" (DS70005146)

- "Master Slave Interface (MSI) Module" (DS70005278)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "Oscillator Module with High-Speed PLL" (DS70005255)

- "Timer1 Module" (DS70005279)

- "Direct Memory Access Controller (DMA)" (DS39742)

- "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS33035)

- "High-Resolution PWM with Fine Edge Placement" (DS70005320)

- "Serial Peripheral Interface (SPI) with Audio Codec Support" (DS70005136)

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70000195)

- "Multiprotocol Universal Asynchronous Receiver Transmitter (UART) Module" (DS70005288)

- "Single-Edge Nibble Transmission (SENT) Module" (DS70005145)

- "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS30009729)

- "Configurable Logic Cell (CLC)" (DS70005298)

- "Quadrature Encoder Interface (QEI)" (DS70000601)

- "High-Speed Analog Comparator Module" (DS70005280)

- "Current Bias Generator (CBG)" (DS70005253)

- "Dual Watchdog Timer" (DS70005250)

- "Programming and Diagnostics" (DS70608)

- "CodeGuard™ Security" (DS70634)

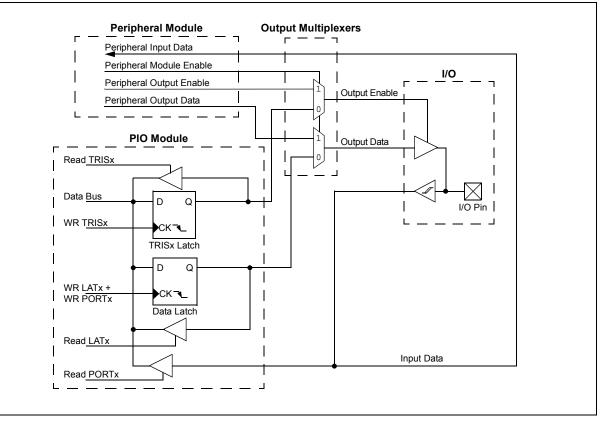

#### FIGURE 3-19: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP53R5 | RP53R4 | RP53R3 | RP53R2 | RP53R1 | RP53R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP52R5 | RP52R4 | RP52R3 | RP52R2 | RP52R1 | RP52R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

#### REGISTER 3-78: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP53&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP53 Output Pin bits (see Table 3-33 for peripheral function numbers)  |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP52R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP52 Output Pin bits (see Table 3-33 for peripheral function numbers) |

#### REGISTER 3-79: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------|--------|

| —       | —   | RP55R5 | RP55R4 | RP55R3 | RP55R2 | RP55R1 | RP55R0 |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP54R5 | RP54R4 | RP54R3 | RP54R2 | RP54R1 | RP54R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

|         |     |        |        |        |        |        |        |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 **RP55R<5:0>:** Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 3-33 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP54R<5:0>:** Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 3-33 for peripheral function numbers)

#### **REGISTER 3-110:** C1TBCH: CAN TIME BASE COUNTER REGISTER HIGH<sup>(1,2)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-----------------|-----------|-------|

|                 |       |                  | TBC<  | 31:24>                                  |                 |           |       |

| bit 15          |       |                  |       |                                         |                 |           | bit 8 |

|                 |       |                  |       |                                         |                 |           |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |

|                 |       |                  | TBC<  | 23:16>                                  |                 |           |       |

| bit 7           |       |                  |       |                                         |                 |           | bit 0 |

|                 |       |                  |       |                                         |                 |           |       |

| Legend:         |       |                  |       |                                         |                 |           |       |

| R = Readable    | bit   | W = Writable bit |       | U = Unimplen                            | nented bit, rea | ad as 'O' |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                 |           | nown  |

bit 15-0 **TBC<31:16>** CAN Time Base Counter bits

This is a free-running timer that increments every TBCPREx clock when TBCEN is set.

**Note 1:** The Time Base Counter (TBC) will be stopped and reset when TBCEN = 0 to save power.

2: The TBC prescaler count will be reset on any write to C1TBCH/L (TBCPREx will be unaffected).

#### **REGISTER 3-111:** C1TBCL: CAN TIME BASE COUNTER REGISTER LOW<sup>(1,2)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |

|-----------------|-------|------------------|-------|-----------------------------------------|-----------------|----------|-------|--|

|                 |       |                  | TBC·  | <15:8>                                  |                 |          |       |  |

| bit 15          |       |                  |       |                                         |                 |          | bit 8 |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |

|                 |       |                  | ТВС   | <7:0>                                   |                 |          |       |  |

| bit 7           |       |                  |       |                                         |                 |          | bit 0 |  |

|                 |       |                  |       |                                         |                 |          |       |  |

| Legend:         |       |                  |       |                                         |                 |          |       |  |

| R = Readable    | bit   | W = Writable bit |       | U = Unimplem                            | nented bit, rea | d as '0' |       |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |

bit 15-0 TBC<15:0> CAN Time Base Counter bits

This is a free-running timer that increments every TBCPREx clock when TBCEN is set.

**Note 1:** The TBC will be stopped and reset when TBCEN = 0 to save power.

2: The TBC prescaler count will be reset on any write to C1TBCH/L (TBCPREx will be unaffected).

#### REGISTER 3-158: ADCON1H: ADC CONTROL REGISTER 1 HIGH

| U-0                               | U-0                                                                                                                                      | U-0              | U-0            | U-0               | U-0              | U-0             | U-0   |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-------------------|------------------|-----------------|-------|

| —                                 | —                                                                                                                                        | —                | —              | —                 | —                | —               | —     |

| bit 15                            |                                                                                                                                          |                  |                |                   |                  |                 | bit 8 |

|                                   |                                                                                                                                          |                  |                |                   |                  |                 |       |

| R/W-0                             | R/W-1                                                                                                                                    | R/W-1            | U-0            | U-0               | U-0              | U-0             | U-0   |

| FORM                              | SHRRES1                                                                                                                                  | SHRRES0          | _              | —                 |                  |                 |       |

| bit 7                             |                                                                                                                                          |                  |                |                   |                  |                 | bit 0 |

|                                   |                                                                                                                                          |                  |                |                   |                  |                 |       |

| Legend:                           |                                                                                                                                          |                  |                |                   |                  |                 |       |

| R = Readable bit W = Writable bit |                                                                                                                                          |                  | bit            | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at POR '1' = Bi        |                                                                                                                                          | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|                                   |                                                                                                                                          |                  |                |                   |                  |                 |       |

| bit 15-8                          | Unimplemen                                                                                                                               | ted: Read as 'd  | )'             |                   |                  |                 |       |

| bit 7                             | FORM: Fracti                                                                                                                             | onal Data Outp   | out Format bit |                   |                  |                 |       |

|                                   | 1 = Fractional<br>0 = Integer                                                                                                            |                  |                |                   |                  |                 |       |

| bit 6-5                           | SHRRES<1:0                                                                                                                               | >: Shared ADC    | C Core Resolut | tion Selection b  | oits             |                 |       |

|                                   | <ul> <li>11 = 12-bit resolution</li> <li>10 = 10-bit resolution</li> <li>01 = 8-bit resolution</li> <li>00 = 6-bit resolution</li> </ul> |                  |                |                   |                  |                 |       |

| bit 4-0                           | Unimplemen                                                                                                                               | ted: Read as 'o  | )'             |                   |                  |                 |       |

#### REGISTER 3-176: ADSTATL: ADC DATA READY STATUS REGISTER LOW

| HSC/R-0                                                                     | HSC/R-0 | HSC/R-0      | HSC/R-0          | HSC/R-0  | HSC/R-0 | HSC/R-0 | HSC/R-0 |

|-----------------------------------------------------------------------------|---------|--------------|------------------|----------|---------|---------|---------|

|                                                                             |         |              | AN<15            | :8>RDY   |         |         |         |

| bit 15                                                                      |         |              |                  |          |         |         | bit 8   |

|                                                                             |         |              |                  |          |         |         |         |

| HSC/R-0                                                                     | HSC/R-0 | HSC/R-0      | HSC/R-0          | HSC/R-0  | HSC/R-0 | HSC/R-0 | HSC/R-0 |

|                                                                             |         |              | AN<7:            | 0>RDY    |         |         |         |

| bit 7                                                                       |         |              |                  |          |         |         | bit 0   |

|                                                                             |         |              |                  |          |         |         |         |

| Legend:                                                                     |         | U = Unimplem | nented bit, read | d as '0' |         |         |         |

| R = Readable bit $W = Writable bit$ $HSC = Hardware Settable/Clearable bit$ |         |              |                  |          |         |         |         |

| R = Readable bit  | W = Writable bit | HSC = Hardware Settal | ole/Clearable bit  |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

bit 15-0 AN<15:0>RDY: Common Interrupt Enable for Corresponding Analog Input bits

1 = Channel conversion result is ready in the corresponding ADCBUFx register

0 = Channel conversion result is not ready

#### REGISTER 3-177: ADSTATH: ADC DATA READY STATUS REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | HSC/R-0 | HSC/R-0 | HSC/R-0    | HSC/R-0 | HSC/R-0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | —   |         | A       | N<20:16>RD | ſ       |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:           | U = Unimplemented bit, read as '0' |                                       |                    |  |  |

|-------------------|------------------------------------|---------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/Clearable bit |                    |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                  | x = Bit is unknown |  |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 AN<20:16>RDY: Common Interrupt Enable for Corresponding Analog Input bits

1 = Channel conversion result is ready in the corresponding ADCBUFx register

0 = Channel conversion result is not ready

| Register                   | Address | All Resets         | Register  | Address            | All Resets         | Register  | Address                                 | All Resets                              |

|----------------------------|---------|--------------------|-----------|--------------------|--------------------|-----------|-----------------------------------------|-----------------------------------------|

| High-Speed PWM (Continued) |         | PG6CLPCIL          | 44A       | 000000000000000000 | PG7DC              | 492       | 000000000000000000000000000000000000000 |                                         |

| PG5CONL                    | 402     | 0-000000000000000  | PG6CLPCIH | 44C                | 0000-00000000000   | PG7DCA    | 494                                     | 00000000                                |

| PG5CONH                    | 404     | 000-0000000000     | PG6FFPCIL | 44E                | 000000000000000000 | PG7PER    | 496                                     | 000000000000000000000000000000000000000 |

| PG5STAT                    | 406     | 000000000000000000 | PG6FFPCIH | 450                | 0000-00000000000   | PG7TRIGA  | 498                                     | 000000000000000000000000000000000000000 |

| PG5IOCONL                  | 408     | 000000000000000000 | PG6SPCIL  | 452                | 000000000000000000 | PG7TRIGB  | 49A                                     | 000000000000000000000000000000000000000 |

| PG5IOCONH                  | 40A     | -0000-000000       | PG6SPCIH  | 454                | 0000-00000000000   | PG7TRIGC  | 49C                                     | 000000000000000000000000000000000000000 |

| PG5EVTL                    | 40C     | 0000000000000      | PG6LEBL   | 456                | 00000000000000000  | PG7DTL    | 49E                                     | 0000000000000000000000000000000000000   |

| PG5EVTH                    | 40E     | 00000000000000     | PG6LEBH   | 458                | 0000000            | PG7DTH    | 4A0                                     | 0000000000000000000000000000000000000   |

| PG5FPCIL                   | 410     | 000000000000000000 | PG6PHASE  | 45A                | 000000000000000000 | PG7CAP    | 4A2                                     | 000000000000000000000000000000000000000 |

| PG5FPCIH                   | 412     | 0000-00000000000   | PG6DC     | 45C                | 000000000000000000 | PG8CONL   | 4A4                                     | 0-0000000000000000000000000000000000000 |

| PG5CLPCIL                  | 414     | 000000000000000000 | PG6DCA    | 45E                | 00000000           | PG8CONH   | 4A6                                     | 000-0000000000                          |

| PG5CLPCIH                  | 416     | 0000-00000000000   | PG6PER    | 460                | 000000000000000000 | PG8STAT   | 4A8                                     | 000000000000000000000000000000000000000 |

| PG5FFPCIL                  | 418     | 000000000000000000 | PG6TRIGA  | 462                | 000000000000000000 | PG8IOCONL | 4AA                                     | 000000000000000000000000000000000000000 |

| PG5FFPCIH                  | 41A     | 0000-00000000000   | PG6TRIGB  | 464                | 000000000000000000 | PG8IOCONH | 4AC                                     | -0000-000000                            |

| PG5SPCIL                   | 41C     | 000000000000000000 | PG6TRIGC  | 466                | 000000000000000000 | PG8EVTL   | 4AE                                     | 000000000000                            |

| PG5SPCIH                   | 41E     | 0000-00000000000   | PG6DTL    | 468                | 000000000000000    | PG8EVTH   | 4B0                                     | 00000000000000                          |

| PG5LEBL                    | 420     | 000000000000000000 | PG6DTH    | 46A                | 000000000000000    | PG8FPCIL  | 4B2                                     | 000000000000000000000000000000000000000 |

| PG5LEBH                    | 422     | 0000000            | PG6CAP    | 46C                | 000000000000000000 | PG8FPCIH  | 4B4                                     | 0000-00000000000                        |

| PG5PHASE                   | 424     | 000000000000000000 | PG7CONL   | 46E                | 0-00000000000000   | PG8CLPCIL | 4B6                                     | 000000000000000000000000000000000000000 |

| PG5DC                      | 426     | 000000000000000000 | PG7CONH   | 470                | 000-0000000000     | PG8CLPCIH | 4B8                                     | 0000-0000000000000                      |

| PG5DCA                     | 428     | 00000000           | PG7STAT   | 472                | 000000000000000000 | PG8FFPCIL | 4BA                                     | 000000000000000000000000000000000000000 |

| PG5PER                     | 42A     | 00000000000000000  | PG7IOCONL | 474                | 00000000000000000  | PG8FFPCIH | 4BC                                     | 0000-0000000000000000000000000000000000 |

| PG5TRIGA                   | 42C     | 000000000000000000 | PG7IOCONH | 476                | -00000-000000      | PG8SPCIL  | 4BE                                     | 000000000000000000000000000000000000000 |

| PG5TRIGB                   | 42E     | 00000000000000000  | PG7EVTL   | 478                | 000000000000       | PG8SPCIH  | 4C0                                     | 0000-00000000000                        |

| PG5TRIGC                   | 430     | 00000000000000000  | PG7EVTH   | 47A                | 00000000000000     | PG8LEBL   | 4C2                                     | 000000000000000000000000000000000000000 |

| PG5DTL                     | 432     | 000000000000000    | PG7FPCIL  | 47C                | 00000000000000000  | PG8LEBH   | 4C4                                     | 0000000                                 |

| PG5DTH                     | 434     | 000000000000000    | PG7FPCIH  | 47E                | 0000-00000000000   | PG8PHASE  | 4C6                                     | 000000000000000000000000000000000000000 |

| PG5CAP                     | 436     | 00000000000000000  | PG7CLPCIL | 480                | 00000000000000000  | PG8DC     | 4C8                                     | 000000000000000000000000000000000000000 |

| PG6CONL                    | 438     | 0-000000000000000  | PG7CLPCIH | 482                | 0000-00000000000   | PG8DCA    | 4CA                                     | 00000000                                |

| PG6CONH                    | 43A     | 000-0000000000     | PG7FFPCIL | 484                | 00000000000000000  | PG8PER    | 4CC                                     | 000000000000000000000000000000000000000 |

| PG6STAT                    | 43C     | 00000000000000000  | PG7FFPCIH | 486                | 0000-00000000000   | PG8TRIGA  | 4CE                                     | 000000000000000000000000000000000000000 |

| PG6IOCONL                  | 43E     | 00000000000000000  | PG7SPCIL  | 488                | 00000000000000000  | PG8TRIGB  | 4D0                                     | 000000000000000000000000000000000000000 |

| PG6IOCONH                  | 440     | -0000-000000       | PG7SPCIH  | 48A                | 0000-00000000000   | PG8TRIGC  | 4D2                                     | 000000000000000000000000000000000000000 |

| PG6EVTL                    | 442     | 0000000000000      | PG7LEBL   | 48C                | 00000000000000000  | PG8DTL    | 4D4                                     | 0000000000000000000000000000000000000   |

| PG6EVTH                    | 444     | 00000000000000     | PG7LEBH   | 48E                | 0000000            | PG8DTH    | 4D6                                     | 00000000000000000                       |

| PG6FPCIL                   | 446     | 000000000000000000 | PG7PHASE  | 490                | 00000000000000000  | PG8CAP    | 4D8                                     | 000000000000000000000000000000000000000 |

| PG6FPCIH                   | 448     | 0000-0000000000    |           |                    |                    |           |                                         |                                         |

#### TABLE 4-7: SLAVE SFR BLOCK 400h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address and Reset values are in hexadecimal and binary, respectively.

#### REGISTER 4-34: CNFx: INTERRUPT CHANGE NOTIFICATION FLAG FOR PORTx REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0   | R/W-0              | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|---------|--------------------|-------|-------|

|                                    |       |       | CNF                                | x<15:8> |                    |       |       |

| bit 15                             |       |       |                                    |         |                    |       | bit 8 |

|                                    |       |       |                                    |         |                    |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0   | R/W-0              | R/W-0 | R/W-0 |

|                                    |       |       | CNF                                | x<7:0>  |                    |       |       |

| bit 7                              |       |       |                                    |         |                    |       | bit 0 |

|                                    |       |       |                                    |         |                    |       |       |

| Legend:                            |       |       |                                    |         |                    |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimplemented bit, read as '0' |         |                    |       |       |

| -n = Value at POR (1' = Bit is set |       |       | '0' = Bit is clea                  | ared    | x = Bit is unknown |       |       |

bit 15-0 **CNFx<15:0>:** Interrupt Change Notification Flag for PORTx bits

When CNSTYLE (CNCONx<11>) = 1:

1 = An enabled edge event occurred on PORTx[n] pin

0 = An enabled edge event did not occur on PORTx[n] pin

'1' = Bit is set

| U-0            | U-0 | R/W-0        | R/W-0  | R/W-0        | R/W-0            | R/W-0  | R/W-0  |

|----------------|-----|--------------|--------|--------------|------------------|--------|--------|

| _              | —   | RP65R5       | RP65R4 | RP65R3       | RP65R2           | RP65R1 | RP65R0 |

| bit 15         |     |              |        |              |                  |        | bit 8  |

|                |     |              |        |              |                  |        |        |

| U-0            | U-0 | R/W-0        | R/W-0  | R/W-0        | R/W-0            | R/W-0  | R/W-0  |

| —              | —   | RP64R5       | RP64R4 | RP64R3       | RP64R2           | RP64R1 | RP64R0 |

| bit 7          |     |              |        |              |                  |        | bit 0  |

|                |     |              |        |              |                  |        |        |

| Legend:        |     |              |        |              |                  |        |        |

| R = Readable I | bit | W = Writable | bit    | U = Unimpler | nented bit, read | as '0' |        |

'0' = Bit is cleared

#### REGISTER 4-76: RPOR16: PERIPHERAL PIN SELECT OUTPUT REGISTER 16

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP65R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP65 Output Pin bits (see Table 4-31 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | RP64R<5:0>: Peripheral Output Function is Assigned to S1RP64 Output Pin bits                                                               |

# REGISTER 4-77: RPOR17: PERIPHERAL PIN SELECT OUTPUT REGISTER 17

(see Table 4-31 for peripheral function numbers)

| U-0                                | U-0 | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|------------------------------------|-----|--------|-----------------------------------------|--------|--------|--------|--------|

|                                    | _   | RP67R5 | RP67R4                                  | RP67R3 | RP67R2 | RP67R1 | RP67R0 |

| bit 15                             |     |        |                                         |        |        |        | bit 8  |

|                                    |     |        |                                         |        |        |        |        |

| U-0                                | U-0 | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| _                                  |     | RP66R5 | RP66R4                                  | RP66R3 | RP66R2 | RP66R1 | RP66R0 |

| bit 7                              |     |        |                                         |        |        |        | bit 0  |

|                                    |     |        |                                         |        |        |        |        |

| Legend:                            |     |        |                                         |        |        |        |        |

| R = Readable bit W = Writable bit  |     | bit    | U = Unimplemented bit, read as '0'      |        |        |        |        |

| -n = Value at POR '1' = Bit is set |     |        | '0' = Bit is cleared x = Bit is unknown |        |        | nown   |        |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP67R<5:0>:** Peripheral Output Function is Assigned to S1RP67 Output Pin bits (see Table 4-31 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP66R<5:0>:** Peripheral Output Function is Assigned to S1RP66 Output Pin bits (see Table 4-31 for peripheral function numbers)

-n = Value at POR

x = Bit is unknown

#### REGISTER 6-2: CLKDIV: CLOCK DIVIDER REGISTER (MASTER) (CONTINUED)

- bit 3-0 **PLLPRE<3:0>:** PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler)<sup>(4)</sup> 11111 = Reserved

- 1001 = Reserved 1000 = Input divided by 8 0111 = Input divided by 7 0110 = Input divided by 6 0101 = Input divided by 5 0100 = Input divided by 4 0011 = Input divided by 3 0010 = Input divided by 2 0001 = Input divided by 1 (power-on default selection) 0000 = Reserved

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 2: This bit is cleared when the ROI bit is set and an interrupt occurs.

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

- 4: PLLPRE<3:0> may be updated while the PLL is operating, but the VCO may overshoot.

#### U-0 U-0 HS/R/W-0 HS/R/W-0 U-0 HS/R/W-0 HS/R/W-0 HS/R/W-0 RXRPTIF TXRPTIF BTCIF WTCIF GTCIF \_\_\_\_ bit 15 bit 8 U-0 U-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 RXRPTIE TXRPTIE BTCIE WTCIE GTCIE bit 7 bit 0 Legend: HS = Hardware Settable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-14 Unimplemented: Read as '0' bit 13 **RXRPTIF:** Receive Repeat Interrupt Flag bit 1 = Parity error has persisted after the same character has been received five times (four retransmits) 0 = Flag is cleared **TXRPTIF:** Transmit Repeat Interrupt Flag bit bit 12 1 = Line error has been detected after the last retransmit per TXRPT<1:0> 0 = Flag is cleared bit 11 Unimplemented: Read as '0' bit 10 **BTCIF:** Block Time Counter Interrupt Flag bit 1 = Block Time Counter has reached 0 0 = Block Time Counter has not reached 0 bit 9 WTCIF: Waiting Time Counter Interrupt Flag bit 1 = Waiting Time Counter has reached 0 0 = Waiting Time Counter has not reached 0 bit 8 **GTCIF:** Guard Time Counter Interrupt Flag bit 1 = Guard Time Counter has reached 0 0 = Guard Time Counter has not reached 0 bit 7-6 Unimplemented: Read as '0' **RXRPTIE:** Receive Repeat Interrupt Enable bit bit 5 1 = An interrupt is invoked when a parity error has persisted after the same character has been received five times (four retransmits) 0 = Interrupt is disabled bit 4 **TXRPTIE:** Transmit Repeat Interrupt Enable bit 1 = An interrupt is invoked when a line error is detected after the last retransmit per TXRPT<1:0> has been completed 0 = Interrupt is disabled bit 3 Unimplemented: Read as '0' bit 2 BTCIE: Block Time Counter Interrupt Enable bit 1 = Block Time Counter interrupt is enabled 0 = Block Time Counter interrupt is disabled bit 1 WTCIE: Waiting Time Counter Interrupt Enable bit 1 = Waiting Time Counter interrupt is enabled 0 = Waiting Time Counter Interrupt is disabled bit 0 **GTCIE:** Guard Time Counter interrupt enable bit 1 = Guard Time Counter interrupt is enabled 0 = Guard Time Counter interrupt is disabled

#### REGISTER 13-16: UXSCINT: UARTX SMART CARD INTERRUPT REGISTER

To set up the SPIx module for Audio mode:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- a) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with AUDEN (SPIxCON1H<15>) = 1.

- 4. Clear the SPIROV bit (SPIxSTATL<6>).

- 5. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 6. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

| Slave Address | R/W Bit | Description                            |  |  |  |

|---------------|---------|----------------------------------------|--|--|--|

| 0000 000      | 0       | General Call Address <sup>(2)</sup>    |  |  |  |

| 0000 000      | 1       | Start Byte                             |  |  |  |

| 0000 001      | х       | Cbus Address                           |  |  |  |

| 0000 01x      | х       | Reserved                               |  |  |  |

| 0000 1xx      | х       | HS Mode Master Code                    |  |  |  |

| 1111 0xx      | х       | 10-Bit Slave Upper Byte <sup>(3)</sup> |  |  |  |

| 1111 1xx      | х       | Reserved                               |  |  |  |

Note 1: The address bits listed here will never cause an address match independent of address mask settings.

2: This address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

## 20.1 Current Bias Generator Control Registers

#### REGISTER 20-1: BIASCON: CURRENT BIAS GENERATOR CONTROL REGISTER

| R/W-0        | U-0                                       | U-0                                                                         | U-0         | U-0              | U-0             | U-0             | U-0                |  |

|--------------|-------------------------------------------|-----------------------------------------------------------------------------|-------------|------------------|-----------------|-----------------|--------------------|--|

| ON           |                                           | —                                                                           | —           | —                |                 | —               |                    |  |

| bit 15       |                                           |                                                                             |             |                  |                 |                 | bit 8              |  |

|              |                                           |                                                                             |             |                  |                 |                 |                    |  |

| U-0          | U-0                                       | U-0                                                                         | U-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0              |  |

|              | —                                         | —                                                                           | —           | 110EN3           | I10EN2          | 110EN1          | 110EN0             |  |

| bit 7        |                                           |                                                                             |             |                  |                 |                 | bit 0              |  |

|              |                                           |                                                                             |             |                  |                 |                 |                    |  |

| Legend:      |                                           |                                                                             |             |                  |                 |                 |                    |  |

| R = Readab   | ole bit                                   | W = Writable I                                                              | oit         | U = Unimpler     | nented bit, rea | d as '0'        |                    |  |

| -n = Value a | at POR                                    | '1' = Bit is set                                                            |             | '0' = Bit is cle | ared            | x = Bit is unkr | x = Bit is unknown |  |

|              |                                           |                                                                             |             |                  |                 |                 |                    |  |

| bit 15       | ON: Current E                             | Bias Module En                                                              | able bit    |                  |                 |                 |                    |  |

|              | 1 = Module is                             |                                                                             |             |                  |                 |                 |                    |  |

|              | 0 = Module is                             |                                                                             |             |                  |                 |                 |                    |  |

| bit 14-4     | Unimplemen                                | ted: Read as '0                                                             | )'          |                  |                 |                 |                    |  |

| bit 3        | <b>Ι10ΕΝ3:</b> 10 μ                       | A Enable for Ou                                                             | utput 3 bit |                  |                 |                 |                    |  |

|              |                                           | put is enabled                                                              |             |                  |                 |                 |                    |  |

|              | •                                         | put is disabled                                                             |             |                  |                 |                 |                    |  |

| bit 2        | •                                         | A Enable for O                                                              | utput 2 bit |                  |                 |                 |                    |  |

|              |                                           | put is enabled                                                              |             |                  |                 |                 |                    |  |

| bit 1        | $0 = 10 \ \mu\text{A}$ output is disabled |                                                                             |             |                  |                 |                 |                    |  |

|              | -                                         | <b>I10EN1:</b> 10 μA Enable for Output 1 bit<br>1 = 10 μA output is enabled |             |                  |                 |                 |                    |  |

|              | $0 = 10 \ \mu\text{A}$ output is disabled |                                                                             |             |                  |                 |                 |                    |  |

| bit 0        | -                                         | A Enable for Ou                                                             | utput 0 bit |                  |                 |                 |                    |  |

|              |                                           | put is enabled                                                              | •           |                  |                 |                 |                    |  |

|              | •                                         | ,<br>put is disabled                                                        |             |                  |                 |                 |                    |  |

|              |                                           |                                                                             |             |                  |                 |                 |                    |  |

#### REGISTER 21-31: FS1ALTREG CONFIGURATION REGISTER (SLAVE) (CONTINUED)

- bit 2-0 S1CTXT1<2:0>: Alternate Working Register Set #1 Interrupt Priority Level Selection bits

- 111 = Not assigned

- 110 = Alternate Register Set #1 is assigned to IPL Level 7

- 101 = Alternate Register Set #1 is assigned to IPL Level 6

- 100 = Alternate Register Set #1 is assigned to IPL Level 5

- 011 = Alternate Register Set #1 is assigned to IPL Level 4

- 010 = Alternate Register Set #1 is assigned to IPL Level 3

- 001 = Alternate Register Set #1 is assigned to IPL Level 2

- 000 = Alternate Register Set #1 is assigned to IPL Level 1

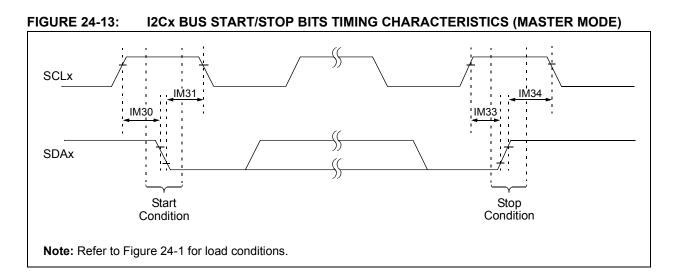

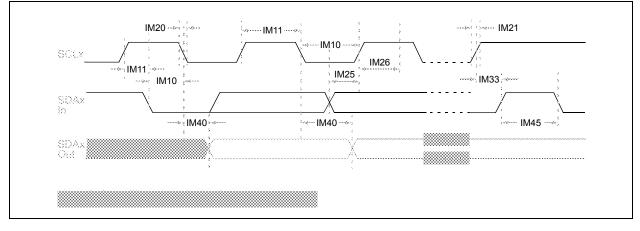

| TABLE 24-40: | I2Cx BUS DATA | TIMING REQUIREMENTS | (MASTER MODE) |

|--------------|---------------|---------------------|---------------|

|--------------|---------------|---------------------|---------------|

| AC CHA       | RACTER                | ISTICS           |                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                        |  |

|--------------|-----------------------|------------------|---------------------------|------------------------------------------------------|------|-------|------------------------|--|

| Param<br>No. | Symbol                | Characte         | eristic <sup>(4)</sup>    | Min. <sup>(1)</sup>                                  | Max. | Units | Conditions             |  |

| IM10         | TLO:SCL               | Clock Low Time   | 100 kHz mode              | Tcy (BRG + 1)                                        | _    | μs    |                        |  |

|              |                       |                  | 400 kHz mode              | Tcy (BRG + 1)                                        | _    | μs    |                        |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | Tcy (BRG + 1)                                        | _    | μs    |                        |  |

| IM11         | THI:SCL               | Clock High Time  | 100 kHz mode              | Tcy (BRG + 1)                                        | —    | μs    |                        |  |

|              |                       |                  | 400 kHz mode              | Tcy (BRG + 1)                                        | —    | μs    |                        |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | Tcy (BRG + 1)                                        | _    | μs    |                        |  |

| IM20         | TF:SCL                | SDAx and SCLx    | 100 kHz mode              |                                                      | 300  | ns    | CB is specified to be  |  |

|              |                       | Fall Time        | 400 kHz mode              | 20 x (VDD/5.5V)                                      | 300  | ns    | from 10 to 400 pF      |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | _                                                    | 120  | ns    |                        |  |

| IM21         | TR:SCL                | SDAx and SCLx    | 100 kHz mode              | _                                                    | 1000 | ns    | CB is specified to be  |  |

|              | Rise Time             | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                          | 300  | ns    | from 10 to 400 pF      |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | _                                                    | 120  | ns    |                        |  |

| IM25         | TSU:DAT               | Data Input       | 100 kHz mode              | 250                                                  | _    | ns    |                        |  |

|              | Set                   | Setup Time       | 400 kHz mode              | 100                                                  | —    | ns    |                        |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | 50                                                   | _    | ns    |                        |  |

| IM26         | 26 THD:DAT Data Input | Data Input       | 100 kHz mode              | 0                                                    | _    | μs    |                        |  |

|              | Hold Time             | 400 kHz mode     | 0                         | 0.9                                                  | μs   |       |                        |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | 0                                                    | 0.3  | μs    |                        |  |

| IM30         | TSU:STA               | Start Condition  | 100 kHz mode              | Tcy (BRG + 1)                                        | _    | μs    | Only relevant for      |  |

|              |                       | Setup Time       | 400 kHz mode              | Tcy (BRG + 1)                                        | _    | μs    | Repeated Start         |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | Tcy (BRG + 1)                                        | _    | μs    | condition              |  |

| IM31         | THD:STA               | Start Condition  | 100 kHz mode              | Tcy (BRG + 1)                                        | _    | μs    | After this period, the |  |

|              |                       | Hold Time        | 400 kHz mode              | TCY (BRG + 1)                                        | —    | μs    | first clock pulse is   |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | Tcy (BRG + 1)                                        | _    | μs    | generated              |  |

| IM33         | Tsu:sto               | Stop Condition   | 100 kHz mode              | TCY (BRG + 1)                                        | —    | μs    |                        |  |

|              |                       | Setup Time       | 400 kHz mode              | Tcy (BRG + 1)                                        | —    | μs    |                        |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | Tcy (BRG + 1)                                        | —    | μs    |                        |  |

| IM34         | THD:STO               | Stop Condition   | 100 kHz mode              | TCY (BRG + 1)                                        | —    | μs    |                        |  |

|              |                       | Hold Time        | 400 kHz mode              | Tcy (BRG + 1)                                        | —    | μs    |                        |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | Tcy (BRG + 1)                                        | _    | μs    |                        |  |

| IM40         | TAA:SCL               | Output Valid     | 100 kHz mode              | —                                                    | 3450 | ns    |                        |  |

|              |                       | from Clock       | 400 kHz mode              |                                                      | 900  | ns    |                        |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | —                                                    | 450  | ns    |                        |  |

| IM45         | TBF:SDA               | Bus Free Time    | 100 kHz mode              | 4.7                                                  | —    | μs    | Time the bus must be   |  |

|              |                       |                  | 400 kHz mode              | 1.3                                                  | —    | μs    | free before a new      |  |

|              |                       |                  | 1 MHz mode <sup>(2)</sup> | 0.5                                                  | —    | μs    | transmission can start |  |

| IM50         | Св                    | Bus Capacitive L | oading                    | —                                                    | 400  | pF    |                        |  |

| IM51         | TPGD                  | Pulse Gobbler De | elay                      | 65                                                   | 390  | ns    | (Note 3)               |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

2: Maximum Pin Capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** Typical value for this parameter is 130 ns.

4: These parameters are characterized but not tested in manufacturing.

#### 25.0 PACKAGING INFORMATION

## 25.1 Package Marking Information

28-Lead SSOP (5.30 mm)

Example

28-Lead UQFN (6x6 mm)

Example

36-Lead UQFN (5x5 mm)

Example

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                      | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                            |

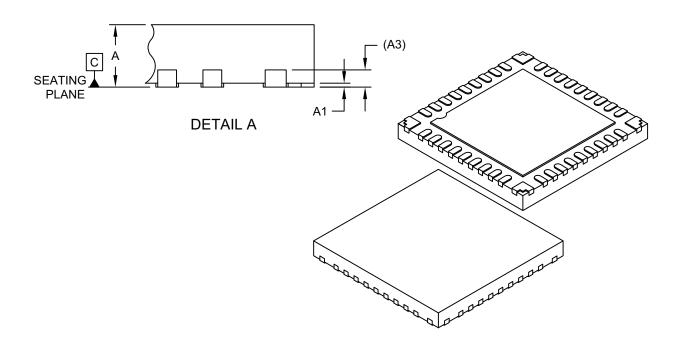

# 36-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M5) - 5x5 mm Body [UQFN] With Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units |           | MILLIMETERS |      |  |

|-------------------------|-------|-----------|-------------|------|--|

| Dimension Limits        |       | MIN       | NOM         | MAX  |  |

| Number of Terminals     | Ν     | 36        |             |      |  |

| Pitch                   | е     | 0.40 BSC  |             |      |  |

| Overall Height          | А     | 0.50      | 0.55        | 0.60 |  |

| Standoff                | A1    | 0.00      | 0.02        | 0.05 |  |

| Terminal Thickness      | A3    | 0.152 REF |             |      |  |

| Overall Length          | D     | 5.00 BSC  |             |      |  |

| Exposed Pad Length      | D2    | 3.60      | 3.70        | 3.80 |  |

| Overall Width           | E     | 5.00 BSC  |             |      |  |

| Exposed Pad Width       | E2    | 3.60      | 3.70        | 3.80 |  |

| Terminal Width          | b     | 0.15      | 0.20        | 0.25 |  |

| Terminal Length         | L     | 0.30      | 0.40        | 0.50 |  |

| Terminal-to-Exposed-Pad | K     | 0.25 REF  |             |      |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-436A-M5 Sheet 2 of 2

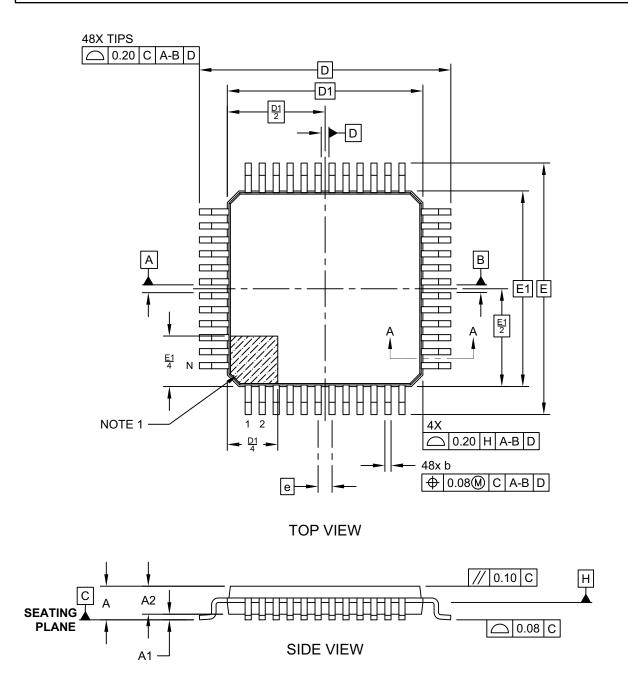

#### 48-Lead Thin Quad Flatpack (PT) - 7x7x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-300-PT Rev A Sheet 1 of 2