Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 27                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 36-UQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp203-e-m5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 6: 36-PIN UQFN

| Pin# | Master Core                             | Slave Core                                                                                           |

|------|-----------------------------------------|------------------------------------------------------------------------------------------------------|

| 1    | RP46/PWM1H/RB14                         | <b>S1RP46</b> /S1PWM1H/S1RB14                                                                        |

| 2    | RP47/PWM1L/RB15                         | S1RP47/S1PWM6H/S1PWM1L/S1RB15                                                                        |

| 3    | MCLR                                    | _                                                                                                    |

| 4    | AN12/IBIAS3/ <b>RP48</b> /RC0           | S1AN10/ <b>S1RP48</b> /S1RC0                                                                         |

| 5    | AN0/CMP1A/RA0                           | S1RA0                                                                                                |

| 6    | AN1/RA1                                 | S1AN15/S1RA1                                                                                         |

| 7    | AN2/RA2                                 | S1AN16/S1RA2                                                                                         |

| 8    | AN3/IBIAS0/RA3                          | S1AN0/S1CMP1A/S1PGA1P1/S1RA3                                                                         |

| 9    | AN4/IBIAS1/RA4                          | S1MCLR3/S1AN1/S1CMP2A/S1PGA2P1/S1PGA3P2/S1RA4                                                        |

| 10   | AVDD                                    | AVDD                                                                                                 |

| 11   | AVss                                    | AVss                                                                                                 |

| 12   | AN13/ISRC0/ <b>RP49</b> /RC1            | S1ANA1/ <b>S1RP49</b> /S1RC1                                                                         |

| 13   | AN14/ISRC1/ <b>RP50</b> /RC2            | S1ANA0/ <b>S1RP50</b> /S1RC2                                                                         |

| 14   | VDD                                     | VDD                                                                                                  |

| 15   | Vss                                     | Vss                                                                                                  |

| 16   | CMP1B/ <b>RP51</b> /RC3                 | S1AN8/S1CMP3B/ <b>S1RP51</b> /S1RC3                                                                  |

| 17   | OSCI/CLKI/AN5/RP32/RB0                  | S1AN5/ <b>S1RP32</b> /S1RB0                                                                          |

| 18   | OSCO/CLKO/AN6/IBIAS2/RP33/RB1           | S1AN4/ <b>S1RP33</b> /S1RB1                                                                          |

| 19   | DACOUT/AN7/CMP1D/ <b>RP34</b> /INT0/RB2 | \$\overline{\text{S1MCLR2}}\s1an3/\s1anc0/\s1anc1/\s1cMP1D/\s1cMP2D/\s1cMP3D/\s1RP34/\s1\into/\s1RB2 |

| 20   | PGD2/AN8/ <b>RP35</b> /RB3              | S1PGD2/S1AN18/S1CMP3A/S1PGA3P1/ <b>S1RP35</b> /S1RB3                                                 |

| 21   | PGC2/RP36/RB4                           | S1PGC2/S1AN9/ <b>S1RP36</b> /S1PWM5L/S1RB4                                                           |

| 22   | Vss                                     | Vss                                                                                                  |

| 23   | VDD                                     | VDD                                                                                                  |

| 24   | PGD3/ <b>RP37</b> /SDA2/RB5             | S1PGD3/ <b>S1RP37</b> /S1RB5                                                                         |

| 25   | PGC3/RP38/SCL2/RB6                      | S1PGC3/ <b>S1RP38</b> /S1RB6                                                                         |

| 26   | TDO/AN9/ <b>RP39</b> /RB7               | \$1MCLR1/\$1AN6/ <b>\$1RP39</b> /\$1PWM5H/\$1RB7                                                     |

| 27   | PGD1/AN10/ <b>RP40</b> /SCL1/RB8        | S1PGD1/S1AN7/ <b>S1RP40</b> /S1SCL1/S1RB8                                                            |

| 28   | PGC1/AN11/ <b>RP41</b> /SDA1/RB9        | S1PGC1/ <b>S1RP41</b> /S1SDA1/S1RB9                                                                  |

| 29   | RP52/RC4                                | S1RP52/S1PWM2H/S1RC4                                                                                 |

| 30   | RP53/RC5                                | S1RP53/S1PWM2L/S1RC5                                                                                 |

| 31   | Vss                                     | Vss                                                                                                  |

| 32   | VDD                                     | VDD                                                                                                  |

| 33   | TMS/ <b>RP42</b> /PWM3H/RB10            | <b>S1RP42</b> /S1PWM3H/S1RB10                                                                        |

| 34   | TCK/ <b>RP43</b> /PWM3L/RB11            | S1RP43/S1PWM8H/S1PWM3L/S1RB11                                                                        |

| 35   | TDI/ <b>RP44</b> /PWM2H/RB12            | S1RP44/S1PWM7L/S1RB12                                                                                |

| 36   | RP45/PWM2L/RB13                         | <b>S1RP45</b> /S1PWM7H/S1RB13                                                                        |

**Legend:** RPn and S1RPn represent remappable pins for Peripheral Pin Select functions.

#### 3.1.5 PROGRAMMER'S MODEL

The programmer's model for the dsPIC33CH128MP508 family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33CH128MP508 devices contain control registers for Modulo Addressing, Bit-Reversed Addressing and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Figure 3-3 and Figure 3-4.

TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

| Register(s) Name                  | Description                                                   |

|-----------------------------------|---------------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>     | Working Register Array                                        |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 1                            |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 2                            |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 3                            |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 4                            |

| ACCA, ACCB                        | 40-Bit DSP Accumulators (Additional 4 Alternate Accumulators) |

| PC                                | 23-Bit Program Counter                                        |

| SR                                | ALU and DSP Engine STATUS Register                            |

| SPLIM                             | Stack Pointer Limit Value Register                            |

| TBLPAG                            | Table Memory Page Address Register                            |

| DSRPAG                            | Extended Data Space (EDS) Read Page Register                  |

| RCOUNT                            | REPEAT Loop Counter Register                                  |

| DCOUNT                            | DO Loop Counter Register                                      |

| DOSTARTH, DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)                 |

| DOENDH, DOENDL                    | DO Loop End Address Register (High and Low)                   |

| CORCON                            | Contains DSP Engine, DO Loop Control and Trap Status bits     |

**Note 1:** Memory-mapped W0 through W14 represent the value of the register in the currently active CPU context.

<sup>2:</sup> The DOSTARTH and DOSTARTL registers are read-only.

### 3.6.15 I/O HELPFUL TIPS

- 1. In some cases, certain pins, as defined in Table 24-18 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or lesser than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low-side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins, by default, after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Select for PORTx registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

Note: Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN14/ISRC1/RP50/RC2; this indicates that AN14 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in Section 24.0 "Electrical Characteristics" of this data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 25.0 "DC and AC Device Characteristics Graphs" for additional information.

#### REGISTER 3-88: RPOR20: PERIPHERAL PIN SELECT OUTPUT REGISTER 20

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _      | _   | RP177R5 <sup>(1)</sup> | RP177R4 <sup>(1)</sup> | RP177R3 <sup>(1)</sup> | RP177R2 <sup>(1)</sup> | RP177R1 <sup>(1)</sup> | RP177R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _     | _   | RP176R5 <sup>(1)</sup> | RP176R4 <sup>(1)</sup> | RP176R3 <sup>(1)</sup> | RP176R2 <sup>(1)</sup> | RP176R1 <sup>(1)</sup> | RP176R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP177R<5:0>: Peripheral Output Function is Assigned to RP177 Output Pin bits<sup>(1)</sup>

(see Table 3-33 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP176R<5:0>: Peripheral Output Function is Assigned to RP176 Output Pin bits<sup>(1)</sup>

(see Table 3-33 for peripheral function numbers)

Note 1: These are virtual output ports.

#### REGISTER 3-89: RPOR21: PERIPHERAL PIN SELECT OUTPUT REGISTER 21

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _      | _   | RP179R5 <sup>(1)</sup> | RP179R4 <sup>(1)</sup> | RP179R3 <sup>(1)</sup> | RP179R2 <sup>(1)</sup> | RP179R1 <sup>(1)</sup> | RP179R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _     | _   | RP178R5 <sup>(1)</sup> | RP178R4 <sup>(1)</sup> | RP178R3 <sup>(1)</sup> | RP178R2 <sup>(1)</sup> | RP178R1 <sup>(1)</sup> | RP178R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP179R<5:0>:** Peripheral Output Function is Assigned to RP179 Output Pin bits<sup>(1)</sup>

(see Table 3-33 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits<sup>(1)</sup>

(see Table 3-33 for peripheral function numbers)

Note 1: These are virtual output ports.

# REGISTER 3-152: C1FLTCONxL: CAN FILTER CONTROL REGISTER x LOW (x = 0 TO 3; a = 0, 4, 8, 12; b = 1, 5, 9, 13)

| R/W-0  | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-------|-------|-------|

| FLTENb | _   | _   | FbBP4 | FbBP3 | FbBP2 | FbBP1 | FbBP0 |

| bit 15 |     |     |       |       |       |       | bit 8 |

| R/W-0  | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-------|-------|-------|

| FLTENa | _   | _   | FaBP4 | FaBP3 | FaBP2 | FaBP1 | FaBP0 |

| bit 7  |     |     |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 FLTENb: Enable Filter b to Accept Messages bit

1 = Filter is enabled0 = Filter is disabled

bit 14-13 **Unimplemented:** Read as '0'

bit 12-8 **FbBP<4:0>:** Pointer to Object When Filter b Hits bits

11111 to 11000 = Reserved

00111 = Message matching filter is stored in Object 7 00110 = Message matching filter is stored in Object 6

. **.** .

00010 = Message matching filter is stored in Object 2 00001 = Message matching filter is stored in Object 1

00000 = Reserved; Object 0 is the TX Queue and can't receive messages

bit 7 FLTENa: Enable Filter a to Accept Messages bit

1 = Filter is enabled0 = Filter is disabled

bit 6-5 **Unimplemented:** Read as '0'

bit 4-0 **FaBP<4:0>:** Pointer to Object When Filter a Hits bits

11111 to 11000 = Reserved

00111 = Message matching filter is stored in Object 7 00110 = Message matching filter is stored in Object 6

. . .

00010 = Message matching filter is stored in Object 2 00001 = Message matching filter is stored in Object 1

00000 = Reserved; Object 0 is the TX Queue and can't receive messages

#### 4.2.2.5 X and Y Data Spaces

The dsPIC33CH128MP508S1 family core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

#### 4.2.3 MEMORY RESOURCES

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 4.2.3.1 Key Resources

- "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

TABLE 4-27: SLAVE REMAPPABLE PIN INPUTS (CONTINUED)

| RPINRx<15:8> or<br>RPINRx<7:0> | Function               | Available on Ports   |  |  |  |

|--------------------------------|------------------------|----------------------|--|--|--|

| 60                             | S1RP60                 | Port Pin RC12        |  |  |  |

| 61                             | S1RP61                 | Port Pin RC13        |  |  |  |

| 62                             | S1RP62                 | Port Pin RC14        |  |  |  |

| 63                             | S1RP63                 | Port Pin RC15        |  |  |  |

| 64                             | S1RP64                 | Port Pin RD0         |  |  |  |

| 65                             | S1RP65                 | Port Pin RD1         |  |  |  |

| 66                             | S1RP66                 | Port Pin RD2         |  |  |  |

| 67                             | S1RP67                 | Port Pin RD3         |  |  |  |

| 68                             | S1RP68                 | Port Pin RD4         |  |  |  |

| 69                             | S1RP69                 | Port Pin RD5         |  |  |  |

| 70                             | S1RP70                 | Port Pin RD6         |  |  |  |

| 71                             | S1RP71                 | Port Pin RD7         |  |  |  |

| 72-161                         | S1RP72-S1RP161         | Reserved             |  |  |  |

| 162                            | Slave On Request PWM3  | Internal PWM Signal  |  |  |  |

| 163                            | Slave Off Request PWM3 | Internal PWM Signal  |  |  |  |

| 164                            | Slave On Request PWM2  | Internal PWM Signal  |  |  |  |

| 165                            | Slave Off Request PWM2 | Internal PWM Signal  |  |  |  |

| 166                            | Slave On Request PWM1  | Internal PWM Signal  |  |  |  |

| 167                            | Slave Off Request PWM1 | Internal PWM Signal  |  |  |  |

| 168-169                        | S1RP168-S1RP169        | Reserved             |  |  |  |

| 170                            | S1RP170                | Slave Virtual S1RPV0 |  |  |  |

| 171                            | S1RP171                | Slave Virtual S1RPV1 |  |  |  |

| 172                            | S1RP172                | Slave Virtual S1RPV2 |  |  |  |

| 173                            | S1RP173                | Slave Virtual S1RPV3 |  |  |  |

| 174                            | S1RP174                | Slave Virtual S1RPV4 |  |  |  |

| 175                            | S1RP175                | Slave Virtual S1RPV5 |  |  |  |

| 176                            | S1RP176                | Master Virtual RPV0  |  |  |  |

| 177                            | S1RP177                | Master Virtual RPV1  |  |  |  |

| 178                            | S1RP178                | Master Virtual RPV2  |  |  |  |

| 179                            | S1RP179                | Master Virtual RPV3  |  |  |  |

| 180                            | S1RP180                | Master Virtual RPV4  |  |  |  |

| 181                            | S1RP181                | Master Virtual RPV5  |  |  |  |

#### REGISTER 4-47: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| R/W-0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| QEIHOM1R7 | QEIHOM1R6 | QEIHOM1R5 | QEIHOM1R4 | QEIHOM1R3 | QEIHOM1R2 | QEIHOM1R1 | QEIHOM1R0 |

| bit 15    |           |           |           |           |           |           | bit 8     |

| R/W-0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| QEINDX1R7 | QEINDX1R6 | QEINDX1R5 | QEINDX1R4 | QEINDX1R3 | QEINDX1R2 | QEINDX1R1 | QEINDX1R0 |

| bit 7     |           |           |           |           |           |           | bit 0     |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 QEIHOM1R<7:0>: Assign QEI Home 1 Input (S1QEIHOM1) to the Corresponding S1RPn Pin bits

See Table 4-27.

bit 7-0 QEINDX1R<7:0>: Assign QEI Index 1 Input (S1QEINDX1) to the Corresponding S1RPn Pin bits

See Table 4-27.

#### REGISTER 4-48: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| U1DSRR7 | U1DSRR6 | U1DSRR5 | U1DSRR4 | U1DSRR3 | U1DSRR2 | U1DSRR1 | U1DSRR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| U1RXR7 | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **U1DSRR<7:0>:** Assign UART1 Data-Set-Ready (\$\overline{S1U1DSR}\$) to the Corresponding \$S1RPn Pin bits

See Table 4-27.

bit 7-0 U1RXR<7:0>: Assign UART1 Receive (S1U1RX) to the Corresponding S1RPn Pin bits

See Table 4-27.

#### REGISTER 4-68: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP49R5 | RP49R4 | RP49R3 | RP49R2 | RP49R1 | RP49R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP48R5 | RP48R4 | RP48R3 | RP48R2 | RP48R1 | RP48R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP49R<5:0>: Peripheral Output Function is Assigned to S1RP49 Output Pin bits

(see Table 4-31 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP48R<5:0>: Peripheral Output Function is Assigned to S1RP48 Output Pin bits

(see Table 4-31 for peripheral function numbers)

#### REGISTER 4-69: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP51R5 | RP51R4 | RP51R3 | RP51R2 | RP51R1 | RP51R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP50R5 | RP50R4 | RP50R3 | RP50R2 | RP50R1 | RP50R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP51R<5:0>: Peripheral Output Function is Assigned to S1RP51 Output Pin bits

(see Table 4-31 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP50R<5:0>: Peripheral Output Function is Assigned to S1RP50 Output Pin bits

(see Table 4-31 for peripheral function numbers)

#### REGISTER 4-101: ADMODOL: ADC INPUT MODE CONTROL REGISTER 0 LOW

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | DIFF1 | SIGN1 | DIFF0 | SIGN0 |

| bit 7 |     |     |     |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 **Unimplemented:** Read as '0'

bit 3 and bit 1 DIFF<1:0>: Differential-Mode for Corresponding Analog Inputs bits

(odd) 1 = Channel is differential

0 = Channel is single-ended

bit 2 and bit 0 SIGN<1:0>: Output Data Sign for Corresponding Analog Inputs bits

(even) 1 = Channel output data is signed

0 = Channel output data is unsigned

### REGISTER 6-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER (MASTER)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   |       |       | TUN   | <5:0> |       |       |

| bit 7 |     |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 TUN<5:0>: FRC Oscillator Tuning bits

011111 = Maximum frequency deviation of 1.74% (MHz)

011110 = Center frequency + 1.693% (MHz)

. .

000001 = Center frequency + 0.047% (MHz)

000000 = Center frequency (8.00 MHz nominal)

111111 = Center frequency – 0.047% (MHz)

. .

100001 = Center frequency - 1.693% (MHz)

100000 = Minimum frequency deviation of -1.74% (MHz)

Example 6-4 illustrates code for using the PLL (50 MIPS) with the Primary Oscillator.

## EXAMPLE 6-4: CODE EXAMPLE FOR USING MASTER PLL (75 MIPS) WITH PRIMARY OSCILLATOR (POSC)

```

//{

m code} example for 70 MIPS system clock using POSC with 10 MHz external crystal

// Select Internal FRC at POR

// Select FRC on POR

#pragma config FNOSC = FRC

// Oscillator Source Selection (Internal Fast RC (FRC))

#pragma config IESO = OFF

/// Enable Clock Switching and Configure POSC in XT mode

#pragma config POSCMD = XT

#pragma config FCKSM = CSECMD

main()

// Configure PLL prescaler, both PLL postscalers, and PLL feedback divider

CLKDIVbits.PLLPRE = 1; // N1=1

// M = 100

PLLFBDbits.PLLFBDIV = 100;

PLLDIVbits.POST1DIV = 5;

// N2=5

PLLDIVbits.POST2DIV = 1;

// N3=1

// Initiate Clock Switch to Primary Oscillator with PLL (NOSC=0b011)

__builtin_write_OSCCONH(0x03);

__builtin_write_OSCCONL(OSCCON | 0x01);

// Wait for Clock switch to occur

while (OSCCONbits.OSWEN! = 0);

// Wait for PLL to lock

while (OSCCONbits.LOCK!= 1);

Note: FPLLO = FPLLI * M/(N1 * N2 * N3); FPLLI = 10; M = 150; N1 = 1; N2 = 5; N3 = 1;

so FPLLO = 10 * 100/(1 * 5 * 1) = 300 MHz or 75 MIPS.

```

#### REGISTER 11-8: SLPxCONH: DACx SLOPE CONTROL HIGH REGISTER

| R/W-0  | U-0 | U-0 | U-0 | R/W-0              | R/W-0               | R/W-0 | U-0   |

|--------|-----|-----|-----|--------------------|---------------------|-------|-------|

| SLOPEN | _   | _   | _   | HME <sup>(1)</sup> | TWME <sup>(2)</sup> | PSE   | _     |

| bit 15 |     |     |     |                    |                     |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 15 SLOPEN: Slope Function Enable/On bit

1 = Enables slope function

0 = Disables slope function; slope accumulator is disabled to reduce power consumption

bit 14-12 **Unimplemented:** Read as '0'

bit 11 **HME:** Hysteretic Mode Enable bit<sup>(1)</sup>

1 = Enables Hysteretic mode for DACx0 = Disables Hysteretic mode for DACx

bit 10 **TWME:** Triangle Wave Mode Enable bit<sup>(2)</sup>

1 = Enables Triangle Wave mode for DACx0 = Disables Triangle Wave mode for DACx

bit 9 **PSE:** Positive Slope Mode Enable bit

1 = Slope mode is positive (increasing)

0 = Slope mode is negative (decreasing)

bit 8-0 **Unimplemented:** Read as '0'

**Note 1:** HME mode requires the user to disable the slope function (SLOPEN = 0).

2: TWME mode requires the user to enable the slope function (SLOPEN = 1).

### REGISTER 12-2: QEIXIOCL: QEIX I/O CONTROL LOW REGISTER (CONTINUED)

bit 6 IDXPOL: INDXx Input Polarity Select bit

1 = Input is inverted0 = Input is not inverted

bit 5 QEBPOL: QEBx Input Polarity Select bit

1 = Input is inverted0 = Input is not inverted

bit 4 QEAPOL: QEAx Input Polarity Select bit

1 = Input is inverted0 = Input is not inverted

bit 3 **HOME:** Status of HOMEx Input Pin after Polarity Control bit (read-only)

1 = Pin is at logic '1' if the HOMPOL bit is set to '0'; pin is at logic '0' if the HOMPOL bit is set to '1' 0 = Pin is at logic '0' if the HOMPOL bit is set to '0'; pin is at logic '1' if the HOMPOL bit is set to '1'

bit 2 INDEX: Status of INDXx Input Pin After Polarity Control bit (read-only)

1 = Pin is at logic '1' if the IDXPOL bit is set to '0'; pin is at logic '0' if the IDXPOL bit is set to '1' 0 = Pin is at logic '0' if the IDXPOL bit is set to '0'; pin is at logic '1' if the IDXPOL bit is set to '1'

bit 1 QEB: Status of QEBx Input Pin After Polarity Control and SWPAB Pin Swapping bit (read-only)

- 1 = Physical pin, QEBx, is at logic '1' if the QEBPOL bit is set to '0' and the SWPAB bit is set to '0'; physical pin, QEBx, is at logic '0' if the QEBPOL bit is set to '1' and the SWPAB bit is set to '0'; physical pin, QEAx, is at logic '1' if the QEBPOL bit is set to '0' and the SWPAB bit is set to '1'; physical pin, QEAx, is at logic '0' if the QEBPOL bit is set to '1' and the SWPAB bit is set to '1'

- 0 = Physical pin, QEBx, is at logic '0' if the QEBPOL bit is set to '0' and the SWPAB bit is set to '0'; physical pin, QEBx, is at logic '1' if the QEBPOL bit is set to '1' and the SWPAB bit is set to '0'; physical pin, QEAx, is at logic '0' if the QEBPOL bit is set to '0' and the SWPAB bit is set to '1'; physical pin, QEAx, is at logic '1' if the QEBPOL bit is set to '1' and the SWPAB bit is set to '1'

bit 0 QEA: Status of QEAx Input Pin After Polarity Control and SWPAB Pin Swapping bit (read-only)

- 1 = Physical pin, QEAx, is at logic '1' if the QEAPOL bit is set to '0' and the SWPAB bit is set to '0'; physical pin, QEAx, is at logic '0' if the QEAPOL bit is set to '1' and the SWPAB bit is set to '0'; physical pin, QEBx, is at logic '1' if the QEAPOL bit is set to '0' and the SWPAB bit is set to '1'; physical pin, QEBx, is at logic '0' if the QEAPOL bit is set to '1' and the SWPAB bit is set to '1'

- 0 = Physical pin, QEAx, is at logic '0' if the QEAPOL bit is set to '0' and the SWPAB bit is set to '0'; physical pin, QEAx, is at logic '1' if the QEAPOL bit is set to '1' and the SWPAB bit is set to '0'; physical pin, QEBx, is at logic '0' if the QEAPOL bit is set to '0' and the SWPAB bit is set to '1'

#### REGISTER 13-16: UxSCINT: UARTX SMART CARD INTERRUPT REGISTER

| U-0    | U-0 | HS/R/W-0 | HS/R/W-0 | U-0 | HS/R/W-0 | HS/R/W-0 | HS/R/W-0 |

|--------|-----|----------|----------|-----|----------|----------|----------|

| _      | _   | RXRPTIF  | TXRPTIF  | _   | BTCIF    | WTCIF    | GTCIF    |

| bit 15 |     |          |          |     |          |          | bit 8    |

| U-0   | U-0 | R/W-0   | R/W-0   | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|---------|---------|-----|-------|-------|-------|

| _     | _   | RXRPTIE | TXRPTIE | _   | BTCIE | WTCIE | GTCIE |

| bit 7 |     |         |         |     |       |       | bit 0 |

**Legend:** HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 RXRPTIF: Receive Repeat Interrupt Flag bit

1 = Parity error has persisted after the same character has been received five times (four retransmits)

0 = Flag is cleared

bit 12 TXRPTIF: Transmit Repeat Interrupt Flag bit

1 = Line error has been detected after the last retransmit per TXRPT<1:0>

0 = Flag is cleared

bit 11 Unimplemented: Read as '0'

bit 10 BTCIF: Block Time Counter Interrupt Flag bit

1 = Block Time Counter has reached 0

0 = Block Time Counter has not reached 0

bit 9 WTCIF: Waiting Time Counter Interrupt Flag bit

1 = Waiting Time Counter has reached 0

0 = Waiting Time Counter has not reached 0

bit 8 GTCIF: Guard Time Counter Interrupt Flag bit

1 = Guard Time Counter has reached 0

0 = Guard Time Counter has not reached 0

bit 7-6 **Unimplemented:** Read as '0'

bit 5 RXRPTIE: Receive Repeat Interrupt Enable bit

1 = An interrupt is invoked when a parity error has persisted after the same character has been

received five times (four retransmits)

0 = Interrupt is disabled

bit 4 **TXRPTIE:** Transmit Repeat Interrupt Enable bit

1 = An interrupt is invoked when a line error is detected after the last retransmit per TXRPT<1:0> has

been completed

0 = Interrupt is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2 BTCIE: Block Time Counter Interrupt Enable bit

1 = Block Time Counter interrupt is enabled

0 = Block Time Counter interrupt is disabled

bit 1 WTCIE: Waiting Time Counter Interrupt Enable bit

1 = Waiting Time Counter interrupt is enabled

0 = Waiting Time Counter Interrupt is disabled

bit 0 GTCIE: Guard Time Counter interrupt enable bit

1 = Guard Time Counter interrupt is enabled

0 = Guard Time Counter interrupt is disabled

### REGISTER 16-1: SENTxCON1: SENTx CONTROL REGISTER 1 (CONTINUED)

bit 4 PS: SENTx Module Clock Prescaler (divider) bits

1 = Divide-by-4

0 = Divide-by-1

bit 3 **Unimplemented:** Read as '0'

bit 2-0 NIBCNT<2:0>: Nibble Count Control bits

111 = Reserved; do not use

110 = Module transmits/receives six data nibbles in a SENT data pocket

101 = Module transmits/receives five data nibbles in a SENT data pocket

100 = Module transmits/receives four data nibbles in a SENT data pocket

011 = Module transmits/receives three data nibbles in a SENT data pocket

010 = Module transmits/receives two data nibbles in a SENT data pocket

001 = Module transmits/receives one data nibble in a SENT data pocket

000 = Reserved; do not use

Note 1: This bit has no function in Receive mode (RCVEN = 1).

2: This bit has no function in Transmit mode (RCVEN = 0).

# 18.0 CONFIGURABLE LOGIC CELL (CLC)

Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. For more information, refer to "Configurable Logic Cell (CLC)" (DS70005298) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- 2: The CLC is identical for both Master core and Slave core (where the x represents the number of the specific module being addressed in Master or Slave).

- 3: All associated register names are the same on the Master core and the Slave core. The Slave code will be developed in a separate project in MPLAB<sup>®</sup> X IDE with the device selection, dsPIC33CH128MP508S1, where the S1 indicates the Slave device. The Master and Slave are CLC1 and CLC2.

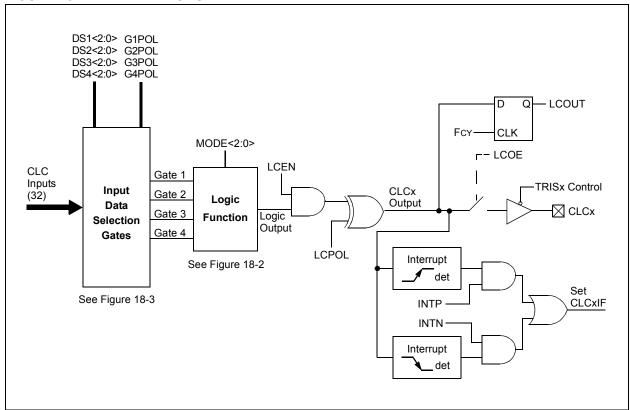

The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins. This provides greater flexibility and potential in embedded designs, since the CLC module can operate outside the limitations of software execution, and supports a vast amount of output designs.

There are four input gates to the selected logic function. These four input gates select from a pool of up to 32 signals that are selected using four data source selection multiplexers. Table 18-1 shows an overview of the module.

**TABLE 18-1: CLC MODULE OVERVIEW**

|        | Number of CLC<br>Modules | ldentical<br>(Modules) |  |  |

|--------|--------------------------|------------------------|--|--|

| Master | 4                        | Yes                    |  |  |

| Slave  | 4                        | Yes                    |  |  |

Figure 18-3 shows the details of the data source multiplexers and Figure 18-2 shows the logic input gate connections.

#### FIGURE 18-1: CLCx MODULE

TABLE 24-7: DC CHARACTERISTICS: OPERATING CURRENT (IDD) (MASTER RUN/SLAVE SLEEP)

| DC CHARACTERISTICS                     | Master (Run) +<br>Slave (Sleep) |      | (unless o       | Operating Co<br>therwise stat<br>temperature | •    |                                                                                   |  |  |  |

|----------------------------------------|---------------------------------|------|-----------------|----------------------------------------------|------|-----------------------------------------------------------------------------------|--|--|--|

| Parameter No.                          | Тур.                            | Max. | Units Condition |                                              |      | itions                                                                            |  |  |  |

| Operating Current (IDD) <sup>(1)</sup> |                                 |      |                 |                                              |      |                                                                                   |  |  |  |

| DC20b                                  | 7.9                             | 9.8  | mA              | -40°C                                        |      | 10 MIPS (N = 1, N2 = 5,                                                           |  |  |  |

|                                        | 8.0                             | 13.4 | mA              | +25°C                                        | 3.3V | N3 = 2, M = 50,                                                                   |  |  |  |

|                                        | 8.2                             | 19.5 | mA              | +85°C                                        | 3.3V | Fvco = 400 MHz,                                                                   |  |  |  |

|                                        | 12.2                            | 26.3 | mA              | +125°C                                       |      | FPLLO = 40 MHz)                                                                   |  |  |  |

| DC21b                                  | 10.3                            | 12.4 | mA              | -40°C                                        |      | 20 MIPS (N = 1, N2 = 5,                                                           |  |  |  |

|                                        | 10.5                            | 16.0 | mA              | +25°C                                        | 3.3V | N3 = 1, M = 50,<br>Fvco = 400 MHz,                                                |  |  |  |

|                                        | 10.6                            | 22.1 | mA              | +85°C                                        |      |                                                                                   |  |  |  |

|                                        | 14.6                            | 28.7 | mA              | +125°C                                       |      | FPLLO = 80 MHz)                                                                   |  |  |  |

| DC22b                                  | 14.2                            | 16.5 | mA              | -40°C                                        |      | 40 MIPS (N = 1, N2 = 3,                                                           |  |  |  |

|                                        | 14.4                            | 20.3 | mA              | +25°C                                        | 3.3V | N3 = 1, M = 60,                                                                   |  |  |  |

|                                        | 14.5                            | 26.3 | mA              | +85°C                                        | 3.30 | Fvco = 480 MHz,<br>Fpllo = 160 MHz)                                               |  |  |  |

|                                        | 18.4                            | 32.6 | mA              | +125°C                                       |      |                                                                                   |  |  |  |

| DC23b                                  | 22.3                            | 25.4 | mA              | -40°C                                        |      | 70 MIPS (N = 1, N2 = 2,<br>N3 = 1, M = 70,<br>Fvco = 560 MHz,<br>FPLLO = 280 MHz) |  |  |  |

|                                        | 22.5                            | 29.4 | mA              | +25°C                                        | 3.3V |                                                                                   |  |  |  |

|                                        | 22.4                            | 34.9 | mA              | +85°C                                        | 3.3V |                                                                                   |  |  |  |

|                                        | 26.4                            | 40.7 | mA              | +125°C                                       |      |                                                                                   |  |  |  |

| DC24b                                  | 25.6                            | 29.0 | mA              | -40°C                                        |      | 90 MIPS (N = 1, N2 = 2,                                                           |  |  |  |

|                                        | 25.8                            | 33.1 | mA              | +25°C                                        | 3.3V | N3 = 1, M = 90,                                                                   |  |  |  |

|                                        | 25.7                            | 38.2 | mA              | +85°C                                        | 3.30 | Fvco = 720 MHz,<br>Fpllo = 360 MHz)                                               |  |  |  |

|                                        | 29.4                            | 43.8 | mA              | +125°C                                       |      |                                                                                   |  |  |  |

- **Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- FIN = 8 MHz, FPFD = 8 MHz

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as output low

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- · No peripheral modules are operating or being clocked (all defined PMDx bits are set)

- CPU is executing while(1) statement

- · JTAG is disabled

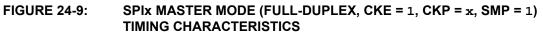

TABLE 24-36: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING REQUIREMENTS

| TIMING REGUINEMENTS                            |                       |                                           |                                                                                                                                                                                                                                                  |                     |      |       |                             |  |

|------------------------------------------------|-----------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| AC CHARACTERISTICS                             |                       |                                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                             |  |

| Param No. Symbol Characteristic <sup>(1)</sup> |                       | Characteristic <sup>(1)</sup>             | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10                                           | FscP                  | Maximum SCKx Frequency                    | _                                                                                                                                                                                                                                                | _                   | 15   | MHz   | Using PPS pins              |  |

|                                                |                       |                                           | _                                                                                                                                                                                                                                                | _                   | 40   | MHz   | SPI2 dedicated pins         |  |

| SP20                                           | TscF                  | SCKx Output Fall Time                     | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 3) |  |

| SP21                                           | TscR                  | SCKx Output Rise Time                     | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 3) |  |

| SP30                                           | TdoF                  | SDOx Data Output Fall<br>Time             | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 3) |  |

| SP31                                           | TdoR                  | SDOx Data Output Rise<br>Time             | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 3) |  |

| SP35                                           | TscH2doV,<br>TscL2doV | SDOx Data Output Valid<br>After SCKx Edge | _                                                                                                                                                                                                                                                | 6                   | 20   | ns    |                             |  |

| SP36                                           | TdoV2sc,              | SDOx Data Output Setup                    | 30                                                                                                                                                                                                                                               | _                   | _    | ns    | Using PPS pins              |  |

|                                                | TdoV2scL              | to First SCKx Edge                        | 3                                                                                                                                                                                                                                                | _                   | _    | ns    | SPI2 dedicated pins         |  |

| SP40                                           | TdiV2scH,             | Setup Time of SDIx Data                   | 30                                                                                                                                                                                                                                               |                     |      | ns    | Using PPS pins              |  |

| TdiV2scL                                       | TdiV2scL              | Input to SCKx Edge                        | 20                                                                                                                                                                                                                                               |                     |      | ns    | SPI2 dedicated pins         |  |

| SP41                                           | TscH2diL,             | Hold Time of SDIx Data                    | 30                                                                                                                                                                                                                                               | _                   |      | ns    | Using PPS pins              |  |

|                                                | TscL2diL              | Input to SCKx Edge                        | 15                                                                                                                                                                                                                                               | _                   | _    | ns    | SPI2 dedicated pins         |  |

Note 1: These parameters are characterized but not tested in manufacturing.

- 2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

- 3: Assumes 50 pF load on all SPIx pins.

### 25.1 Package Marking Information (Continued)

48-Lead TQFP (7x7 mm)

Example

CH64MP 2041810 017

48-Lead UQFN (6x6 mm)

Example

64-Lead TQFP (10x10x1 mm)

Example

64-Lead QFN (9x9x0.9 mm)

Example

80-Lead TQFP (12x12x1 mm)

Example