Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 27                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

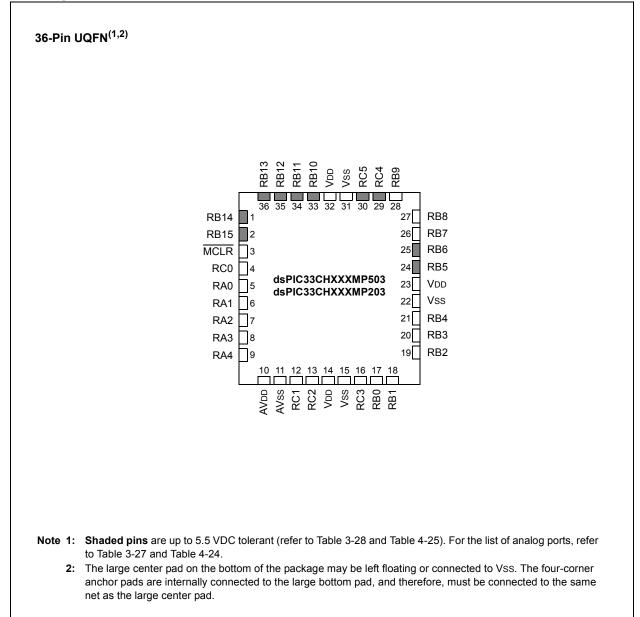

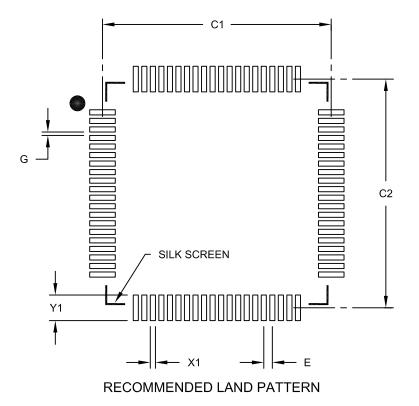

| Package / Case             | 36-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 36-UQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp203-i-m5 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33CH128MP508 FAMILY

## Pin Diagrams (Continued)

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------|

|------------|-------------------------------------|

| Pin Name <sup>(1)</sup>                                                        | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                                                                                      |  |  |  |

|--------------------------------------------------------------------------------|-------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MCLR/S1MCLR1/S1MCLR2/<br>S1MCLR3                                               | I/P         | ST             | No  | Master <u>Clear (Res</u> et) input. This pin is an active-low Reset to t<br>device. S1MCLRx is valid only for slave debug in Dual Debug<br>mode. |  |  |  |

| AVDD                                                                           | Р           | Ρ              | No  | Positive supply for analog modules. This pin must be connected at a times.                                                                       |  |  |  |

| AVss                                                                           | Р           | Р              | No  | Ground reference for analog modules. This pin must be connected at all times.                                                                    |  |  |  |

| Vdd                                                                            | Р           |                | No  | Positive supply for peripheral logic and I/O pins                                                                                                |  |  |  |

| Vss                                                                            | Р           | _              | No  | Ground reference for logic and I/O pins                                                                                                          |  |  |  |

| Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power |             |                |     |                                                                                                                                                  |  |  |  |

ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

**2:** These pins are remappable as well as dedicated. Some of the pins are associated with the Slave function and have S1 attached to the beginning of the name. For example, AN0 for the Slave is S1AN0.

**3:** S1 attached to the beginning of the name indicates the Slave feature for that function. For example, AN0 for the Slave is S1AN0.

#### REGISTER 3-28: CNPUX: CHANGE NOTIFICATION PULL-UP ENABLE FOR PORTX REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | CNPL  | Jx<15:8>                                |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

|                 |       |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | CNP   | Ux<7:0>                                 |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

|                 |       |                  |       |                                         |       |       |       |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable I  | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 CNPUx<15:0>: Change Notification Pull-up Enable for PORTx bits

1 = The pull-up for PORTx[n] is enabled – takes precedence over the pull-down selection

0 = The pull-up for PORTx[n] is disabled

#### REGISTER 3-29: CNPDx: CHANGE NOTIFICATION PULL-DOWN ENABLE FOR PORTx REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| CNPDx<15:8> |       |       |       |       |       |       |       |  |

| bit 15      |       |       |       |       |       |       | bit 8 |  |

|             |       |       |       |       |       |       |       |  |

| R/W-0      | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------------|-------|-------|-------|-------|-------|-------|--|--|

| CNPDx<7:0> |             |       |       |       |       |       |       |  |  |

| bit 7      | bit 7 bit 0 |       |       |       |       |       |       |  |  |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-0 CNPDx<15:0>: Change Notification Pull-Down Enable for PORTx bits

1 = The pull-down for PORTx[n] is enabled (if the pull-up for PORTx[n] is not enabled)

0 = The pull-down for PORTx[n] is disabled

#### **REGISTER 3-30: CNCONX: CHANGE NOTIFICATION CONTROL FOR PORTX REGISTER**

| R/W-0                                                                                                                                                                                                                                                             | U-0                             | U-0              | U-0                                                            | R/W-0                | U-0 | U-0                | U-0   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|----------------------------------------------------------------|----------------------|-----|--------------------|-------|--|

| ON                                                                                                                                                                                                                                                                |                                 | —                |                                                                | CNSTYLE              | —   | —                  | _     |  |

| bit 15                                                                                                                                                                                                                                                            |                                 |                  |                                                                |                      |     |                    | bit 8 |  |

|                                                                                                                                                                                                                                                                   |                                 |                  |                                                                |                      |     |                    |       |  |

| U-0                                                                                                                                                                                                                                                               | U-0                             | U-0              | U-0                                                            | U-0                  | U-0 | U-0                | U-0   |  |

|                                                                                                                                                                                                                                                                   |                                 | <u> </u>         | —                                                              | <u> </u>             | —   | <u> </u>           | —     |  |

| bit 7                                                                                                                                                                                                                                                             |                                 |                  |                                                                |                      |     |                    | bit 0 |  |

|                                                                                                                                                                                                                                                                   |                                 |                  |                                                                |                      |     |                    |       |  |

| Legend:                                                                                                                                                                                                                                                           |                                 |                  |                                                                |                      |     |                    |       |  |

| R = Readab                                                                                                                                                                                                                                                        | le bit                          | W = Writable     | <pre>/ = Writable bit U = Unimplemented bit, read as '0'</pre> |                      |     |                    |       |  |

| -n = Value a                                                                                                                                                                                                                                                      | t POR                           | '1' = Bit is set |                                                                | '0' = Bit is cleared |     | x = Bit is unknown |       |  |

|                                                                                                                                                                                                                                                                   |                                 |                  |                                                                |                      |     |                    |       |  |

| bit 15                                                                                                                                                                                                                                                            | ON: Change                      | Notification (CN | I) Control for                                                 | PORTx On bit         |     |                    |       |  |

|                                                                                                                                                                                                                                                                   | 1 = CN is ena<br>0 = CN is disa |                  |                                                                |                      |     |                    |       |  |

| bit 14-12                                                                                                                                                                                                                                                         | Unimplemen                      | ted: Read as '   | )'                                                             |                      |     |                    |       |  |

| bit 11                                                                                                                                                                                                                                                            | CNSTYLE: C                      | hange Notificat  | ion Style Sele                                                 | ection bit           |     |                    |       |  |

| <ul> <li>1 = Edge style (detects edge transitions, CNFx&lt;15:0&gt; bits are used for a Change Notification event)</li> <li>0 = Mismatch style (detects change from last port read, CNSTATx&lt;15:0&gt; bits are used for a Change Notification event)</li> </ul> |                                 |                  |                                                                |                      |     |                    |       |  |

| bit 10-0 Unimplemented: Read as '0'                                                                                                                                                                                                                               |                                 |                  |                                                                |                      |     |                    |       |  |

|                                                                                                                                                                                                                                                                   |                                 |                  |                                                                |                      |     |                    |       |  |

#### REGISTER 3-31: CNEN0x: INTERRUPT CHANGE NOTIFICATION ENABLE FOR PORTX REGISTER

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------|-------|---------|-------|-------|-------|

|         |       |       | CNEN0 | x<15:8> |       |       |       |

| bit 15  |       |       |       |         |       |       | bit 8 |

|         |       |       |       |         |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | CNEN  | )x<7:0> |       |       |       |

| bit 7   |       |       |       |         |       |       | bit 0 |

|         |       |       |       |         |       |       |       |

| Legend: |       |       |       |         |       |       |       |

| =ogona.           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-0 **CNEN0x<15:0>:** Interrupt Change Notification Enable for PORTx bits 1 = Interrupt-on-change (from the last read value) is enabled for PORTx[n] 0 = Interrupt-on-change is disabled for PORTx[n]

DS70005319B-page 120

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| U2DSRR7 | U2DSRR6 | U2DSRR5 | U2DSRR4 | U2DSRR3 | U2DSRR2 | U2DSRR1 | U2DSRR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| R/W-0   |

| U2RXR7  | U2RXR6  | U2RXR5  | U2RXR4  | U2RXR3  | U2RXR2  | U2RXR1  | U2RXR0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

#### REGISTER 3-53: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-8

U2DSRR<7:0>: Assign UART2 Data-Set-Ready (U2DSR) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0

U2RXR<7:0>: Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits

See Table 3-30.

### REGISTER 3-54: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SCK1R7 | SCK1R6 | SCK1R5 | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SDI1R7 | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  | •      |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 SCK1R<7:0>: Assign SPI1 Clock Input (SCK1IN) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **SDI1R<7:0>:** Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits See Table 3-30.

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| REFOIR7 | REFOIR6 | REFOIR5 | REFOIR4 | REFOIR3 | REFOIR2 | REFOIR1 | REFOIR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| R/W-0   |

| SS1R7   | SS1R6   | SS1R5   | SS1R4   | SS1R3   | SS1R2   | SS1R1   | SS1R0   |

#### REGISTER 3-55: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **REFOIR<7:0>:** Assign Reference Clock Input (REFOI) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **SS1R<7:0>:** Assign SPI1 Slave Select (SS1) to the Corresponding RPn Pin bits See Table 3-30.

#### REGISTER 3-56: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SCK2R7 | SCK2R6 | SCK2R5 | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SDI2R7 | SDI2R6 | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 SCK2R<7:0>: Assign SPI2 Clock Input (SCK2IN) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **SDI2R<7:0>:** Assign SPI2 Data Input (SDI2) to the Corresponding RPn Pin bits See Table 3-30.

bit 7

bit 0

| U-0           | U-0            | U-0              | U-0          | U-0                                     | U-0             | U-0                                                     | U-0            |  |  |

|---------------|----------------|------------------|--------------|-----------------------------------------|-----------------|---------------------------------------------------------|----------------|--|--|

| —             | _              | _                | —            | —                                       | —               | _                                                       | _              |  |  |

| bit 15        |                |                  |              |                                         |                 |                                                         | bit 8          |  |  |

|               |                |                  |              |                                         |                 |                                                         |                |  |  |

| R/W-0         | R/W-0          | R/W-0            | R/W-0        | R/W-0                                   | R/W-0           | R/W-0                                                   | R/W-0          |  |  |

|               |                |                  | STEP2        | <7:0>                                   |                 |                                                         |                |  |  |

| bit 7         |                |                  |              |                                         |                 |                                                         | bit 0          |  |  |

|               |                |                  |              |                                         |                 |                                                         |                |  |  |

| Legend:       |                |                  |              |                                         |                 |                                                         |                |  |  |

| R = Readable  | e bit          | W = Writable     | bit          | U = Unimplei                            | mented bit, rea | ad as '0'                                               |                |  |  |

| -n = Value at | POR            | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is unknown |                 |                                                         |                |  |  |

|               |                |                  |              |                                         |                 |                                                         |                |  |  |

| bit 15-8      | Unimplemen     | ted: Read as '   | )'           |                                         |                 |                                                         |                |  |  |

| bit 7-0       | STEP2<7:0>:    | DMT Clear Tir    | ner bits     |                                         |                 |                                                         |                |  |  |

|               | 00001000       | •                | e STEP1<7:0> | bits in the corre                       | ect sequence.   | ner if preceded<br>The write to the<br>ng the counter I | se bits may be |  |  |

|               | All Other      |                  |              |                                         |                 |                                                         |                |  |  |

|               | Write Patterns | •                |              |                                         |                 | ain unchanged<br>hese bits are cl                       |                |  |  |

|               |                |                  |              |                                         |                 |                                                         |                |  |  |

## REGISTER 3-93: DMTCLR: DEADMAN TIMER CLEAR REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | —   | -   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| HC/R-0 | HC/R-0 | HC/R-0   | U-0 | U-0 | U-0 | U-0 | R-0    |

|--------|--------|----------|-----|-----|-----|-----|--------|

| BAD1   | BAD2   | DMTEVENT | —   | —   | —   | —   | WINOPN |

| bit 7  |        |          |     |     |     |     | bit 0  |

| Legend:           | HC = Hardware Clearable bit                         |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                             |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Deadman Timer Bad STEP1<7:0> Value Detect bit                                                                                                                                                                    |

|          | 1 = Incorrect STEP1<7:0> value was detected<br>0 = Incorrect STEP1<7:0> value was not detected                                                                                                                         |

| bit 6    | BAD2: Deadman Timer Bad STEP2<7:0> Value Detect bit                                                                                                                                                                    |

|          | 1 = Incorrect STEP2<7:0> value was detected<br>0 = Incorrect STEP2<7:0> value was not detected                                                                                                                         |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                                                                                                      |

|          | <ul> <li>1 = Deadman Timer event was detected (counter expired, or bad STEP1&lt;7:0&gt; or STEP2&lt;7:0&gt; value was entered prior to counter increment)</li> <li>0 = Deadman Timer event was not detected</li> </ul> |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                                                                                                             |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                                                                                                                 |

|          | 1 = Deadman Timer clear window is open                                                                                                                                                                                 |

|          | 0 = Deadman Timer clear window is not open                                                                                                                                                                             |

|          |                                                                                                                                                                                                                        |

| U-0           | U-0                                                                                                                                                                                                                                                                               | U-0               | U-0            | U-0              | U-0                                     | R/W-0    | R/W-0   |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|------------------|-----------------------------------------|----------|---------|--|

| _             | —                                                                                                                                                                                                                                                                                 | —                 | _              | _                | —                                       | EDGFLTEN | SID11EN |  |

| bit 15        |                                                                                                                                                                                                                                                                                   |                   |                |                  |                                         |          | bit 8   |  |

|               |                                                                                                                                                                                                                                                                                   |                   |                |                  |                                         |          |         |  |

| U-0           | U-0                                                                                                                                                                                                                                                                               | U-0               | U-0            | U-0              | U-0                                     | R/W-1    | R/W-0   |  |

|               |                                                                                                                                                                                                                                                                                   | <u> </u>          | —              |                  |                                         | TDCMOD1  | TDCMOD0 |  |

| bit 7         |                                                                                                                                                                                                                                                                                   |                   |                |                  |                                         |          | bit 0   |  |

|               |                                                                                                                                                                                                                                                                                   |                   |                |                  |                                         |          |         |  |

| Legend:       |                                                                                                                                                                                                                                                                                   |                   |                |                  |                                         |          |         |  |

| R = Readabl   | e bit                                                                                                                                                                                                                                                                             | W = Writable b    | it             | U = Unimplei     | mented bit, rea                         | d as '0' |         |  |

| -n = Value at | t POR                                                                                                                                                                                                                                                                             | '1' = Bit is set  |                | '0' = Bit is cle | '0' = Bit is cleared x = Bit is unknown |          |         |  |

|               |                                                                                                                                                                                                                                                                                   |                   |                |                  |                                         |          |         |  |

| bit 15-10     | Unimplemen                                                                                                                                                                                                                                                                        | ted: Read as '0   | ,              |                  |                                         |          |         |  |

| bit 9         | EDGFLTEN:                                                                                                                                                                                                                                                                         | Enable Edge Fil   | tering During  | Bus Integratio   | n State bit                             |          |         |  |

|               | •                                                                                                                                                                                                                                                                                 | ring is enabled a | according to I | SO11898-1:20     | 15                                      |          |         |  |

|               | -                                                                                                                                                                                                                                                                                 | ring is disabled  |                | _                |                                         |          |         |  |

| bit 8         |                                                                                                                                                                                                                                                                                   | able 12-Bit SID   |                |                  | U                                       |          |         |  |

|               | 1 = RRS is used as SID11 in CAN FD base format messages: SID<11:0> = {SID<10:0>, SID11}<br>0 = Does not use RRS; SID<10:0>                                                                                                                                                        |                   |                |                  |                                         |          |         |  |

| bit 7-2       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                        |                   |                |                  |                                         |          |         |  |

| bit 1-0       | <b>TDCMOD&lt;1:0&gt;:</b> Transmitter Delay Compensation Mode bits (Secondary Sample Point (SSP))<br>10-11 = Auto: Measures delay and adds TSEG1<4:0> (C1DBTCFGH<4:0>), adds TDCO<6:0><br>01 = Manual: Does not measure, uses TDCV<5:0> + TDCO<6:0> from register<br>00 = Disable |                   |                |                  |                                         |          |         |  |

|               | hia ragiatar aga a                                                                                                                                                                                                                                                                |                   |                |                  |                                         | >        |         |  |

## REGISTER 3-108: C1TDCH: CAN TRANSMITTER DELAY COMPENSATION REGISTER HIGH<sup>(1)</sup>

**Note 1:** This register can only be modified in Configuration mode (OPMOD<2:0> = 100).

## REGISTER 3-131: C1TXQCONL: CAN TRANSMIT QUEUE CONTROL REGISTER LOW

| U-0                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                          | U-0                                                                                                                                                                   | U-0                                                                | R/W-0                        | R/W-0           | R/W-0         |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------|-----------------|---------------|

| _                                                             | —                                                                                                                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                            |                                                                                                                                                                       |                                                                    | FRESET                       | TXREQ           | UINC          |

| bit 15                                                        |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                       |                                                                    |                              |                 | bit 8         |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                       |                                                                    |                              |                 |               |

| R-0                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                          | HS/C-0                                                                                                                                                                | U-0                                                                | R/W-0                        | U-0             | R/W-0         |

| TXEN                                                          | —                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                              | TXATIE                                                                                                                                                                |                                                                    | TXQEIE                       |                 | TXQNIE        |

| bit 7                                                         |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                       |                                                                    |                              |                 | bit (         |

| Legend:                                                       |                                                                                                                                                                                                                                                                                                                                                                                               | HS = Hardware                                                                                                                                                                                                                                                                                | e Settable bit                                                                                                                                                        | C = Clearable                                                      | e bit                        |                 |               |

| R = Readab                                                    | ole bit                                                                                                                                                                                                                                                                                                                                                                                       | W = Writable b                                                                                                                                                                                                                                                                               | it                                                                                                                                                                    | U = Unimpler                                                       | mented bit, read             | as '0'          |               |

| -n = Value a                                                  | It POR                                                                                                                                                                                                                                                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                                                                                                                             |                                                                                                                                                                       | '0' = Bit is cle                                                   | ared                         | x = Bit is unkr | nown          |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                       |                                                                    |                              |                 |               |

| bit 15-11                                                     | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                    | ted: Read as '0                                                                                                                                                                                                                                                                              | ,                                                                                                                                                                     |                                                                    |                              |                 |               |

| bit 10                                                        | FRESET: FIF                                                                                                                                                                                                                                                                                                                                                                                   | O Reset bit                                                                                                                                                                                                                                                                                  |                                                                                                                                                                       |                                                                    |                              |                 |               |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                       |                                                                    | ware when FIF                | O is reset; us  | er should po  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                               | this bit is clear b                                                                                                                                                                                                                                                                          | efore taking a                                                                                                                                                        | any action                                                         |                              |                 |               |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                       |                                                                    |                              |                 |               |

| hit 0                                                         | 0 = No effect                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                              | uggt bit                                                                                                                                                              |                                                                    |                              |                 |               |

| bit 9                                                         | TXREQ: Mes                                                                                                                                                                                                                                                                                                                                                                                    | sage Send Req                                                                                                                                                                                                                                                                                |                                                                                                                                                                       | will automatic                                                     | ally clear when              | all the messar  | nes queued i  |

| bit 9                                                         | TXREQ: Mess<br>1 = Requests                                                                                                                                                                                                                                                                                                                                                                   | sage Send Req<br>s sending a mes                                                                                                                                                                                                                                                             | ssage; the bit                                                                                                                                                        | will automatic                                                     | ally clear when              | all the messag  | ges queued i  |

| bit 9                                                         | TXREQ: Mess<br>1 = Requests<br>the TXQ                                                                                                                                                                                                                                                                                                                                                        | sage Send Req                                                                                                                                                                                                                                                                                | ssage; the bit<br>/ sent                                                                                                                                              |                                                                    | -                            | all the messag  | ges queued i  |

| bit 9<br>bit 8                                                | TXREQ: Mess<br>1 = Requests<br>the TXQ<br>0 = Clearing                                                                                                                                                                                                                                                                                                                                        | sage Send Req<br>s sending a mes<br>are successfully                                                                                                                                                                                                                                         | ssage; the bit<br>/ sent<br>le set ('1') will                                                                                                                         |                                                                    | -                            | all the messag  | ges queued i  |

|                                                               | TXREQ: Mess<br>1 = Requests<br>the TXQ<br>0 = Clearing<br>UINC: Increm                                                                                                                                                                                                                                                                                                                        | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi                                                                                                                                                                                                                   | ssage; the bit<br>/ sent<br>le set ('1') will<br>it                                                                                                                   | l request a me                                                     | ssage abort                  | all the messag  | ges queued i  |

| bit 8                                                         | TXREQ: Mess<br>1 = Requests<br>the TXQ<br>0 = Clearing<br>UINC: Increm                                                                                                                                                                                                                                                                                                                        | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO                                                                                                                                                                           | ssage; the bit<br>/ sent<br>le set ('1') will<br>it                                                                                                                   | l request a me                                                     | ssage abort                  | all the messag  | ges queued in |

|                                                               | TXREQ: Mess<br>1 = Requests<br>the TXQ<br>0 = Clearing<br>UINC: Increm<br>When this bit<br>TXEN: TX En                                                                                                                                                                                                                                                                                        | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO                                                                                                                                                                           | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr                                                                                                 | l request a me                                                     | ssage abort                  | all the messag  | ges queued in |

| bit 8<br>bit 7                                                | TXREQ: Mess<br>1 = Requests<br>the TXQ<br>0 = Clearing<br>UINC: Increm<br>When this bit<br>TXEN: TX En<br>Unimplemen                                                                                                                                                                                                                                                                          | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO<br>able bit                                                                                                                                                               | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr<br>,                                                                                            | l request a me                                                     | ssage abort<br>ngle message. | all the messag  | ges queued ir |

| bit 8<br>bit 7<br>bit 6-5                                     | <ul> <li>TXREQ: Mess</li> <li>1 = Requests<br/>the TXQ</li> <li>0 = Clearing</li> <li>UINC: Increm</li> <li>When this bit</li> <li>TXEN: TX En</li> <li>Unimplement</li> <li>TXATIE: Tran</li> <li>1 = Enables in</li> </ul>                                                                                                                                                                  | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO<br>able bit<br>ted: Read as '0<br>ismit Attempts Enterrupt                                                                                                                | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr<br>,                                                                                            | l request a me                                                     | ssage abort<br>ngle message. | all the messag  | ges queued ir |

| bit 8<br>bit 7<br>bit 6-5<br>bit 4                            | <ul> <li>TXREQ: Mession</li> <li>1 = Requests the TXQ</li> <li>0 = Clearing</li> <li>UINC: Increment When this bit</li> <li>TXEN: TX En</li> <li>Unimplement</li> <li>TXATIE: Trans</li> <li>1 = Enables in</li> <li>0 = Disables in</li> </ul>                                                                                                                                               | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ient Head/Tail bi<br>is set, the FIFO<br>able bit<br><b>ted:</b> Read as '0<br>ismit Attempts Enterrupt<br>interrupt                                                                                           | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr<br>,<br>xhausted Inte                                                                           | l request a me                                                     | ssage abort<br>ngle message. | all the messag  | ges queued ir |

| bit 8<br>bit 7<br>bit 6-5<br>bit 4<br>bit 3                   | <ul> <li>TXREQ: Mession</li> <li>1 = Requests the TXQ</li> <li>0 = Clearing</li> <li>UINC: Increment</li> <li>When this bit</li> <li>TXEN: TX En</li> <li>Unimplement</li> <li>1 = Enables in</li> <li>0 = Disables in</li> <li>Unimplement</li> </ul>                                                                                                                                        | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO<br>able bit<br><b>ted:</b> Read as '0<br>smit Attempts E<br>nterrupt<br>interrupt<br><b>ted:</b> Read as '0                                                               | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr<br>,<br>Exhausted Inte                                                                          | l request a me<br>rement by a sir<br>errupt Enable b               | ssage abort<br>ngle message. | all the messag  | ges queued in |

| bit 8<br>bit 7<br>bit 6-5                                     | <ul> <li>TXREQ: Messing</li> <li>1 = Requests the TXQ</li> <li>0 = Clearing</li> <li>UINC: Increment When this bit</li> <li>TXEN: TX En</li> <li>Unimplement</li> <li>TXATIE: Transing</li> <li>1 = Enables in</li> <li>0 = Disables in</li> <li>Unimplement</li> <li>TXQEIE: Transing</li> </ul>                                                                                             | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO<br>able bit<br><b>ted:</b> Read as '0<br>smit Attempts Enterrupt<br>interrupt<br><b>ted:</b> Read as '0<br>nsmit Queue En                                                 | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr<br>,<br>Exhausted Inte<br>,                                                                     | l request a me<br>rement by a sir<br>errupt Enable b               | ssage abort<br>ngle message. | all the messag  | ges queued in |

| bit 8<br>bit 7<br>bit 6-5<br>bit 4<br>bit 3                   | <ul> <li>TXREQ: Mession</li> <li>1 = Requests the TXQ</li> <li>0 = Clearing</li> <li>UINC: Increment When this bit</li> <li>TXEN: TX En</li> <li>Unimplement</li> <li>TXATIE: Trann</li> <li>1 = Enables in</li> <li>0 = Disables in</li> <li>Unimplement</li> <li>TXQEIE: Trans</li> <li>1 = Interrupt is</li> </ul>                                                                         | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO<br>able bit<br><b>ted:</b> Read as '0<br>smit Attempts E<br>nterrupt<br>interrupt<br><b>ted:</b> Read as '0                                                               | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr<br>,<br>Exhausted Inte<br>,<br>npty Interrupt<br>KQ empty                                       | l request a me<br>rement by a sir<br>errupt Enable b               | ssage abort<br>ngle message. | all the messag  | ges queued in |

| bit 8<br>bit 7<br>bit 6-5<br>bit 4<br>bit 3                   | <ul> <li>TXREQ: Mession</li> <li>1 = Requests the TXQ</li> <li>0 = Clearing</li> <li>UINC: Increment When this bit</li> <li>TXEN: TX En</li> <li>Unimplement</li> <li>TXATIE: Trann</li> <li>1 = Enables in</li> <li>0 = Disables in</li> <li>Unimplement</li> <li>TXQEIE: Trann</li> <li>1 = Interrupt is</li> <li>0 = Interrupt is</li> </ul>                                               | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO<br>able bit<br>ted: Read as '0<br>smit Attempts Enterrupt<br>interrupt<br>ted: Read as '0<br>nsmit Queue Enter<br>s enabled for TX                                        | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr<br>,<br>Exhausted Inte<br>,<br>npty Interrupt<br>XQ empty<br>XQ empty                           | l request a me<br>rement by a sir<br>errupt Enable b               | ssage abort<br>ngle message. | all the messag  | ges queued i  |

| bit 8<br>bit 7<br>bit 6-5<br>bit 4<br>bit 3<br>bit 2          | <ul> <li>TXREQ: Mession</li> <li>1 = Requests the TXQ</li> <li>0 = Clearing</li> <li>UINC: Increment When this bit</li> <li>TXEN: TX En</li> <li>Unimplement</li> <li>TXATIE: Transistication</li> <li>1 = Enables in</li> <li>0 = Disables in</li> <li>Unimplement</li> <li>TXQEIE: Transistication</li> <li>1 = Interrupt in</li> <li>0 = Interrupt in</li> <li>0 = Interrupt in</li> </ul> | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO<br>able bit<br><b>ted:</b> Read as '0<br>asmit Attempts Enterrupt<br>interrupt<br><b>ted:</b> Read as '0<br>asmit Queue Enter<br>s enabled for T2<br>s disabled for T2    | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr<br>,<br>Exhausted Inte<br>,<br>npty Interrupt<br>XQ empty<br>XQ empty<br>,                      | l request a me<br>rement by a sir<br>errupt Enable b<br>Enable bit | ssage abort<br>ngle message. | all the messag  | ges queued i  |

| bit 8<br>bit 7<br>bit 6-5<br>bit 4<br>bit 3<br>bit 2<br>bit 1 | <ul> <li>TXREQ: Mession</li> <li>1 = Requests the TXQ</li> <li>0 = Clearing</li> <li>UINC: Increment When this bit</li> <li>TXEN: TX En</li> <li>Unimplement</li> <li>TXATIE: Trann</li> <li>1 = Enables in</li> <li>0 = Disables in</li> <li>Unimplement</li> <li>TXQEIE: Trann</li> <li>1 = Interrupt is</li> <li>0 = Interrupt is</li> <li>0 = Interrupt is</li> </ul>                     | sage Send Req<br>s sending a mes<br>are successfully<br>the bit to '0' whi<br>ent Head/Tail bi<br>is set, the FIFO<br>able bit<br>ted: Read as '0<br>smit Attempts Enterrupt<br>interrupt<br>ted: Read as '0<br>nsmit Queue En<br>s enabled for T2<br>s disabled for T2<br>s disabled for T2 | ssage; the bit<br>/ sent<br>le set ('1') will<br>it<br>head will incr<br>,<br>Exhausted Inter<br>,<br>Apty Interrupt<br>XQ empty<br>XQ empty<br>,<br>ot Full Interrup | l request a me<br>rement by a sir<br>errupt Enable b<br>Enable bit | ssage abort<br>ngle message. | all the messag  | ges queued i  |

| R/W-0   | U-0   | R/W-0         | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|---------|-------|---------------|--------|---------------------|-----|-------|-------|

| VAR     | —     | US1           | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15  |       |               |        |                     |     |       | bit 8 |

|         |       |               |        |                     |     |       |       |

| R/W-0   | R/W-0 | R/W-1         | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA    | SATB  | SATDW         | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7   |       |               |        |                     |     |       | bit 0 |

|         |       |               |        |                     |     |       |       |

| Legend: |       | C = Clearable | bit    |                     |     |       |       |

## REGISTER 4-17: CORCON: SLAVE CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                                    |                    |  |

|-------------------|-------------------|------------------------------------|--------------------|--|