Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 39                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 31x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

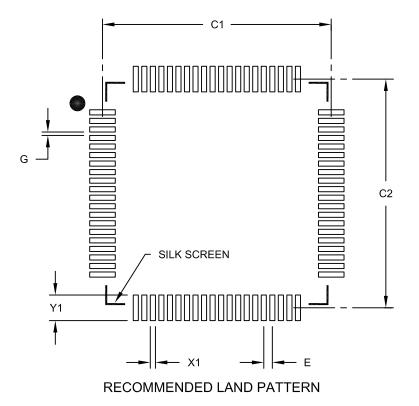

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-TQFP                                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp205-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Feature                      | Master Core       | Slave Core                      | Shared |

|------------------------------|-------------------|---------------------------------|--------|

| Core Frequency               | 90 MIPS @ 180 MHz | 100 MIPS @ 200 MHz              | _      |

| Program Memory               | 64K-128 Kbytes    | 24 Kbytes (PRAM) <sup>(2)</sup> | _      |

| Internal Data RAM            | 16 Kbytes         | 4 Kbytes                        | _      |

| 16-Bit Timer                 | 1                 | 1                               | _      |

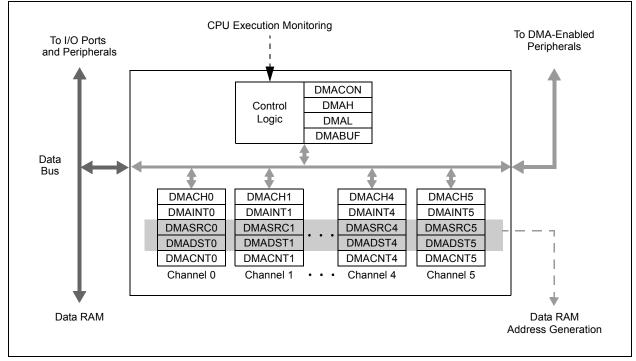

| DMA                          | 6                 | 2                               | _      |

| SCCP (Capture/Compare/Timer) | 8                 | 4                               | _      |

| UART                         | 2                 | 1                               | _      |

| SPI/I <sup>2</sup> S         | 2                 | 1                               | _      |

| I <sup>2</sup> C             | 2                 | 1                               | _      |

| CAN FD                       | 1                 | _                               | _      |

| SENT                         | 2                 | _                               | _      |

| CRC                          | 1                 | —                               | _      |

| QEI                          | 1                 | 1                               | _      |

| PTG                          | 1                 | _                               | _      |

| CLC                          | 4                 | 4                               | _      |

| 16-Bit High-Speed PWM        | 4                 | 8                               | _      |

| ADC 12-Bit                   | 1                 | 3                               | _      |

| Digital Comparator           | 4                 | 4                               | _      |

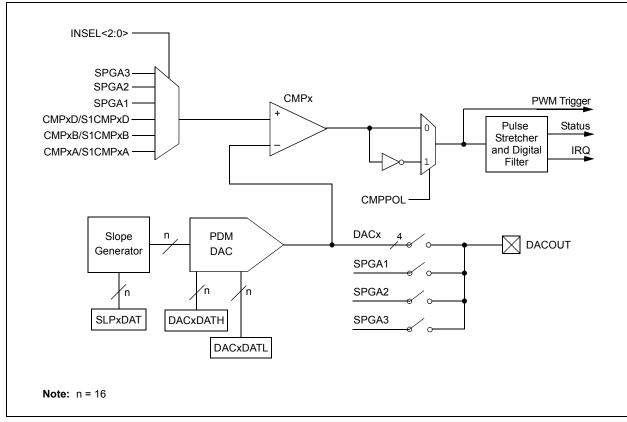

| 12-Bit DAC/Analog CMP Module | 1                 | 3                               | _      |

| Watchdog Timer               | 1                 | 1                               | _      |

| Deadman Timer                | 1                 | —                               | _      |

| Input/Output                 | 69                | 69                              | 69     |

| Simple Breakpoints           | 5                 | 2                               | _      |

| PGAs <sup>(1)</sup>          | —                 | 3                               | 3      |

| DAC Output Buffer            | —                 |                                 | 1      |

| Oscillator                   | 1                 | 1                               | 1      |

#### TABLE 1: MASTER AND SLAVE CORE FEATURES

Note 1: Slave owns the peripheral/feature, but it is shared with the Master.

2: Dual Partition feature is available on Slave PRAM.

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------|

|------------|-------------------------------------|

| Pin Name <sup>(1)</sup>                                                        | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                                                                                 |  |  |  |  |  |

|--------------------------------------------------------------------------------|-------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MCLR/S1MCLR1/S1MCLR2/<br>S1MCLR3                                               | I/P         | ST             | No  | Master <u>Clear</u> (Reset) input. This pin is an active-low Reset to the device. S1MCLRx is valid only for slave debug in Dual Debug mode. |  |  |  |  |  |

| AVDD                                                                           | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times.                                                                |  |  |  |  |  |

| AVss                                                                           | Р           | Р              | No  | Ground reference for analog modules. This pin must be connected at all times.                                                               |  |  |  |  |  |

| Vdd                                                                            | Р           |                | No  | Positive supply for peripheral logic and I/O pins                                                                                           |  |  |  |  |  |

| Vss                                                                            | Р           | _              | No  | Ground reference for logic and I/O pins                                                                                                     |  |  |  |  |  |

| Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power |             |                |     |                                                                                                                                             |  |  |  |  |  |

ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

**2:** These pins are remappable as well as dedicated. Some of the pins are associated with the Slave function and have S1 attached to the beginning of the name. For example, AN0 for the Slave is S1AN0.

**3:** S1 attached to the beginning of the name indicates the Slave feature for that function. For example, AN0 for the Slave is S1AN0.

## 3.4.2 RESET CONTROL REGISTER

## REGISTER 3-15: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0                | U-0                                 | U-0            | U-0                   | U-0              | R/W-0            | R/W-0        |

|-----------------|----------------------|-------------------------------------|----------------|-----------------------|------------------|------------------|--------------|

| TRAPR           | IOPUWR               | —                                   | —              | _                     | —                | CM               | VREGS        |

| bit 15          |                      |                                     |                |                       |                  |                  | bit 8        |

| R/W-0           | R/W-0                | U-0                                 | R/W-0          | R/W-0                 | R/W-0            | R/W-1            | R/W-1        |

| EXTR            | SWR                  |                                     | WDTO           | SLEEP                 | IDLE             | BOR              | POR          |

| bit 7           | own                  |                                     | WBIO           | OLLLI                 | IDEE             | Bolt             | bit (        |

|                 |                      |                                     |                |                       |                  |                  |              |

| Legend:         |                      |                                     |                |                       |                  |                  |              |

| R = Readable    | bit                  | W = Writable                        | bit            | U = Unimpler          | nented bit, read | l as '0'         |              |

| -n = Value at F | POR                  | '1' = Bit is set                    |                | '0' = Bit is cle      | ared             | x = Bit is unki  | nown         |

|                 |                      | Deest Flee bit                      |                |                       |                  |                  |              |

| bit 15          |                      | Reset Flag bit                      |                |                       |                  |                  |              |

|                 |                      | onflict Reset ha                    |                | d                     |                  |                  |              |

| bit 14          | •                    |                                     |                |                       | ess Reset Flag   | bit              |              |

|                 |                      |                                     |                |                       | ode or Uninitial |                  | er used as a |

|                 | Address              | Pointer caused                      | l a Reset      |                       |                  | -                |              |

|                 | •                    | •                                   |                | Register Reset        | has not occurre  | d                |              |

| oit 13-10       | -                    | ted: Read as '                      |                |                       |                  |                  |              |

| oit 9           | •                    | ation Mismatch                      | •              |                       |                  |                  |              |

|                 |                      | ration Mismato                      |                |                       |                  |                  |              |

| oit 8           | VREGS: Volta         | age Regulator                       | Standby Durin  | ig Sleep bit          |                  |                  |              |

|                 | •                    | egulator is acti<br>equlator goes i | •              | ep<br>node during Sle | еер              |                  |              |

| oit 7           | -                    | al Reset (MCL                       |                | <b>3</b> -            | 1-               |                  |              |

|                 |                      | Clear (pin) Res<br>Clear (pin) Res  |                |                       |                  |                  |              |

| bit 6           |                      | re RESET (Inst                      |                |                       |                  |                  |              |

|                 | 1 <b>= A</b> reset i | instruction has instruction has     | been execute   | ed                    |                  |                  |              |

| oit 5           |                      | ted: Read as '                      |                |                       |                  |                  |              |

| oit 4           | -                    | hdog Timer Tin                      |                | ŀ                     |                  |                  |              |

|                 |                      | e-out has occur                     |                | -                     |                  |                  |              |

|                 | 0 = WDT time         | e-out has not o                     | ccurred        |                       |                  |                  |              |

| bit 3           | SLEEP: Wake          | e-up from Slee                      | p Flag bit     |                       |                  |                  |              |

|                 |                      | is been in Slee<br>is not been in S | -              |                       |                  |                  |              |

| bit 2           | IDLE: Wake-u         | up from Idle Fla                    | ag bit         |                       |                  |                  |              |

|                 | 1 = Device ha        | s been in Idle                      | mode           |                       |                  |                  |              |

| L:1 A           |                      | is not been in I                    |                |                       |                  |                  |              |

| bit 1           |                      | out Reset Flag                      |                |                       |                  |                  |              |

|                 |                      | out Reset has<br>out Reset has      |                |                       |                  |                  |              |

| Note 1: All     | of the Reset sta     | tue hite can he                     | set or cleared | t in coffwara. S      | etting one of th | oso hite in coft | wara daga na |

cause a device Reset.

## TABLE 3-23: MASTER INTERRUPT VECTOR DETAILS (CONTINUED)

|                                                       | Vector  | IRQ<br># |                   | Interrupt Bit Location |          |              |  |

|-------------------------------------------------------|---------|----------|-------------------|------------------------|----------|--------------|--|

| Interrupt Source                                      | #       |          | IVT Address       | Flag                   | Enable   | Priority     |  |

| ADCAN16 – ADC AN16 Interrupt                          | 115     | 107      | 0x0000EA          | IFS6<11>               | IEC6<11> | IPC26<14:12> |  |

| ADCAN17 – ADC AN17 Interrupt                          | 116     | 108      | 0x0000EC          | IFS6<12>               | IEC6<12> | IPC27<2:0>   |  |

| ADCAN18 – ADC AN18 Interrupt                          | 117     | 109      | 0x0000EE          | IFS6<13>               | IEC6<13> | IPC27<6:4>   |  |

| ADCAN19 – ADC AN19 Interrupt                          | 118     | 110      | 0x0000F0          | IFS6<14>               | IEC6<14> | IPC27<10:8>  |  |

| ADCAN20 – ADC AN20 Interrupt                          | 119     | 111      | 0x0000F2          | IFS6<15>               | IEC6<15> | IPC27<14:12> |  |

| Reserved                                              | 120-122 | 112-114  | 0x0000F4-0x0000F8 | _                      | _        | _            |  |

| ADFLT – ADC Fault                                     | 123     | 115      | 0x0000FA          | IFS7<3>                | IEC7<3>  | IPC28<14:12> |  |

| ADCMP0 – ADC Digital Comparator 0                     | 124     | 116      | 0x0000FC          | IFS7<4>                | IEC7<4>  | IPC29<2:0>   |  |

| ADCMP1 – ADC Digital Comparator 1                     | 125     | 117      | 0x0000FE          | IFS7<5>                | IEC7<5>  | IPC29<6:4>   |  |

| ADCMP2 – ADC Digital Comparator 2                     | 126     | 118      | 0x000100          | IFS7<6>                | IEC7<6>  | IPC29<10:8>  |  |

| ADCMP3 – ADC Digital Comparator 3                     | 127     | 119      | 0x000102          | IFS7<7>                | IEC7<7>  | IPC29<14:12> |  |

| ADFLTR0 – ADC Oversample Filter 0                     | 128     | 120      | 0x000104          | IFS7<8>                | IEC7<8>  | IPC30<2:0>   |  |

| ADFLTR1 – ADC Oversample Filter 1                     | 129     | 121      | 0x000106          | IFS7<9>                | IEC7<9>  | IPC30<6:4>   |  |

| ADFLTR2 – ADC Oversample Filter 2                     | 130     | 122      | 0x000108          | IFS7<10>               | IEC7<10> | IPC30<10:8>  |  |

| ADFLTR3 – ADC Oversample Filter 3                     | 131     | 123      | 0x00010A          | IFS7<11>               | IEC7<11> | IPC30<14:12> |  |

| CLC1P – CLC1 Positive Edge                            | 132     | 124      | 0x00010C          | IFS7<12>               | IEC7<12> | IPC31<2:0>   |  |

| CLC2P – CLC2 Positive Edge                            | 133     | 125      | 0x00010E          | IFS7<13>               | IEC7<13> | IPC31<6:4>   |  |

| SPI1G – SPI1 Error                                    | 134     | 126      | 0x000110          | IFS7<14>               | IEC7<14> | IPC31<10:8>  |  |

| SPI2G – SPI2 Error                                    | 135     | 127      | 0x000112          | IFS7<15>               | IEC7<15> | IPC31<14:12> |  |

| Reserved                                              | 136     | 128      | 0x000114          | —                      | _        | —            |  |

| MSIS1 – MSI Slave Initiated Interrupt                 | 137     | 129      | 0x000116          | IFS8<1>                | IEC8<1>  | IPC32<6:4>   |  |

| MSIA – MSI Protocol A                                 | 138     | 130      | 0x000118          | IFS8<2>                | IEC8<2>  | IPC32<10:8>  |  |

| MSIB – MSI Protocol B                                 | 139     | 131      | 0x00011A          | IFS8<3>                | IEC8<3>  | IPC32<14:12> |  |

| MSIC – MSI Protocol C                                 | 140     | 132      | 0x00011C          | IFS8<4>                | IEC8<4>  | IPC33<2:0>   |  |

| MSID – MSI Protocol D                                 | 141     | 133      | 0x00011E          | IFS8<5>                | IEC8<5>  | IPC33<6:4>   |  |

| MSIE – MSI Protocol E                                 | 142     | 134      | 0x000120          | IFS8<6>                | IEC8<6>  | IPC33<10:8>  |  |

| MSIF – MSI Protocol F                                 | 143     | 135      | 0x000122          | IFS8<7>                | IEC8<7>  | IPC33<14:12> |  |

| MSIG – MSI Protocol G                                 | 144     | 136      | 0x000124          | IFS8<8>                | IEC8<8>  | IPC34<2:0>   |  |

| MSIH – MSI Protocol H                                 | 145     | 137      | 0x000126          | IFS8<9>                | IEC8<9>  | IPC34<6:4>   |  |

| MSIDT – Master Read FIFO Data Ready                   | 146     | 138      | 0x000128          | IFS8<10>               | IEC8<10> | IPC34<10:8>  |  |

| MSIWFE – Master Write FIFO Empty                      | 147     | 139      | 0x00012A          | IFS8<11>               | IEC8<11> | IPC34<14:12> |  |

| MSIFLT – Read or Write FIFO Fault<br>(Over/Underflow) | 148     | 140      | 0x00012C          | IFS8<12>               | IEC8<12> | IPC35<2:0>   |  |

| S1SRST – MSI Slave Reset                              | 149     | 141      | 0x00012E          | IFS8<13>               | IEC8<13> | IPC35<6:4>   |  |

| Reserved                                              | 150-153 | 142-145  | 0x000130-0x000136 | —                      | —        | —            |  |

| S1BRK – Slave Break                                   | 154     | 146      | 0x000138          | IFS9<2>                | IEC9<2>  | IPC36<10:8>  |  |

| Reserved                                              | 155-156 | 147-148  | 0x00013A-0x00013C | —                      | —        | —            |  |

| CCP7 – Input Capture/Output Compare 7                 | 157     | 149      | 0x00013E          | IFS9<5>                | IEC9<5>  | IPC37<6:4>   |  |

| CCT7 – CCP7 Timer                                     | 158     | 150      | 0x000140          | IFS9<6>                | IEC9<6>  | IPC37<10:8>  |  |

| Reserved                                              | 159     | 151      | 0x000142          | —                      |          | —            |  |

| CCP8 – Input Capture/Output Compare 8                 | 160     | 152      | 0x000144          | IFS9<8>                | IEC9<8>  | IPC38<2:0>   |  |

| CCT8 – CCP8 Timer                                     | 161     | 153      | 0x000146          | IFS9<9>                | IEC9<9>  | IPC38<6:4>   |  |

| Reserved                                              | 162-164 | 154-156  | 0x000148-0x00014C | —                      |          | —            |  |

| S1CLKF – Slave Clock Fail                             | 165     | 157      | 0x00014E          | IFS9<13>               | IEC9<13> | IPC39<6:4>   |  |

| Reserved                                              | 166-175 | 158-167  | 0x000150-0x000162 | —                      | —        | —            |  |

| ADFIFO – ADC FIFO Ready                               | 176     | 168      | 0x000164          | IFS10<8>               | IEC10<8> | IPC42<2:0>   |  |

Unimplemented: Read as '0'

Unimplemented: Read as '0'

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|-----|------------------|--------|------------------|------------------|-----------------|--------|

| —               | —   | RP33R5           | RP33R4 | RP33R3           | RP33R2           | RP33R1          | RP33R0 |

| bit 15          |     | -                |        | ÷                | •                |                 | bit 8  |

|                 |     |                  |        |                  |                  |                 |        |

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| —               | —   | RP32R5           | RP32R4 | RP32R3           | RP32R2           | RP32R1          | RP32R0 |

| bit 7           |     |                  |        |                  |                  |                 | bit 0  |

|                 |     |                  |        |                  |                  |                 |        |

| Legend:         |     |                  |        |                  |                  |                 |        |

| R = Readable    | bit | W = Writable     | bit    | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value at F | POR | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

RP33R<5:0>: Peripheral Output Function is Assigned to RP33 Output Pin bits

RP32R<5:0>: Peripheral Output Function is Assigned to RP32 Output Pin bits

## REGISTER 3-68: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| REGISTER 3-69 | RPOR1 | PFRIPHFRAI | PIN SELE | ΕСТ ΟΠΤΡΠΤ | REGISTER 1 |

|---------------|-------|------------|----------|------------|------------|

(see Table 3-33 for peripheral function numbers)

(see Table 3-33 for peripheral function numbers)

| U-0                                | U-0         | R/W-0          | R/W-0            | R/W-0                              | R/W-0              | R/W-0    | R/W-0  |

|------------------------------------|-------------|----------------|------------------|------------------------------------|--------------------|----------|--------|

| _                                  | —           | RP35R5         | RP35R4           | RP35R3                             | RP35R2             | RP35R1   | RP35R0 |

| bit 15                             |             |                |                  |                                    | ·                  |          | bit 8  |

|                                    |             |                |                  |                                    |                    |          |        |

| U-0                                | U-0         | R/W-0          | R/W-0            | R/W-0                              | R/W-0              | R/W-0    | R/W-0  |

| —                                  | —           | RP34R5         | RP34R4           | RP34R3                             | RP34R2             | RP34R1   | RP34R0 |

| bit 7                              |             | •              |                  |                                    |                    |          | bit 0  |

|                                    |             |                |                  |                                    |                    |          |        |

| Legend:                            |             |                |                  |                                    |                    |          |        |

| R = Readable                       | e bit       | W = Writable   | bit              | U = Unimplemented bit, read as '0' |                    |          |        |

| -n = Value at POR '1' = Bit is set |             |                | '0' = Bit is cle | ared                               | x = Bit is unknown |          |        |

|                                    |             |                |                  |                                    |                    |          |        |

| bit 15-14                          | Unimplemen  | ted: Read as ' | כ'               |                                    |                    |          |        |

| bit 13-8                           | RP35R<5:0>: | Peripheral Ou  | tput Function    | is Assigned to                     | RP35 Output F      | Pin bits |        |

(see Table 3-33 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP34R<5:0>:** Peripheral Output Function is Assigned to RP34 Output Pin bits (see Table 3-33 for peripheral function numbers)

bit 15-14

bit 13-8

bit 7-6

bit 5-0

Unimplemented: Read as '0'

Unimplemented: Read as '0'

(see Table 3-33 for peripheral function numbers)

(see Table 3-33 for peripheral function numbers)

| U-0             | U-0                                                              | R/W-0            | R/W-0                                            | R/W-0   | R/W-0  | R/W-0  | R/W-0    |

|-----------------|------------------------------------------------------------------|------------------|--------------------------------------------------|---------|--------|--------|----------|

| 0-0             | 0-0                                                              | N/ W-U           | N/VV-0                                           | N/ VV-U | N/W-0  | N/W-0  | N/ V V-U |

| —               | —                                                                | RP65R5           | RP65R4                                           | RP65R3  | RP65R2 | RP65R1 | RP65R0   |

| bit 15          |                                                                  |                  |                                                  |         |        |        | bit 8    |

|                 |                                                                  |                  |                                                  |         |        |        |          |

| U-0             | U-0                                                              | R/W-0            | R/W-0                                            | R/W-0   | R/W-0  | R/W-0  | R/W-0    |

| —               | —                                                                | RP64R5           | RP64R4                                           | RP64R3  | RP64R2 | RP64R1 | RP64R0   |

| bit 7           |                                                                  |                  |                                                  |         |        |        | bit 0    |

|                 |                                                                  |                  |                                                  |         |        |        |          |

| Legend:         |                                                                  |                  |                                                  |         |        |        |          |

| R = Readable    | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                                                  |         |        |        |          |

| -n = Value at P | POR                                                              | '1' = Bit is set | Bit is set'0' = Bit is clearedx = Bit is unknown |         |        | nown   |          |

RP65R<5:0>: Peripheral Output Function is Assigned to RP65 Output Pin bits

RP64R<5:0>: Peripheral Output Function is Assigned to RP64 Output Pin bits

## REGISTER 3-84: RPOR16: PERIPHERAL PIN SELECT OUTPUT REGISTER 16

| REGISTER 3-85: | <b>RPOR17: PERIPHERAL</b> | PIN SELECT OUTPUT REGISTER 17 |

|----------------|---------------------------|-------------------------------|

|                |                           |                               |

| U-0             | U-0                                                                                     | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0           | R/W-0              |  |  |

|-----------------|-----------------------------------------------------------------------------------------|------------------|--------|------------------------------------|--------|-----------------|--------------------|--|--|

| —               | —                                                                                       | RP67R5           | RP67R4 | RP67R3                             | RP67R2 | RP67R1          | RP67R0             |  |  |

| bit 15          |                                                                                         | •                |        |                                    |        |                 | bit 8              |  |  |

|                 |                                                                                         |                  |        |                                    |        |                 |                    |  |  |

| U-0             | U-0                                                                                     | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0           | R/W-0              |  |  |

| —               | —                                                                                       | RP66R5           | RP66R4 | RP66R3                             | RP66R2 | RP66R1          | RP66R0             |  |  |

| bit 7           |                                                                                         |                  |        |                                    |        |                 | bit 0              |  |  |

|                 |                                                                                         |                  |        |                                    |        |                 |                    |  |  |

| Legend:         |                                                                                         |                  |        |                                    |        |                 |                    |  |  |

| R = Readable    | bit                                                                                     | W = Writable     | bit    | U = Unimplemented bit, read as '0' |        |                 |                    |  |  |

| -n = Value at P | POR                                                                                     | '1' = Bit is set |        | '0' = Bit is cle                   | ared   | x = Bit is unkr | k = Bit is unknown |  |  |

|                 |                                                                                         |                  |        |                                    |        |                 |                    |  |  |

| bit 15-14       | Unimplemen                                                                              | ted: Read as '   | כי     |                                    |        |                 |                    |  |  |

| bit 13-8        | <b>RP67R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP67 Output Pin bits |                  |        |                                    |        |                 |                    |  |  |

(see Table 3-33 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP66R<5:0>:** Peripheral Output Function is Assigned to RP66 Output Pin bits (see Table 3-33 for peripheral function numbers)

bit 15-14

bit 13-8

bit 7-6

bit 5-0

## REGISTER 3-128: C1FIFOBAH: CAN MESSAGE MEMORY BASE ADDRESS REGISTER HIGH

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0           | R/W-0          | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------|-----------------|----------------|-------|-------|

|                                    |       |       | FIFOBA           | <31:24>         |                |       |       |

| bit 15                             |       |       |                  |                 |                |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0           | R/W-0          | R/W-0 | R/W-0 |

|                                    |       |       | FIFOBA           | <23:16>         |                |       |       |

| bit 7                              |       |       |                  |                 |                |       | bit 0 |

| Legend:                            |       |       |                  |                 |                |       |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimpler     | mented bit, rea | ad as '0'      |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared            | x = Bit is unk | nown  |       |

bit 15-0 **FIFOBA<31:16>:** Message Memory Base Address bits

Defines the base address for the transmit event FIFO followed by the message objects.

## REGISTER 3-129: C1FIFOBAL: CAN MESSAGE MEMORY BASE ADDRESS REGISTER LOW

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0   | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|---------|-----------------|-------|-------|

|                                    |       |       | FIFOB.                             | A<15:8> |                 |       |       |

| bit 15                             |       |       |                                    |         |                 |       | bit 8 |

|                                    |       |       |                                    |         |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0   | R/W-0           | R-0   | R-0   |

|                                    |       |       | FIFOE                              | 3A<7:0> |                 |       |       |

| bit 7                              |       |       |                                    |         |                 |       | bit C |

|                                    |       |       |                                    |         |                 |       |       |

| Legend:                            |       |       |                                    |         |                 |       |       |

| R = Readable bit W = Writable bit  |       | it    | U = Unimplemented bit, read as '0' |         |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle                   | ared    | x = Bit is unkr | nown  |       |

bit 15-0 **FIFOBA<15:0>:** Message Memory Base Address bits Defines the base address for the transmit event FIFO followed by the message objects.

| U-0                                 | U-0 | R/W-0  | R/W-0           | R/W-0           | R/W-0  | R/W-0  | R/W-0  |

|-------------------------------------|-----|--------|-----------------|-----------------|--------|--------|--------|

| _                                   | —   | RP33R5 | RP33R4          | RP33R3          | RP33R2 | RP33R1 | RP33R0 |

| bit 15                              |     |        |                 |                 |        |        | bit 8  |

|                                     |     |        |                 |                 |        |        |        |

| U-0                                 | U-0 | R/W-0  | R/W-0           | R/W-0           | R/W-0  | R/W-0  | R/W-0  |

| —                                   | —   | RP32R5 | RP32R4          | RP32R3          | RP32R2 | RP32R1 | RP32R0 |

| bit 7                               |     |        |                 |                 |        |        | bit 0  |

|                                     |     |        |                 |                 |        |        |        |

| Legend:                             |     |        |                 |                 |        |        |        |

| R = Readable bit $W = Writable bit$ |     | hit    | II = I Inimpler | mented hit read | as '0' |        |        |

## REGISTER 4-60: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP33R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP33 Output Pin bits (see Table 4-31 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | <b>RP32R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP32 Output Pin bits (see Table 4-31 for peripheral function numbers) |

## REGISTER 4-61: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0            | U-0 | R/W-0         | R/W-0  | R/W-0         | R/W-0           | R/W-0  | R/W-0  |

|----------------|-----|---------------|--------|---------------|-----------------|--------|--------|

| —              | —   | RP35R5        | RP35R4 | RP35R3        | RP35R2          | RP35R1 | RP35R0 |

| bit 15         |     |               |        |               |                 |        | bit 8  |

|                |     |               |        |               |                 |        |        |

| U-0            | U-0 | R/W-0         | R/W-0  | R/W-0         | R/W-0           | R/W-0  | R/W-0  |

| —              | —   | RP34R5        | RP34R4 | RP34R3        | RP34R2          | RP34R1 | RP34R0 |

| bit 7          |     |               |        | •             |                 |        | bit 0  |

|                |     |               |        |               |                 |        |        |

| Legend:        |     |               |        |               |                 |        |        |

| P - Poodablo I | bit | M = M/ritabla | hit    | II – Unimplor | monted hit read | 26 '0' |        |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP35R<5:0>:** Peripheral Output Function is Assigned to S1RP35 Output Pin bits (see Table 4-31 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP34R<5:0>:** Peripheral Output Function is Assigned to S1RP34 Output Pin bits (see Table 4-31 for peripheral function numbers)

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —      | —   | RP171R5 <sup>(1)</sup> | RP171R4 <sup>(1)</sup> | RP171R3 <sup>(1)</sup> | RP171R2 <sup>(1)</sup> | RP171R1 <sup>(1)</sup> | RP171R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —     | —   | RP170R5 <sup>(1)</sup> | RP170R4 <sup>(1)</sup> | RP170R3 <sup>(1)</sup> | RP170R2 <sup>(1)</sup> | RP170R1 <sup>(1)</sup> | RP170R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP171R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP171 Output Pin bits <sup>(1)</sup> |

|           | (see Table 4-31 for peripheral function numbers)                                                           |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP170R<5:0>:** Peripheral Output Function is Assigned to S1RP170 Output Pin bits<sup>(1)</sup> (see Table 4-31 for peripheral function numbers)

Note 1: These are virtual output ports.

| REGISTER 4-81: | <b>RPOR21: PERIPHERAL PIN SELECT OUTPUT REGISTER 21</b> |

|----------------|---------------------------------------------------------|

|----------------|---------------------------------------------------------|

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —      | —   | RP173R5 <sup>(1)</sup> | RP173R4 <sup>(1)</sup> | RP173R3 <sup>(1)</sup> | RP173R2 <sup>(1)</sup> | RP173R1 <sup>(1)</sup> | RP173R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —     | —   | RP172R5 <sup>(1)</sup> | RP172R4 <sup>(1)</sup> | RP172R3 <sup>(1)</sup> | RP172R2 <sup>(1)</sup> | RP172R1 <sup>(1)</sup> | RP172R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP173R<5:0>:** Peripheral Output Function is Assigned to S1RP173 Output Pin bits<sup>(1)</sup> (see Table 4-31 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP172R<5:0>:** Peripheral Output Function is Assigned to S1RP172 Output Pin bits<sup>(1)</sup> (see Table 4-31 for peripheral function numbers)

Note 1: These are virtual output ports.

## REGISTER 4-102: ADIEL: ADC INTERRUPT ENABLE REGISTER LOW

| R/W-0                                                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0          | R/W-0     | R/W-0 |

|-------------------------------------------------------------------------|-------|-------|-------|---------------|----------------|-----------|-------|

|                                                                         |       |       | IE<   | <15:8>        |                |           |       |

| bit 15                                                                  |       |       |       |               |                |           | bit 8 |

|                                                                         |       |       |       |               |                |           |       |

| R/W-0                                                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0          | R/W-0     | R/W-0 |

|                                                                         |       |       | IE    | <7:0>         |                |           |       |

| bit 7                                                                   |       |       |       |               |                |           | bit 0 |

|                                                                         |       |       |       |               |                |           |       |

| Legend:                                                                 |       |       |       |               |                |           |       |

| R = Readable bit W = Writable bit                                       |       |       |       | U = Unimpleme | ented bit, rea | ıd as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkn |       |       |       | nown          |                |           |       |

bit 15-0 IE<15:0>: Common Interrupt Enable bits

1 = Common and individual interrupts are enabled for the corresponding channel

0 = Common and individual interrupts are disabled for the corresponding channel

## REGISTER 4-103: ADIEH: ADC INTERRUPT ENABLE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | IE<20:16> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 IE<20:16>: Common Interrupt Enable bits

1 = Common and individual interrupts are enabled for the corresponding channel

0 = Common and individual interrupts are disabled for the corresponding channel

| REGISTER 6-6: | ACLKCON1: AUXILIARY CLOCK CONTROL REGISTER (MASTER) |

|---------------|-----------------------------------------------------|

|               |                                                     |

| R/W-0                       | R/W-0                                                                                                                                                                                                                                                     | U-0                                                                                                                                                                                                                                                              | U-0                                                  | U-0                                           | U-0             | U-0                 | R/W-0    |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------|-----------------|---------------------|----------|--|--|

| APLLEN <sup>(1)</sup>       | APLLCK                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                |                                                      | _                                             | _               | _                   | FRCSEL   |  |  |

| bit 15                      |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                  |                                                      |                                               |                 |                     | bit 8    |  |  |

|                             |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                  |                                                      |                                               |                 |                     |          |  |  |

| U-0                         | U-0                                                                                                                                                                                                                                                       | r-0                                                                                                                                                                                                                                                              | r-0                                                  | R/W-0                                         | R/W-0           | R/W-0               | R/W-1    |  |  |

| —                           |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                  | _                                                    | APLLPRE3                                      | APLLPRE2        | APLLPRE1            | APLLPRE0 |  |  |

| bit 7                       |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                  |                                                      |                                               |                 |                     | bit C    |  |  |

| Logondu                     |                                                                                                                                                                                                                                                           | r = Reserved b                                                                                                                                                                                                                                                   | :4                                                   |                                               |                 |                     |          |  |  |

| Legend:<br>R = Readabl      | la hit                                                                                                                                                                                                                                                    | W = Writable b                                                                                                                                                                                                                                                   |                                                      |                                               | antad hit raad  | aa 'O'              |          |  |  |

|                             |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                  | DIC                                                  | •                                             | ented bit, read |                     |          |  |  |

| -n = Value at               | TPOR                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                 |                                                      | '0' = Bit is clea                             | ared            | x = Bit is unkr     | iown     |  |  |

| bit 15                      |                                                                                                                                                                                                                                                           | kiliary PLL Enab                                                                                                                                                                                                                                                 |                                                      | lect bit <sup>(1)</sup><br>t-divider output ( | 'hynass disable | ad)                 |          |  |  |

|                             |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                  |                                                      | t clock (bypass                               |                 | <i>(</i> <b>u</b> ) |          |  |  |

| bit 14                      |                                                                                                                                                                                                                                                           | LL Phase-Lock                                                                                                                                                                                                                                                    | -                                                    |                                               | ,               |                     |          |  |  |

|                             | 1 = Auxiliary                                                                                                                                                                                                                                             | PLL is in lock                                                                                                                                                                                                                                                   |                                                      |                                               |                 |                     |          |  |  |

|                             | 0 = Auxiliary                                                                                                                                                                                                                                             | PLL is not in loc                                                                                                                                                                                                                                                |                                                      |                                               |                 |                     |          |  |  |

|                             | o naxilary                                                                                                                                                                                                                                                | 0 = Auxiliary PLL is not in lock                                                                                                                                                                                                                                 |                                                      |                                               |                 |                     |          |  |  |

| bit 13-9                    |                                                                                                                                                                                                                                                           | ted: Read as '0                                                                                                                                                                                                                                                  |                                                      |                                               |                 |                     |          |  |  |

| bit 13-9<br>bit 8           | Unimplemen                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | ,                                                    |                                               |                 |                     |          |  |  |

|                             | Unimplement<br>FRCSEL: FR<br>1 = FRC is th                                                                                                                                                                                                                | ted: Read as '0<br>C Clock Source<br>le clock source                                                                                                                                                                                                             | ,<br>Select bit<br>for APLL                          |                                               |                 |                     |          |  |  |

| bit 8                       | Unimplement<br>FRCSEL: FR<br>1 = FRC is th<br>0 = Primary (                                                                                                                                                                                               | ted: Read as '0<br>C Clock Source<br>le clock source<br>Dscillator is the                                                                                                                                                                                        | ,<br>Select bit<br>for APLL<br>clock source t        | for APLL                                      |                 |                     |          |  |  |

| bit 8<br>bit 7-6            | Unimplement<br>FRCSEL: FR<br>1 = FRC is th<br>0 = Primary (<br>Unimplement                                                                                                                                                                                | ted: Read as '0<br>C Clock Source<br>le clock source<br>Oscillator is the<br>ted: Read as '0                                                                                                                                                                     | ,<br>Select bit<br>for APLL<br>clock source t        | for APLL                                      |                 |                     |          |  |  |

| bit 8                       | Unimplement<br>FRCSEL: FRC<br>1 = FRC is th<br>0 = Primary (<br>Unimplement<br>Reserved: Ma                                                                                                                                                               | ted: Read as '0<br>C Clock Source<br>le clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'                                                                                                                                                   | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   |                                               |                 |                     |          |  |  |

| bit 8<br>bit 7-6            | Unimplement<br>FRCSEL: FR(<br>1 = FRC is th<br>0 = Primary (<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:                                                                                                                                                 | ted: Read as '0<br>C Clock Source<br>te clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br>0>: Auxiliary Pl                                                                                                                               | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   | for APLL<br>ector Input Divic                 | ler bits        |                     |          |  |  |

| bit 8<br>bit 7-6<br>bit 5-4 | Unimplement<br>FRCSEL: FRC<br>1 = FRC is th<br>0 = Primary C<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:<br>1111 = Reserved                                                                                                                              | ted: Read as '0<br>C Clock Source<br>te clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br>0>: Auxiliary Pl                                                                                                                               | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   |                                               | ler bits        |                     |          |  |  |

| bit 8<br>bit 7-6<br>bit 5-4 | Unimplement<br>FRCSEL: FRC<br>1 = FRC is th<br>0 = Primary (<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:<br>1111 = Reser                                                                                                                                 | ted: Read as '0<br>C Clock Source<br>le clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br>0>: Auxiliary Pl<br>ved                                                                                                                        | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   |                                               | ler bits        |                     |          |  |  |

| bit 8<br>bit 7-6<br>bit 5-4 | Unimplement<br>FRCSEL: FRC<br>1 = FRC is th<br>0 = Primary C<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:<br>1111 = Reserved                                                                                                                              | ted: Read as '0<br>C Clock Source<br>le clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br>0>: Auxiliary Pl<br>ved                                                                                                                        | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   |                                               | ler bits        |                     |          |  |  |

| bit 8<br>bit 7-6<br>bit 5-4 | Unimplement<br>FRCSEL: FR<br>1 = FRC is th<br>0 = Primary (<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:<br>1111 = Reser<br><br>1001 = Reser<br>1000 = Input<br>0111 = Input                                                                              | ted: Read as '0<br>C Clock Source<br>le clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br>0>: Auxiliary Pl<br>rved<br>tved<br>divided by 8<br>divided by 7                                                                               | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   |                                               | ler bits        |                     |          |  |  |

| bit 8<br>bit 7-6<br>bit 5-4 | Unimplement<br>FRCSEL: FR<br>1 = FRC is th<br>0 = Primary (<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:<br>1111 = Reser<br><br>1001 = Reser<br>1000 = Input<br>0111 = Input<br>0110 = Input                                                              | ted: Read as '0<br>C Clock Source<br>le clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br><b>0&gt;:</b> Auxiliary Pl<br>ved<br>ved<br>divided by 8<br>divided by 7<br>divided by 6                                                       | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   |                                               | ler bits        |                     |          |  |  |

| bit 8<br>bit 7-6<br>bit 5-4 | Unimplement<br>FRCSEL: FR<br>1 = FRC is th<br>0 = Primary C<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:<br>1111 = Reser<br><br>1001 = Reser<br>1000 = Input<br>0111 = Input<br>0110 = Input<br>0101 = Input                                              | ted: Read as '0<br>C Clock Source<br>te clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br><b>0&gt;:</b> Auxiliary Pl<br>ved<br>tivided by 8<br>divided by 8<br>divided by 7<br>divided by 6<br>divided by 5                              | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   |                                               | ler bits        |                     |          |  |  |

| bit 8<br>bit 7-6<br>bit 5-4 | Unimplement<br>FRCSEL: FR<br>1 = FRC is th<br>0 = Primary (<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:<br>1111 = Reser<br><br>1001 = Reser<br>1000 = Input<br>0111 = Input<br>0110 = Input<br>0101 = Input<br>0101 = Input                              | ted: Read as '0<br>C Clock Source<br>le clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br>0>: Auxiliary Pl<br>ved<br>divided by 8<br>divided by 8<br>divided by 7<br>divided by 6<br>divided by 5<br>divided by 4                        | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   |                                               | ler bits        |                     |          |  |  |

| bit 8<br>bit 7-6<br>bit 5-4 | Unimplement<br>FRCSEL: FR<br>1 = FRC is th<br>0 = Primary (C<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:<br>1111 = Reser<br>1001 = Reser<br>1001 = Reser<br>1000 = Input<br>0111 = Input<br>0101 = Input<br>0101 = Input<br>0100 = Input<br>0101 = Input | ted: Read as '0<br>C Clock Source<br>le clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br>0>: Auxiliary Pl<br>ved<br>ved<br>divided by 8<br>divided by 8<br>divided by 7<br>divided by 6<br>divided by 5<br>divided by 4<br>divided by 3 | ,<br>Select bit<br>for APLL<br>clock source 1<br>,   |                                               | ler bits        |                     |          |  |  |

| bit 8<br>bit 7-6<br>bit 5-4 | Unimplement<br>FRCSEL: FR<br>1 = FRC is th<br>0 = Primary (C<br>Unimplement<br>Reserved: Ma<br>APLLPRE<3:<br>1111 = Reser<br>1001 = Reser<br>1000 = Input<br>0111 = Input<br>0101 = Input<br>0101 = Input<br>0101 = Input<br>0101 = Input<br>0101 = Input | ted: Read as '0<br>C Clock Source<br>le clock source<br>Dscillator is the<br>ted: Read as '0<br>aintain as '0'<br>0>: Auxiliary Pl<br>ved<br>ved<br>divided by 8<br>divided by 8<br>divided by 7<br>divided by 6<br>divided by 5<br>divided by 4<br>divided by 3 | ,<br>for APLL<br>clock source 1<br>,<br>_L Phase Det | ector Input Divic                             | ler bits        |                     |          |  |  |

Note 1: Even with the APLLEN bit set, another peripheral must generate a clock request before the APLL will start.

## 7.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification on the I/O ports or peripherals that use an External Clock input.

- Any peripheral that requires the system clock source for its operation is disabled.