Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 88KB (88K × 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 34x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp206-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0    | U-0 | U-0 | U-0   | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-----|-----|-------|-------|

| —      | _   | —   | —     | —   | —   | CAN   | NAE   |

| bit 15 |     |     |       |     |     |       | bit 8 |

|        |     |     |       |     |     |       |       |

| U-0    | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0   | R/W-0 |

|        | _   | —   | DOOVR | —   | —   | —     | APLL  |

| bit 7  |     |     |       |     |     |       | bit 0 |

|        |     |     |       |     |     |       |       |

#### REGISTER 3-20: INTCON3: INTERRUPT CONTROL REGISTER 3

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-10 | Unimplemented: Read as '0'                                                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9     | CAN: CAN Address Error Soft Trap Status bit                                                                                               |

|           | <ul> <li>1 = CAN address error soft trap has occurred</li> <li>0 = CAN address error soft trap has not occurred</li> </ul>                |

| bit 8     | NAE: NVM Address Error Soft Trap Status bit                                                                                               |

|           | <ul> <li>1 = NVM address error soft trap has occurred</li> <li>0 = NVM address error soft trap has not occurred</li> </ul>                |

| bit 7-5   | Unimplemented: Read as '0'                                                                                                                |

| bit 4     | DOOVR: DO Stack Overflow Soft Trap Status bit                                                                                             |

|           | <ul> <li>1 = DO stack overflow soft trap has occurred</li> <li>0 = DO stack overflow soft trap has not occurred</li> </ul>                |

| bit 3-1   | Unimplemented: Read as '0'                                                                                                                |

| bit 0     | APLL: Auxiliary PLL Loss of Lock Soft Trap Status bit<br>1 = APLL lock soft trap has occurred<br>0 = APLL lock soft trap has not occurred |

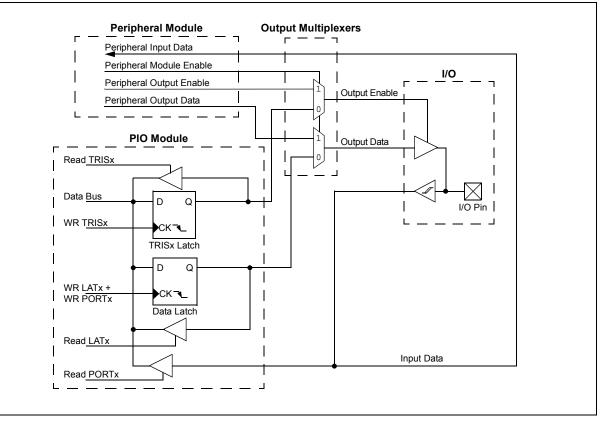

#### FIGURE 3-19: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

#### REGISTER 3-24: TRISX: OUTPUT ENABLE FOR PORTX REGISTER

| R/W-1                                                                | R/W-1 | R/W-1 | R/W-1    | R/W-1            | R/W-1 | R/W-1          | R/W-1 |

|----------------------------------------------------------------------|-------|-------|----------|------------------|-------|----------------|-------|

|                                                                      |       |       | TRIS     | x<15:8>          |       |                |       |

| bit 15                                                               |       |       |          |                  |       |                | bit 8 |

| R/W-1                                                                | R/W-1 | R/W-1 | R/W-1    | R/W-1            | R/W-1 | R/W-1          | R/W-1 |

|                                                                      |       |       | TRIS     | Sx<7:0>          |       |                |       |

| bit 7                                                                |       |       |          |                  |       |                | bit 0 |

|                                                                      |       |       |          |                  |       |                |       |

| Legend:                                                              |       |       |          |                  |       |                |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       | d as '0' |                  |       |                |       |

| -n = Value at POR (1' = Bit is set                                   |       |       |          | '0' = Bit is cle | ared  | x = Bit is unk | nown  |

bit 15-0 **TRISx<15:0**: Output Enable for PORTx bits 1 = LATx[n] is not driven on the PORTx[n] pin

0 = LATx[n] is driven on the PORTx[n] pin

#### REGISTER 3-25: PORTX: INPUT DATA FOR PORTX REGISTER

| R/W-1                             | R/W-1   | R/W-1            | R/W-1        | R/W-1            | R/W-1     | R/W-1          | R/W-1   |

|-----------------------------------|---------|------------------|--------------|------------------|-----------|----------------|---------|

|                                   |         |                  | PORT         | <15:8>           |           |                |         |

| bit 15                            |         |                  |              |                  |           |                | bit 8   |

| R/W-1                             | R/W-1   | R/W-1            | R/W-1        | R/W-1            | R/W-1     | R/W-1          | R/W-1   |

| 1.7.4.4                           | 10.00-1 | 10/00-1          |              | x<7:0>           | 10/00-1   | 10/00-1        | 10/00-1 |

| bit 7                             |         |                  |              |                  |           |                | bit 0   |

| Legend:                           |         |                  |              |                  |           |                |         |

| R = Readable bit W = Writable bit |         |                  | U = Unimplen | nented bit, rea  | ad as '0' |                |         |

| -n = Value at POR '1' = Bit is se |         | '1' = Bit is set |              | '0' = Bit is cle | ared      | x = Bit is unk | nown    |

bit 15-0 **PORTx<15:0>:** PORTx Data Input Value bits

| Input Name <sup>(1)</sup> | Function Name | Register | Register Bits |

|---------------------------|---------------|----------|---------------|

| External Interrupt 1      | INT1          | RPINR0   | INT1R<7:0>    |

| External Interrupt 2      | INT2          | RPINR1   | INT2R<7:0>    |

| External Interrupt 3      | INT3          | RPINR1   | INT3R<7:0>    |

| Timer1 External Clock     | T1CK          | RPINR2   | T1CK<7:0>     |

| SCCP Timer1               | TCKI1         | RPINR3   | TCKI1R<7:0>   |

| SCCP Capture 1            | ICM1          | RPINR3   | ICM1R<7:0>    |

| SCCP Timer2               | TCKI2         | RPINR4   | TCKI2R<7:0>   |

| SCCP Capture 2            | ICM2          | RPINR4   | ICM2R<7:0>    |

| SCCP Timer3               | TCKI3         | RPINR5   | TCKI3R<7:0>   |

| SCCP Capture 3            | ICM3          | RPINR5   | ICM3R<7:0>    |

| SCCP Timer4               | TCKI4         | RPINR6   | TCKI4R<7:0>   |

| SCCP Capture 4            | ICM4          | RPINR6   | ICM4R<7:0>    |

| SCCP Timer5               | TCKI5         | RPINR7   | TCKI5R<7:0>   |

| SCCP Capture 5            | ICM5          | RPINR7   | ICM5R<7:0>    |

| SCCP Timer6               | TCKI6         | RPINR8   | TCKI6R<7:0>   |

| SCCP Capture 6            | ICM6          | RPINR8   | ICM6R<7:0>    |

| SCCP Timer7               | TCKI7         | RPINR9   | TCKI7R<7:0>   |

| SCCP Capture 7            | ICM7          | RPINR9   | ICM7R<7:0>    |

| SCCP Timer8               | TCKI8         | RPINR10  | TCKI8R<7:0>   |

| SCCP Capture 8            | ICM8          | RPINR10  | ICM8R<7:0>    |

| SCCP Fault A              | OCFA          | RPINR11  | OCFAR<7:0>    |

| SCCP Fault B              | OCFB          | RPINR11  | OCFBR<7:0>    |

| PWM Input 8               | PCI8          | RPINR12  | PCI8R<7:0>    |

| PWM Input 9               | PCI9          | RPINR12  | PCI9R<7:0>    |

| PWM Input 10              | PCI10         | RPINR13  | PCI10R<7:0>   |

| PWM Input 11              | PCI11         | RPINR13  | PCI11R<7:0>   |

| QEI Input A               | QEIA1         | RPINR14  | QEIA1R<7:0>   |

| QEI Input B               | QEIB1         | RPINR14  | QEIB1R<7:0>   |

| QEI Index 1 Input         | QEINDX1       | RPINR15  | QEINDX1R<7:0> |

| QEI Home 1 Input          | QEIHOM1       | RPINR15  | QEIHOM1R<7:0> |

| UART1 Receive             | U1RX          | RPINR18  | U1RXR<7:0>    |

| UART1 Data-Set-Ready      | U1DSR         | RPINR18  | U1DSRR<7:0>   |

| UART2 Receive             | U2RX          | RPINR19  | U2RXR<7:0>    |

| UART2 Data-Set-Ready      | U2DSR         | RPINR19  | U2DSRR<7:0>   |

| SPI1 Data Input           | SDI1          | RPINR20  | SDI1R<7:0>    |

| SPI1 Clock Input          | SCK1IN        | RPINR20  | SCK1R<7:0>    |

| SPI1 Slave Select         | SS1           | RPINR21  | SS1R<7:0>     |

| Reference Clock Input     | REFOI         | RPINR21  | REFOIR<7:0>   |

| SPI2 Data Input           | SDI2          | RPINR22  | SDI2R<7:0>    |

| SPI2 Clock Input          | SCK2IN        | RPINR22  | SCK2R<7:0>    |

| SPI2 Slave Select         | SS2           | RPINR23  | SS2R<7:0>     |

| UART1 Clear-to-Send       | U1CTS         | RPINR23  | U1CTSR<7:0>   |

| TABLE 3-31: | SELECTABLE INPUT SOURCES ( | MAPS INPUT TO FUNCTION) |

|-------------|----------------------------|-------------------------|

|             |                            |                         |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRISx setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRISx settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned.

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Select for PORTx (ANSELx) registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Select for PORTx registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

### 3.6.16 I/O PORTS RESOURCES

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 3.6.16.1 Key Resources

- "I/O Ports with Edge Detect" (DS70005322) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### **REGISTER 3-134:** C1FIFOCONLx: CAN FIFO CONTROL REGISTER x (x = 1 TO 7) LOW (CONTINUED)

| bit 2 | <b>TFERFFIE:</b> Transmit/Receive FIFO Empty/Full Interrupt Enable bit<br><u>TXEN = 1 (FIFO configured as a transmit FIFO):</u><br>Transmit FIFO Empty Interrupt Enable<br>1 = Interrupt is enabled for FIFO empty<br>0 = Interrupt is disabled for FIFO empty                                                                                                                                                                                                                      |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>TXEN = 0 (FIFO configured as a receive FIFO):</u><br>Receive FIFO Full Interrupt Enable<br>1 = Interrupt is enabled for FIFO full<br>0 = Interrupt is disabled for FIFO full                                                                                                                                                                                                                                                                                                     |

| bit 1 | <b>TFHRFHIE:</b> Transmit/Receive FIFO Half Empty/Half Full Interrupt Enable bit<br><u>TXEN = 1 (FIFO configured as a transmit FIFO):</u><br>Transmit FIFO Half Empty Interrupt Enable<br>1 = Interrupt is enabled for FIFO half empty<br>0 = Interrupt is disabled for FIFO half empty<br><u>TXEN = 0 (FIFO configured as a receive FIFO):</u><br>Receive FIFO Half Full Interrupt Enable                                                                                          |

|       | <ul><li>1 = Interrupt is enabled for FIFO half full</li><li>0 = Interrupt is disabled for FIFO half full</li></ul>                                                                                                                                                                                                                                                                                                                                                                  |

| bit 0 | <b>TFNRFNIE:</b> Transmit/Receive FIFO Not Full/Not Empty Interrupt Enable bit<br><u>TXEN = 1 (FIFO configured as a transmit FIFO)</u> :<br>Transmit FIFO Not Full Interrupt Enable<br>1 = Interrupt is enabled for FIFO not full<br>0 = Interrupt is disabled for FIFO not full<br><u>TXEN = 0 (FIFO configured as a receive FIFO)</u> :<br>Receive FIFO Not Empty Interrupt Enable<br>1 = Interrupt is enabled for FIFO not empty<br>0 = Interrupt is disabled for FIFO not empty |

**Note 1:** This bit can only be modified in Configuration mode (OPMOD<2:0> = 100).

#### REGISTER 3-193: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0            | R/W-0                                    | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|----------------|-------|------------------|------------------------------------------|----------|-------|-------|-------|

|                |       |                  | PTGAI                                    | DJ<15:8> |       |       |       |

| bit 15         |       |                  |                                          |          |       |       | bit 8 |

|                |       |                  |                                          |          |       |       |       |

| R/W-0          | R/W-0 | R/W-0            | R/W-0                                    | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                |       |                  | PTGA                                     | DJ<7:0>  |       |       |       |

| bit 7          |       |                  |                                          |          |       |       | bit 0 |

|                |       |                  |                                          |          |       |       |       |

| Legend:        |       |                  |                                          |          |       |       |       |

| R = Readable b | bit   | W = Writable bit | e bit U = Unimplemented bit, read as '0' |          |       |       |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds the user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 register using the PTGADD command.

Note 1: These bits are read-only when the module is executing Step commands.

#### REGISTER 3-194: PTGL0: PTG LITERAL 0 REGISTER<sup>(1,2)</sup>

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| PTGL0<15:8> |       |       |       |       |       |       |       |

| bit 15      |       |       |       |       |       |       | bit 8 |

|             |       |       |       |       |       |       |       |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| PTGL0<7:0>  |       |       |       |       |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGL0<15:0>:** PTG Literal 0 Register bits

This register holds the 6-bit value to be written to the CNVCHSEL<5:0> bits (ADCON3L<5:0>) with the PTGCTRL Step command.

- Note 1: These bits are read-only when the module is executing Step commands.

- 2: The PTG strobe output is typically connected to the ADC Channel Select register. This allows the PTG to directly control ADC channel switching. See the specific device data sheet for connections of the PTG output.

bit 7

bit 0

| VAR             |                                                                                                                                                                                      |                                                       |                 | R/W-0               | -                  | R-0             |       |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|---------------------|--------------------|-----------------|-------|

| .,              | —                                                                                                                                                                                    | US1                                                   | US0             | EDT <sup>(1)</sup>  | DL2                | DL1             | DL0   |

| bit 15          |                                                                                                                                                                                      |                                                       |                 |                     |                    |                 | bit 8 |

| DAMA            |                                                                                                                                                                                      |                                                       | DAA/ O          | D/0.0               | <b>D</b> 0         | DAMA            | DAMO  |

| R/W-0           | R/W-0                                                                                                                                                                                | R/W-1                                                 | R/W-0           | R/C-0               | R-0                | R/W-0           | R/W-0 |

| SATA            | SATB                                                                                                                                                                                 | SATDW                                                 | ACCSAT          | IPL3 <sup>(2)</sup> | SFA                | RND             | IF    |

| bit 7           |                                                                                                                                                                                      |                                                       |                 |                     |                    |                 | bit 0 |

| Legend:         |                                                                                                                                                                                      | C = Clearable                                         | e bit           |                     |                    |                 |       |

| R = Readable    | bit                                                                                                                                                                                  | W = Writable                                          | bit             | U = Unimplei        | mented bit, rea    | d as '0'        |       |

| -n = Value at P | OR                                                                                                                                                                                   | '1' = Bit is set                                      |                 | '0' = Bit is cle    |                    | x = Bit is unkr | iown  |

| bit 15          | 1 = Variable e                                                                                                                                                                       | e Exception Pro<br>exception proce                    | essing is enab  | led                 |                    |                 |       |

| bit 14          | Unimplemen                                                                                                                                                                           | ted: Read as '                                        | 0'              |                     |                    |                 |       |

| bit 13-12       | <b>US&lt;1:0&gt;:</b> DS                                                                                                                                                             | P Multiply Uns                                        | igned/Signed    | Control bits        |                    |                 |       |

|                 | <ul> <li>11 = Reserved</li> <li>10 = DSP engine multiplies are mixed sign</li> <li>01 = DSP engine multiplies are unsigned</li> <li>00 = DSP engine multiplies are signed</li> </ul> |                                                       |                 |                     |                    |                 |       |

| bit 11          | EDT: Early DO                                                                                                                                                                        | Loop Termina                                          | ation Control b | it <sup>(1)</sup>   |                    |                 |       |

|                 | 1 = Terminate<br>0 = No effect                                                                                                                                                       | es executing DO                                       | loop at the e   | nd of the curre     | ent loop iteration | n               |       |

| bit 10-8        | DL<2:0>: DO                                                                                                                                                                          | Loop Nesting                                          | Level Status b  | its                 |                    |                 |       |

|                 | <br>001 <b>= One</b> DO                                                                                                                                                              | DO loops are a                                        |                 |                     |                    |                 |       |

|                 |                                                                                                                                                                                      | o loops are act                                       |                 |                     |                    |                 |       |

| bit 7           | 1 = Accumula                                                                                                                                                                         | Saturation En<br>ator A saturatio<br>ator A saturatio | n is enabled    |                     |                    |                 |       |

| bit 6           | SATB: ACCB                                                                                                                                                                           | Saturation En                                         | able bit        |                     |                    |                 |       |

|                 |                                                                                                                                                                                      | ntor B saturatio<br>Itor B saturatio                  |                 |                     |                    |                 |       |

| bit 5           | SATDW: Data                                                                                                                                                                          | a Space Write t                                       | from DSP Eng    | ine Saturation      | Enable bit         |                 |       |

|                 | <ul> <li>1 = Data Space write saturation is enabled</li> <li>0 = Data Space write saturation is disabled</li> </ul>                                                                  |                                                       |                 |                     |                    |                 |       |

| bit 4           | 1 = 9.31 satu                                                                                                                                                                        | cumulator Satu<br>ration (super s<br>ration (normal   | aturation)      | Select bit          |                    |                 |       |

| bit 3           | IPL3: CPU Int                                                                                                                                                                        | terrupt Priority                                      |                 |                     |                    |                 |       |

#### REGISTER 4-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| Register  | Address   | All Resets         | Register | Address | All Resets         | Register | Address | All Resets   |

|-----------|-----------|--------------------|----------|---------|--------------------|----------|---------|--------------|

| I/O Ports | I/O Ports |                    | RPINR23  | D32     | 111111111111111111 | RPOR8    | D90     | 000000000000 |

| RPCON     | D00       | 0                  | RPINR37  | D4E     | 11111111           | RPOR9    | D92     | 000000000000 |

| RPINR0    | D04       | 11111111           | RPINR38  | D50     | 111111111          | RPOR10   | D94     | 000000000000 |

| RPINR1    | D06       | 111111111111111111 | RPINR42  | D58     | 111111111111111111 | RPOR11   | D96     | 000000000000 |

| RPINR2    | D08       | 11111111           | RPINR43  | D5A     | 111111111111111111 | RPOR12   | D98     | 000000000000 |

| RPINR3    | D0A       | 111111111111111111 | RPINR44  | D5C     | 111111111111111111 | RPOR13   | D9A     | 000000000000 |

| RPINR4    | D0C       | 111111111111111111 | RPINR45  | D5E     | 111111111111111111 | RPOR14   | D9C     | 000000000000 |

| RPINR5    | D0E       | 111111111111111111 | RPINR46  | D60     | 111111111111111111 | RPOR15   | D9E     | 000000000000 |

| RPINR6    | D10       | 111111111111111111 | RPINR47  | D62     | 111111111111111111 | RPOR16   | DA0     | 000000000000 |

| RPINR11   | D1A       | 111111111111111111 | RPOR0    | D80     | 000000000000       | RPOR17   | DA2     | 000000000000 |

| RPINR12   | D1C       | 111111111111111111 | RPOR1    | D82     | 000000000000       | RPOR18   | DA4     | 000000000000 |

| RPINR13   | D1E       | 111111111111111111 | RPOR2    | D84     | 000000000000       | RPOR19   | DA6     | 000000000000 |

| RPINR14   | D20       | 111111111111111111 | RPOR3    | D86     | 000000000000       | RPOR20   | DA8     | 000000000000 |

| RPINR15   | D22       | 111111111111111111 | RPOR4    | D88     | 000000000000       | RPOR21   | DAA     | 000000000000 |

| RPINR18   | D28       | 111111111111111111 | RPOR5    | D8A     | 000000000000       | RPOR22   | DAC     | 000000000000 |

| RPINR20   | D2C       | 111111111111111111 | RPOR6    | D8C     | 000000000000       |          |         |              |

| RPINR21   | D2E       | 111111111111111111 | RPOR7    | D8E     | 000000000000       |          |         |              |

#### TABLE 4-13: SLAVE SFR BLOCK D00h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address and Reset values are in hexadecimal and binary, respectively.

# dsPIC33CH128MP508 FAMILY

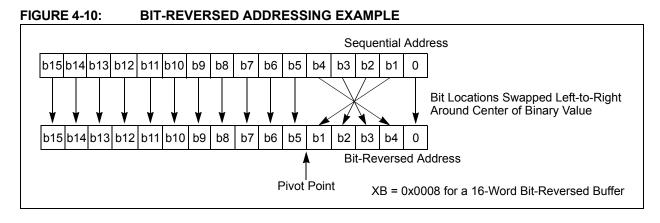

#### TABLE 4-18: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | s       | Bit-Reversed Ad |    |    |    | ldress  |

|----|----|-------|-----------|---------|-----------------|----|----|----|---------|

| A3 | A2 | A1    | A0        | Decimal | A3              | A2 | A1 | A0 | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0               | 0  | 0  | 0  | 0       |

| 0  | 0  | 0     | 1         | 1       | 1               | 0  | 0  | 0  | 8       |

| 0  | 0  | 1     | 0         | 2       | 0               | 1  | 0  | 0  | 4       |

| 0  | 0  | 1     | 1         | 3       | 1               | 1  | 0  | 0  | 12      |

| 0  | 1  | 0     | 0         | 4       | 0               | 0  | 1  | 0  | 2       |

| 0  | 1  | 0     | 1         | 5       | 1               | 0  | 1  | 0  | 10      |

| 0  | 1  | 1     | 0         | 6       | 0               | 1  | 1  | 0  | 6       |

| 0  | 1  | 1     | 1         | 7       | 1               | 1  | 1  | 0  | 14      |

| 1  | 0  | 0     | 0         | 8       | 0               | 0  | 0  | 1  | 1       |

| 1  | 0  | 0     | 1         | 9       | 1               | 0  | 0  | 1  | 9       |

| 1  | 0  | 1     | 0         | 10      | 0               | 1  | 0  | 1  | 5       |

| 1  | 0  | 1     | 1         | 11      | 1               | 1  | 0  | 1  | 13      |

| 1  | 1  | 0     | 0         | 12      | 0               | 0  | 1  | 1  | 3       |

| 1  | 1  | 0     | 1         | 13      | 1               | 0  | 1  | 1  | 11      |

| 1  | 1  | 1     | 0         | 14      | 0               | 1  | 1  | 1  | 7       |

| 1  | 1  | 1     | 1         | 15      | 1               | 1  | 1  | 1  | 15      |

| Function     | RPnR<5:0> | Output Name                          |

|--------------|-----------|--------------------------------------|

| Default PORT | 000000    | S1RPn tied to Default Pin            |

| S1U1TX       | 000001    | S1RPn tied to UART1 Transmit         |

| S1U1RTS      | 000010    | S1RPn tied to UART1 Request-to-Send  |

| S1SDO1       | 000101    | S1RPn tied to SPI1 Data Output       |

| S1SCK1OUT    | 000110    | S1RPn tied to SPI1 Clock Output      |

| S1SS1OUT     | 000111    | S1RPn tied to SPI1 Slave Select      |

| S1REFCLKO    | 001110    | S1RPn tied to Reference Clock Output |

| S10CM1       | 001111    | S1RPn tied to SCCP1 Output           |

| S1OCM2       | 010000    | S1RPn tied to SCCP2 Output           |

| S1OCM3       | 010001    | S1RPn tied to SCCP3 Output           |

| S1OCM4       | 010010    | S1RPn tied to SCCP4 Output           |

| S1CMP1       | 010111    | S1RPn tied to Comparator 1 Output    |

| S1CMP2       | 011000    | S1RPn tied to Comparator 2 Output    |

| S1CMP3       | 011001    | S1RPn tied to Comparator 3 Output    |

| S1PWMH4      | 100010    | S1RPn tied to PWM4H Output           |

| S1PWML4      | 100011    | S1RPn tied to PWM4L Output           |

| S1PWMEA      | 100100    | S1RPn tied to PWM Event A Output     |

| S1PWMEB      | 100101    | S1RPn tied to PWM Event B Output     |

| S1QEICMP1    | 100110    | S1RPn tied to QEI Comparator Output  |

| S1CLC1OUT    | 101000    | S1RPn tied to CLC1 Output            |

| S1CLC2OUT    | 101001    | S1RPn tied to CLC2 Output            |

| S1PWMEC      | 101100    | S1RPn tied to PWM Event C Output     |

| S1PWMED      | 101101    | S1RPn tied to PWM Event D Output     |

| MPTGTRG1     | 101110    | Master PTG24 Output                  |

| MPTGTRG2     | 101111    | Master PTG25 Output                  |

| S1CLC3OUT    | 110010    | S1RPn tied to CLC3 Output            |

#### TABLE 4-31: OUTPUT SELECTION FOR REMAPPABLE PINS (S1RPn)

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a Built-In Self-Test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRISx setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRISx settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned.

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Select for PORTx (ANSELx) registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Select for PORTx registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 4.6.7 I/O PORTS RESOURCES

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 4.6.7.1 Key Resources

- "I/O Ports with Edge Detect" (DS70005322) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0        | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------------|--------|

| _       | —   | RP41R5 | RP41R4 | RP41R3 | RP41R2 | RP41R1       | RP41R0 |

| bit 15  |     |        |        |        |        |              | bit 8  |

|         |     |        |        |        |        |              |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0        | R/W-0  |

| —       | —   | RP40R5 | RP40R4 | RP40R3 | RP40R2 | RP40R1       | RP40R0 |

| bit 7   |     |        |        |        |        |              | bit 0  |

|         |     |        |        |        |        |              |        |

| Legend: |     |        |        |        |        |              |        |

|         |     |        |        |        |        | ( <b>a</b> ) |        |

#### REGISTER 4-64: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP41R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP41 Output Pin bits (see Table 4-31 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | <b>RP40R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP40 Output Pin bits (see Table 4-31 for peripheral function numbers) |

#### REGISTER 4-65: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP43  | RP43  | RP43  | RP43  | RP43  | RP43  |

| bit 15 |     |       |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP42R5 | RP42R4 | RP42R3 | RP42R2 | RP42R1 | RP42R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP43R<5:0>:** Peripheral Output Function is Assigned to S1RP43 Output Pin bits (see Table 4-31 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP42R<5:0>:** Peripheral Output Function is Assigned to S1RP42 Output Pin bits (see Table 4-31 for peripheral function numbers)

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP61R5 | RP61R4 | RP61R3 | RP61R2 | RP61R1 | RP61R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP60R5 | RP60R4 | RP60R3 | RP60R2 | RP60R1 | RP60R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

#### REGISTER 4-74: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP61R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP61 Output Pin bits (see Table 4-31 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | <b>RP60R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP60 Output Pin bits (see Table 4-31 for peripheral function numbers) |

#### REGISTER 4-75: RPOR15: PERIPHERAL PIN SELECT OUTPUT REGISTER 15

| U-0    | U-0 | R/W-0           | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----------------|-------|--------|--------|--------|--------|

| —      | —   | – RP63R5 RP63R4 |       | RP63R3 | RP63R2 | RP63R1 | RP63R0 |

| bit 15 |     |                 |       |        |        |        | bit 8  |

| U-0   | U-0          | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------------|-------|--------|--------|--------|--------|--------|

| —     | — RP62R5 RP6 |       | RP62R4 | RP62R3 | RP62R2 | RP62R1 | RP62R0 |

| bit 7 |              |       |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP63R<5:0>:** Peripheral Output Function is Assigned to S1RP63 Output Pin bits (see Table 4-31 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP62R<5:0>:** Peripheral Output Function is Assigned to S1RP62 Output Pin bits (see Table 4-31 for peripheral function numbers)

x = Bit is unknown

'1' = Bit is set

| HS/R/W-0     | U-0 | U-0            | U-0            | U-0                                | r-0 | R/W-0  | R/W-0   |

|--------------|-----|----------------|----------------|------------------------------------|-----|--------|---------|

| CSHRRDY      | _   | —              | —              | —                                  | —   | CSHREN | CSHRRUN |

| bit 15       |     |                |                |                                    |     |        | bit 8   |

|              |     |                |                |                                    |     |        |         |

| U-0          | U-0 | U-0            | U-0            | U-0                                | U-0 | U-0    | U-0     |

| —            | —   | —              | —              | _                                  | —   | —      | —       |

| bit 7        |     |                |                |                                    |     |        | bit 0   |

|              |     |                |                |                                    |     |        |         |

| Legend:      |     | HS = Hardwar   | e Settable bit | r = Reserved                       | bit |        |         |

| R = Readable | bit | W = Writable b | bit            | U = Unimplemented bit, read as '0' |     |        |         |

|              |     |                |                |                                    |     |        |         |

'0' = Bit is cleared

| bit 15    | CSHRRDY: Shared ADC Core Calibration Status Flag bit                                                      |

|-----------|-----------------------------------------------------------------------------------------------------------|

|           | 1 = Shared ADC core calibration is finished                                                               |

|           | 0 = Shared ADC core calibration is in progress                                                            |

| bit 14-11 | Unimplemented: Read as '0'                                                                                |

| bit 10    | Reserved: Maintain as '0'                                                                                 |

| bit 9     | CSHREN: Shared ADC Core Calibration Enable bit                                                            |

|           | 1 = Shared ADC core calibration bits (CSHRRDY and CSHRRUN) can be accessed by software                    |

|           | 0 = Shared ADC core calibration bits are disabled                                                         |

| bit 8     | CSHRRUN: Shared ADC Core Calibration Start bit                                                            |

|           | 1 = If this bit is set by software, the shared ADC core calibration cycle is started; this bit is cleared |

|           | automatically by hardware                                                                                 |

|           | 0 = Software can start the next calibration cycle                                                         |

| bit 7-0   | Unimplemented: Read as '0'                                                                                |

-n = Value at POR

#### REGISTER 5-5: MSI1MBXnD: MSI1 MASTER MAILBOX n DATA REGISTER (n = 0 to 15)

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0  | R/W-0             | R/W-0 | R/W-0          | R/W-0 |

|----------------------------------------------------------------------|-------|-------|--------|-------------------|-------|----------------|-------|

|                                                                      |       |       | MSIMBX | nD<15:8>          |       |                |       |

| bit 15                                                               |       |       |        |                   |       |                | bit 8 |

|                                                                      |       |       |        |                   |       |                |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0  | R/W-0             | R/W-0 | R/W-0          | R/W-0 |

|                                                                      |       |       | MSIMB) | (nD<7:0>          |       |                |       |

| bit 7                                                                |       |       |        |                   |       |                | bit 0 |

|                                                                      |       |       |        |                   |       |                |       |

| Legend:                                                              |       |       |        |                   |       |                |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |        |                   |       |                |       |

| -n = Value at POR (1' = Bit is set                                   |       |       |        | '0' = Bit is clea | ared  | x = Bit is unk | nown  |

bit 15-0

MSIMBXnD<15:0>: MSI1 Mailbox n Data bits

When Configuration bit, MBXMx = 1 (programmed):

Mailbox Data Direction: Master read, Slave write; Master MSIMBXnD<15:0> bits become R-0 (a Master

write to MSIMBXnD<15:0> will have no effect).

When Configuration bit, MBXMx = 0 (programmed):

Mailbox Data Direction: Master write, Slave read; Master MSIMBXnD<15:0> bits become R/W-0.

# 15.4 I<sup>2</sup>C Control/Status Registers

#### REGISTER 15-1: I2CxCONL: I2Cx CONTROL REGISTER LOW

| R/W-0            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HC/R/W-0                                                                                                                           | R/W-1                                                                                                                                                                                        | R/W-0                                                                                                     |                                                                         |                                                                         |                                         |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------|--|

|                  | 0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                    | SCLREL <sup>(1)</sup>                                                                                                                                                                        | -                                                                                                         | R/W-0                                                                   | R/W-0                                                                   | R/W-0                                   |  |

| I2CEN            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I2CSIDL                                                                                                                            | SCLREL                                                                                                                                                                                       | STRICT                                                                                                    | A10M                                                                    | DISSLW                                                                  | SMEN                                    |  |

| bit 15           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         | bit 8                                   |  |

| R/W-0            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                              | HC/R/W-0                                                                                                                                                                                     | HC/R/W-0                                                                                                  | HC/R/W-0                                                                | HC/R/W-0                                                                | HC/R/W-0                                |  |

| GCEN             | STREN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ACKDT                                                                                                                              | ACKEN                                                                                                                                                                                        | RCEN                                                                                                      | PEN                                                                     | RSEN                                                                    | SEN                                     |  |

| bit 7            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |                                                                                                                                                                                              | -                                                                                                         |                                                                         |                                                                         | bit                                     |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HC = Hardware                                                                                                                      | e Clearable bit                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |

| R = Readable     | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W = Writable b                                                                                                                     | bit                                                                                                                                                                                          | U = Unimplem                                                                                              | nented bit, read                                                        | l as '0'                                                                |                                         |  |

| -n = Value at    | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                                                                                                                   |                                                                                                                                                                                              | '0' = Bit is clea                                                                                         | ared                                                                    | x = Bit is unkr                                                         | nown                                    |  |

| bit 15<br>bit 14 | 1 = Enables f<br>0 = Disables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Enable bit (writa<br>the I2Cx module<br>the I2Cx module<br>nted: Read as '0                                                        | e, and configure<br>e; all I <sup>2</sup> C pins a                                                                                                                                           | s the SDAx and                                                                                            |                                                                         | serial port pins                                                        | 3                                       |  |

|                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |

| bit 13           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cx Stop in Idle M                                                                                                                  |                                                                                                                                                                                              | vice enters Idle                                                                                          | mode                                                                    |                                                                         |                                         |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | s module operat<br>CLx Release Cor                                                                                                 |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |