Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 34x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp206-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 3-5: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                 |       |                  | NVMA  | DR<15:8>                           |       |                 |       |

| bit 15          |       |                  |       |                                    |       |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|                 |       |                  | NVMA  | DR<7:0>                            |       |                 |       |

| bit 7           |       |                  |       |                                    |       |                 | bit 0 |

|                 |       |                  |       |                                    |       |                 |       |

| Legend:         |       |                  |       |                                    |       |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at P | OR    | '1' = Bit is set | •     |                                    |       | x = Bit is unkr | nown  |

bit 15-0 **NVMADR<15:0>:** Nonvolatile Memory Lower Write Address bits Selects the lower 16 bits of the location to program or erase in Program Flash Memory. This register may be read or written to by the user application.

### REGISTER 3-6: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0             | U-0   | U-0              | U-0   | U-0                               | U-0             | U-0             | U-0   |

|-----------------|-------|------------------|-------|-----------------------------------|-----------------|-----------------|-------|

| —               | _     | —                | _     | —                                 | —               | —               |       |

| bit 15          |       |                  |       |                                   |                 |                 | bit 8 |

|                 |       |                  |       |                                   |                 |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                             | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | NVMAD | RU<23:16>                         |                 |                 |       |

| bit 7           |       |                  |       |                                   |                 |                 | bit 0 |

|                 |       |                  |       |                                   |                 |                 |       |

| Legend:         |       |                  |       |                                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimple                       | mented bit, rea | id as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is u |                 | x = Bit is unkr | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADRU<23:16>:** Nonvolatile Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in Program Flash Memory. This register may be read or written to by the user application.

# REGISTER 3-18: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 6 | DIV0ERR: Divide-by-Zero Error Status bit               |

|-------|--------------------------------------------------------|

|       | 1 = Math error trap was caused by a divide-by-zero     |

|       | 0 = Math error trap was not caused by a divide-by-zero |

| bit 5 | DMACERR: DMA Controller Trap Status bit                |

|       | 1 = DMAC error trap has occurred                       |

|       | 0 = DMAC error trap has not occurred                   |

| bit 4 | MATHERR: Math Error Status bit                         |

|       | 1 = Math error trap has occurred                       |

|       | 0 = Math error trap has not occurred                   |

| bit 3 | ADDRERR: Address Error Trap Status bit                 |

|       | 1 = Address error trap has occurred                    |

|       | 0 = Address error trap has not occurred                |

| bit 2 | STKERR: Stack Error Trap Status bit                    |

|       | 1 = Stack error trap has occurred                      |

|       | 0 = Stack error trap has not occurred                  |

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit            |

|       | 1 = Oscillator failure trap has occurred               |

|       | 0 = Oscillator failure trap has not occurred           |

| bit 0 | Unimplemented: Read as '0'                             |

### 3.6.17 PERIPHERAL PIN SELECT REGISTERS

# **REGISTER 3-35:** RPCON: PERIPHERAL REMAPPING CONFIGURATION REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|--------|-----|-----|-------|

| _      | _   | —   | _   | IOLOCK | —   | _   | _     |

| bit 15 |     |     |     |        |     |     | bit 8 |

|        |     |     |     |        |     |     |       |

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0 | U-0 | U-0   |

| —      | —   | —   | —   | —      | —   | —   | —     |

| bit 7  | ÷   | •   |     |        | •   | •   | bit 0 |

|        |     |     |     |        |     |     |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-12 | Unimplemented: Read as '0' |  |

|-----------|----------------------------|--|

|           |                            |  |

bit 11 **IOLOCK:** Peripheral Remapping Register Lock bit 1 = All Peripheral Remapping registers are locked and cannot be written 0 = All Peripheral Remapping registers are unlocked and can be written

bit 10-0 Unimplemented: Read as '0'

**Note 1:** Writing to this register needs an unlock sequence.

### REGISTER 3-36: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|--------|--------|--------|--------|--------|--------|--------|

| INT1R7  | INT1R6 | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15  |        |        |        |        |        |        | bit 8  |

|         |        |        |        |        |        |        |        |

| U-0     | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    |

| —       | —      | —      | _      | —      | —      | —      | —      |

| bit 7   |        |        |        |        |        |        | bit 0  |

|         |        |        |        |        |        |        |        |

| Legend: |        |        |        |        |        |        |        |

| U                 |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

|                   |                  |                            |                    |

bit 15-8 INT1R<7:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 Unimplemented: Read as '0'

### REGISTER 3-137: C1TEFCONL: CAN TRANSMIT EVENT FIFO CONTROL REGISTER LOW

| U-0          | U-0                                         | U-0                                                                                                         | U-0           | U-0                          | S/HC-0           | U-0              | S/HC-0          |  |  |  |  |  |

|--------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------|------------------------------|------------------|------------------|-----------------|--|--|--|--|--|

| _            |                                             | _                                                                                                           |               | _                            | FRESET           | _                | UINC            |  |  |  |  |  |

| bit 15       |                                             |                                                                                                             |               |                              |                  |                  | bit 8           |  |  |  |  |  |

|              |                                             |                                                                                                             |               |                              |                  |                  |                 |  |  |  |  |  |

| U-0          | U-0                                         | R/W-0                                                                                                       | U-0           | R/W-0                        | R/W-0            | R/W-0            | R/W-0           |  |  |  |  |  |

|              | _                                           | TEFTSEN <sup>(1)</sup>                                                                                      |               | TEFOVIE                      | TEFFIE           | TEFHIE           | TEFNEIE         |  |  |  |  |  |

| bit 7        |                                             |                                                                                                             |               |                              |                  |                  | bit (           |  |  |  |  |  |

| Legend:      |                                             | S = Settable bit                                                                                            |               | HC = Hardwa                  | are Clearable b  | it               |                 |  |  |  |  |  |

| R = Readab   | le hit                                      | W = Writable bit                                                                                            |               |                              | mented bit, read |                  |                 |  |  |  |  |  |

| -n = Value a |                                             | '1' = Bit is set                                                                                            |               | '0' = Bit is cle             |                  | x = Bit is unki  | n               |  |  |  |  |  |

|              |                                             |                                                                                                             |               |                              |                  |                  | IOWIT           |  |  |  |  |  |

| bit 15-11    | Unimplemer                                  | nted: Read as '0'                                                                                           |               |                              |                  |                  |                 |  |  |  |  |  |

| bit 10       | FRESET: FIF                                 | O Reset bit                                                                                                 |               |                              |                  |                  |                 |  |  |  |  |  |

|              |                                             | I be reset when b                                                                                           |               |                              | are when FIFO    | is reset; the us | ser should poll |  |  |  |  |  |

|              |                                             | this bit is clear be                                                                                        | fore taking   | any action                   |                  |                  |                 |  |  |  |  |  |

| 1.1.0        | 0 = No effec                                |                                                                                                             |               |                              |                  |                  |                 |  |  |  |  |  |

| bit 9        | •                                           | nted: Read as '0'                                                                                           |               |                              |                  |                  |                 |  |  |  |  |  |

| bit 8        | UINC: Incren                                |                                                                                                             | C toil will i | noromont by a c              | ingle message    |                  |                 |  |  |  |  |  |

|              |                                             | s bit is set, the FIF<br>will not increment                                                                 |               | ncrement by a s              | single message   |                  |                 |  |  |  |  |  |

| bit 7-6      | Unimplemer                                  | nted: Read as '0'                                                                                           |               |                              |                  |                  |                 |  |  |  |  |  |

| bit 5        | TEFTSEN: T                                  | ransmit Event FIF                                                                                           | O Timestar    | mp Enable bit <sup>(1)</sup> | 1                |                  |                 |  |  |  |  |  |

|              | 1 = Timestamps elements in TEF              |                                                                                                             |               |                              |                  |                  |                 |  |  |  |  |  |

|              | 0 = Does not                                | 0 = Does not timestamp elements in TEF                                                                      |               |                              |                  |                  |                 |  |  |  |  |  |

| bit 4        | Unimplemer                                  | nted: Read as '0'                                                                                           |               |                              |                  |                  |                 |  |  |  |  |  |

| bit 3        | TEFOVIE: Tr                                 | ansmit Event FIF                                                                                            | Overflow      | Interrupt Enabl              | e bit            |                  |                 |  |  |  |  |  |

|              | 1 = Interrupt is enabled for overflow event |                                                                                                             |               |                              |                  |                  |                 |  |  |  |  |  |

|              | •                                           | is disabled for ove                                                                                         |               |                              |                  |                  |                 |  |  |  |  |  |

| bit 2        |                                             | nsmit Event FIFO                                                                                            |               | pt Enable bit                |                  |                  |                 |  |  |  |  |  |

|              | •                                           | <ul> <li>1 = Interrupt is enabled for FIFO full</li> <li>0 = Interrupt is disabled for FIFO full</li> </ul> |               |                              |                  |                  |                 |  |  |  |  |  |

| bit 1        | •                                           | nsmit Event FIFO                                                                                            |               | terrupt Enable I             | oit              |                  |                 |  |  |  |  |  |

|              |                                             | is enabled for FIF                                                                                          |               |                              |                  |                  |                 |  |  |  |  |  |

|              |                                             | is disabled for FIF                                                                                         |               |                              |                  |                  |                 |  |  |  |  |  |

| bit 0        | TEFNEIE: Tr                                 | ansmit Event FIF                                                                                            | O Not Empt    | ty Interrupt Enal            | ble bit          |                  |                 |  |  |  |  |  |

|              | 1 = Interrupt                               | is enabled for FIF                                                                                          | O not empt    | У                            |                  |                  |                 |  |  |  |  |  |

|              | 0 = Interrupt                               | is disabled for FIF                                                                                         | O not emp     | ty                           |                  |                  |                 |  |  |  |  |  |

|              |                                             |                                                                                                             |               |                              |                  |                  |                 |  |  |  |  |  |

**Note 1:** These bits can only be modified in Configuration mode (OPMOD<2:0> = 100).

## REGISTER 3-164: ADCON5H: ADC CONTROL REGISTER 5 HIGH

| U-0               | U-0                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                             | R/W-0                                 | R/W-0                                         | R/W-0            | R/W-0        |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------|------------------|--------------|

|                   | —                                                                                                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                 | WARMTIME3                             | WARMTIME2                                     | WARMTIME1        | WARMTIME     |

| bit 15            |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                 |                                       |                                               |                  | bit          |

|                   |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                 |                                       |                                               |                  |              |

| R/W-0             | U-0                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                             | U-0                                   | U-0                                           | U-0              | U-0          |

| SHRCIE            | <u> </u>                                                                                                                                                                                                                                                         | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                 |                                       | _                                             |                  |              |

| bit 7             |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                 |                                       |                                               |                  | bit          |

| Legend:           |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                 |                                       |                                               |                  |              |

| R = Readab        | le bit                                                                                                                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit                                                                                                                                                                             | U = Unimplem                          | ented bit, read                               | as '0'           |              |

| -n = Value at     | It POR                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                 | '0' = Bit is clea                     | ired                                          | x = Bit is unkno | own          |

| bit 11-8          |                                                                                                                                                                                                                                                                  | etermine the po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                 | e Power-up Delay<br>y in the number o |                                               | rce Clock Perio  | ds (Tcoresro |

| bit 11-8          | These bits de<br>for all ADC c<br>1111 = 3276<br>1110 = 1638<br>1101 = 8192<br>1100 = 4096<br>1011 = 2048<br>1010 = 1024<br>1001 = 5123<br>1000 = 2563<br>0111 = 1283<br>0110 = 64 S<br>0101 = 32 S<br>0100 = 16 S                                               | etermine the po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | wer-up delay<br>Periods<br>Periods<br>Periods<br>Periods<br>Periods<br>eriods<br>eriods<br>eriods<br>riods<br>riods<br>riods                                                    |                                       |                                               | rce Clock Perio  | ds (TCORESRO |

| bit 11-8<br>bit 7 | These bits da<br>for all ADC o<br>1111 = 3276<br>1110 = 1638<br>1101 = 8192<br>1100 = 4096<br>1011 = 2048<br>1010 = 1024<br>1001 = 512 =<br>1000 = 256 =<br>0111 = 128 =<br>0110 = 64 S<br>0101 = 32 S<br>0100 = 16 S<br>00xx = 16 S<br>SHRCIE: Sh<br>1 = Commor | etermine the po<br>fores.<br>38 Source Clock<br>34 Source Clock<br>35 Source Clock<br>35 Source Clock<br>35 Source Clock P<br>35 Source Clock | wer-up delay<br>C Periods<br>Periods<br>Periods<br>Periods<br>Periods<br>Periods<br>eriods<br>eriods<br>eriods<br>riods<br>riods<br>riods<br>riods<br>eredy Corr<br>e generated |                                       | f the Core Sou<br>nable bit<br>is powered and |                  |              |

# REGISTER 3-185: PTGBTE: PTG BROADCAST TRIGGER ENABLE LOW REGISTER<sup>(1)</sup>

| R/W-0            | R/W-0 | R/W-0                | R/W-0   | R/W-0  | R/W-0          | R/W-0    | R/W-0 |

|------------------|-------|----------------------|---------|--------|----------------|----------|-------|

|                  |       |                      | PTGBTE< | <15:8> |                |          |       |

| bit 15           |       |                      |         |        |                |          | bit 8 |

|                  |       |                      |         |        |                |          |       |

| R/W-0            | R/W-0 | R/W-0                | R/W-0   | R/W-0  | R/W-0          | R/W-0    | R/W-0 |

|                  |       |                      | PTGBTE  | <7:0>  |                |          |       |

| bit 7            |       |                      |         |        |                |          | bit 0 |

|                  |       |                      |         |        |                |          |       |

| Legend:          |       |                      |         |        |                |          |       |

| D - Doodoblo hit |       | \// = \//ritable bit |         |        | ontod hit room | 1 00 '0' |       |

| Eogona.           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | read as '0'          |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 15-0 **PTGBTE<15:0>:** PTG Broadcast Trigger Enable bits

1 = Generates trigger when the broadcast command is executed

0 = Does not generate trigger when the broadcast command is executed

Note 1: These bits are read-only when the module is executing Step commands.

## REGISTER 3-186: PTGBTEH: PTG BROADCAST TRIGGER ENABLE HIGH REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 R/W-0 R/W-0 R/W-0 |       | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------------------------|-------|-------|-------|

|        |       |       | PTGBT | E<31:24>                |       |       |       |

| bit 15 |       |       |       |                         |       |       | bit 8 |

|        |       |       |       |                         |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0                   | R/W-0 | R/W-0 | R/W-0 |

| R/W-U         | R/W-U | R/ W-U | R/W-U | R/W-U | R/W-U | R/W-U | R/ W-U |  |  |

|---------------|-------|--------|-------|-------|-------|-------|--------|--|--|

| PTGBTE<23:16> |       |        |       |       |       |       |        |  |  |

| bit 7         |       |        |       |       |       |       | bit 0  |  |  |

|               |       |        |       |       |       |       |        |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 PTGBTE<31:16>: PTG Broadcast Trigger Enable bits

1 = Generates trigger when the broadcast command is executed

0 = Does not generate trigger when the broadcast command is executed

Note 1: These bits are read-only when the module is executing Step commands.

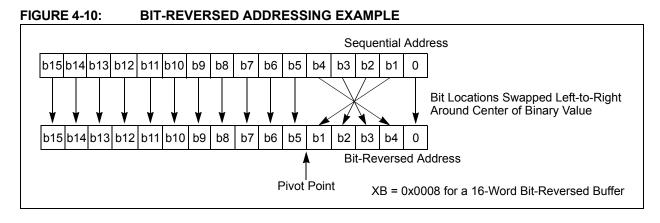

# dsPIC33CH128MP508 FAMILY

## TABLE 4-18: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | s       |    | Bit-Reversed Address |    |    |         |  |

|----|----|-------|-----------|---------|----|----------------------|----|----|---------|--|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2                   | A1 | A0 | Decimal |  |

| 0  | 0  | 0     | 0         | 0       | 0  | 0                    | 0  | 0  | 0       |  |

| 0  | 0  | 0     | 1         | 1       | 1  | 0                    | 0  | 0  | 8       |  |

| 0  | 0  | 1     | 0         | 2       | 0  | 1                    | 0  | 0  | 4       |  |

| 0  | 0  | 1     | 1         | 3       | 1  | 1                    | 0  | 0  | 12      |  |

| 0  | 1  | 0     | 0         | 4       | 0  | 0                    | 1  | 0  | 2       |  |

| 0  | 1  | 0     | 1         | 5       | 1  | 0                    | 1  | 0  | 10      |  |

| 0  | 1  | 1     | 0         | 6       | 0  | 1                    | 1  | 0  | 6       |  |

| 0  | 1  | 1     | 1         | 7       | 1  | 1                    | 1  | 0  | 14      |  |

| 1  | 0  | 0     | 0         | 8       | 0  | 0                    | 0  | 1  | 1       |  |

| 1  | 0  | 0     | 1         | 9       | 1  | 0                    | 0  | 1  | 9       |  |

| 1  | 0  | 1     | 0         | 10      | 0  | 1                    | 0  | 1  | 5       |  |

| 1  | 0  | 1     | 1         | 11      | 1  | 1                    | 0  | 1  | 13      |  |

| 1  | 1  | 0     | 0         | 12      | 0  | 0                    | 1  | 1  | 3       |  |

| 1  | 1  | 0     | 1         | 13      | 1  | 0                    | 1  | 1  | 11      |  |

| 1  | 1  | 1     | 0         | 14      | 0  | 1                    | 1  | 1  | 7       |  |

| 1  | 1  | 1     | 1         | 15      | 1  | 1                    | 1  | 1  | 15      |  |

## 4.5.3 INTERRUPT RESOURCES

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 4.5.3.1 Key Resources

- "Interrupts" (DS70000600) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 4.5.4 INTERRUPT CONTROL AND STATUS REGISTERS

The dsPIC33CH128MP508S1 family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

### 4.5.4.1 INTCON1 through INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the Auxiliary PLL and DO stack overflow status trap sources.

The INTCON4 register contains the Software Generated Hard Trap Status bit (SGHT).

### 4.5.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 4.5.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

### 4.5.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of seven priority levels.

### 4.5.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<7:0>) and Interrupt Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 4-20. For example, INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP<2:0> bits in the first position of IPC0 (IPC0<2:0>).

## 4.5.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to "dsPIC33E Enhanced CPU" (DS70005158) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 4-18 through Register 4-22 on the following pages.

# 4.6.4 INPUT CHANGE NOTIFICATION (ICN)

The Input Change Notification function of the I/O ports allows the dsPIC33CH128MP508S1 family devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State. Five control registers are associated with the Change Notification (CN) functionality of each I/O port. To enable the Change Notification feature for the port, the ON bit (CNCONx<15>) must be set.

The CNEN0x and CNEN1x registers contain the CN interrupt enable control bits for each of the input pins. The setting of these bits enables a CN interrupt for the corresponding pins. Also, these bits, in combination with the CNSTYLE bit (CNCONx<11>), define a type of transition when the interrupt is generated. Possible CN event options are listed in Table 4-26.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. In addition to the CNSTATx register, the CNFx register is implemented for each port. This register contains flags for Change Notification events. These flags are set if the valid transition edge, selected in the CNEN0x and CNEN1x registers, is detected. CNFx stores the occurrence of the event. CNFx bits must be cleared in software to get the next Change Notification interrupt. The CN interrupt is generated only for the I/Os configured as inputs (corresponding TRISx bits must be set).

### TABLE 4-26: CHANGE NOTIFICATION EVENT OPTIONS

| CNSTYLE Bit<br>(CNCONx<11>) | CNEN1x<br>Bit      | CNEN0x<br>Bit | Change Notification Event<br>Description                                              |

|-----------------------------|--------------------|---------------|---------------------------------------------------------------------------------------|

| 0                           | Does not<br>matter | 0             | Disabled                                                                              |

| 0                           | Does not<br>matter | 1             | Detects a mismatch between<br>the last read state and the<br>current state of the pin |

| 1                           | 0                  | 0             | Disabled                                                                              |

| 1                           | 0                  | 1             | Detects a positive transition<br>only (from '0' to '1')                               |

| 1                           | 1                  | 0             | Detects a negative transition<br>only (from '1' to '0')                               |

| 1                           | 1                  | 1             | Detects both positive and<br>negative transitions                                     |

Note: Pull-ups and pull-downs on Input Change Notification pins should always be disabled when the port pin is configured as a digital output.

### EXAMPLE 4-3: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

| Register              | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-----------------------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|

| RPOR0                 | —      | —      | RP33R5  | RP33R4  | RP33R3  | RP33R2  | RP33R1  | RP33R0  |       |       | RP32R5  | RP32R4  | RP32R3  | RP32R2  | RP32R1  | RP32R0  |

| RPOR1                 | —      | —      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | —     |       | RP34R5  | RP34R4  | RP34R3  | RP34R2  | RP34R1  | RP34R0  |

| RPOR2                 | —      | —      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  | —     |       | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  |

| RPOR3                 | —      | —      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  | —     |       | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  |

| RPOR4                 | —      | —      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | —     |       | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  |

| RPOR5                 | —      | —      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | —     |       | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  |

| RPOR6                 | —      | —      | RP45R5  | RP45R4  | RP45R3  | RP45R2  | RP45R1  | RP45R0  | —     |       | RP44R5  | RP44R4  | RP44R3  | RP44R2  | RP44R1  | RP44R0  |

| RPOR7                 | —      | —      | RP47R5  | RP47R4  | RP47R3  | RP47R2  | RP47R1  | RP47R0  | —     |       | RP46R5  | RP46R4  | RP46R3  | RP46R2  | RP46R1  | RP46R0  |

| RPOR8                 | —      | —      | RP49R5  | RP49R4  | RP49R3  | RP49R2  | RP49R1  | RP49R0  | —     |       | RP48R5  | RP48R4  | RP48R3  | RP48R2  | RP48R1  | RP48R0  |

| RPOR9                 | —      | —      | RP51R5  | RP51R4  | RP51R3  | RP51R2  | RP51R1  | RP51R0  | —     |       | RP50R5  | RP50R4  | RP50R3  | RP50R2  | RP50R1  | RP50R0  |

| RPOR10                | —      | —      | RP53R5  | RP53R4  | RP53R3  | RP53R2  | RP53R1  | RP53R0  | —     |       | RP52R5  | RP52R4  | RP52R3  | RP52R2  | RP52R1  | RP52R0  |

| RPOR11                | —      | —      | RP55R5  | RP55R4  | RP55R3  | RP55R2  | RP55R1  | RP55R0  | —     |       | RP54R5  | RP54R4  | RP54R3  | RP54R2  | RP54R1  | RP54R0  |

| RPOR12                | —      | —      | RP57R5  | RP57R4  | RP57R3  | RP57R2  | RP57R1  | RP57R0  | —     |       | RP56R5  | RP56R4  | RP56R3  | RP56R2  | RP56R1  | RP56R0  |

| RPOR13                | —      | —      | RP59R5  | RP59R4  | RP59R3  | RP59R2  | RP59R1  | RP59R0  | —     |       | RP58R5  | RP58R4  | RP58R3  | RP58R2  | RP58R1  | RP58R0  |

| RPOR14                | —      | —      | RP61R5  | RP61R4  | RP61R3  | RP61R2  | RP61R1  | RP61R0  | —     |       | RP60R5  | RP60R4  | RP60R3  | RP60R2  | RP60R1  | RP60R0  |

| RPOR15                | —      | —      | RP63R5  | RP63R4  | RP63R3  | RP63R2  | RP63R1  | RP63R0  | —     |       | RP62R5  | RP62R4  | RP62R3  | RP62R2  | RP62R1  | RP62R0  |

| RPOR16                | —      | —      | RP65R5  | RP65R4  | RP65R3  | RP65R2  | RP65R1  | RP65R0  | —     |       | RP64R5  | RP64R4  | RP64R3  | RP64R2  | RP64R1  | RP64R0  |

| RPOR17                | _      | _      | RP67R5  | RP67R4  | RP67R3  | RP67R2  | RP67R1  | RP67R0  | _     | _     | RP66R5  | RP66R4  | RP66R3  | RP66R2  | RP66R1  | RP66R0  |

| RPOR18                | _      | _      | RP69R5  | RP69R4  | RP69R3  | RP69R2  | RP69R1  | RP69R0  | _     | _     | RP68R5  | RP68R4  | RP68R3  | RP68R2  | RP68R1  | RP68R0  |

| RPOR19                | _      | _      | RP71R5  | RP71R4  | RP71R3  | RP71R2  | RP71R1  | RP71R0  | _     | _     | RP70R5  | RP70R4  | RP70R3  | RP70R2  | RP70R1  | RP70R0  |

| RPOR20 <sup>(1)</sup> | —      | —      | RP171R5 | RP171R4 | RP171R3 | RP177R2 | RP171R1 | RP171R0 | —     | _     | RP170R5 | RP170R4 | RP170R3 | RP170R2 | RP170R1 | RP170R0 |

| RPOR21 <sup>(1)</sup> | —      | —      | RP173R5 | RP173R4 | RP173R3 | RP173R2 | RP173R1 | RP173R0 | —     | _     | RP172R5 | RP172R4 | RP172R3 | RP172R2 | RP172R1 | RP172R0 |

| RPOR22 <sup>(1)</sup> | _      | _      | RP175R5 | RP175R4 | RP175R3 | RP175R2 | RP175R1 | RP175R0 | _     | _     | RP174R5 | RP174R4 | RP174R3 | RP174R2 | RP174R1 | RP174R0 |

# TABLE 4-32: SLAVE PPS OUTPUT CONTROL REGISTERS

Note 1: The RPOR20, RPOR21 and RPOR22 registers are for virtual output pins.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP61R5 | RP61R4 | RP61R3 | RP61R2 | RP61R1 | RP61R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP60R5 | RP60R4 | RP60R3 | RP60R2 | RP60R1 | RP60R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

### REGISTER 4-74: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|