Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                 |

|--------------------------|---------------------------------------------------------------------------------|

|                          | Antico                                                                          |

| oduct Status             | Active                                                                          |

| ore Processor            | dsPIC                                                                           |

| ore Size                 | 16-Bit Dual-Core                                                                |

| peed                     | 180MHz, 200MHz                                                                  |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| eripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| umber of I/O             | 53                                                                              |

| ogram Memory Size        | 88KB (88K x 8)                                                                  |

| ogram Memory Type        | FLASH, PRAM                                                                     |

| PROM Size                | -                                                                               |

| AM Size                  | 20K x 8                                                                         |

| ltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| ita Converters           | A/D 34x12b; D/A 4x12b                                                           |

| cillator Type            | Internal                                                                        |

| erating Temperature      | -40°C ~ 85°C (TA)                                                               |

| ounting Type             | Surface Mount                                                                   |

| ckage / Case             | 64-TQFP                                                                         |

| pplier Device Package    | 64-TQFP (10x10)                                                                 |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp206-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 7: 48-PIN QFN/TQFP/UQFN

| Pin#     | Master Core                                                           | Slave Core                                                                                                     |

|----------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1        | RP46/PWM1H/RB14                                                       | <b>\$1RP46</b> /\$1PWM6L/\$1RB14                                                                               |

|          | RP47/PWM1L/RB15                                                       | <b>S1RP47</b> /S1PWM6H/S1RB15                                                                                  |

|          | <b>RP60</b> /RC12                                                     | <b>S1RP60</b> /S1PWM3H/S1RC12                                                                                  |

| 4        | RP61/RC13                                                             | \$1RP61/\$1PWM3L/\$1RC13                                                                                       |

| 5        | MCLR                                                                  |                                                                                                                |

| 6        | RD13                                                                  | S1ANN0/S1PGA1N2/S1RD13                                                                                         |

| 7        | AN12/IBIAS3/ <b>RP48</b> /RC0                                         | S1AN10/ <b>S1RP48</b> /S1RC0                                                                                   |

| 8        | ANO/CMP1A/RA0                                                         | S1RA0                                                                                                          |

| 9        | AN1/RA1                                                               | S1AN15/S1RA1                                                                                                   |

| _        | AN2/RA2                                                               | \$1AN16/\$1RA2                                                                                                 |

|          | AN3/IBIAS0/RA3                                                        | S1AN0/S1CMP1A/S1PGA1P1/S1RA3                                                                                   |

| 12       | AN4/IBIAS1/RA4                                                        | S1MCLR3/S1AN1/S1CMP2A/S1PGA2P1/S1PGA3P2/S1RA4                                                                  |

|          | AVDD                                                                  | AVDD                                                                                                           |

|          | AVSS                                                                  | AVSS                                                                                                           |

|          | AN13/ISRC0/ <b>RP49</b> /RC1                                          | S1ANA1/ <b>S1RP49</b> /S1RC1                                                                                   |

|          | AN14/ISRC1/ <b>RP50</b> /RC2                                          | S1ANA0/S1RP50/S1RC2                                                                                            |

|          | RP54/RC6                                                              | S1AN11/S1CMP1B/ <b>S1RP54</b> /S1RC6                                                                           |

| 18       |                                                                       |                                                                                                                |

|          | VDD                                                                   | VDD                                                                                                            |

| 19       | VSS                                                                   | VSS                                                                                                            |

| 20       | CMP1B/ <b>RP51</b> /RC3                                               | \$1AN8/\$1CMP3B/\$1RP51/\$1RC3                                                                                 |

| 21       | OSCI/CLKI/AN5/RP32/RB0                                                | \$1AN5/ <b>\$1RP32</b> /\$1RB0                                                                                 |

| 22       | OSCO/CLKO/AN6/IBIAS2/RP33/RB1                                         | \$1AN4/\$1RP33/\$1RB1                                                                                          |

| 23       | ISRC3/RD10                                                            | \$1AN13/\$1CMP2B/\$1RD10                                                                                       |

| 24<br>25 | AN15/ISRC2/ <b>RP55</b> /RC7  DACOUT/AN7/CMP1D/ <b>RP34</b> /INT0/RB2 | \$1AN12/ <b>S1RP55</b> /\$1RC7<br>\$1MCLR2/\$1AN3/\$1ANC0/\$1ANC1/\$1CMP1D/\$1CMP2D/\$1CMP3D/ <b>\$1RP34</b> / |

|          | Bridge in William I Brid Gamillian BE                                 | \$1INT0/\$1RB2                                                                                                 |

| 26       | PGD2/AN8/ <b>RP35</b> /RB3                                            | S1PGD2/S1AN18/S1CMP3A/S1PGA3P1/ <b>S1RP35</b> /S1RB3                                                           |

| 27       | PGC2/ <b>RP36</b> /RB4                                                | S1PGC2/S1AN9/ <b>S1RP36</b> /S1PWM5L/S1RB4                                                                     |

| 28       | RP56/ASDA1/SCK2/RC8                                                   | <b>S1RP56</b> /S1ASDA1/S1SCK1/S1RC8                                                                            |

| 29       | RP57/ASCL1/SDI2/RC9                                                   | S1RP57/S1ASCL1/S1SDI1/S1RC9                                                                                    |

| 30       | SDO2/PCI19/RD8                                                        | S1SDO1/S1PCI19/S1RD8                                                                                           |

| 31       | Vss                                                                   | Vss                                                                                                            |

| 32       | VDD                                                                   | VDD                                                                                                            |

| 33       | PGD3/ <b>RP37</b> /SDA2/RB5                                           | S1PGD3/ <b>S1RP37</b> /S1RB5                                                                                   |

| 34       | PGC3/RP38/SCL2/RB6                                                    | S1PGC3/ <b>S1RP38</b> /S1RB6                                                                                   |

| 35       | TDO/AN9/ <b>RP39</b> /RB7                                             | S1MCLR1/S1AN6/ <b>S1RP39</b> /S1PWM5H/S1RB7                                                                    |

| 36       | PGD1/AN10/RP40/SCL1/RB8                                               | S1PGD1/S1AN7/ <b>S1RP40</b> /S1SCL1/S1RB8                                                                      |

| 37       | PGC1/AN11/ <b>RP41</b> /SDA1/RB9                                      | S1PGC1/ <b>S1RP41</b> /S1SDA1/S1RB9                                                                            |

| 38       | RP52/RC4                                                              | S1RP52/S1PWM2H/S1RC4                                                                                           |

| 39       | RP53/RC5                                                              | S1RP53/S1PWM2L/S1RC5                                                                                           |

| 40       | RP58/RC10                                                             | <b>S1RP58</b> /S1PWM1H/S1RC10                                                                                  |

| 41       | RP59/RC11                                                             | <b>S1RP59</b> /S1PWM1L/S1RC11                                                                                  |

| 42       | Vss                                                                   | Vss                                                                                                            |

| 43       | VDD                                                                   | VDD                                                                                                            |

| 44       | RP65/RD1                                                              | <b>S1RP65</b> /S1PWM4H/S1RD1                                                                                   |

| 45       | TMS/ <b>RP42</b> /PWM3H/RB10                                          | S1RP42/S1PWM8L/S1RB10                                                                                          |

| 46       | TCK/ <b>RP43</b> /PWM3L/RB11                                          | <b>S1RP43</b> /S1PWM8H/S1RB11                                                                                  |

| 47       | TDI/ <b>RP44</b> /PWM2H/RB12                                          | S1RP44/S1PWM7L/S1RB12                                                                                          |

| 48       | RP45/PWM2L/RB13                                                       | <b>S1RP45</b> /S1PWM7H/S1RB13                                                                                  |

| .0       |                                                                       | Tena secon minimonia io                                                                                        |

Legend: RPn and S1RPn represent remappable pins for Peripheral Pin Select functions.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(1)</sup>          | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                                                                          |

|----------------------------------|-------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| MCLR/S1MCLR1/S1MCLR2/<br>S1MCLR3 | I/P         | ST             | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device. S1MCLRx is valid only for slave debug in Dual Debug mode. |

| AVDD                             | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times.                                                         |

| AVss                             | Р           | Р              | No  | Ground reference for analog modules. This pin must be connected at all times.                                                        |

| VDD                              | Р           | _              | No  | Positive supply for peripheral logic and I/O pins                                                                                    |

| Vss                              | Р           | _              | No  | Ground reference for logic and I/O pins                                                                                              |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog input P = Power I = Input TTL = TTL input buffer

- Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

- 2: These pins are remappable as well as dedicated. Some of the pins are associated with the Slave function and have S1 attached to the beginning of the name. For example, AN0 for the Slave is S1AN0.

- **3:** S1 attached to the beginning of the name indicates the Slave feature for that function. For example, AN0 for the Slave is S1AN0.

#### REGISTER 3-18: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|---------|---------|-------|-------|-------|

| NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE | OVBTE | COVTE |

| bit 15 |        |        |         |         |       |       | bit 8 |

| R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|----------|---------|---------|---------|---------|--------|---------|-------|

| SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL | _     |

| bit 7    |         |         |         |         |        |         | bit 0 |

| Le | eg | е | n | d |   |

|----|----|---|---|---|---|

|    | Ü  | _ |   |   | - |

bit 11

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **NSTDIS:** Interrupt Nesting Disable bit

1 = Interrupt nesting is disabled

0 = Interrupt nesting is enabled

bit 14 **OVAERR:** Accumulator A Overflow Trap Flag bit

1 = Trap was caused by an overflow of Accumulator A

0 = Trap was not caused by an overflow of Accumulator A

bit 13 OVBERR: Accumulator B Overflow Trap Flag bit

1 = Trap was caused by an overflow of Accumulator B

0 = Trap was not caused by an overflow of Accumulator B

bit 12 COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit

1 = Trap was caused by a catastrophic overflow of Accumulator A

0 = Trap was not caused by a catastrophic overflow of Accumulator A

COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit

1 = Trap was caused by a catastrophic overflow of Accumulator B

0 = Trap was not caused by a catastrophic overflow of Accumulator B

bit 10 **OVATE:** Accumulator A Overflow Trap Enable bit

1 = Trap overflow of Accumulator A

0 = Trap is disabled

bit 9 **OVBTE:** Accumulator B Overflow Trap Enable bit

1 = Trap overflow of Accumulator B

0 = Trap is disabled

bit 8 **COVTE**: Catastrophic Overflow Trap Enable bit

1 = Trap catastrophic overflow of Accumulator A or B is enabled

0 = Trap is disabled

bit 7 SFTACERR: Shift Accumulator Error Status bit

1 = Math error trap was caused by an invalid accumulator shift

0 = Math error trap was not caused by an invalid accumulator shift

#### REGISTER 3-22: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0    | U-0 | R-0   | U-0 | R-0  | R-0  | R-0  | R-0   |

|--------|-----|-------|-----|------|------|------|-------|

| _      | _   | VHOLD | _   | ILR3 | ILR2 | ILR1 | ILR0  |

| bit 15 |     |       |     |      |      |      | bit 8 |

| R-0     |

|---------|---------|---------|---------|---------|---------|---------|---------|

| VECNUM7 | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 VHOLD: Vector Number Capture Enable bit

1 = VECNUM<7:0> bits read current value of vector number encoding tree (i.e., highest priority pending

interrupt)

0 = Vector number latched into VECNUM<7:0> at Interrupt Acknowledge and retained until next IACK

bit 12 **Unimplemented:** Read as '0'

bit 11-8 ILR<3:0>: New CPU Interrupt Priority Level bits

1111 = CPU Interrupt Priority Level is 15

. . .

0001 = CPU Interrupt Priority Level is 1 0000 = CPU Interrupt Priority Level is 0

bit 7-0 **VECNUM<7:0>:** Vector Number of Pending Interrupt bits

11111111 = 255, Reserved; do not use

•

00001001 = 9, IC1 - Input Capture 1

00001000 = 8, INT0 - External Interrupt 0

00000111 = 7, Reserved; do not use

00000110 = 6, Generic soft error trap

00000101 = 5, Reserved; do not use

00000100 = 4, Math error trap

00000011 = 3, Stack error trap

00000010 = 2, Generic hard trap

00000001 = 1, Address error trap

00000000 = 0, Oscillator fail trap

#### REGISTER 3-28: CNPUx: CHANGE NOTIFICATION PULL-UP ENABLE FOR PORTX REGISTER

| R/W-0  | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | CNPUx<15:8> |       |       |       |       |       |       |  |  |  |

| bit 15 |             |       |       |       |       |       | bit 8 |  |  |  |

| R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | CNPUx<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 | bit 7      |       |       |       |       |       |       |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 CNPUx<15:0>: Change Notification Pull-up Enable for PORTx bits

1 = The pull-up for PORTx[n] is enabled – takes precedence over the pull-down selection

0 = The pull-up for PORTx[n] is disabled

#### REGISTER 3-29: CNPDx: CHANGE NOTIFICATION PULL-DOWN ENABLE FOR PORTX REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-------|-------|-------|--------|-------|-------|-------|--|

|        |       |       | CNPD  | <15:8> |       |       |       |  |

| bit 15 |       |       |       |        |       |       |       |  |

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-------------|-------|-------|--------|-------|-------|-------|--|--|--|

|       |             |       | CNPD  | x<7:0> |       |       |       |  |  |  |

| bit 7 | bit 7 bit 0 |       |       |        |       |       |       |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 CNPDx<15:0>: Change Notification Pull-Down Enable for PORTx bits

1 = The pull-down for PORTx[n] is enabled (if the pull-up for PORTx[n] is not enabled)

0 = The pull-down for PORTx[n] is disabled

#### REGISTER 3-53: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| U2DSRR7 | U2DSRR6 | U2DSRR5 | U2DSRR4 | U2DSRR3 | U2DSRR2 | U2DSRR1 | U2DSRR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| U2RXR7 | U2RXR6 | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **U2DSRR<7:0>:** Assign UART2 Data-Set-Ready (U2DSR) to the Corresponding RPn Pin bits

See Table 3-30.

bit 7-0 U2RXR<7:0>: Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits

See Table 3-30.

#### REGISTER 3-54: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SCK1R7 | SCK1R6 | SCK1R5 | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SDI1R7 | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 SCK1R<7:0>: Assign SPI1 Clock Input (SCK1IN) to the Corresponding RPn Pin bits

See Table 3-30.

bit 7-0 SDI1R<7:0>: Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits

See Table 3-30.

#### REGISTER 3-84: RPOR16: PERIPHERAL PIN SELECT OUTPUT REGISTER 16

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP65R5 | RP65R4 | RP65R3 | RP65R2 | RP65R1 | RP65R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP64R5 | RP64R4 | RP64R3 | RP64R2 | RP64R1 | RP64R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP65R<5:0>: Peripheral Output Function is Assigned to RP65 Output Pin bits

(see Table 3-33 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP64R<5:0>: Peripheral Output Function is Assigned to RP64 Output Pin bits

(see Table 3-33 for peripheral function numbers)

#### REGISTER 3-85: RPOR17: PERIPHERAL PIN SELECT OUTPUT REGISTER 17

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP67R5 | RP67R4 | RP67R3 | RP67R2 | RP67R1 | RP67R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP66R5 | RP66R4 | RP66R3 | RP66R2 | RP66R1 | RP66R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP67R<5:0>: Peripheral Output Function is Assigned to RP67 Output Pin bits

(see Table 3-33 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP66R<5:0>: Peripheral Output Function is Assigned to RP66 Output Pin bits

(see Table 3-33 for peripheral function numbers)

### REGISTER 3-143: C1TXQUAH: CAN TRANSMIT QUEUE USER ADDRESS REGISTER HIGH<sup>(1)</sup>

| R-x    | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|--------|-----|-----|--------|---------|-----|-----|-------|

|        |     |     | TXQUA< | <31:24> |     |     |       |

| bit 15 |     |     |        |         |     |     | bit 8 |

| R-x   | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|-------|-----|-----|--------|---------|-----|-----|-------|

|       |     |     | TXQUA< | <23:16> |     |     |       |

| bit 7 |     |     |        |         |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **TXQUA<31:16>:** TXQ User Address bits

A read of this register will return the address where the next message is to be written (TXQ head).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

#### REGISTER 3-144: C1TXQUAL: CAN TRANSMIT QUEUE USER ADDRESS REGISTER LOW(1)

| R-x         | R-x | R-x | R-x | R-x | R-x | R-x | R-x   |  |

|-------------|-----|-----|-----|-----|-----|-----|-------|--|

| TXQUA<15:8> |     |     |     |     |     |     |       |  |

| bit 15      |     |     |     |     |     |     | bit 8 |  |

| R-x        | R-x | R-x | R-x | R-x | R-x | R-x | R-x   |  |  |

|------------|-----|-----|-----|-----|-----|-----|-------|--|--|

| TXQUA<7:0> |     |     |     |     |     |     |       |  |  |

| bit 7      |     |     |     |     |     |     | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **TXQUA<15:0>:** TXQ User Address bits

A read of this register will return the address where the next message is to be written (TXQ head).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

#### REGISTER 3-174: ADIEL: ADC INTERRUPT ENABLE REGISTER LOW

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | IE<1  | 5:8>  |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | IE<   | 7:0>  |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **IE<15:0>:** Common Interrupt Enable bits

1 = Common and individual interrupts are enabled for the corresponding channel

0 = Common and individual interrupts are disabled for the corresponding channel

#### REGISTER 3-175: ADIEH: ADC INTERRUPT ENABLE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| _     | _   | _   |       |       | IE<20:16> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 **IE<20:16>:** Common Interrupt Enable bits

1 = Common and individual interrupts are enabled for the corresponding channel

0 = Common and individual interrupts are disabled for the corresponding channel

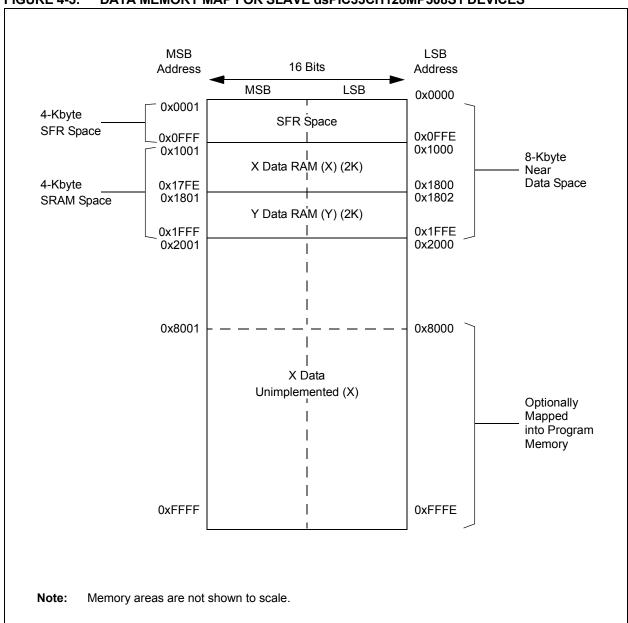

FIGURE 4-5: DATA MEMORY MAP FOR SLAVE dsPIC33CH128MP508S1 DEVICES

#### REGISTER 4-19: INTCON2: SLAVE INTERRUPT CONTROL REGISTER 2

| R/W-1  | R/W-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-------|--------|-----|-----|-----|-----|-------|

| GIE    | DISI  | SWTRAP | _   | _   | _   | _   | _     |

| bit 15 | •     |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|--------|--------|--------|--------|

| _     | _   | _   | _   | INT3EP | INT2EP | INT1EP | INT0EP |

| bit 7 |     |     |     |        |        |        | bit 0  |

Legend:

R = Readable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Gle: Global Interrupt Enable bit

1 = Interrupts and associated IE bits are enabled

0 = Interrupts are disabled, but traps are still enabled

bit 14 DISI: DISI Instruction Status bit

1 = DISI instruction is active

0 = DISI instruction is not active

bit 13 SWTRAP: Software Trap Status bit

1 = Software trap is enabled

0 = Software trap is disabled

bit 12-4 Unimplemented: Read as '0'

bit 3 INT3EP: External Interrupt 3 Edge Detect Polarity Select bit

1 = Interrupt on negative edge

0 = Interrupt on positive edge

bit 2 INT2EP: External Interrupt 2 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 1 INT1EP: External Interrupt 1 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 0 INT0EP: External Interrupt 0 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

#### REGISTER 4-28: CNPUx: CHANGE NOTIFICATION PULL-UP ENABLE FOR PORTX REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | CNPUx | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | CNPU  | x<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 CNPUx<15:0>: Change Notification Pull-up Enable for PORTx bits

1 = The pull-up for PORTx[n] is enabled – takes precedence over pull-down selection

0 = The pull-up for PORTx[n] is disabled

#### REGISTER 4-29: CNPDx: CHANGE NOTIFICATION PULL-DOWN ENABLE FOR PORTX REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | CNPDx | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | CNPD  | x<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 CNPDx<15:0>: Change Notification Pull-Down Enable for PORTx bits

1 = The pull-down for PORTx[n] is enabled (if the pull-up for PORTx[n] is not enabled)

0 = The pull-down for PORTx[n] is disabled

# 4.6.4 INPUT CHANGE NOTIFICATION (ICN)

The Input Change Notification function of the I/O ports allows the dsPIC33CH128MP508S1 family devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State. Five control registers are associated with the Change Notification (CN) functionality of each I/O port. To enable the Change Notification feature for the port, the ON bit (CNCONx<15>) must be set.

The CNEN0x and CNEN1x registers contain the CN interrupt enable control bits for each of the input pins. The setting of these bits enables a CN interrupt for the corresponding pins. Also, these bits, in combination with the CNSTYLE bit (CNCONx<11>), define a type of transition when the interrupt is generated. Possible CN event options are listed in Table 4-26.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. In addition to the CNSTATx register, the CNFx register is implemented for each port. This register contains flags for Change Notification events. These flags are set if the valid transition edge, selected in the CNEN0x and CNEN1x registers, is detected. CNFx stores the occurrence of the event. CNFx bits must be cleared in software to get the next Change Notification interrupt. The CN interrupt is generated only for the I/Os configured as inputs (corresponding TRISx bits must be set).

TABLE 4-26: CHANGE NOTIFICATION EVENT OPTIONS

| CNSTYLE Bit<br>(CNCONx<11>) | CNEN1x<br>Bit   | CNEN0x<br>Bit | Change Notification Event<br>Description                                              |

|-----------------------------|-----------------|---------------|---------------------------------------------------------------------------------------|

| 0                           | Does not matter | 0             | Disabled                                                                              |

| 0                           | Does not matter | 1             | Detects a mismatch between<br>the last read state and the<br>current state of the pin |

| 1                           | 0               | 0             | Disabled                                                                              |

| 1                           | 0               | 1             | Detects a positive transition only (from '0' to '1')                                  |

| 1                           | 1               | 0             | Detects a negative transition only (from '1' to '0')                                  |

| 1                           | 1               | 1             | Detects both positive and negative transitions                                        |

Note: Pull-ups and pull-downs on Input Change Notification pins should always be disabled when the port pin is configured as a digital output.

## EXAMPLE 4-3: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

#### 4.6.5 PERIPHERAL PIN SELECT (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 4.6.5.1 Available Pins

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "S1RPn", in their full pin designation, where "n" is the remappable pin number. "S1RP" is used to designate pins that support both remappable input and output functions.

#### 4.6.5.2 Available Peripherals

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. One example includes I<sup>2</sup>C modules. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/Os and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 4.6.5.3 Controlling Peripheral Pin Select

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

TABLE 4-30: SLAVE REMAPPABLE OUTPUT PIN REGISTERS

| Register     | S1RP Pin        | I/O Port           |

|--------------|-----------------|--------------------|

| RPOR0<5:0>   | S1RP32          | Port Pin S1RB0     |

| RPOR0<13:8>  | S1RP33          | Port Pin S1RB1     |

| RPOR1<5:0>   | S1RP34          | Port Pin S1RB2     |

| RPOR1<13:8>  | S1RP35          | Port Pin S1RB3     |

| RPOR2<5:0>   | S1RP36          | Port Pin S1RB4     |

| RPOR2<13:8>  | S1RP37          | Port Pin S1RB5     |

| RPOR3<5:0>   | S1RP38          | Port Pin S1RB6     |

| RPOR3<13:8>  | S1RP39          | Port Pin S1RB7     |

| RPOR4<5:0>   | S1RP40          | Port Pin S1RB8     |

| RPOR4<13:8>  | S1RP41          | Port Pin S1RB9     |

| RPOR5<5:0>   | S1RP42          | Port Pin S1RB10    |

| RPOR5<13:8>  | S1RP43          | Port Pin S1RB11    |

| RPOR6<5:0>   | S1RP44          | Port Pin S1RB12    |

| RPOR6<13:8>  | S1RP45          | Port Pin S1RB13    |

| RPOR7<5:0>   | S1RP46          | Port Pin S1RB14    |

| RPOR7<13:8>  | S1RP47          | Port Pin S1RB15    |

| RPOR8<5:0>   | S1RP48          | Port Pin S1RC0     |

| RPOR8<13:8>  | S1RP49          | Port Pin S1RC1     |

| RPOR9<5:0>   | S1RP50          | Port Pin S1RC2     |

| RPOR9<13:8>  | S1RP51          | Port Pin S1RC3     |

| RPOR10<5:0>  | S1RP52          | Port Pin S1RC4     |

| RPOR10<13:8> | S1RP53          | Port Pin S1RC5     |

| RPOR11<5:0>  | S1RP54          | Port Pin S1RC6     |

| RPOR11<13:8> | S1RP55          | Port Pin S1RC7     |

| RPOR12<5:0>  | S1RP56          | Port Pin S1RC8     |

| RPOR12<13:8> | S1RP57          | Port Pin S1RC9     |

| RPOR13<5:0>  | S1RP58          | Port Pin S1RC10    |

| RPOR13<13:8> | S1RP59          | Port Pin S1RC11    |

| RPOR14<5:0>  | S1RP60          | Port Pin S1RC12    |

| RPOR14<13:8> | S1RP61          | Port Pin S1RC13    |

| RPOR15<5:0>  | S1RP62          | Port Pin S1RC14    |

| RPOR15<13:8> | S1RP63          | Port Pin S1RC15    |

| RPOR16<5:0>  | S1RP64          | Port Pin S1RD0     |

| RPOR16<13:8> | S1RP65          | Port Pin S1RD1     |

| RPOR17<5:0>  | S1RP66          | Port Pin S1RD2     |

| RPOR17<13:8> | S1RP67          | Port Pin S1RD3     |

| RPOR18<5:0>  | S1RP68          | Port Pin S1RD4     |

| RPOR18<13:8> | S1RP69          | Port Pin S1RD5     |

| RPOR19<5:0>  | S1RP70          | Port Pin S1RD6     |

| RPOR19<13:8> | S1RP71          | Port Pin S1RD7     |

|              | S1RP181-S1RP176 | Reserved           |

| RPOR20<5:0>  | S1RP170         | Virtual Pin S1RPV0 |

| RPOR20<13:8> | S1RP171         | Virtual Pin S1RPV1 |

| RPOR21<5:0>  | S1RP172         | Virtual Pin S1RPV2 |

| RPOR21<13:8> | S1RP173         | Virtual Pin S1RPV3 |

| RPOR22<5:0>  | S1RP174         | Virtual Pin S1RPV4 |

| RPOR22<13:8> | S1RP175         | Virtual Pin S1RPV5 |

#### REGISTER 6-8: APLLDIV1: APLL OUTPUT DIVIDER REGISTER (MASTER)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0        | R/W-0 |

|--------|-----|-----|-----|-----|-----|--------------|-------|

| _      | _   | _   | _   | _   | _   | AVCODIV<1:0> |       |

| bit 15 |     |     |     |     |     |              | bit 8 |

| U-0   | R/W-1               | R/W-0 | R/W-0 | U-0 | R/W-0               | R/W-0 | R/W-1 |

|-------|---------------------|-------|-------|-----|---------------------|-------|-------|

| _     | APOST1DIV<2:0>(1,2) |       |       | _   | APOST2DIV<2:0>(1,2) |       |       |

| bit 7 |                     |       |       |     |                     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9-8 AVCODIV<1:0>: APLL VCO Output Divider Select bits

11 = AFVCO 10 = AFVCO/2 01 = AFVCO/3

00 = AFVCO/4

bit 7 **Unimplemented:** Read as '0'

bit 6-4 APOST1DIV<2:0>: APLL Output Divider #1 Ratio bits<sup>(1,2)</sup>

APOST1DIV<2:0> can have a valid value, from 1 to 7 (the APOST1DIVx value should be greater than or equal to the APOST2DIVx value). The APOST1DIVx divider is designed to operate at higher clock

rates than the APOST2DIVx divider.

bit 3 **Unimplemented:** Read as '0'

bit 2-0 APOST2DIV<2:0>: APLL Output Divider #2 Ratio bits<sup>(1,2)</sup>

APOST2DIV < 2:0 > can have a valid value, from 1 to 7 (the APOST2DIVx value should be less than or equal to the APOST1DIVx value). The APOST1DIVx divider is designed to operate at higher clock

rates than the APOST2DIVx divider.

Note 1: The APOST1DIVx and APOST2DIVx values must not be changed while the PLL is operating.

2: The default values for APOST1DIVx and APOST2DIVx are 4 and 1, respectively, yielding a 150 MHz system source clock.

### 8.5 DMA Control Registers

#### REGISTER 8-1: DMACON: DMA ENGINE CONTROL REGISTER

| R/W-0        | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| DMAEN        | _   | _   | _   | _   | _   | _   | _   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| _     | _   | _   | _   | _   | _   | _   | PRSSEL |

| bit 7 |     |     |     |     |     |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **DMAEN:** DMA Module Enable bit

1 = Enables module

0 = Disables module and terminates all active DMA operation(s)

bit 14-1 **Unimplemented:** Read as '0'

bit 0 PRSSEL: Channel Priority Scheme Selection bit

1 = Round robin scheme0 = Fixed priority scheme

#### REGISTER 10-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS (CONTINUED)

bit 3-0 MOD<3:0>: CCPx Mode Select bits

For CCSEL = 1 (Input Capture modes):

1xxx = Reserved

011x = Reserved

0101 = Capture every 16th rising edge

0100 = Capture every 4th rising edge

0011 = Capture every rising and falling edge

0010 = Capture every falling edge

0001 = Capture every rising edge

0000 = Capture every rising and falling edge (Edge Detect mode)

For CCSEL = 0 (Output Compare/Timer modes):

1111 = External Input mode: Pulse generator is disabled, source is selected by ICS<2:0>

1110 = Reserved

110x = Reserved

10xx = Reserved

0111 = Reserved

0110 = Reserved

0101 = Dual Edge Compare mode, buffered

0100 = Dual Edge Compare mode

0011 = 16-Bit/32-Bit Single Edge mode, toggles output on compare match

0010 = 16-Bit/32-Bit Single Edge mode, drives output low on compare match

0001 = 16-Bit/32-Bit Single Edge mode, drives output high on compare match

0000 = 16-Bit/32-Bit Timer mode, output functions are disabled

Note 1: Clock selection is the same for the Master and the Slave.

#### REGISTER 14-6: SPIXIMSKL: SPIX INTERRUPT MASK REGISTER LOW

| U-0    | U-0 | U-0 | R/W-0    | R/W-0  | U-0 | U-0 | R/W-0    |

|--------|-----|-----|----------|--------|-----|-----|----------|

| _      | _   | _   | FRMERREN | BUSYEN | _   | _   | SPITUREN |

| bit 15 |     |     |          |        |     |     | bit 8    |

| R/W-0  | R/W-0    | R/W-0   | U-0 | R/W-0   | U-0 | R/W-0    | R/W-0    |

|--------|----------|---------|-----|---------|-----|----------|----------|

| SRMTEN | SPIROVEN | SPIRBEN |     | SPITBEN | _   | SPITBFEN | SPIRBFEN |

| bit 7  |          |         |     |         |     |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit

1 = Frame error generates an interrupt event

0 = Frame error does not generate an interrupt event

bit 11 BUSYEN: Enable Interrupt Events via SPIBUSY bit

1 = SPIBUSY generates an interrupt event

0 = SPIBUSY does not generate an interrupt event

bit 10-9 **Unimplemented:** Read as '0'

bit 8 SPITUREN: Enable Interrupt Events via SPITUR bit

1 = Transmit Underrun (TUR) generates an interrupt event

0 = Transmit Underrun does not generate an interrupt event

bit 7 SRMTEN: Enable Interrupt Events via SRMT bit

1 = Shift Register Empty (SRMT) generates interrupt events0 = Shift Register Empty does not generate interrupt events

bit 6 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = SPIx Receive Overflow (ROV) generates an interrupt event

0 = SPIx Receive Overflow does not generate an interrupt event

bit 5 SPIRBEN: Enable Interrupt Events via SPIRBE bit

1 = SPIx RX buffer empty generates an interrupt event

0 = SPIx RX buffer empty does not generate an interrupt event

bit 4 Unimplemented: Read as '0'

bit 3 SPITBEN: Enable Interrupt Events via SPITBE bit

1 = SPIx transmit buffer empty generates an interrupt event

${\tt 0}$  = SPIx transmit buffer empty does not generate an interrupt event

bit 2 Unimplemented: Read as '0'

bit 1 SPITBFEN: Enable Interrupt Events via SPITBF bit

1 = SPIx transmit buffer full generates an interrupt event

0 = SPIx transmit buffer full does not generate an interrupt event

bit 0 SPIRBFEN: Enable Interrupt Events via SPIRBF bit

1 = SPIx receive buffer full generates an interrupt event

0 = SPIx receive buffer full does not generate an interrupt event

#### 25.1 **Package Marking Information (Continued)**

48-Lead TQFP (7x7 mm)

Example

CH64MP 2041810 017

48-Lead UQFN (6x6 mm)

Example

64-Lead TQFP (10x10x1 mm)

Example

64-Lead QFN (9x9x0.9 mm)

Example

80-Lead TQFP (12x12x1 mm)