Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 23x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

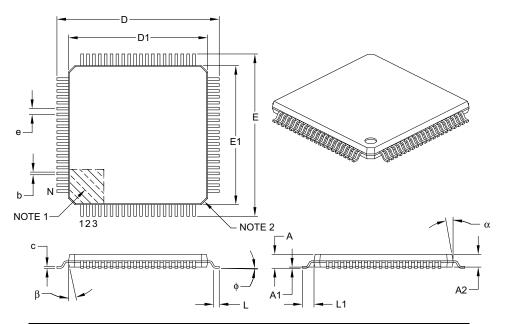

| Package / Case             | 28-UQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp502-e-2n |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 MASTER MODULES

## 3.1 Master CPU

Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "dsPIC33E Enhanced CPU" (DS70005158) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

There are two independent CPU cores in the dsPIC33CH128MP508 family. The Master and Slave cores are similar, except for the fact that the Slave core can run at a higher speed than the Master core.

The Slave core fetches instructions from the PRAM and the Master core fetches the code from the Flash. The Master and Slave cores can run independently asynchronously, at the same speed or at a different speed. This section discusses the Master core.

| Note: | All of the associated register names are the            |

|-------|---------------------------------------------------------|

|       | same on the Master, as well as on the Slave.            |

|       | The Slave code will be developed in a sepa-             |

|       | rate project in $MPLAB^{ otin N} X$ IDE with the device |

|       | selection, dsPIC33CH128MP508S1, where                   |

|       | the S1 indicates the Slave device.                      |

The dsPIC33CH128MP508 family CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for Digital Signal Processing (DSP). The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

## 3.1.1 REGISTERS

The dsPIC33CH128MP508 devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The 16th Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33CH128MP508 devices include four Alternate Working register sets, which consist of W0 through W14. The Alternate Working registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The Alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL7) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register. The Alternate Working registers can also be accessed manually by using the CTXTSWP instruction. The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

## 3.1.2 INSTRUCTION SET

The instruction set for dsPIC33CH128MP508 devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

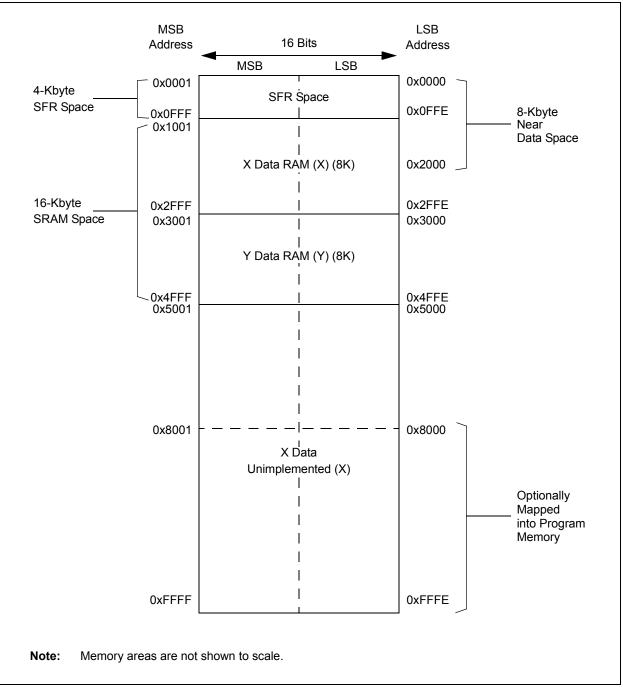

### FIGURE 3-6: DATA MEMORY MAP FOR dsPIC33CH128MP508 DEVICES

# dsPIC33CH128MP508 FAMILY

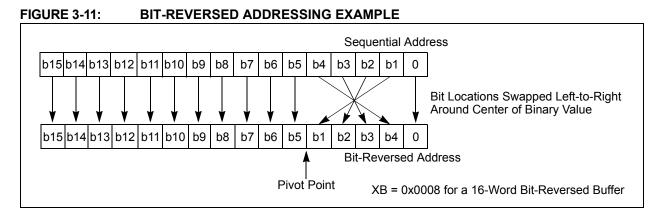

## TABLE 3-21: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

| Normal Address |    |    |    |         |    |    | Bit-Rev | ersed Ac | Idress  |

|----------------|----|----|----|---------|----|----|---------|----------|---------|

| A3             | A2 | A1 | A0 | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0              | 0  | 0  | 0  | 0       | 0  | 0  | 0       | 0        | 0       |

| 0              | 0  | 0  | 1  | 1       | 1  | 0  | 0       | 0        | 8       |

| 0              | 0  | 1  | 0  | 2       | 0  | 1  | 0       | 0        | 4       |

| 0              | 0  | 1  | 1  | 3       | 1  | 1  | 0       | 0        | 12      |

| 0              | 1  | 0  | 0  | 4       | 0  | 0  | 1       | 0        | 2       |

| 0              | 1  | 0  | 1  | 5       | 1  | 0  | 1       | 0        | 10      |

| 0              | 1  | 1  | 0  | 6       | 0  | 1  | 1       | 0        | 6       |

| 0              | 1  | 1  | 1  | 7       | 1  | 1  | 1       | 0        | 14      |

| 1              | 0  | 0  | 0  | 8       | 0  | 0  | 0       | 1        | 1       |

| 1              | 0  | 0  | 1  | 9       | 1  | 0  | 0       | 1        | 9       |

| 1              | 0  | 1  | 0  | 10      | 0  | 1  | 0       | 1        | 5       |

| 1              | 0  | 1  | 1  | 11      | 1  | 1  | 0       | 1        | 13      |

| 1              | 1  | 0  | 0  | 12      | 0  | 0  | 1       | 1        | 3       |

| 1              | 1  | 0  | 1  | 13      | 1  | 0  | 1       | 1        | 11      |

| 1              | 1  | 1  | 0  | 14      | 0  | 1  | 1       | 1        | 7       |

| 1              | 1  | 1  | 1  | 15      | 1  | 1  | 1       | 1        | 15      |

#### REGISTER 3-5: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

| R/W-x                                                                | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |

|----------------------------------------------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                                                                      |       |                  | NVMA  | DR<15:8>                                |       |       |       |

| bit 15                                                               |       |                  |       |                                         |       |       | bit 8 |

| R/W-x                                                                | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |

|                                                                      |       |                  | NVMA  | DR<7:0>                                 |       |       |       |

| bit 7                                                                |       |                  |       |                                         |       |       | bit 0 |

|                                                                      |       |                  |       |                                         |       |       |       |

| Legend:                                                              |       |                  |       |                                         |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                                         |       |       |       |

| -n = Value at P                                                      | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

bit 15-0 **NVMADR<15:0>:** Nonvolatile Memory Lower Write Address bits Selects the lower 16 bits of the location to program or erase in Program Flash Memory. This register may be read or written to by the user application.

#### REGISTER 3-6: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0             | U-0   | U-0              | U-0   | U-0                                     | U-0   | U-0   | U-0   |  |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|

| —               | _     | —                | _     | —                                       | —     | —     |       |  |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |  |

|                 |       |                  |       |                                         |       |       |       |  |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|                 |       |                  | NVMAD | RU<23:16>                               |       |       |       |  |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |  |

|                 |       |                  |       |                                         |       |       |       |  |

| Legend:         |       |                  |       |                                         |       |       |       |  |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADRU<23:16>:** Nonvolatile Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in Program Flash Memory. This register may be read or written to by the user application.

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| U2DSRR7 | U2DSRR6 | U2DSRR5 | U2DSRR4 | U2DSRR3 | U2DSRR2 | U2DSRR1 | U2DSRR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| R/W-0   |

| U2RXR7  | U2RXR6  | U2RXR5  | U2RXR4  | U2RXR3  | U2RXR2  | U2RXR1  | U2RXR0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

#### REGISTER 3-53: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8

U2DSRR<7:0>: Assign UART2 Data-Set-Ready (U2DSR) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0

U2RXR<7:0>: Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits

See Table 3-30.

### REGISTER 3-54: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SCK1R7 | SCK1R6 | SCK1R5 | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SDI1R7 | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  | •      |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 SCK1R<7:0>: Assign SPI1 Clock Input (SCK1IN) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **SDI1R<7:0>:** Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits See Table 3-30.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP45R5 | RP45R4 | RP45R3 | RP45R2 | RP45R1 | RP45R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP44R5 | RP44R4 | RP44R3 | RP44R2 | RP44R1 | RP44R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

#### REGISTER 3-74: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP45R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP45 Output Pin bits (see Table 3-33 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP44R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP44 Output Pin bits (see Table 3-33 for peripheral function numbers) |

#### REGISTER 3-75: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

|        | —   | RP47R5 | RP47R4 | RP47R3 | RP47R2 | RP47R1 | RP47R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|        | —   | RP46R5 | RP46R4 | RP46R3 | RP46R2 | RP46R1 | RP46R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

| Logond |     |        |        |        |        |        |        |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 **RP47R<5:0>:** Peripheral Output Function is Assigned to RP47 Output Pin bits (see Table 3-33 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP46R<5:0>:** Peripheral Output Function is Assigned to RP46 Output Pin bits (see Table 3-33 for peripheral function numbers)

## REGISTER 3-99: DMTPSINTVL: DMT POST-CONFIGURE INTERVAL STATUS REGISTER LOW

| R/W-0                                                                     | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|---------------------------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|

|                                                                           |       |       | PSINT | <sup>-</sup> V<15:8>               |       |       |       |

| bit 15                                                                    |       |       |       |                                    |       |       | bit 8 |

|                                                                           |       |       |       |                                    |       |       |       |

| R/W-0                                                                     | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                                           |       |       | PSIN  | TV<7:0>                            |       |       |       |

| bit 7                                                                     |       |       |       |                                    |       |       | bit 0 |

|                                                                           |       |       |       |                                    |       |       |       |

| Legend:                                                                   |       |       |       |                                    |       |       |       |

| R = Readable bit W = Writable bit                                         |       |       | bit   | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |       |       |       | nown                               |       |       |       |

bit 15-0 **PSINTV<15:0>:** Lower DMT Window Interval Configuration Status bits This is always the value of the FDMTIVTL Configuration register.

#### REGISTER 3-100: DMTPSINTVH: DMT POST-CONFIGURE INTERVAL STATUS REGISTER HIGH

| R/W-0                              | R/W-0 | R/W-0          | R/W-0            | R/W-0        | R/W-0           | R/W-0            | R/W-0 |

|------------------------------------|-------|----------------|------------------|--------------|-----------------|------------------|-------|

|                                    |       |                | PSINT            | V<31:24>     |                 |                  |       |

| bit 15                             |       |                |                  |              |                 |                  | bit 8 |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0            | R/W-0        | R/W-0           | R/W-0            | R/W-0 |

|                                    |       |                | PSINT            | V<23:16>     |                 |                  |       |

| bit 7                              |       |                |                  |              |                 |                  | bit ( |

| Legend:                            |       |                |                  |              |                 |                  |       |

| R = Readable                       | bit   | W = Writable b | oit              | U = Unimplen | nented bit, rea | <b>id as</b> '0' |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cle | ared         | x = Bit is unk  | nown             |       |

bit 15-0 **PSINTV<31:16>:** Higher DMT Window Interval Configuration Status bits This is always the value of the FDMTIVTH Configuration register.

| U-0          | R-1                       | R-0                                                                         | R-0          | R-0               | R-0            | R-0             | R-0   |

|--------------|---------------------------|-----------------------------------------------------------------------------|--------------|-------------------|----------------|-----------------|-------|

| _            |                           |                                                                             |              | RXCODE<6:0>       | >              |                 |       |

| bit 15       |                           |                                                                             |              |                   |                |                 | bit 8 |

| U-0          | R-1                       | R-0                                                                         | R-0          | R-0               | R-0            | R-0             | R-0   |

| _            |                           |                                                                             |              | TXCODE<6:0>       |                |                 |       |

| bit 7        |                           |                                                                             |              |                   |                |                 | bit 0 |

| Legend:      |                           |                                                                             |              |                   |                |                 |       |

| R = Readab   | le bit                    | W = Writable bit                                                            |              | U = Unimplen      | nented bit, re | ad as '0'       |       |

| -n = Value a | It POR                    | '1' = Bit is set                                                            |              | '0' = Bit is clea | ared           | x = Bit is unkr | nown  |

|              |                           | No interrupt<br>111111 = Reserve<br>FIFO 7 interrupt (F                     |              | )                 |                |                 |       |

|              | 0000001 = F               | FIFO 2 interrupt (F<br>FIFO 1 interrupt (F<br>Reserved; FIFO 0              | RFIF1 is set | )                 |                |                 |       |

| bit 7        |                           | nted: Read as '0'                                                           |              |                   |                |                 |       |

| bit 6-0      | -                         | 0>: Transmit Inter                                                          | rupt Flag C  | ode bits          |                |                 |       |

|              | 1000000 = N<br>0001000-01 | 111111 = Reserve<br>No interrupt<br>111111 = Reserve<br>FIFO 7 interrupt (T | ed           | )                 |                |                 |       |

|              |                           | FIFO 1 interrupt (T<br>FIFO 0 interrupt (T                                  |              |                   |                |                 |       |

### REGISTER 3-114: C1VECH: CAN INTERRUPT CODE REGISTER HIGH

| REGISTER 3-159: ADCON2L: ADC CONTROL REGISTER 2 LOW |

|-----------------------------------------------------|

|-----------------------------------------------------|

| R/W-0        | R/W-0                                                                                                    | U-0                                                                                                                        | R/W-0                                                                                                                | U-0                                                                                                | R/W-0                                                                                                    | R/W-0                                                                                                                                                                                     | R/W-0                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| REFCIE       | REFERCIE                                                                                                 |                                                                                                                            | EIEN                                                                                                                 | _                                                                                                  | SHREISEL2(1)                                                                                             | SHREISEL1(1)                                                                                                                                                                              | SHREISEL0 <sup>(1</sup>                                                                                        |

| oit 15       |                                                                                                          |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                                           | bit                                                                                                            |

| U-0          | R/W-0                                                                                                    | R/W-0                                                                                                                      | R/W-0                                                                                                                | R/W-0                                                                                              | R/W-0                                                                                                    | R/W-0                                                                                                                                                                                     | R/W-0                                                                                                          |

|              | SHRADCS6                                                                                                 | SHRADCS5                                                                                                                   | SHRADCS4                                                                                                             | SHRADCS3                                                                                           | SHRADCS2                                                                                                 | SHRADCS1                                                                                                                                                                                  | SHRADCS0                                                                                                       |

| bit 7        |                                                                                                          | 01110120000                                                                                                                | 011012001                                                                                                            | 01110120000                                                                                        | 0111012002                                                                                               |                                                                                                                                                                                           | bit                                                                                                            |

|              |                                                                                                          |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

| Legend:      |                                                                                                          |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

| R = Readab   | ole bit                                                                                                  | W = Writable                                                                                                               | bit                                                                                                                  | U = Unimpler                                                                                       | nented bit, read                                                                                         | as '0'                                                                                                                                                                                    |                                                                                                                |

| -n = Value a | at POR                                                                                                   | '1' = Bit is set                                                                                                           | t                                                                                                                    | '0' = Bit is cle                                                                                   | ared                                                                                                     | x = Bit is unkno                                                                                                                                                                          | own                                                                                                            |

|              |                                                                                                          |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

| bit 15       |                                                                                                          | -                                                                                                                          |                                                                                                                      |                                                                                                    | imon Interrupt E                                                                                         |                                                                                                                                                                                           |                                                                                                                |

|              |                                                                                                          | •                                                                                                                          | •                                                                                                                    | /hen the band<br>band gap read                                                                     | gap becomes re                                                                                           | eady                                                                                                                                                                                      |                                                                                                                |

| bit 14       |                                                                                                          | -                                                                                                                          |                                                                                                                      | •                                                                                                  | mon Interrupt E                                                                                          | nable bit                                                                                                                                                                                 |                                                                                                                |

|              |                                                                                                          |                                                                                                                            |                                                                                                                      | •                                                                                                  | •                                                                                                        | voltage error is                                                                                                                                                                          | detected                                                                                                       |

|              |                                                                                                          |                                                                                                                            |                                                                                                                      |                                                                                                    | reference voltag                                                                                         |                                                                                                                                                                                           |                                                                                                                |

| bit 13       | Unimplemen                                                                                               | ted: Read as                                                                                                               | '0'                                                                                                                  |                                                                                                    |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

| bit 12       | EIEN: Early Ir                                                                                           | nterrupts Enab                                                                                                             | ole bit                                                                                                              |                                                                                                    |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

|              |                                                                                                          |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          | s (when the EIS<br>hen the ANxRD                                                                                                                                                          |                                                                                                                |

| bit 11       | Unimplemen                                                                                               | ted: Read as                                                                                                               | '0'                                                                                                                  |                                                                                                    |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

| bit 10-8     | SHREISEL<2                                                                                               | ::0>: Shared C                                                                                                             | Core Early Inte                                                                                                      | rrupt Time Sel                                                                                     | ection bits <sup>(1)</sup>                                                                               |                                                                                                                                                                                           |                                                                                                                |

|              | 110 = Early ir<br>101 = Early ir<br>100 = Early ir<br>011 = Early ir<br>010 = Early ir<br>001 = Early ir | nterrupt is set a<br>nterrupt is set a | and interrupt is<br>and interrupt is<br>and interrupt is<br>and interrupt is<br>and interrupt is<br>and interrupt is | s generated 7<br>s generated 6<br>s generated 5<br>s generated 4<br>s generated 3<br>s generated 2 | TADCORE Clocks<br>TADCORE Clocks<br>TADCORE Clocks<br>TADCORE Clocks<br>TADCORE Clocks<br>TADCORE Clocks | prior to when the<br>prior to when the | ne data is read<br>ne data is read |

| bit 7        | Unimplemen                                                                                               | ted: Read as                                                                                                               | '0'                                                                                                                  |                                                                                                    |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

| bit 6-0      |                                                                                                          |                                                                                                                            | -                                                                                                                    | t Clock Divide                                                                                     |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

|              | These bits de<br>Clock Period)<br>1111111 = 2                                                            |                                                                                                                            |                                                                                                                      | RESRC (Source                                                                                      | Clock Periods)                                                                                           | for one shared                                                                                                                                                                            | TADCORE (Co                                                                                                    |

|              | <br>0000011 = 6<br>0000010 = 4<br>0000001 = 2<br>0000000 = 2                                             | Source Clock<br>Source Clock                                                                                               | Periods<br>Periods                                                                                                   |                                                                                                    |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

|              | For the 6-bit shar<br>rom '100' to '112                                                                  |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                                           |                                                                                                                |

from '100' to '111', are not valid and should not be used. For the 8-bit shared ADC core resolution (SHRRES<1:0> = 01), the SHREISEL<2:0> settings, '110' and '111', are not valid and should not be used.

#### 4.2.8.1 Data Access from Program Memory Using Table Instructions

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper eight bits of a Program Space word as data.

This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to read byte or word-sized (16-bit) data from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, either the upper or lower byte of the upper program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'. When the upper byte is selected, the 'phantom' byte is read as '0'.

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. For these writes, data is written to a set of NVM latches and subsequently copied to the Program Space address using an NVM write operation. The details of their operation are explained in Section 4.3.2 "RTSP Operation".

|  | şə.                    | altuan ginana                                                                                                                                                                                                          |

|--|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | - 6×000000<br>0/020000 | 23 16 8 0<br>0000000<br>0000000<br>0000000<br>0000000<br>000000                                                                                                                                                        |

|  |                        | TBLEDELE (\$98<0> > 0)<br>TBLEDELE (\$98<0> > 1)<br>TBLEDLE (\$98<0> > 0)<br>TBLEDLE (\$98<0> > 0)<br>TBLEDLE (\$98<0> > 0)                                                                                            |

|  | 9,4800000              | The addrate for the table constition is determined by the data EA<br>within the party defined by the TBUAKG register.<br>Only read operations are chosen; write constitutes are also valid in<br>the true democy area. |

## FIGURE 4-12: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

#### REGISTER 4-47: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| R/W-0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| QEIHOM1R7 | QEIHOM1R6 | QEIHOM1R5 | QEIHOM1R4 | QEIHOM1R3 | QEIHOM1R2 | QEIHOM1R1 | QEIHOM1R0 |

| bit 15    | •         |           |           |           |           | •         | bit 8     |

| R/W-0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| QEINDX1R7 | QEINDX1R6 | QEINDX1R5 | QEINDX1R4 | QEINDX1R3 | QEINDX1R2 | QEINDX1R1 | QEINDX1R0 |

| bit 7     |           |           |           |           |           |           | bit 0     |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **QEIHOM1R<7:0>:** Assign QEI Home 1 Input (S1QEIHOM1) to the Corresponding S1RPn Pin bits See Table 4-27.

### REGISTER 4-48: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| U1DSRR7 | U1DSRR6 | U1DSRR5 | U1DSRR4 | U1DSRR3 | U1DSRR2 | U1DSRR1 | U1DSRR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| U1RXR7 | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **U1DSRR<7:0>:** Assign UART1 Data-Set-Ready (S1U1DSR) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 **U1RXR<7:0>:** Assign UART1 Receive (S1U1RX) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 **QEINDX1R<7:0>:** Assign QEI Index 1 Input (S1QEINDX1) to the Corresponding S1RPn Pin bits See Table 4-27.

### REGISTER 9-27: PGxTRIGA: PWM GENERATOR x TRIGGER A REGISTER

| R/W-0         | R/W-0                              | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

|---------------|------------------------------------|----------------|-------|--------------|------------------|-----------------|-------|

|               |                                    |                | PGxTF | RIGA<15:8>   |                  |                 |       |

| bit 15        |                                    |                |       |              |                  |                 | bit 8 |

| R/W-0         | R/W-0                              | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

|               |                                    |                | PGxT  | RIGA<7:0>    |                  |                 |       |

| bit 7         |                                    |                |       |              |                  |                 | bit 0 |

| Legend:       |                                    |                |       |              |                  |                 |       |

| R = Readabl   | e bit                              | W = Writable b | oit   | U = Unimplem | nented bit, read | d as '0'        |       |

| -n = Value at | -n = Value at POR '1' = Bit is set |                |       |              | ared             | x = Bit is unkn | own   |

bit 15-0 PGxTRIGA<15:0>: PWM Generator x Trigger A Register bits

### REGISTER 9-28: PGxTRIGB: PWM GENERATOR x TRIGGER B REGISTER

| R/W-0         | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|---------------|-------|------------------|-------|-------------------|----------------|-----------------|-------|

|               |       |                  | PGxTI | RIGB<15:8>        |                |                 |       |

| bit 15        |       |                  |       |                   |                |                 | bit 8 |

| R/W-0         | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|               |       |                  | PGxT  | RIGB<7:0>         |                |                 |       |

| bit 7         |       |                  |       |                   |                |                 | bit 0 |

| Legend:       |       |                  |       |                   |                |                 |       |

| R = Readable  | e bit | W = Writable bit |       | U = Unimplem      | ented bit, rea | ıd as '0'       |       |

| -n = Value at | POR   | '1' = Bit is set |       | '0' = Bit is clea | red            | x = Bit is unkn | own   |

bit 15-0 PGxTRIGB<15:0>: PWM Generator x Trigger B Register bits

#### REGISTER 9-29: PGxTRIGC: PWM GENERATOR x TRIGGER C REGISTER

| R/W-0   | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------|--------|----------|-------|-------|-------|

|         |       |       | PGxTRI | GC<15:8> |       |       |       |

| bit 15  |       |       |        |          |       |       | bit 8 |

|         |       |       |        |          |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | PGxTR  | IGC<7:0> |       |       |       |

| bit 7   |       |       |        |          |       |       | bit 0 |

|         |       |       |        |          |       |       |       |

| Legend: |       |       |        |          |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PGxTRIGC<15:0>:** PWM Generator x Trigger C Register bits

|                    | R/W-0                                               | U-0                                                                               | R/W-0                          | U-0                            | U-0             | U-0                | U-0            |

|--------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------|--------------------------------|-----------------|--------------------|----------------|

| R/W-0<br>PWMRSEN   | ASDGM                                               | 0-0                                                                               | SSDG                           | 0-0                            | 0-0             | 0-0                | 0-0            |

|                    | ASDGIVI                                             |                                                                                   | 33DG                           |                                |                 |                    |                |

| bit 15             |                                                     |                                                                                   |                                |                                |                 |                    | bit            |

| R/W-0              | R/W-0                                               | R/W-0                                                                             | R/W-0                          | R/W-0                          | R/W-0           | R/W-0              | R/W-0          |

| ASDG7              | ASDG6                                               | ASDG5                                                                             | ASDG4                          | ASDG3                          | ASDG2           | ASDG1              | ASDG0          |

| bit 7              |                                                     |                                                                                   |                                |                                |                 |                    | bit            |

| Legend:            |                                                     |                                                                                   |                                |                                |                 |                    |                |

| R = Readable       | e bit                                               | W = Writable                                                                      | bit                            | U = Unimplem                   | ented bit, read | d as '0'           |                |

| -n = Value at      | POR                                                 | '1' = Bit is set                                                                  |                                | '0' = Bit is clea              | ared            | x = Bit is unknown |                |

| bit 14             |                                                     | oit must be clea<br>Px Auto-Shutdo                                                |                                | e to resume PW<br>e Enable bit | M activity on c | output pins        |                |

|                    | has ende                                            | ed                                                                                | -                              | beginning of the               |                 |                    | ·              |

|                    |                                                     |                                                                                   |                                | or rollover for sh             | utdown to occ   | ur                 |                |

| bit 13             |                                                     | n event occurs<br><b>ted:</b> Read as 'o                                          | •                              |                                |                 |                    |                |

| bit 15             | •                                                   |                                                                                   |                                |                                |                 |                    |                |

| hit 12             |                                                     |                                                                                   | down/(late (lo                 |                                |                 |                    |                |

| bit 12             | 1 = Manually                                        |                                                                                   | down/Gate Co<br>nutdown, timer | clock gate or                  | input capture   | signal gate ev     | ent (setting o |

| bit 12             | 1 = Manually<br>ASDGM                               | forces auto-sh                                                                    | nutdown, timer                 |                                | input capture   | signal gate ev     | ent (setting o |

| bit 12<br>bit 11-8 | 1 = Manually<br>ASDGM<br>0 = Normal n               | forces auto-sh<br>bit still applies)                                              | nutdown, timei<br>n            |                                | input capture   | signal gate ev     | ent (setting   |

|                    | 1 = Manually<br>ASDGM<br>0 = Normal n<br>Unimplemen | forces auto-sh<br>bit still applies)<br>nodule operatio<br><b>ted:</b> Read as '( | nutdown, timer<br>n            |                                |                 | signal gate ev     | ent (setting   |

## REGISTER 10-3: CCPxCON2L: CCPx CONTROL 2 LOW REGISTERS

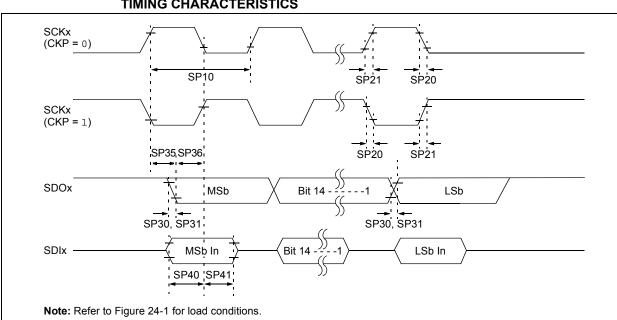

# 14.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI) with Audio Codec Support" (DS70005136) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: The SPI is Identical for both Master core and Slave core. The x is common for both Master and Slave (where the x represents the number of the specific module being addressed). The number of SPI modules available on the Master and Slave is different and they are located in different SFR locations.

- 3: All associated register names are the same on the Master core and the Slave core. The Slave code will be developed in a separate project in MPLAB<sup>®</sup> X IDE with the device selection, dsPIC33CH128MP508S1, where the S1 indicates the Slave device. The Master is SPI1 and SPI2, and the Slave is SPI1.

Table 14-1 shows an overview of the SPI module.

TABLE 14-1: SPI MODULE OVERVIEW

|             | Number of SPI<br>Modules | ldentical<br>(Modules) |

|-------------|--------------------------|------------------------|

| Master Core | 2                        | Yes                    |

| Slave Core  | 1                        | Yes                    |

The Serial Peripheral Interface (SPI) module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the Motorola® SPI and SIOP interfaces. All devices in the dsPIC33CH128MP508 family include three SPI modules: two SPIs for the Master core and one for the Slave core. One of the SPI modules can work up to 50 MHz speed when selected as a non-PPS pin. For the Master core, it will be SPI2 and for the Slave core, it will be SPI1. The selection is done using the SPI2PIN bit (FDEVOPT<13>) for the Master and the S1SPI1PIN bit (FS1DEVOPT<13>) for the Slave. If the bit for SPI2PIN/S1SPI1PIN is '1', the PPS pin will be used. If the SPI2PIN/S1SPI1PIN is '0', it will use the dedicated SPI pads.

The module supports operation in two Buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through a FIFO buffer. The FIFO level depends on the configured mode.

| Note: | FIFO depth for this device is four (in 8-Bit |

|-------|----------------------------------------------|

|       | Data mode).                                  |

Variable length data can be transmitted and received, from 2 to 32 bits.

Note: Do not perform Read-Modify-Write operations (such as bit-oriented instructions) on the SPIxBUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The module also supports Audio modes. Four different Audio modes are available.

- I<sup>2</sup>S mode

- · Left Justified mode

- · Right Justified mode

- PCM/DSP mode

In each of these modes, the serial clock is free-running and audio data is always transferred.

If an audio protocol data transfer takes place between two devices, then usually one device is the Master and the other is the Slave. However, audio data can be transferred between two Slaves. Because the audio protocols require free-running clocks, the Master can be a third-party controller. In either case, the Master generates two free-running clocks: SCKx and LRC (Left, Right Channel Clock/SSx/FSYNC).

The SPI serial interface consists of four pins:

- SDIx/S1SDIx: Serial Data Input

- SDOx/S1SDOx: Serial Data Output

- SCKx/S1SCKx: Shift Clock Input or Output

- SSx/S1SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using two, three or four pins. In the 3-pin mode, SSx/S1SSx is not used. In the 2-pin mode, both SDOx/S1SDOx and SSx/S1SSx are not used.

| bit 7  |        |        |        |         |             |        | bit 0  |

|--------|--------|--------|--------|---------|-------------|--------|--------|

| 1.11.7 |        |        | BSLI   | vi<7:0> |             |        | L:1.0  |

| R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1  | R/PO-1      | R/PO-1 | R/PO-1 |

| bit 15 |        |        |        |         |             |        | bit 8  |

| —      | —      | —      |        |         | BSLIM<12:8> |        |        |

| U-1    | U-1    | U-1    | R/PO-1 | R/PO-1  | R/PO-1      | R/PO-1 | R/PO-1 |

| bit 23 |        |        |        |         |             |        | bit 16 |

| —      | —      | _      | —      | _       | —           | —      | —      |

| U-1    | U-1    | U-1    | U-1    | U-1     | U-1         | U-1    | U-1    |

## REGISTER 21-2: FBSLIM CONFIGURATION REGISTER

| Legend:           | PO = Program Once bit |                                    |                    |  |

|-------------------|-----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 23-13 Unimplemented: Read as '1'

bit 12-0 **BSLIM<12:0>:** Boot Segment Code Flash Page Address Limit bits Contains the page address of the first active General Segment page. The value to be programmed is the inverted page address, such that programming additional '0's can only increase the Boot Segment size.

## **REGISTER 21-3:** FSIGN CONFIGURATION REGISTER

| U-1                               | U-1                        | U-1              | U-1 | U-1                                | U-1 | U-1                | U-1    |  |  |

|-----------------------------------|----------------------------|------------------|-----|------------------------------------|-----|--------------------|--------|--|--|

| _                                 | —                          | —                | —   | —                                  | —   | —                  | —      |  |  |

| bit 23                            |                            |                  |     |                                    |     |                    | bit 16 |  |  |

|                                   |                            |                  |     |                                    |     |                    |        |  |  |

| r-0                               | U-1                        | U-1              | U-1 | U-1                                | U-1 | U-1                | U-1    |  |  |

|                                   | —                          | —                |     | —                                  | —   | —                  | —      |  |  |

| bit 15                            |                            |                  |     |                                    |     |                    | bit 8  |  |  |

|                                   |                            |                  |     |                                    |     |                    |        |  |  |

| U-1                               | U-1                        | U-1              | U-1 | U-1                                | U-1 | U-1                | U-1    |  |  |

| _                                 | —                          | —                | —   | —                                  | —   | —                  | —      |  |  |

| bit 7 bit                         |                            |                  |     |                                    |     |                    |        |  |  |

|                                   |                            |                  |     |                                    |     |                    |        |  |  |

| Legend: r = Reserved bit          |                            |                  | bit | PO = Program Once bit              |     |                    |        |  |  |

| R = Readable bit W = Writable bit |                            |                  | bit | U = Unimplemented bit, read as '0' |     |                    |        |  |  |

| -n = Value at POR '1' = Bit is se |                            | '1' = Bit is set |     | '0' = Bit is cleared               |     | x = Bit is unknown |        |  |  |

|                                   |                            |                  |     |                                    |     |                    |        |  |  |

| bit 23-16                         | Unimplemented: Read as '1' |                  |     |                                    |     |                    |        |  |  |

| bit 15                            | Reserved: Maintain as '0'  |                  |     |                                    |     |                    |        |  |  |

| bit 14-0                          | Unimplemented: Read as '1' |                  |     |                                    |     |                    |        |  |  |

## 21.7 Dual Watchdog Timer (WDT)

- Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Dual Watchdog Timer", (DS70005250) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: The WDT is identical for both Master core and Slave core. The x is common for both Master core and Slave core (where the x represents the number of the specific module being addressed). The number of WDT modules available on the Master and Slaves is different and they are located in different SFR locations.

- 3: All associated register names are the same on the Master core and the Slave core. The Slave code will be developed in a separate project in MPLAB<sup>®</sup> X IDE with the device selection, dsPIC33CH128MP508S1, where the S1 indicates the Slave device.

Table 21-6 shows an overview of the WDT module.

# TABLE 21-6:DUAL WDT MODULEOVERVIEW

|             | Number of<br>WDT Modules | ldentical<br>(Modules) |  |  |  |

|-------------|--------------------------|------------------------|--|--|--|

| Master Core | 1                        | Yes                    |  |  |  |

| Slave Core  | 1                        | Yes                    |  |  |  |

The dsPIC33 dual Watchdog Timer (WDT) is described in this section. Refer to Figure 21-2 for a block diagram of the WDT.

The WDT, when enabled, operates from the internal Low-Power RC (LPRC) Oscillator clock source or a selectable clock source in Run mode. The WDT can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. The WDT can be configured in Windowed mode or Non-Windowed mode. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode (Power Save mode). If the WDT expires and issues a device Reset, the WTDO bit of the RCON register (Register 21-37) will be set.

The following are some of the key features of the WDT modules:

- Configuration or Software Controlled

- Separate User-Configurable Time-out Periods for Run and Sleep/Idle

- Can Wake the Device from Sleep or Idle

- · User-Selectable Clock Source in Run mode

- Operates from LPRC in Sleep/Idle mode

**Note:** While executing a clock switch, the WDT will not be reset. It is recommended to reset the WDT prior to executing a clock switch instruction.