Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 23x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-UQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp502-i-2n |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(1)</sup>                                             | Pin<br>Type                      | Buffer<br>Type   | PPS      | Description                                                                                                                            |

|---------------------------------------------------------------------|----------------------------------|------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| TMS                                                                 | Ι                                | ST               | No       | JTAG Test mode select pin                                                                                                              |

| ТСК                                                                 | I                                | ST               | No       | JTAG test clock input pin                                                                                                              |

| TDI                                                                 | I                                | ST               | No       | JTAG test data input pin                                                                                                               |

| TDO                                                                 | 0                                | —                | No       | JTAG test data output pin                                                                                                              |

| PCI8-PCI18/<br>S1PCI8-S1PCI18                                       | Ι                                | ST               | Yes      | PWM Inputs 8 through 18                                                                                                                |

| PWMEA-PWMED/<br>S1PWMEA-S1PWMED                                     | 0                                | —                | Yes      | PWM Event Outputs A through D                                                                                                          |

| PCI19-PCI22/<br>S1PCI19-S1PCI22 <sup>(3)</sup>                      | Т                                | ST               | No       | PWM Inputs 19 through 22                                                                                                               |

| PWM1L-PWM4L/S1PWM1L/<br>S1PWM8L <sup>(3)</sup>                      | 0                                | —                | No       | PWM Low Outputs 1 through 8                                                                                                            |

| PWM1H-PWM4H/<br>S1PWM1H-S1PWM8H <sup>(2,3)</sup>                    | 0                                | _                |          | PWM High Outputs 1 through 8                                                                                                           |

| CLCINA-CLCIND/<br>S1CLCINA-S1CLCIND <sup>(3)</sup>                  | I                                | ST               | Yes      | CLC Inputs A through D                                                                                                                 |

| CLC1OUT-CLC4OUT                                                     | 0                                | _                | Yes      | CLC Outputs 1 through 4                                                                                                                |

| CMP1                                                                | 0                                |                  | Yes      | Comparator 1 output                                                                                                                    |

| CMP1A/<br>S1CMP1A-S1CMP3A <sup>(3)</sup>                            | I                                | Analog           | No       | Comparator Channels 1A through 3A inputs                                                                                               |

| CMP1B/<br>S1CMP1B-S1CMP3B <sup>(3)</sup>                            | I                                | Analog           | No       | Comparator Channels 1B through 3B inputs                                                                                               |

| CMP1D/<br>S1CMP1D-S1CMP3D <sup>(3)</sup>                            | I                                | Analog           | No       | Comparator Channels 1D through 3D inputs                                                                                               |

| DACOUT                                                              | 0                                | _                | No       | DAC output voltage                                                                                                                     |

| IBIAS3, IBIAS2, IBIAS1,<br>IBIAS0/ISRC3, ISRC2,<br>ISRC1, ISRC0     | 0                                | Analog           | No       | Constant-Current Outputs 0 through 3                                                                                                   |

| S1PGA1P2                                                            | I                                | Analog           | No       | PGA1 Positive Input 2                                                                                                                  |

| S1PGA1N2                                                            | I                                | Analog           | No       | PGA1 Negative Input 2                                                                                                                  |

| S1PGA2P2                                                            | 1                                | Analog           | No       | PGA2 Positive Input 2                                                                                                                  |

| S1PGA2N2                                                            | 1                                | Analog           | No       | PGA2 Negative Input 2                                                                                                                  |

| S1PGA3P1-S1PGA3P2                                                   | 1                                | Analog           | No       | PGA3 Positive Inputs 1 through 2                                                                                                       |

| S1PGA3N2                                                            |                                  | Analog           |          | PGA3 Negative Input 2                                                                                                                  |

| PGD1/S1PGD1 <sup>(3)</sup>                                          | I/O                              | ST               | No       | Data I/O pin for Programming/Debugging Communication Channel 1                                                                         |

| PGC1/S1PGC1 <sup>(3)</sup>                                          | 1                                | ST               | No       | Clock input pin for Programming/Debugging Communication<br>Channel 1                                                                   |

| PGD2/S1PGD2 <sup>(3)</sup>                                          | I/O                              | ST               | No       | Data I/O pin for Programming/Debugging Communication Channel 2                                                                         |

| PGC2/S1PGC2 <sup>(3)</sup>                                          | 1                                | ST               | No       | Clock input pin for Programming/Debugging Communication<br>Channel 2                                                                   |

| PGD3/S1PGD3 <sup>(3)</sup><br>PGC3/S1PGC3 <sup>(3)</sup>            | I/O<br>I                         | ST<br>ST         | No<br>No | Data I/O pin for Programming/Debugging Communication Channel 3<br>Clock input pin for Programming/Debugging Communication<br>Channel 3 |

| Legend: CMOS = CMOS co<br>ST = Schmitt Trigge<br>PPS = Peripheral P | er inpu <sup>.</sup><br>'in Sele | t with CN<br>ect | /IOS le  | put Analog = Analog input P = Power                                                                                                    |

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

2: These pins are remappable as well as dedicated. Some of the pins are associated with the Slave function and have S1 attached to the beginning of the name. For example, AN0 for the Slave is S1AN0.

**3:** S1 attached to the beginning of the name indicates the Slave feature for that function. For example, AN0 for the Slave is S1AN0.

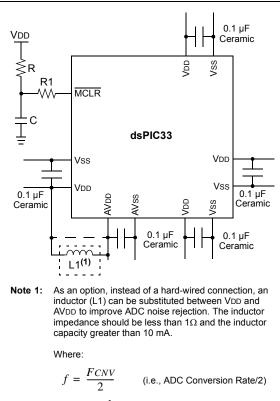

## FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

$$f = \frac{1}{2}$$

(i.e., ADC Conversion Rate.

$$f = \frac{1}{(2\pi\sqrt{LC})}$$

$$L = \left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

## 2.2.1 BULK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a bulk capacitor for integrated circuits, including DSCs, to supply a local power source. The value of the bulk capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the bulk capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

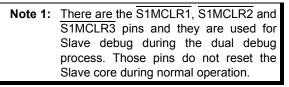

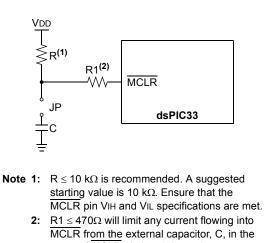

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- · Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components, as shown in Figure 2-2, within one-quarter inch (6 mm) from the MCLR pin.

## FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

ACLR from the external capacitor, C, in the event of MCLR pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

| R/W-0           | R/W-0                                                                                                                                                            | R/W-0                | R/W-0                                     | R/W-0              | R/W-0           | R/W-0          | R/W-0 |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------|--------------------|-----------------|----------------|-------|--|--|--|

| NSTDIS          | OVAERR                                                                                                                                                           | OVBERR               | COVAERR                                   | COVBERR            | OVATE           | OVBTE          | COVTE |  |  |  |

| bit 15          |                                                                                                                                                                  |                      |                                           |                    |                 |                | bit 8 |  |  |  |

|                 |                                                                                                                                                                  |                      |                                           |                    |                 |                |       |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                            | R/W-0                | R/W-0                                     | R/W-0              | R/W-0           | R/W-0          | U-0   |  |  |  |

| SFTACERR        | DIV0ERR                                                                                                                                                          | DMACERR              | MATHERR                                   | ADDRERR            | STKERR          | OSCFAIL        | —     |  |  |  |

| bit 7           |                                                                                                                                                                  |                      |                                           |                    |                 |                | bit 0 |  |  |  |

|                 |                                                                                                                                                                  |                      |                                           |                    |                 |                |       |  |  |  |

| Legend:         | 1.11                                                                                                                                                             |                      | 1.11                                      |                    |                 | (0)            |       |  |  |  |

| R = Readable    |                                                                                                                                                                  | W = Writable         |                                           | -                  | ented bit, read |                |       |  |  |  |

| -n = Value at F | VOR                                                                                                                                                              | '1' = Bit is set     |                                           | '0' = Bit is clea  | ired            | x = Bit is unk | nown  |  |  |  |

| bit 15          | NSTDIS: Inte                                                                                                                                                     | errupt Nesting       | Disable bit                               |                    |                 |                |       |  |  |  |

| 2.1.10          |                                                                                                                                                                  | nesting is disa      |                                           |                    |                 |                |       |  |  |  |

|                 | •                                                                                                                                                                | nesting is ena       |                                           |                    |                 |                |       |  |  |  |

| bit 14          | OVAERR: A                                                                                                                                                        | ccumulator A (       | Overflow Trap F                           | -lag bit           |                 |                |       |  |  |  |

|                 | <ul> <li>1 = Trap was caused by an overflow of Accumulator A</li> <li>0 = Trap was not caused by an overflow of Accumulator A</li> </ul>                         |                      |                                           |                    |                 |                |       |  |  |  |

| h# 40           | -                                                                                                                                                                |                      | -                                         |                    | A               |                |       |  |  |  |

| bit 13          |                                                                                                                                                                  |                      | Overflow Trap I                           | •                  |                 |                |       |  |  |  |

|                 | <ul> <li>1 = Trap was caused by an overflow of Accumulator B</li> <li>0 = Trap was not caused by an overflow of Accumulator B</li> </ul>                         |                      |                                           |                    |                 |                |       |  |  |  |

| bit 12          | -                                                                                                                                                                |                      | -                                         | Overflow Trap F    |                 |                |       |  |  |  |

|                 |                                                                                                                                                                  |                      | •                                         | erflow of Accum    | •               |                |       |  |  |  |

|                 |                                                                                                                                                                  |                      |                                           | c overflow of Ac   |                 |                |       |  |  |  |

| bit 11          |                                                                                                                                                                  |                      | tor B Catastrophic Overflow Trap Flag bit |                    |                 |                |       |  |  |  |

|                 | <ul> <li>1 = Trap was caused by a catastrophic overflow of Accumulator B</li> <li>0 = Trap was not caused by a catastrophic overflow of Accumulator B</li> </ul> |                      |                                           |                    |                 |                |       |  |  |  |

| bit 10          | -                                                                                                                                                                |                      |                                           |                    | cumulator B     |                |       |  |  |  |

| bit 10          | OVATE: Accumulator A Overflow Trap Enable bit                                                                                                                    |                      |                                           |                    |                 |                |       |  |  |  |

|                 | 1 = Trap overflow of Accumulator A<br>0 = Trap is disabled                                                                                                       |                      |                                           |                    |                 |                |       |  |  |  |

| bit 9           | OVBTE: Acc                                                                                                                                                       | cumulator B O        | verflow Trap En                           | able bit           |                 |                |       |  |  |  |

|                 | 1 = Trap ove                                                                                                                                                     | erflow of Accun      | nulator B                                 |                    |                 |                |       |  |  |  |

|                 |                                                                                                                                                                  | 0 = Trap is disabled |                                           |                    |                 |                |       |  |  |  |

| bit 8           |                                                                                                                                                                  |                      | flow Trap Enal                            |                    |                 |                |       |  |  |  |

|                 |                                                                                                                                                                  |                      | low of Accumu                             | lator A or B is ei | nabled          |                |       |  |  |  |

| bit 7           | 0 = Trap is d                                                                                                                                                    |                      | lator Error Stat                          | us hit             |                 |                |       |  |  |  |

|                 |                                                                                                                                                                  |                      |                                           | alid accumulator   | shift           |                |       |  |  |  |

|                 |                                                                                                                                                                  |                      | •                                         | invalid accumul    |                 |                |       |  |  |  |

|                 |                                                                                                                                                                  | -                    | -                                         |                    |                 |                |       |  |  |  |

# REGISTER 3-18: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0                             | R/W-0   | R/W-0            | R/W-0   | R/W-0                                   | R/W-0   | R/W-0   | R/W-0   |

|-----------------------------------|---------|------------------|---------|-----------------------------------------|---------|---------|---------|

| U2CTSR7                           | U2CTSR6 | U2CTSR5          | U2CTSR4 | U2CTSR3                                 | U2CTSR2 | U2CTSR1 | U2CTSR0 |

| bit 15                            |         |                  |         |                                         |         |         | bit 8   |

|                                   |         |                  |         |                                         |         |         |         |

| U-0                               | U-0     | U-0              | U-0     | U-0                                     | U-0     | U-0     | U-0     |

| —                                 | —       | —                | —       | —                                       | —       | —       | —       |

| bit 7                             |         |                  |         |                                         |         |         | bit 0   |

|                                   |         |                  |         |                                         |         |         |         |

| Legend:                           |         |                  |         |                                         |         |         |         |

| R = Readable bit W = Writable bit |         |                  | bit     | U = Unimplemented bit, read as '0'      |         |         |         |

| -n = Value at P                   | OR      | '1' = Bit is set |         | '0' = Bit is cleared x = Bit is unknown |         |         | nown    |

# REGISTER 3-59: RPINR30: PERIPHERAL PIN SELECT INPUT REGISTER 30

bit 15-8 **U2CTSR<7:0>:** Assign UART2 Clear-to-Send (U2CTS) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 3-60: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37

| R/W-0                             | R/W-0   | R/W-0   | R/W-0                | R/W-0                              | R/W-0              | R/W-0   | R/W-0   |

|-----------------------------------|---------|---------|----------------------|------------------------------------|--------------------|---------|---------|

| PCI17R7                           | PCI17R6 | PCI17R5 | PCI17R4              | PCI17R3                            | PCI17R2            | PCI17R1 | PCI17R0 |

| bit 15                            |         | •       |                      |                                    |                    |         | bit 8   |

|                                   |         |         |                      |                                    |                    |         |         |

| U-0                               | U-0     | U-0     | U-0                  | U-0                                | U-0                | U-0     | U-0     |

| —                                 | —       | —       | —                    | —                                  | —                  | —       | —       |

| bit 7                             |         |         |                      |                                    |                    |         | bit 0   |

|                                   |         |         |                      |                                    |                    |         |         |

| Legend:                           |         |         |                      |                                    |                    |         |         |

| R = Readable bit W = Writable bit |         |         | bit                  | U = Unimplemented bit, read as '0' |                    |         |         |

| n = Value at POR '1' = Bit is set |         |         | '0' = Bit is cleared |                                    | x = Bit is unknown |         |         |

bit 15-8 **PCI17R<7:0>:** Assign PWM Input 17 (PCI17) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 Unimplemented: Read as '0'

| R/W-0                                            | R/W-0                                                                              | R/W-0                                                                                                                   | R/W-0           | R/W-0            | R/W-0           | U-0             | U-0   |  |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|--|--|--|

| IVMIE                                            | WAKIE                                                                              | CERRIE                                                                                                                  | SERRIE          | RXOVIE           | TXATIE          | _               | _     |  |  |  |

| bit 15                                           |                                                                                    |                                                                                                                         |                 |                  |                 |                 | bit 8 |  |  |  |

|                                                  |                                                                                    |                                                                                                                         |                 |                  |                 |                 |       |  |  |  |

| U-0                                              | U-0                                                                                | U-0                                                                                                                     | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |  |

| —                                                | _                                                                                  | —                                                                                                                       | TEFIE           | MODIE            | TBCIE           | RXIE            | TXIE  |  |  |  |

| bit 7                                            |                                                                                    |                                                                                                                         |                 |                  |                 |                 | bit 0 |  |  |  |

|                                                  |                                                                                    |                                                                                                                         |                 |                  |                 |                 |       |  |  |  |

| Legend:                                          |                                                                                    |                                                                                                                         |                 |                  |                 |                 |       |  |  |  |

| R = Readable                                     |                                                                                    | W = Writable b                                                                                                          | oit             |                  | mented bit, rea | d as '0'        |       |  |  |  |

| -n = Value at                                    | POR                                                                                | '1' = Bit is set                                                                                                        |                 | '0' = Bit is cle | ared            | x = Bit is unkn | iown  |  |  |  |

|                                                  |                                                                                    |                                                                                                                         |                 | .,               |                 |                 |       |  |  |  |

| bit 15                                           |                                                                                    | d Message Inter                                                                                                         | -               | It               |                 |                 |       |  |  |  |

|                                                  |                                                                                    | essage interrupt<br>essage interrupt                                                                                    |                 |                  |                 |                 |       |  |  |  |

| bit 14                                           |                                                                                    | Wake-up Activit                                                                                                         |                 | able bit         |                 |                 |       |  |  |  |

|                                                  |                                                                                    | activity interrup                                                                                                       |                 |                  |                 |                 |       |  |  |  |

|                                                  |                                                                                    | Activity Interrup                                                                                                       |                 |                  |                 |                 |       |  |  |  |

| it 13 CERRIE: CAN Bus Error Interrupt Enable bit |                                                                                    |                                                                                                                         |                 |                  |                 |                 |       |  |  |  |

|                                                  |                                                                                    | error interrupt is                                                                                                      |                 |                  |                 |                 |       |  |  |  |

| L:1 40                                           |                                                                                    | error interrupt is                                                                                                      |                 |                  |                 |                 |       |  |  |  |

| bit 12                                           | -                                                                                  | stem Error Interr                                                                                                       | -               |                  |                 |                 |       |  |  |  |

|                                                  |                                                                                    | error interrupt is                                                                                                      |                 |                  |                 |                 |       |  |  |  |

| bit 11                                           | -                                                                                  | ceive Buffer Ove                                                                                                        |                 | t Enable bit     |                 |                 |       |  |  |  |

|                                                  | 1 = Receive                                                                        | buffer overflow i                                                                                                       | nterrupt is ena | abled            |                 |                 |       |  |  |  |

|                                                  |                                                                                    | buffer overflow i                                                                                                       | •               |                  |                 |                 |       |  |  |  |

| bit 10                                           |                                                                                    | nsmit Attempt In                                                                                                        | •               | e bit            |                 |                 |       |  |  |  |

|                                                  |                                                                                    | attempt interrup<br>attempt interrup                                                                                    |                 |                  |                 |                 |       |  |  |  |

| bit 9-5                                          |                                                                                    | nted: Read as '0                                                                                                        |                 |                  |                 |                 |       |  |  |  |

| bit 4                                            | •                                                                                  | smit Event FIFO                                                                                                         |                 | hle hit          |                 |                 |       |  |  |  |

|                                                  |                                                                                    |                                                                                                                         |                 |                  |                 |                 |       |  |  |  |

|                                                  |                                                                                    | <ul> <li>1 = Transmit event FIFO interrupt is enabled</li> <li>0 = Transmit event FIFO interrupt is disabled</li> </ul> |                 |                  |                 |                 |       |  |  |  |

| bit 3                                            | MODIE: Mod                                                                         | le Change Interr                                                                                                        | upt Enable bit  |                  |                 |                 |       |  |  |  |

|                                                  |                                                                                    | ange interrupt is                                                                                                       |                 |                  |                 |                 |       |  |  |  |

|                                                  |                                                                                    | 0 = Mode change interrupt is disabled                                                                                   |                 |                  |                 |                 |       |  |  |  |

| bit 2                                            | <b>TBCIE:</b> CAN Timer Interrupt Enable bit<br>1 = CAN timer interrupt is enabled |                                                                                                                         |                 |                  |                 |                 |       |  |  |  |

|                                                  |                                                                                    | er interrupt is en<br>er interrupt is dis                                                                               |                 |                  |                 |                 |       |  |  |  |

| bit 1                                            |                                                                                    | ve Object Interru                                                                                                       |                 |                  |                 |                 |       |  |  |  |

|                                                  |                                                                                    | object interrupt i                                                                                                      |                 |                  |                 |                 |       |  |  |  |

|                                                  | 0 = Receive                                                                        | object interrupt i                                                                                                      | s disabled      |                  |                 |                 |       |  |  |  |

| bit 0                                            | TXIE: Transn                                                                       | nit Object Interru                                                                                                      | ipt Enable bit  |                  |                 |                 |       |  |  |  |

|                                                  |                                                                                    | object interrupt                                                                                                        |                 |                  |                 |                 |       |  |  |  |

|                                                  | 0 = Transmit                                                                       | object interrupt                                                                                                        | is disabled     |                  |                 |                 |       |  |  |  |

## REGISTER 3-116: C1INTH: CAN INTERRUPT REGISTER HIGH

## **REGISTER 3-122:** C1TXIFH: CAN TRANSMIT INTERRUPT STATUS REGISTER HIGH<sup>(1)</sup>

| R-0                                                                        | R-0 | R-0              | R-0   | R-0           | R-0           | R-0       | R-0   |

|----------------------------------------------------------------------------|-----|------------------|-------|---------------|---------------|-----------|-------|

|                                                                            |     |                  | TFIF< | :31:24>       |               |           |       |

| bit 15                                                                     |     |                  |       |               |               |           | bit 8 |

|                                                                            |     |                  |       |               |               |           |       |

| R-0                                                                        | R-0 | R-0              | R-0   | R-0           | R-0           | R-0       | R-0   |

|                                                                            |     |                  | TFIF< | 23:16>        |               |           |       |

| bit 7                                                                      |     |                  |       |               |               |           | bit 0 |

|                                                                            |     |                  |       |               |               |           |       |

| Legend:                                                                    |     |                  |       |               |               |           |       |

| R = Readable b                                                             | oit | W = Writable bit |       | U = Unimpleme | ented bit, re | ad as 'O' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |                  |       |               |               | nown      |       |

#### bit 15-0 TFIF<31:16>: Unimplemented

Note 1: C1TXIFH: FIFO: TFIFx = 'or' of the enabled TX FIFO flags (flags need to be cleared in the FIFO register).

### **REGISTER 3-123:** C1TXIFL: CAN TRANSMIT INTERRUPT STATUS REGISTER LOW<sup>(1)</sup>

| R-0             | R-0                           | R-0              | R-0   | R-0                                | R-0  | R-0             | R-0   |  |

|-----------------|-------------------------------|------------------|-------|------------------------------------|------|-----------------|-------|--|

|                 |                               |                  | TFIF∙ | <15:8>                             |      |                 |       |  |

| bit 15          |                               |                  |       |                                    |      |                 | bit 8 |  |

| R-0             | R-0                           | R-0              | R-0   | R-0                                | R-0  | R-0             | R-0   |  |

|                 |                               |                  | TFIF< | :7:0> <sup>(2)</sup>               |      |                 |       |  |

| bit 7           |                               |                  |       |                                    |      |                 | bit 0 |  |

| Legend:         |                               |                  |       |                                    |      |                 |       |  |

| R = Readable b  | Readable bit W = Writable bit |                  |       | U = Unimplemented bit, read as '0' |      |                 |       |  |

| -n = Value at P | OR                            | '1' = Bit is set |       | '0' = Bit is cle                   | ared | x = Bit is unki | nown  |  |

bit 15-8 **TFIF<15:8>:** Unimplemented

bit 7-0 **TFIF<7:0>:** Transmit FIFO/TXQ Interrupt Pending bits<sup>(2)</sup>

1 = One or more enabled transmit FIFO/TXQ interrupts are pending

0 = No enabled transmit FIFO/TXQ interrupts are pending

Note 1: C1TXIFL: FIFO: TFIFx = 'or' of the enabled TX FIFO flags (flags need to be cleared in the FIFO register).

2: TFIF0 is for the transmit queue.

# REGISTER 3-151: C1FLTCONxH: CAN FILTER CONTROL REGISTER x HIGH (x = 0 TO 3;

| R/W-0           |                                                     |                                                         |                    |                   |                  |                 |                |  |

|-----------------|-----------------------------------------------------|---------------------------------------------------------|--------------------|-------------------|------------------|-----------------|----------------|--|

|                 | U-0                                                 | U-0                                                     | R/W-0              | R/W-0             | R/W-0            | R/W-0           | R/W-0          |  |

| FLTENd          |                                                     | —     —     FdBP4     FdBP3     FdBP2     FdBP1         |                    |                   |                  |                 |                |  |

| bit 15          |                                                     |                                                         |                    |                   |                  |                 | bit 8          |  |

| <b>D</b> 444 A  |                                                     |                                                         | <b>D</b> 444 0     | D M M A           | <b>D</b> 444 0   | <b>D</b> 444 0  |                |  |

| R/W-0<br>FLTENc | U-0                                                 | U-0                                                     | R/W-0<br>FcBP4     | R/W-0             | R/W-0            | R/W-0           | R/W-0<br>FcBP0 |  |

| bit 7           | —                                                   | —                                                       | ГСБР4              | FcBP3             | FcBP2            | FcBP1           | bit 0          |  |

|                 |                                                     |                                                         |                    |                   |                  |                 |                |  |

| Legend:         |                                                     |                                                         |                    |                   |                  |                 |                |  |

| R = Readable    | e bit                                               | W = Writable                                            | bit                | U = Unimplen      | nented bit, read | l as '0'        |                |  |

| -n = Value at   | POR                                                 | '1' = Bit is set                                        |                    | '0' = Bit is clea | ared             | x = Bit is unkr | nown           |  |

| bit 15          | <b>FLTENd:</b> Er<br>1 = Filter is<br>0 = Filter is |                                                         | Accept Messag      | ges bit           |                  |                 |                |  |

| bit 14-13       | Unimpleme                                           | nted: Read as '                                         | 0'                 |                   |                  |                 |                |  |

| bit 12-8        | FdBP<4:0>                                           | : Pointer to Obje                                       | ect When Filter    | d Hits bits       |                  |                 |                |  |

|                 | 00111 = Me<br>00110 = Me                            | L000 = Reserve<br>essage matching<br>essage matching    | filter is stored   |                   |                  |                 |                |  |

|                 | 00001 = Me                                          | essage matching<br>essage matching<br>eserved; Object ( | filter is stored   | in Object 1       | ceive message    | es              |                |  |

| bit 7           |                                                     | hable Filter c to /                                     |                    |                   | C                |                 |                |  |

|                 | 1 = Filter is<br>0 = Filter is                      |                                                         |                    |                   |                  |                 |                |  |

| bit 6-5         | Unimpleme                                           | ented: Read as '                                        | 0'                 |                   |                  |                 |                |  |

| bit 4-0         |                                                     | : Pointer to Obje                                       |                    | c Hits bits       |                  |                 |                |  |

|                 | 00111 = M                                           | L000 = Reserve<br>essage matchin<br>essage matching     | g filter is stored |                   |                  |                 |                |  |

|                 | 00001 <b>= M</b> e                                  | essage matching<br>essage matching<br>eserved; Object ( | filter is stored   | in Object 1       | ceive message    | es              |                |  |

# 4.1.6 CPU RESOURCES

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 4.1.6.1 Key Resources

- "dsPIC33E Enhanced CPU" (DS70005158) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ICM3R7  | ICM3R6  | ICM3R5  | ICM3R4  | ICM3R3  | ICM3R2  | ICM3R1  | ICM3R0  |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| R/W-0   |

| TCKI3R7 | TCKI3R6 | TCKI3R5 | TCKI3R4 | TCKI3R3 | TCKI3R2 | TCKI3R1 | TCKI3R0 |

| bit 7   |         |         |         | •       |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Lonondi |         |         |         |         |         |         |         |

#### REGISTER 4-41: RPINR5: PERIPHERAL PIN SELECT INPUT REGISTER 5

| Legena:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

bit 15-8 ICM3R<7:0>: Assign SCCP Capture 3 (S1ICM3) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 **TCKI3R<7:0>:** Assign SCCP Timer3 (S1TCKI3) to the Corresponding S1RPn Pin bits See Table 4-27.

## REGISTER 4-42: RPINR6: PERIPHERAL PIN SELECT INPUT REGISTER 6

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ICM4R7 | ICM4R6 | ICM4R5 | ICM4R4 | ICM4R3 | ICM4R2 | ICM4R1 | ICM4R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TCKI4R7 | TCKI4R6 | TCKI4R5 | TCKI4R4 | TCKI4R3 | TCKI4R2 | TCKI4R1 | TCKI4R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 ICM4R<7:0>: Assign SCCP Capture 4 (S1ICM4) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 **TCKI4R<7:0>:** Assign SCCP Timer4 (S1TCKI4) to the Corresponding S1RPn Pin bits See Table 4-27.

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI15R7 | PCI15R6 | PCI15R5 | PCI15R4 | PCI15R3 | PCI15R2 | PCI15R1 | PCI15R0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

#### REGISTER 4-55: RPINR43: PERIPHERAL PIN SELECT INPUT REGISTER 43

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI14R7 | PCI14R6 | PCI14R5 | PCI14R4 | PCI14R3 | PCI14R2 | PCI14R1 | PCI14R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **PCI15R<7:0>:** Assign PWM Input 15 (S1PCI15) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 PCI14R<7:0>: Assign PWM Input 14 (S1PCI14) to the Corresponding S1RPn Pin bits See Table 4-27.

## REGISTER 4-56: RPINR44: PERIPHERAL PIN SELECT INPUT REGISTER 44

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI16R7 | PCI16R6 | PCI16R5 | PCI16R4 | PCI16R3 | PCI16R2 | PCI16R1 | PCI16R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **PCI16<7:0>:** Assign PWM Input 16 (S1PCI16) to the Corresponding S1RPn Pin bits See Table 4-27.

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------|--------|

| —       | —   | RP49R5 | RP49R4 | RP49R3 | RP49R2 | RP49R1 | RP49R0 |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP48R5 | RP48R4 | RP48R3 | RP48R2 | RP48R1 | RP48R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Logondu |     |        |        |        |        |        |        |

#### REGISTER 4-68: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP49R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP49 Output Pin bits (see Table 4-31 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | <b>RP48R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to S1RP48 Output Pin bits (see Table 4-31 for peripheral function numbers) |

#### REGISTER 4-69: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------|--------|

|         | _   | RP51R5 | RP51R4 | RP51R3 | RP51R2 | RP51R1 | RP51R0 |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP50R5 | RP50R4 | RP50R3 | RP50R2 | RP50R1 | RP50R0 |

| bit 7   |     |        |        | •      |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

| -ogonai           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP51R<5:0>:** Peripheral Output Function is Assigned to S1RP51 Output Pin bits (see Table 4-31 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP50R<5:0>:** Peripheral Output Function is Assigned to S1RP50 Output Pin bits (see Table 4-31 for peripheral function numbers)

#### 4.8.3 PGA CONTROL REGISTERS

## REGISTER 4-112: PGAxCON: PGAx CONTROL REGISTER

| R/W-0         | R/W-0                                              | R/W-0                                                                                                                  | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

|---------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| PGAEN         | PGAOEN                                             | SELPI2                                                                                                                 | SELPI1         | SELPI0           | SELNI2           | SELNI1          | SELNI0  |  |  |  |  |  |

| bit 15        |                                                    |                                                                                                                        |                | ·                |                  |                 | bit 8   |  |  |  |  |  |

|               |                                                    |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

| U-0           | U-0                                                | U-0                                                                                                                    | R/W-0          | U-0              | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

| —             | —                                                  |                                                                                                                        | HIGAIN         |                  | GAIN2            | GAIN1           | GAIN0   |  |  |  |  |  |

| bit 7         |                                                    |                                                                                                                        |                |                  |                  |                 | bit 0   |  |  |  |  |  |

|               |                                                    |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

| Legend:       |                                                    |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

| R = Readable  |                                                    | W = Writable                                                                                                           |                | -                | mented bit, read |                 |         |  |  |  |  |  |

| -n = Value at | POR                                                | '1' = Bit is set                                                                                                       |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

|               |                                                    |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

| bit 15        | PGAEN: PGA                                         |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               |                                                    | dule is enabled                                                                                                        |                | wor oonoumnti    |                  |                 |         |  |  |  |  |  |

| bit 14        |                                                    | GAX Output En                                                                                                          | -              | wer consumpti    | on)              |                 |         |  |  |  |  |  |

| DIL 14        |                                                    | •                                                                                                                      |                |                  |                  |                 |         |  |  |  |  |  |

|               |                                                    | <ol> <li>PGAx output is connected to the DACOUT pin</li> <li>PGAx output is not connected to the DACOUT pin</li> </ol> |                |                  |                  |                 |         |  |  |  |  |  |

| bit 13-11     |                                                    |                                                                                                                        |                | •                |                  |                 |         |  |  |  |  |  |

|               |                                                    | SELPI<2:0>: PGAx Positive Input Selection bits 111 = Reserved                                                          |                |                  |                  |                 |         |  |  |  |  |  |

|               | 110 = Reserved                                     |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 101 = Reserved                                     |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               |                                                    | 100 = Reserved                                                                                                         |                |                  |                  |                 |         |  |  |  |  |  |

|               | 011 = Ground<br>010 = Ground                       |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 001 = S1PGA                                        | 010 = S10GAxP2                                                                                                         |                |                  |                  |                 |         |  |  |  |  |  |

|               | 000 <b>= S1PGA</b>                                 | AxP1                                                                                                                   |                |                  |                  |                 |         |  |  |  |  |  |

| bit 10-8      |                                                    | PGAx Negativ                                                                                                           | e Input Select | tion bits        |                  |                 |         |  |  |  |  |  |

|               | 111 = Reserved                                     |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 110 = Reserved<br>101 = Reserved                   |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 101 = Reserved                                     |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 011 = Ground (Single-Ended mode)                   |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 010 = Reserved                                     |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 001 = S1PGAxN2<br>000 = Ground (Single-Ended mode) |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

| bit 7-5       |                                                    | ted: Read as '                                                                                                         | -              |                  |                  |                 |         |  |  |  |  |  |

| bit 4         | •                                                  | -Gain Select b                                                                                                         |                |                  |                  |                 |         |  |  |  |  |  |

|               | •                                                  |                                                                                                                        |                | crease in gain   | as specified by  | the GAIN<2:0    | > bits. |  |  |  |  |  |

| bit 3         |                                                    | ted: Read as '                                                                                                         |                | gant             |                  |                 | 2.101   |  |  |  |  |  |

| bit 2-0       | •                                                  |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

| 5112 0        | GAIN<2:0>: PGAx Gain Selection bits 111 = Reserved |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 110 = Reserved                                     |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 101 = Gain of 32x                                  |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 100 = Gain of                                      |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 011 = Gain of<br>010 = Gain of                     |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               |                                                    |                                                                                                                        |                |                  |                  |                 |         |  |  |  |  |  |

|               | 001 = Reserv                                       | red                                                                                                                    |                |                  |                  |                 |         |  |  |  |  |  |

| R/W-0         | U-0                                                            | U-0                                     | U-0   | R/W-0             | R/W-0            | R/W-0                  | R/W-0         |  |  |  |

|---------------|----------------------------------------------------------------|-----------------------------------------|-------|-------------------|------------------|------------------------|---------------|--|--|--|

| CANCLKEN      |                                                                | —                                       | _     |                   | CANCLKS          | EL<3:0> <sup>(1)</sup> |               |  |  |  |

| bit 15        |                                                                |                                         |       |                   |                  |                        | bit 8         |  |  |  |