Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit Dual-Core                                                                 |

| Speed                      | 180MHz, 200MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 88KB (88K x 8)                                                                   |

| Program Memory Type        | FLASH, PRAM                                                                      |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 20K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 23x12b; D/A 4x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp502t-i-2n |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

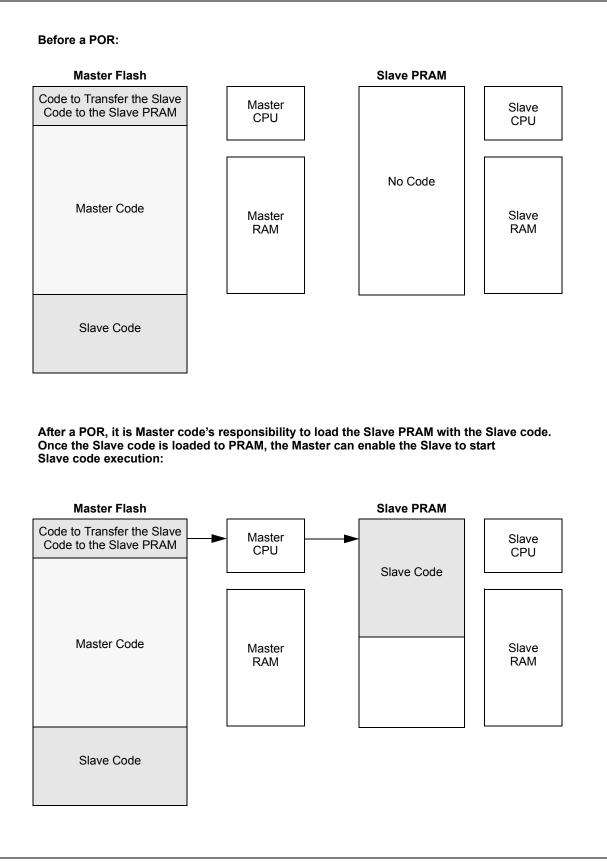

## FIGURE 1-1: SLAVE CORE CODE TRANSFER BLOCK DIAGRAM

### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled                                                                   |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                                                                                                 |

|         | 101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)                                                 |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                                                                                                 |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                                                                                                 |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                                                                                  |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                                                                                  |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                   |

|         | 1 = REPEAT loop is in progress                                                                                                               |

|         | 0 = REPEAT loop is not in progress                                                                                                           |

| bit 3   | N: MCU ALU Negative bit                                                                                                                      |

|         | 1 = Result was negative                                                                                                                      |

|         | 0 = Result was non-negative (zero or positive)                                                                                               |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                     |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state. |

|         | 1 = Overflow occurred for signed arithmetic (in this arithmetic operation)                                                                   |

|         | 0 = No overflow occurred                                                                                                                     |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                          |

|         | 1 = An operation that affects the Z bit has set it at some time in the past                                                                  |

|         | 0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)                                                |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                  |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                         |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                        |

| Note 1  | The IPI <2:0> hits are concatenated with the IPI <3> hit (CORCON<3>) to form the CPI I Interrupt Priority                                    |

- Note 1: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

| IADLE 3-0 | <b>.</b> . | ASIEK SFK DL                            |           |         |                                         |            | -       |                                         |

|-----------|------------|-----------------------------------------|-----------|---------|-----------------------------------------|------------|---------|-----------------------------------------|

| Register  | Address    | All Resets                              | Register  | Address | All Resets                              | Register   | Address | All Resets                              |

| Timers    |            |                                         | INT1TMRH  | 15E     | 00000000000000000                       | MSI1MBX3D  | 1E0     | 000000000000000000                      |

| T1CON     | 100        | 0-000000-00-00-                         | INT1HLDL  | 160     | 00000000000000000                       | MSI1MBX4D  | 1E2     | 000000000000000000                      |

| TMR1      | 104        | 000000000000000000000000000000000000000 | INT1HLDH  | 162     | 000000000000000000                      | MSI1MBX5D  | 1E4     | 000000000000000000                      |

| PR1       | 108        | 000000000000000000000000000000000000000 | INDX1CNTL | 164     | 000000000000000000                      | MSI1MBX6D  | 1E6     | 000000000000000000                      |

| QEI       |            |                                         | INDX1CNTH | 166     | 000000000000000000                      | MSI1MBX7D  | 1E8     | 000000000000000000                      |

| QEI1CON   | 140        | 000000000000000000000000000000000000000 | INDX1HLDL | 168     | 000000000000000000                      | MSI1MBX8D  | 1EA     | 000000000000000000                      |

| QEI1IOCL  | 144        | 000000000000xxxx                        | INDX1HLDH | 16A     | 000000000000000000                      | MSI1MBX9D  | 1EC     | 000000000000000000                      |

| QEI1IOCH  | 146        | 0                                       | QEI1GECL  | 16C     | 000000000000000000                      | MSI1MBX10D | 1EE     | 000000000000000000                      |

| QEI1STAT  | 148        | 000000000000000                         | QEI1GECH  | 16E     | 00000000000000000                       | MSI1MBX11D | 1F0     | 000000000000000000                      |

| POS1CNTL  | 14C        | 000000000000000000                      | QEI1LECL  | 170     | 00000000000000000                       | MSI1MBX12D | 1F2     | 000000000000000000                      |

| POS1CNTH  | 14E        | 000000000000000000000000000000000000000 | QEI1LECH  | 172     | 000000000000000000                      | MSI1MBX13D | 1F4     | 000000000000000000                      |

| POS1HLDL  | 150        | 000000000000000000000000000000000000000 | MSI1CON   | 1D2     | 0xx0000000000                           | MSI1MBX14D | 1F6     | 000000000000000000000000000000000000000 |

| POS1HLDH  | 152        | 000000000000000000000000000000000000000 | MSI1STAT  | 1D4     | 000000000000000000000000000000000000000 | MSI1MBX15D | 1F8     | 000000000000000000000000000000000000000 |

| VEL1CNTL  | 154        | 000000000000000000000000000000000000000 | MSI1KEY   | 1D6     | 00000000                                | MSI1FIFOCS | 1FA     | 0000000000                              |

| VEL1CNTH  | 156        | 000000000000000000000000000000000000000 | MSI1MBXS  | 1D8     | 00000000                                | MRSWFDATA  | 1FC     | 000000000000000000000000000000000000000 |

| VEL1HLDL  | 158        | 000000000000000000                      | MSI1MBX0D | 1DA     | 000000000000000000                      | MWSRFDATA  | 1FE     | 000000000000000000                      |

| VEL1HLDH  | 15A        | 000000000000000000                      | MSI1MBX1D | 1DC     | 000000000000000000                      |            |         |                                         |

| INT1TMRL  | 15C        | 000000000000000000                      | MSI1MBX2D | 1DE     | 000000000000000000                      |            |         |                                         |

TABLE 3-5: MASTER SFR BLOCK 100h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address and Reset values are in hexadecimal and binary, respectively.

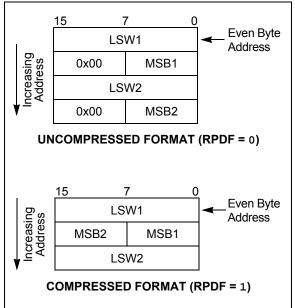

Row programming is performed by first loading 128 instructions into data RAM and then loading the address of the first instruction in that row into the NVMSRCADRL/H registers. Once the write has been initiated, the device will automatically load two instructions into the write latches and write them to the program space destination address defined by the NVMADR/U registers.

The operation will increment the NVMSRCADRL/H and the NVMADR/U registers until all double instruction words have been programmed.

The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 3-15 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

All erase and program operations may optionally use the NVM interrupt to signal the successful completion of the operation.

## 3.3.3 ERROR CORRECTING CODE (ECC)

In order to improve program memory performance and durability, the devices include Error Correcting Code functionality (ECC) as an integral part of the Flash memory controller. ECC can determine the presence of single bit errors in program data, including which bit is in error, and correct the data automatically without user intervention. ECC cannot be disabled.

When data is written to program memory, ECC generates a 7-bit Hamming code parity value for every two (24-bit) instruction words. The data is stored in blocks of 48 data bits and 7 parity bits; parity data is not memorymapped and is inaccessible. When the data is read back, the ECC calculates the parity on it and compares it to the previously stored parity value. If a parity mismatch occurs, there are two possible outcomes:

- Single bit error has occurred and has been automatically corrected on readback.

- Double-bit error has occurred and the read data is not changed.

Single bit error occurrence can be identified by the state of the ECCSBEIF (IFS0<13>) bit. An interrupt can be generated when the corresponding interrupt enable bit is set, ECCSBEIE (IEC0<13>). The ECCSTATL register contains the parity information for single bit errors. The SECOUT<7:0> bit field contains the expected calculated SEC parity and SECIN<7:0> bits contain the actual value from a Flash read operation. The SECSYNDx bits (ECCSTATH<7:0>) indicate the bit position of the single bit error within the 48-bit pair of instruction words. When no error is present, SECINx equals SECOUTx and SECSYNDx is zero.

Double-bit errors result in a generic hard trap. The ECCDBE bit (INTCON4<1>) will be set to identify the source of the hard trap. If no Interrupt Service Routine is implemented for the hard trap, a device Reset will also occur. The ECCSTATH register contains double-bit error status information. The DEDOUT bit is the expected calculated DED parity and DEDIN is the actual value from a Flash read operation. When no error is present, DEDIN equals DEDOUT.

| Input Name <sup>(1)</sup>    | Function Name | Register | Register Bits |

|------------------------------|---------------|----------|---------------|

| CAN1 Input                   | CAN1RX        | RPINR26  | CAN1RXR<7:0>  |

| UART2 Clear-to-Send          | U2CTS         | RPINR30  | U2CTSR<7:0>   |

| PWM Input 17                 | PCI17         | RPINR37  | PCI17R<7:0>   |

| PWM Input 18                 | PCI18         | RPINR38  | PCI18R<7:0>   |

| PWM Input 12                 | PCI12         | RPINR42  | PCI12R<7:0>   |

| PWM Input 13                 | PCI13         | RPINR42  | PCI13R<7:0>   |

| PWM Input 14                 | PCI14         | RPINR43  | PCI14R<7:0>   |

| PWM Input 15                 | PCI15         | RPINR43  | PCI15R<7:0>   |

| PWM Input 16                 | PCI16         | RPINR44  | PCI16R<7:0>   |

| SENT1 Input                  | SENT1         | RPINR44  | SENT1R<7:0>   |

| SENT2 Input                  | SENT2         | RPINR45  | SENT2R<7:0>   |

| CLC Input A                  | CLCINA        | RPINR45  | CLCINAR<7:0>  |

| CLC Input B                  | CLCINB        | RPINR46  | CLCINBR<7:0>  |

| CLC Input C                  | CLCINC        | RPINR46  | CLCINCR<7:0>  |

| CLC Input D                  | CLCIND        | RPINR47  | CLCINDR<7:0>  |

| ADC Trigger Input (ADTRIG31) | ADCTRG        | RPINR47  | ADCTRGR<7:0>  |

## TABLE 3-31: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION) (CONTINUED)

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

| U-0          | U-0                 | U-0                                                                                                                                                             | R-0         | R-0              | R-0              | R-0             | R-0   |  |  |  |  |

|--------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|------------------|-----------------|-------|--|--|--|--|

| _            | _                   | —                                                                                                                                                               |             |                  | FILHIT<4:0>      |                 |       |  |  |  |  |

| bit 15       |                     |                                                                                                                                                                 |             |                  |                  |                 | bit 8 |  |  |  |  |

|              |                     |                                                                                                                                                                 |             |                  |                  |                 |       |  |  |  |  |

| U-0          | R-1                 | R-0                                                                                                                                                             | R-0         | R-0              | R-0              | R-0             | R-0   |  |  |  |  |

|              |                     |                                                                                                                                                                 |             | ICODE<6:0>       |                  |                 |       |  |  |  |  |

| bit 7        |                     |                                                                                                                                                                 |             |                  |                  |                 | bit 0 |  |  |  |  |

| Legend:      |                     |                                                                                                                                                                 |             |                  |                  |                 |       |  |  |  |  |

| R = Readab   | le bit              | W = Writable bit                                                                                                                                                |             | U = Unimpler     | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR               | '1' = Bit is set                                                                                                                                                |             | '0' = Bit is cle |                  | x = Bit is unkr | nown  |  |  |  |  |

|              |                     |                                                                                                                                                                 |             |                  |                  |                 |       |  |  |  |  |

| bit 15-13    | Unimpleme           | nted: Read as '0'                                                                                                                                               |             |                  |                  |                 |       |  |  |  |  |

| bit 12-8     | FILHIT<4:0>         | : Filter Hit Number                                                                                                                                             | r bits      |                  |                  |                 |       |  |  |  |  |

|              | 01111 = Filt        |                                                                                                                                                                 |             |                  |                  |                 |       |  |  |  |  |

|              | 01110 <b>= Filt</b> | er 14                                                                                                                                                           |             |                  |                  |                 |       |  |  |  |  |

|              | <br>00001 = Filt    | er 1                                                                                                                                                            |             |                  |                  |                 |       |  |  |  |  |

|              | 00000 = Filt        | -                                                                                                                                                               |             |                  |                  |                 |       |  |  |  |  |

| bit 7        | Unimpleme           | nted: Read as '0'                                                                                                                                               |             |                  |                  |                 |       |  |  |  |  |

| bit 6-0      | ICODE<6:0>          | Interrupt Flag Co                                                                                                                                               | de bits     |                  |                  |                 |       |  |  |  |  |

|              |                     | 111111 <b>= Reserve</b>                                                                                                                                         |             |                  |                  |                 |       |  |  |  |  |

|              |                     | Transmit attempt in                                                                                                                                             |             |                  |                  |                 |       |  |  |  |  |

|              |                     | Transmit event FIF<br>Invalid message of                                                                                                                        | •           |                  | EFSTA IS Set)    |                 |       |  |  |  |  |

|              |                     | CAN module mode                                                                                                                                                 |             |                  | -/IE)            |                 |       |  |  |  |  |

|              |                     | CAN timer overflow                                                                                                                                              |             |                  | ,                |                 |       |  |  |  |  |

|              |                     | 1000101 = RX/TX MAB overflow/underflow (RX: Message received before previous message wa                                                                         |             |                  |                  |                 |       |  |  |  |  |

|              |                     | saved to memory; TX: Can't feed TX MAB fast enough to transmit consistent data)<br>1000100 = Address error interrupt (illegal FIFO address presented to system) |             |                  |                  |                 |       |  |  |  |  |

|              |                     | Receive FIFO over                                                                                                                                               |             |                  |                  |                 |       |  |  |  |  |

|              |                     | Wake-up interrupt                                                                                                                                               |             |                  |                  | ()              |       |  |  |  |  |

|              |                     | Error interrupt (CE                                                                                                                                             |             | ,                |                  |                 |       |  |  |  |  |

|              | 1000000 =           |                                                                                                                                                                 |             |                  |                  |                 |       |  |  |  |  |

|              |                     | 111111 = Reserve<br>FIFO 7 interrupt (T                                                                                                                         |             | IE7 is sot)      |                  |                 |       |  |  |  |  |

|              | 0000111 =           |                                                                                                                                                                 |             | ir i is selj     |                  |                 |       |  |  |  |  |

|              |                     | FIFO 1 interrupt (T                                                                                                                                             | FIF1 or RF  | IF1 is set)      |                  |                 |       |  |  |  |  |

|              | 0000000 =           | FIFO 0 interrupt (T                                                                                                                                             | FIF0 is set | )                |                  |                 |       |  |  |  |  |

|              |                     |                                                                                                                                                                 |             |                  |                  |                 |       |  |  |  |  |

## REGISTER 3-115: C1VECL: CAN INTERRUPT CODE REGISTER LOW

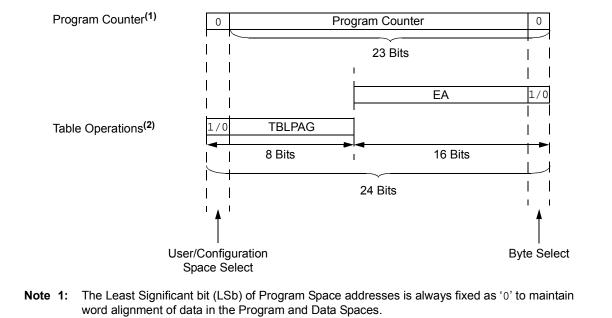

# 4.2.8 INTERFACING PROGRAM AND DATA MEMORY SPACES

The dsPIC33CH128MP508S1 family architecture uses a 24-bit wide Program Space (PS) and a 16-bit wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33CH128MP508S1 family devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. However, this method only provides visibility to the lower 16 bits in each location addressed.

## TABLE 4-19: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access |                               | Program Space Address |                     |               |     |  |  |  |

|------------------------|--------|-------------------------------|-----------------------|---------------------|---------------|-----|--|--|--|

| Access Type            | Space  | <23>                          | <22:16>               | <15>                | <14:1>        | <0> |  |  |  |

| Instruction Access     | User   | 0                             | PC<22:1> 0            |                     |               |     |  |  |  |

| (Code Execution)       |        | 0xxx xxxx xxxx xxxx xxxx xxx0 |                       |                     |               |     |  |  |  |

| TBLRD/TBLWT            | User   | TB                            | LPAG<7:0>             |                     | Data EA<15:0> |     |  |  |  |

| (Byte/Word Read/Write) |        | 0                             | xxx xxxx              | xxxx xxxx xxxx xxxx |               |     |  |  |  |

### FIGURE 4-11: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

2: Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

## REGISTER 4-102: ADIEL: ADC INTERRUPT ENABLE REGISTER LOW

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0              | R/W-0          | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|--------------------|----------------|-----------------|-------|

|                 |       |                  | IE<   | <15:8>             |                |                 |       |

| bit 15          |       |                  |       |                    |                |                 | bit 8 |

|                 |       |                  |       |                    |                |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0              | R/W-0          | R/W-0           | R/W-0 |

|                 |       |                  | IE    | <7:0>              |                |                 |       |

| bit 7           |       |                  |       |                    |                |                 | bit 0 |

|                 |       |                  |       |                    |                |                 |       |

| Legend:         |       |                  |       |                    |                |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpleme      | ented bit, rea | ıd as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clear | ed             | x = Bit is unkr | nown  |

bit 15-0 IE<15:0>: Common Interrupt Enable bits

1 = Common and individual interrupts are enabled for the corresponding channel

0 = Common and individual interrupts are disabled for the corresponding channel

#### REGISTER 4-103: ADIEH: ADC INTERRUPT ENABLE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | IE<20:16> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 IE<20:16>: Common Interrupt Enable bits

1 = Common and individual interrupts are enabled for the corresponding channel

0 = Common and individual interrupts are disabled for the corresponding channel

# 5.0 MASTER SLAVE INTERFACE (MSI)

Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Master Slave Interface (MSI) Module" (DS70005278) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Master Slave Interface (MSI) module is a bridge between the Master and a Slave processor system, each of which operates within independent clock domains. The Master and Slave have their own registers to communicate between the MSI modules; the Master MSI registers are located in the Master SFR space and the Slave MSI registers are in the Slave SFR space. The Master Slave Interface (MSI) includes these characteristics:

- 16 Unidirectional Data Mailbox Registers:

- Direction of each Mailbox register is fuse-selectable

- Byte and word-addressable

- Eight Mailbox Data Flow Control Protocol Blocks:

- Individual fuse enables

- Write port active; read port passive (i.e., no read data request required)

- Automatic, interrupt driven (or polled), data flow control mechanism across MSI clock boundary

- Fuse assignable to any of the Mailbox registers, supports any length data buffers (up to the number of available Mailbox registers)

- DMA transfer compatible

- Master to Slave and Slave to Master Interrupt Request with Acknowledge Data Flow Control

- Optional (parameterized) 2-Channel FIFO Memory Structure

- Parameterized Depth (between 16 and 32 words):

- One read and one write channel

- Circular operation with empty and full status, and interrupts

- Overflow/underflow detection with interrupts to Master core and Slave core

- Interrupt-based, software polled or DMA transfer compatible

- Master and Slave Processor Cross-Boundary Control and Status:

- Readable operating mode status for both processors

- Slave enable from Master (subject to satisfying a hardware write interlock sequencer)

- Master interrupt when Slave is reset during code execution

- Slave interrupt when Master is reset during code execution

- Optional (fuse) Decoupling of Master and Slave Resets; POR/BOR/MCLR always Resets Master and Slave; Influence of Remaining Run-Time Resets on the Slave Enable is Fuse-Programmable

## 5.1 Master MSI Control Registers

The following registers are associated with the Master MSI module and are located in the Master SFR space.

- Register 5-1: MSI1CON

- Register 5-2: MSI1STAT

- Register 5-3: MSI1KEY

- Register 5-4: MSI1MBXS

- Register 5-5: MSI1MBXnD

- Register 5-6: MSI1FIFOCS

- Register 5-7: MRSWFDATA

- Register 5-8: MWSRFDATA

Equation 6-1 provides the relationship between the PLL Input Frequency (FPLLI) and VCO Output Frequency (FVCO).

#### EQUATION 6-1: MASTER/SLAVE CORE Fvco CALCULATION

$FVCO = FPLLI \times \left(\frac{M}{N1}\right) = FPLLI \times \left(\frac{PLLFBDIV < 7:0>}{PLLPRE < 3:0>}\right)$

Equation 6-2 provides the relationship between the PLL Input Frequency (FPLLI) and PLL Output Frequency (FPLLO).

### EQUATION 6-2: MASTER/SLAVE CORE FPLLO CALCULATION

$FPLLO = FPLLI \times \left(\frac{M}{N1 \times N2 \times N3}\right) = FPLLI \times \left(\frac{PLLFBDIV < 7:0>}{PLLPRE < 3:0> \times POST1DIV < 2:0> \times POST2DIV < 2:0>}\right)$

Where:

M = PLLFBDIV<7:0> N1 = PLLPRE<3:0> N2 = POST1DIV<2:0> N3 = POST2DIV<2:0>

Note: The PLL Phase Detector Input Divider Select (PLLPREx) bits and the PLL Feedback Divider (PLLFBDIVx) bits should not be changed when operating in PLL mode. Therefore, the user must start in either a non-PLL mode or clock switch to a non-PLL mode (e.g., internal FRC Oscillator) to make any necessary changes and then clock switch to the desired PLL mode.

It is not permitted to directly clock switch from one PLL clock source to a different PLL clock source. The user would need to transition between PLL clock sources with a clock switch to a non-PLL clock source.

© 2017-2018 Microchip Technology Inc.

| R/W-0        | R/W-0                                                                                | R/W-0                                            | R/W-0           | R/W-0                                     | R/W-0                         | R/W-0                                 | R/W-0                    |

|--------------|--------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|-------------------------------------------|-------------------------------|---------------------------------------|--------------------------|

| ADTR1PS4     | ADTR1PS3                                                                             | ADTR1PS2                                         | ADTR1PS1        | ADTR1PS0                                  | ADTR1EN3                      | ADTR1EN2                              | ADTR1EN1                 |

| bit 15       |                                                                                      |                                                  |                 |                                           |                               |                                       | bit 8                    |

|              |                                                                                      |                                                  |                 |                                           |                               |                                       |                          |

| U-0          | U-0                                                                                  | U-0                                              | R/W-0           | R/W-0                                     | R/W-0                         | R/W-0                                 | R/W-0                    |

| —            | _                                                                                    | _                                                | UPDTRG1         | UPDTRG0                                   | PGTRGSEL2 <sup>(1)</sup>      | PGTRGSEL1 <sup>(1)</sup>              | PGTRGSEL0 <sup>(1)</sup> |

| bit 7        |                                                                                      |                                                  |                 |                                           |                               |                                       | bit 0                    |

|              |                                                                                      |                                                  |                 |                                           |                               |                                       |                          |

| Legend:      |                                                                                      |                                                  |                 |                                           |                               |                                       |                          |

| R = Readal   |                                                                                      | W = Writable                                     | bit             |                                           | mented bit, read              | as '0'                                |                          |

| -n = Value a | at POR                                                                               | '1' = Bit is se                                  | t               | '0' = Bit is cle                          | eared                         | x = Bit is unknow                     | n                        |

|              |                                                                                      |                                                  |                 |                                           |                               |                                       |                          |

| bit 15-11    |                                                                                      |                                                  | gger 1 Postso   | caler Selection                           | n bits                        |                                       |                          |

|              | 11111 <b>= 1</b> :3                                                                  | 2                                                |                 |                                           |                               |                                       |                          |

|              | 00010 <b>= 1</b> :3                                                                  |                                                  |                 |                                           |                               |                                       |                          |

|              | 00001 = 1:2                                                                          |                                                  |                 |                                           |                               |                                       |                          |

|              | 00000 = 1:1                                                                          |                                                  |                 |                                           |                               |                                       |                          |

| bit 10       |                                                                                      |                                                  |                 |                                           | ompare Event En               |                                       |                          |

|              |                                                                                      | •                                                | •               |                                           | s trigger source f            | or ADC Trigger 1<br>for ADC Trigger 1 |                          |

| bit 9        |                                                                                      | -                                                | -               |                                           | mpare Event En                |                                       |                          |

| bit 0        |                                                                                      |                                                  |                 |                                           | s trigger source for          |                                       |                          |

|              |                                                                                      |                                                  |                 |                                           |                               | or ADC Trigger 1                      |                          |

| bit 8        | ADTR1EN1                                                                             | ADC Trigger                                      | 1 Source is F   | PGxTRIGA Co                               | mpare Event En                | able bit                              |                          |

|              |                                                                                      |                                                  |                 |                                           | s trigger source for          |                                       |                          |

|              |                                                                                      | -                                                | -               | t is disabled a                           | s trigger source f            | or ADC Trigger 1                      |                          |

| bit 7-5      | -                                                                                    | nted: Read a                                     |                 |                                           |                               |                                       |                          |

| bit 4-3      |                                                                                      | :0>: Update T                                    |                 |                                           |                               |                                       |                          |

|              |                                                                                      |                                                  |                 |                                           | sets the UPDAT                |                                       |                          |

|              |                                                                                      |                                                  |                 |                                           | s the UPDATE bi               |                                       |                          |

|              |                                                                                      |                                                  |                 | GxSTAT<4>)                                |                               |                                       |                          |

|              | PGTRGSEL                                                                             | <2:0>: PWM                                       | Generator Tri   | igger Output S                            | Selection bits <sup>(1)</sup> |                                       |                          |

| bit 2-0      | TOINCOLL                                                                             |                                                  |                 |                                           |                               |                                       |                          |

| bit 2-0      | 111 = Rese                                                                           |                                                  |                 |                                           |                               |                                       |                          |

| bit 2-0      | 111 = Rese<br>110 = Rese                                                             | rved                                             |                 |                                           |                               |                                       |                          |

| bit 2-0      | 111 = Rese                                                                           | rved<br>rved                                     |                 |                                           |                               |                                       |                          |

| bit 2-0      | 111 = Rese<br>110 = Rese<br>101 = Rese<br>100 = Rese<br>011 = PGxT                   | rved<br>rved<br>rved<br>RIGC compa               |                 | e PWM Gener                               |                               |                                       |                          |

| bit 2-0      | 111 = Reset<br>110 = Reset<br>101 = Reset<br>100 = Reset<br>011 = PGxT<br>010 = PGxT | rved<br>rved<br>rved<br>RIGC compa<br>RIGB compa | re event is the | e PWM Gener<br>e PWM Gener<br>e PWM Gener | ator trigger                  |                                       |                          |

#### REGISTER 9-19: PGxEVTL: PWM GENERATOR x EVENT REGISTER LOW

Note 1: These events are derived from the internal PWM Generator time base comparison events.

| R/W-0                  | U-0                          | R/W-0                      | U-0                    | U-0                       | U-0                     | U-0                     | U-0                     |

|------------------------|------------------------------|----------------------------|------------------------|---------------------------|-------------------------|-------------------------|-------------------------|

| DACON                  | _                            | DACSIDL                    |                        | _                         | _                       |                         | —                       |

| bit 15                 |                              |                            |                        |                           |                         | I                       | bit 8                   |

|                        |                              |                            |                        |                           |                         |                         |                         |

| R/W-0                  | R/W-0                        | R/W-0                      | R/W-0                  | U-0                       | R/W-0                   | R/W-0                   | R/W-0                   |

| CLKSEL1 <sup>(1)</sup> | CLKSEL0 <sup>(1)</sup>       | CLKDIV1 <sup>(1)</sup>     | CLKDIV0 <sup>(1)</sup> | —                         | FCLKDIV2 <sup>(2)</sup> | FCLKDIV1 <sup>(2)</sup> | FCLKDIV0 <sup>(2)</sup> |

| bit 7                  |                              |                            |                        |                           |                         |                         | bit 0                   |

| Legend:                |                              |                            |                        |                           |                         |                         |                         |

| R = Readable           | e bit                        | W = Writable b             | it                     | U = Unimple               | emented bit, rea        | d as '0'                |                         |

| -n = Value at          |                              | '1' = Bit is set           |                        | '0' = Bit is c            |                         |                         |                         |

|                        |                              |                            |                        | 0 2000                    |                         |                         |                         |

| bit 15                 | DACON: Cor                   | mmon DAC Moo               | lule Enable bit        |                           |                         |                         |                         |

|                        | 1 = Enables                  | DAC modules                |                        |                           |                         |                         |                         |

|                        |                              |                            |                        |                           | to reduce powe          | r consumption           | ; any pending           |

|                        | -                            | ode and/or unde            |                        | s are cleared             |                         |                         |                         |

| bit 14                 | -                            | nted: Read as '            |                        |                           |                         |                         |                         |

| bit 13                 |                              | AC Stop in Idle            |                        |                           |                         |                         |                         |

|                        |                              | ues module opera           |                        |                           | dle mode                |                         |                         |

| bit 12-8               |                              | nted: Read as '(           |                        | •                         |                         |                         |                         |

| bit 7-6                | •                            | >: DAC Clock S             |                        | its <sup>(1)</sup>        |                         |                         |                         |

|                        | 11 <b>= F</b> pllo           |                            |                        |                           |                         |                         |                         |

|                        | 10 = AFPLLO                  |                            |                        |                           |                         |                         |                         |

|                        | 01 = Fvco/2<br>00 = AFvco/2  | n                          |                        |                           |                         |                         |                         |

| bit 5-4                |                              |                            | ividor bite (DAC       | chould be a               | perated at 500 N        | ر1) (1)                 |                         |

| Dit 3-4                | 11 = Divide-b                |                            | INIGEI DILS (DAC       |                           | perated at 500 h        | vii iz) <sup>(*</sup>   |                         |

|                        |                              | by -4<br>by-3 (non-unifori | n dutv cvcle)          |                           |                         |                         |                         |

|                        | 01 = Divide-b                | • •                        |                        |                           |                         |                         |                         |

|                        | 00 = 1x                      |                            |                        |                           |                         |                         |                         |

| bit 3                  | Unimplemer                   | nted: Read as 'o           | )'                     |                           |                         |                         |                         |

| bit 2-0                | FCLKDIV<2:                   | 0>: Comparator             | Filter Clock Div       | vider bits <sup>(2)</sup> |                         |                         |                         |

|                        | 111 = Divide                 | •                          |                        |                           |                         |                         |                         |

|                        | 110 = Divide<br>101 = Divide |                            |                        |                           |                         |                         |                         |

|                        | 101 - Divide                 |                            |                        |                           |                         |                         |                         |

|                        | 011 = Divide                 |                            |                        |                           |                         |                         |                         |

|                        | 010 = Divide                 | -by-3                      |                        |                           |                         |                         |                         |

|                        | 001 = Divide<br>000 = 1x     | -by-2                      |                        |                           |                         |                         |                         |

|                        |                              |                            |                        |                           |                         |                         |                         |

| Note 1: Th             | ese bits should              | d only be chang            | ed when DACO           | N = 0 to avo              | id unpredictable        | behavior.               |                         |

#### REGISTER 11-1: DACCTRL1L: DAC CONTROL 1 LOW REGISTER

- **Note 1:** These bits should only be changed when DACON = 0 to avoid unpredictable behavior.

- 2: The input clock to this divider is the selected clock input, CLKSEL<1:0>, and then divided by two.

#### REGISTER 12-1: QEIXCON: QEIX CONTROL REGISTER (CONTINUED)

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = External gate signal controls the position counter/timer operation</li> <li>0 = External gate signal does not affect the position counter/timer operation</li> </ul> |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                     |

|         | 11 = Internal timer with External Gate mode                                                                                                                                       |

- 10 = External Clock count with External Gate mode

- 01 = External Clock count with External Up/Down mode

- 00 = Quadrature Encoder mode

#### REGISTER 12-2: QEIxIOCL: QEIx I/O CONTROL LOW REGISTER

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0 |

|--------|--------|--------|--------|--------|---------|---------|-------|

| QCAPEN | FLTREN | QFDIV2 | QFDIV1 | QFDIV0 | OUTFNC1 | OUTFNC0 | SWPAB |

| bit 15 |        |        |        |        |         |         | bit 8 |

| R/W-0       | R/W-0  | R/W-0  | R/W-0  | R-x  | R-x   | R-x | R-x |

|-------------|--------|--------|--------|------|-------|-----|-----|

| HOMPOL      | IDXPOL | QEBPOL | QEAPOL | HOME | INDEX | QEB | QEA |

| bit 7 bit 0 |        |        |        |      |       |     |     |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15    | <b>QCAPEN:</b> QEIx Position Counter Input Capture by Index Event Enable bit<br>1 = Index match event (positive edge) triggers a position capture event                                                                                                                              |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 0 = Index match event (positive edge) does not trigger a position capture event                                                                                                                                                                                                      |

| bit 14    | FLTREN: QEAx/QEBx/INDXx/HOMEx Digital Filter Enable bit                                                                                                                                                                                                                              |

|           | <ul> <li>1 = Input pin digital filter is enabled</li> <li>0 = Input pin digital filter is disabled (bypassed)</li> </ul>                                                                                                                                                             |

| bit 13-11 | QFDIV<2:0>: QEAx/QEBx/INDXx/HOMEx Digital Input Filter Clock Divide Select bits                                                                                                                                                                                                      |

|           | 111 = 1:128 clock divide<br>110 = 1:64 clock divide<br>101 = 1:32 clock divide<br>100 = 1:16 clock divide<br>011 = 1:8 clock divide<br>010 = 1:4 clock divide<br>001 = 1:2 clock divide<br>000 = 1:1 clock divide                                                                    |

| bit 10-9  | OUTFNC<1:0>: QEIx Module Output Function Mode Select bits<br>11 = The CNTCMPx pin goes high when POSxCNT ≤ QEIxLEC or POSxCNT ≥ QEIxGEC<br>10 = The CNTCMPx pin goes high when POSxCNT ≤ QEIxLEC<br>01 = The CNTCMPx pin goes high when POSxCNT ≥ QEIxGEC<br>00 = Output is disabled |

| bit 8     | <b>SWPAB:</b> Swap QEAx and QEBx Inputs bit<br>1 = QEAx and QEBx are swapped prior to Quadrature Decoder logic<br>0 = QEAx and QEBx are not swapped                                                                                                                                  |

| bit 7     | HOMPOL: HOMEx Input Polarity Select bit<br>1 = Input is inverted<br>0 = Input is not inverted                                                                                                                                                                                        |

HSC/R-0

SPITUR<sup>(1)</sup>

bit 8

| U-0    | U-0 | U-0 | HS/R/C-0 | HSC/R-0 | U-0 | U-0 |  |

|--------|-----|-----|----------|---------|-----|-----|--|

|        | —   | —   | FRMERR   | SPIBUSY | —   | —   |  |

| bit 15 |     |     |          |         |     |     |  |

#### REGISTER 14-4: SPIxSTATL: SPIx STATUS REGISTER LOW

| HSC/R-0     | HS/R/C-0 | HSC/R-1 | U-0 | HSC/R-1 | U-0 | HSC/R-0 | HSC/R-0 |

|-------------|----------|---------|-----|---------|-----|---------|---------|

| SRMT        | SPIROV   | SPIRBE  | —   | SPITBE  | —   | SPITBF  | SPIRBF  |

| bit 7 bit 0 |          |         |     |         |     |         |         |

| Legend: C = Clearable bit |                  | U = Unimplemented, read as '0'        |                            |  |  |

|---------------------------|------------------|---------------------------------------|----------------------------|--|--|

| R = Readable bit          | W = Writable bit | HSC = Hardware Settable/Clearable bit |                            |  |  |

| -n = Value at POR         | '1' = Bit is set | '0' = Bit is cleared                  | HS = Hardware Settable bit |  |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                                                                                            |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12    | FRMERR: SPIx Frame Error Status bit                                                                                                                                   |

|           | 1 = Frame error is detected                                                                                                                                           |

|           | 0 = No frame error is detected                                                                                                                                        |

| bit 11    | SPIBUSY: SPIx Activity Status bit                                                                                                                                     |

|           | <ul> <li>1 = Module is currently busy with some transactions</li> <li>0 = No ongoing transactions (at time of read)</li> </ul>                                        |

| bit 10-9  | Unimplemented: Read as '0'                                                                                                                                            |

| bit 8     | SPITUR: SPIx Transmit Underrun Status bit <sup>(1)</sup>                                                                                                              |

|           | <ul> <li>1 = Transmit buffer has encountered a Transmit Underrun condition</li> <li>0 = Transmit buffer does not have a Transmit Underrun condition</li> </ul>        |

| bit 7     | SRMT: Shift Register Empty Status bit                                                                                                                                 |

|           | <ul> <li>1 = No current or pending transactions (i.e., neither SPIxTXB or SPIxTXSR contains data to transmit)</li> <li>0 = Current or pending transactions</li> </ul> |

| bit 6     | SPIROV: SPIx Receive Overflow Status bit                                                                                                                              |

|           | <ul> <li>1 = A new byte/half-word/word has been completely received when the SPIxRXB was full</li> <li>0 = No overflow</li> </ul>                                     |

| bit 5     | SPIRBE: SPIx RX Buffer Empty Status bit                                                                                                                               |

|           | 1 = RX buffer is empty<br>0 = RX buffer is not empty                                                                                                                  |

|           | Standard Buffer Mode:<br>Automatically set in hardware when SPIxBUF is read from, reading SPIxRXB. Automatically cleared in                                           |

|           | hardware when SPIx transfers data from SPIxRXSR to SPIxRXB.                                                                                                           |

|           | Enhanced Buffer Mode:<br>Indicates RXELM<5:0> = 000000.                                                                                                               |

| L:1 4     |                                                                                                                                                                       |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                            |

**Note 1:** SPITUR is cleared when SPIEN = 0. When IGNTUR = 1, SPITUR provides dynamic status of the Transmit Underrun condition, but does not stop RX/TX operation and does not need to be cleared by software.

## 16.3 Receive Mode

The module can be configured for receive operation by setting the RCVEN (SENTxCON1<11>) bit. The time between each falling edge is compared to SYNCMIN<15:0> (SENTxCON3<15:0>) and SYNCMAX<15:0> (SENTxCON2<15:0>), and if the measured time lies between the minimum and maximum limits, the module begins to receive data. The validated Sync time is captured in the SENTxSYNC register and the tick time is calculated. Subsequent falling edges are verified to be within the valid data width and the data is stored in the SENTxDATL/H registers. An interrupt event is generated at the completion of the message and the user software should read the SENTx Data registers before the reception of the next nibble. The equation for SYNCMIN<15:0> and SYNCMAX<15:0> is shown in Equation 16-3.

#### EQUATION 16-3: SYNCMIN<15:0> AND SYNCMAX<15:0> CALCULATIONS

$TTICK = TCLK \bullet (TICKTIME < 15:0 > + 1)$

FRAMETIME < 15:0 > = TTICK/TFRAME

SyncCount = 8 x FRCV x TTICK

SYNCMIN<15:0> = 0.8 x SyncCount

SYNCMAX<15:0> = 1.2 x SyncCount

$FRAMETIME < 15:0 \ge 122 + 27N$

$FRAMETIME < 15:0 > \ge 848 + 12N$

#### Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6  $F_{RCV}$  = FCY x Prescaler  $T_{CLK}$  = FCY/Prescaler

For TTICK = 3.0  $\mu$ s and FCLK = 4 MHz, SYNCMIN<15:0> = 76.

| Note: | To ensure a Sync period can be identified, |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | the value written to SYNCMIN<15:0>         |  |  |  |  |  |  |

|       | must be less than the value written to     |  |  |  |  |  |  |

|       | SYNCMAX<15:0>.                             |  |  |  |  |  |  |

#### 16.3.1 RECEIVE MODE CONFIGURATION

#### 16.3.1.1 Initializing the SENTx Module

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 1 for Receive mode.

- 2. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 3. Write CRCEN (SENTxCON1<8>) for hardware or software CRC validation.

- 4. Write PPP (SENTxCON1<7>) = 1 if pause pulse is present.

- 5. Write SENTxCON2 with the value of SYNCMAXx (Nominal Sync Period + 20%).

- 6. Write SENTxCON3 with the value of SYNCMINx (Nominal Sync Period 20%).

- 7. Enable interrupts and set interrupt priority.

- 8. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

The data should be read from the SENTxDATL/H registers after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt trigger.

### **REGISTER 16-3:** SENTXDATL: SENTX RECEIVE DATA REGISTER LOW<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 |

|--------|-------|-------|-------|-------|-------|--------|-------|

|        | DATA4 | <3:0> |       |       | DATAS | 5<3:0> |       |

| bit 15 |       |       |       |       |       |        | bit 8 |

|        |       |       |       |       |       |        |       |

|        |       |       |       |       |       |        |       |

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-------|--------|-------|----------|-------|-------|-------|--|

|       | DATA6 | 6<3:0> |       | CRC<3:0> |       |       |       |  |

| bit 7 |       |        |       |          |       |       | bit 0 |  |

| Legend:           |                  |                       |                      |

|-------------------|------------------|-----------------------|----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , <b>read as</b> '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown   |

| bit 15-12 | DATA4<3:0>: Data Nibble 4 Data bits |

|-----------|-------------------------------------|

| bit 11-8  | DATA5<3:0>: Data Nibble 5 Data bits |

| bit 7-4   | DATA6<3:0>: Data Nibble 6 Data bits |

| bit 3-0   | CRC<3:0>: CRC Nibble Data bits      |

**Note 1:** Register bits are read-only in Receive mode (RCVEN = 1). In Transmit mode, the CRC<3:0> bits are read-only when automatic CRC calculation is enabled (RCVEN = 0, CRCEN = 1).

#### REGISTER 16-4: SENTxDATH: SENTx RECEIVE DATA REGISTER HIGH<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0             | R/W-0           | R/W-0          | R/W-0      | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|-------------------|-----------------|----------------|------------|-------|-------|--|--|

| STAT<3:0>                          |       |                   |                 |                | DATA1<3:0> |       |       |  |  |

| bit 15                             |       |                   |                 |                |            |       | bit 8 |  |  |

| R/W-0                              | R/W-0 | R/W-0             | R/W-0           | R/W-0          | R/W-0      | R/W-0 | R/W-0 |  |  |

| DATA2<3:0>                         |       |                   | DATA3<3:0>      |                |            |       |       |  |  |

| bit 7                              |       |                   |                 |                |            | bit C |       |  |  |

| Legend:                            |       |                   |                 |                |            |       |       |  |  |

| R = Readable bit W = Writable bit  |       | U = Unimplen      | nented bit, rea | ad as '0'      |            |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unk | nown       |       |       |  |  |

bit 15-12 STAT<3:0>: Status Nibble Data bits

bit 11-8 **DATA1<3:0>:** Data Nibble 1 Data bits

bit 7-4 DATA2<3:0>: Data Nibble 2 Data bits

bit 3-0 DATA3<3:0>: Data Nibble 3 Data bits

**Note 1:** Register bits are read-only in Receive mode (RCVEN = 1). In Transmit mode, the CRC<3:0> bits are read-only when automatic CRC calculation is enabled (RCVEN = 0, CRCEN = 1).

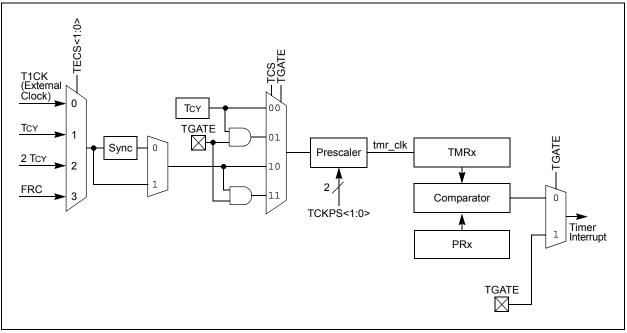

## 17.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timer1 Module" (DS70005279) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: The timer is identical for both Master core and Slave core. The x is common for both Master core and Slave core (where the x represents the number of the specific module being addressed).

- All associated register names are the same on the Master core and the Slave core. The Slave code will be developed in a separate project in MPLAB<sup>®</sup> X IDE with the device selection, dsPIC33CH128MP508S1, where S1 indicates the Slave device.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be Operated in Asynchronous Counter mode

- Asynchronous Timer

- · Operational during CPU Sleep mode

- Software Selectable Prescalers 1:1, 1:8, 1:64 and 1:256

- · External Clock Selection Control

- The Timer1 External Clock Input (T1CK) can Optionally be Synchronized to the Internal Device Clock and the Clock Synchronization is Performed after the Prescaler

If Timer1 is used for SCCP, the timer should be running in Synchronous mode.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

Table 17-1 shows an overview of the Timer1 module.

#### TABLE 17-1:TIMER1 MODULE OVERVIEW

|             | Number of<br>Timer1 Modules | ldentical<br>(Modules) |

|-------------|-----------------------------|------------------------|

| Master Core | 1                           | Yes                    |

| Slave Core  | 1                           | Yes                    |

A block diagram of Timer1 is shown in Figure 17-1.

## FIGURE 17-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| REGISTER 21-9: FDMTIVTL CONFIGURATION REGISTER |

|------------------------------------------------|

|------------------------------------------------|

| U-1    | U-1          | U-1    | U-1    | U-1    | U-1    | U-1    | U-1    |  |

|--------|--------------|--------|--------|--------|--------|--------|--------|--|

| _      | —            | —      |        | —      | —      | —      | —      |  |

| bit 23 |              | •      |        |        |        | •      | bit 16 |  |

|        |              |        |        |        |        |        |        |  |

| R/PO-1 | R/PO-1       | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |  |

|        | DMTIVT<15:8> |        |        |        |        |        |        |  |

| bit 15 |

|--------|

|--------|

| R/PO-1      | R/PO-1      | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |  |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--|

| DMTIVT<7:0> |             |        |        |        |        |        |        |  |

| bit 7       | bit 7 bit 0 |        |        |        |        |        |        |  |

| Legend:           | PO = Program Once bit |                       |                    |  |