Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 27                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 36-UQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp503-e-m5 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.6 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to a certain frequency (see Section 6.0 "Oscillator with High-Frequency PLL") to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

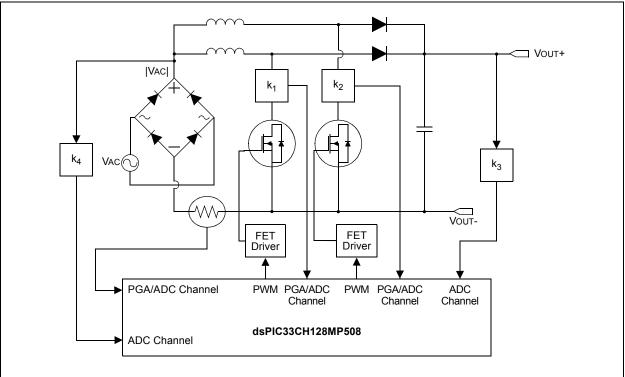

# FIGURE 2-4: INTERLEAVED PFC

#### 2.8 Targeted Applications

- Power Factor Correction (PFC):

- Interleaved PFC

- Critical Conduction PFC

- Bridgeless PFC

- DC/DC Converters:

- Buck, Boost, Forward, Flyback, Push-Pull

- Half/Full-Bridge

- Phase-Shift Full-Bridge

- Resonant Converters

- · DC/AC:

- Half/Full-Bridge Inverter

- Resonant Inverter

- Motor Control

- BLDC

- PMSM

- SR

- ACIM

Examples of typical application connections are shown in Figure 2-4 through Figure 2-6.

## 3.2.5.2 Extended X Data Space

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible, regardless of the contents of the Data Space Read Page register. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space in combination with DSRPAG = 0x00. Consequently, DSRPAG is initialized to 0x001 at Reset.

- Note 1: DSRPAG should not be used to access Page 0. An EDS access with DSRPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSRPAG in software has no effect.

The remaining PSV pages are only accessible using the DSRPAG register in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit, EA<15> = 1.

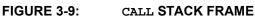

#### 3.2.5.3 Software Stack

The W15 register serves as a dedicated Software Stack Pointer (SSP), and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33CH128MP508 devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 3-9 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes). When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 3-9. During exception processing, the MSB of the PC is concatenated with the lower eight bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

# REGISTER 3-139: C1FIFOUAHx: CAN FIFO USER ADDRESS REGISTER x (x = 1 TO 7) HIGH<sup>(1)</sup>

| R-x     | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|---------|-----|-----|--------|---------|-----|-----|-------|

|         |     |     | FIFOUA | <31:24> |     |     |       |

| bit 15  |     |     |        |         |     |     | bit 8 |

|         |     |     |        |         |     |     |       |

| R-x     | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|         |     |     | FIFOUA | <23:16> |     |     |       |

| bit 7   |     |     |        |         |     |     | bit 0 |

|         |     |     |        |         |     |     |       |

| Legend: |     |     |        |         |     |     |       |

| Legenu.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

FIFOUA<31:16>: FIFO User Address bits

TXEN = 1 (FIFO configured as a transmit buffer):

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0 (FIFO configured as a receive buffer):

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

#### **REGISTER 3-140:** C1FIFOUALX: CAN FIFO USER ADDRESS REGISTER x (x = 1 TO 7) $LOW^{(1)}$

| R-x             | R-x | R-x              | R-x    | R-x                 | R-x          | R-x                | R-x   |

|-----------------|-----|------------------|--------|---------------------|--------------|--------------------|-------|

|                 |     |                  | FIFOUA | \<15:8>             |              |                    |       |

| bit 15          |     |                  |        |                     |              |                    | bit 8 |

|                 |     |                  |        |                     |              |                    |       |

| R-x             | R-x | R-x              | R-x    | R-x                 | R-x          | R-x                | R-x   |

|                 |     |                  | FIFOU  | A<7:0>              |              |                    |       |

| bit 7           |     |                  |        |                     |              |                    | bit 0 |

|                 |     |                  |        |                     |              |                    |       |

| Legend:         |     |                  |        |                     |              |                    |       |

| R = Readable I  | bit | W = Writable bit |        | U = Unimpleme       | nted bit, re | ad as '0'          |       |

| -n = Value at P | OR  | '1' = Bit is set |        | '0' = Bit is cleare | ed           | x = Bit is unknowr | ı     |

bit 15-0

FIFOUA<15:0>: FIFO User Address bits

TXEN = 1 (FIFO configured as a transmit buffer):

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0 (FIFO configured as a receive buffer):

A read of this register will return the address where the next message is to be read (FIFO tail).

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

# 4.1.5 PROGRAMMER'S MODEL

The programmer's model for the dsPIC33CH128MP508S1 family is shown in Figure 4-2. All registers in the programmer's model are memorymapped and can be manipulated directly by instructions. Table 4-1 lists a description of each register. In addition to the registers contained in the programmer's model, the dsPIC33CH128MP508S1 devices contain control registers for Modulo Addressing, Bit-Reversed Addressing and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Figure 4-3.

| Register(s) Name                                  | Description                                                   |

|---------------------------------------------------|---------------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>                     | Working Register Array                                        |

| W0 through W14 <sup>(1)</sup>                     | Alternate 1 Working Register Array                            |

| W0 through W14 <sup>(1)</sup>                     | Alternate 2 Working Register Array                            |

| W0 through W14 <sup>(1)</sup>                     | Alternate 3 Working Register Array                            |

| W0 through W14 <sup>(1)</sup>                     | Alternate 4 Working Register Array                            |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators (Additional 4 Alternate Accumulators) |

| PC                                                | 23-Bit Program Counter                                        |

| SR                                                | ALU and DSP Engine STATUS Register                            |

| SPLIM                                             | Stack Pointer Limit Value Register                            |

| TBLPAG                                            | Table Memory Page Address Register                            |

| DSRPAG                                            | Extended Data Space (EDS) Read Page Register                  |

| RCOUNT                                            | REPEAT Loop Counter Register                                  |

| DCOUNT                                            | DO Loop Counter Register                                      |

| DOSTARTH <sup>(2)</sup> , DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)                 |

| DOENDH, DOENDL                                    | DO Loop End Address Register (High and Low)                   |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits     |

Note 1: Memory-mapped W0 through W14 represent the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

## REGISTER 4-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                           |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                               |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                       |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                         |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                         |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                        |

| Noto 1: | The IPI $<2:0$ bits are concatenated with the IPI $<3$ bit (COPCON( $<3$ )) to form the CPI I Interrupt Priority                                                                                                                                                                                                                                                                                               |

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

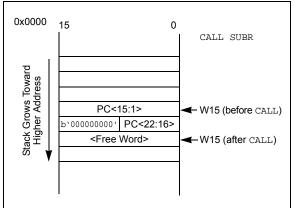

## 4.2.1.1 Program Memory Organization

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-4).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented, or decremented, by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.2.1.2 Interrupt and Trap Vectors

All dsPIC33CH128MP508S1 family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of PRAM memory, with the actual address for the start of code at address, 0x000200, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in Table 4-20.

#### FIGURE 4-4: PROGRAM MEMORY ORGANIZATION

# 4.2.2 DATA ADDRESS SPACE (SLAVE)

The dsPIC33CH128MP508S1 family CPU has a separate 16-bit wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory map is shown in Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes or 32K words.

The lower half of the data memory space (i.e., when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV).

The dsPIC33CH128MP508S1 family devices implement up to 4 Kbytes of data memory. If an EA points to a location outside of this area, an all-zero word or byte is returned.

#### 4.2.2.1 Data Space Width

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2.2 Data Memory Organization and Alignment

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33CH128MP508S1 family instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through wordaligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.2.3 SFR Space

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33CH128MP508S1 family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.2.4 Near Data Space

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

# REGISTER 4-24: TRISX: OUTPUT ENABLE FOR PORTX REGISTER

| R/W-1                              | R/W-1 | R/W-1 | R/W-1 | R/W-1                              | R/W-1 | R/W-1          | R/W-1 |  |

|------------------------------------|-------|-------|-------|------------------------------------|-------|----------------|-------|--|

|                                    |       |       | TRIS  | x<15:8>                            |       |                |       |  |

| bit 15                             |       |       |       |                                    |       |                | bit 8 |  |

| R/W-1                              | R/W-1 | R/W-1 | R/W-1 | R/W-1                              | R/W-1 | R/W-1          | R/W-1 |  |

|                                    |       |       | TRIS  | Sx<7:0>                            |       |                |       |  |

| bit 7                              |       |       |       |                                    |       |                | bit 0 |  |

|                                    |       |       |       |                                    |       |                |       |  |

| Legend:                            |       |       |       |                                    |       |                |       |  |

| R = Readable bit W = Writable bit  |       |       | bit   | U = Unimplemented bit, read as '0' |       |                |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cle                   | eared | x = Bit is unk | nown  |  |

bit 15-0 TRISx<15:0>: Output Enable for PORTx bits

1 = LATx[n] is not driven on PORTx[n] pin

0 = LATx[n] is driven on PORTx[n] pin

## REGISTER 4-25: PORTX: INPUT DATA FOR PORTX REGISTER

| R/W-1                             | R/W-1 | R/W-1            | R/W-1                                 | R/W-1    | R/W-1           | R/W-1 | R/W-1 |

|-----------------------------------|-------|------------------|---------------------------------------|----------|-----------------|-------|-------|

|                                   |       |                  | POR                                   | Tx<15:8> |                 |       |       |

| bit 15                            |       |                  |                                       |          |                 |       | bit 8 |

| R/W-1                             | R/W-1 | R/W-1            | R/W-1                                 | R/W-1    | R/W-1           | R/W-1 | R/W-1 |

|                                   |       |                  | POF                                   | Tx<7:0>  |                 |       |       |

| bit 7                             |       |                  |                                       |          |                 |       | bit C |

| Legend:                           |       |                  |                                       |          |                 |       |       |

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0'    |          |                 |       |       |

| -n = Value at F                   | POR   | '1' = Bit is set | et '0' = Bit is cleared x = Bit is ur |          | x = Bit is unkr | nown  |       |

bit 15-0 **PORTx<15:0>:** PORTx Data Input Value bits

# dsPIC33CH128MP508 FAMILY

# 5.0 MASTER SLAVE INTERFACE (MSI)

Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Master Slave Interface (MSI) Module" (DS70005278) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Master Slave Interface (MSI) module is a bridge between the Master and a Slave processor system, each of which operates within independent clock domains. The Master and Slave have their own registers to communicate between the MSI modules; the Master MSI registers are located in the Master SFR space and the Slave MSI registers are in the Slave SFR space. The Master Slave Interface (MSI) includes these characteristics:

- 16 Unidirectional Data Mailbox Registers:

- Direction of each Mailbox register is fuse-selectable

- Byte and word-addressable

- Eight Mailbox Data Flow Control Protocol Blocks:

- Individual fuse enables

- Write port active; read port passive (i.e., no read data request required)

- Automatic, interrupt driven (or polled), data flow control mechanism across MSI clock boundary

- Fuse assignable to any of the Mailbox registers, supports any length data buffers (up to the number of available Mailbox registers)

- DMA transfer compatible

- Master to Slave and Slave to Master Interrupt Request with Acknowledge Data Flow Control

- Optional (parameterized) 2-Channel FIFO Memory Structure

- Parameterized Depth (between 16 and 32 words):

- One read and one write channel

- Circular operation with empty and full status, and interrupts

- Overflow/underflow detection with interrupts to Master core and Slave core

- Interrupt-based, software polled or DMA transfer compatible

- Master and Slave Processor Cross-Boundary Control and Status:

- Readable operating mode status for both processors

- Slave enable from Master (subject to satisfying a hardware write interlock sequencer)

- Master interrupt when Slave is reset during code execution

- Slave interrupt when Master is reset during code execution

- Optional (fuse) Decoupling of Master and Slave Resets; POR/BOR/MCLR always Resets Master and Slave; Influence of Remaining Run-Time Resets on the Slave Enable is Fuse-Programmable

# 5.1 Master MSI Control Registers

The following registers are associated with the Master MSI module and are located in the Master SFR space.

- Register 5-1: MSI1CON

- Register 5-2: MSI1STAT

- Register 5-3: MSI1KEY

- Register 5-4: MSI1MBXS

- Register 5-5: MSI1MBXnD

- Register 5-6: MSI1FIFOCS

- Register 5-7: MRSWFDATA

- Register 5-8: MWSRFDATA

# 5.2 Slave MSI Control Registers

The following registers are associated with the Slave MSI module and are located in the Slave SFR space.

- Register 5-9: SI1CON

- Register 5-10: SI1STAT

- Register 5-11: SI1MBX

- Register 5-12: SI1MBXnD

- Register 5-13: SI1FIFOCS

- Register 5-14: SWMRFDATA

- Register 5-15: SRMWFDATA

## REGISTER 5-9: SI1CON: MSI1 SLAVE CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0  | R/W-0   |

|--------|-----|-----|-----|----------|----------|--------|---------|

| —      | —   | —   | —   | RFITSEL1 | RFITSEL0 | STMIRQ | MTSIACK |

| bit 15 |     |     |     |          |          |        | bit 8   |

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| MRSTIE | —   | —   | —   | —   | —   | —   | —     |

| bit 7  |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-12 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-10 | RFITSEL<1:0>: Read FIFO Interrupt Threshold Select bits                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>11 = Triggers data valid interrupt when FIFO is full after Slave write</li> <li>10 = Triggers data valid interrupt when FIFO is 75% full after Slave write</li> <li>01 = Triggers data valid interrupt when FIFO is 50% full after Slave write</li> <li>00 = Triggers data valid interrupt when 1st FIFO entry is written by Slave</li> </ul> |

| bit 9     | STMIRQ: Slave to Master Interrupt Request bit                                                                                                                                                                                                                                                                                                          |

|           | <ul> <li>1 = Interrupts the Master</li> <li>0 = Does not interrupt the Master</li> </ul>                                                                                                                                                                                                                                                               |

| bit 8     | MTSIACK: Slave to Acknowledge Master Interrupt bit                                                                                                                                                                                                                                                                                                     |

|           | <ul> <li>1 = If MTSIRQ = 1, Slave Acknowledges Master interrupt request, else protocol error</li> <li>0 = If MTSIRQ = 0, Slave has not yet Acknowledged Master interrupt request, else no Master to Slave interrupt request is pending</li> </ul>                                                                                                      |

| bit 7     | MRSTIE: Master Reset Event Interrupt Enable bit                                                                                                                                                                                                                                                                                                        |

|           | <ul> <li>1 = Slave Master Reset event interrupt occurs when Master enters Reset state</li> <li>0 = Slave Master Reset event interrupt does not occur when Master enters Reset state</li> </ul>                                                                                                                                                         |

|           |                                                                                                                                                                                                                                                                                                                                                        |

bit 6-0 Unimplemented: Read as '0'

# 15.4 I<sup>2</sup>C Control/Status Registers

#### REGISTER 15-1: I2CxCONL: I2Cx CONTROL REGISTER LOW

| R/W-0            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HC/R/W-0                                                                                                                           | R/W-1                                                                                                                                                                                        | R/W-0                                                                                                     |                                                                         |                                                                         |                                         |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------|--|

|                  | 0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                    | SCLREL <sup>(1)</sup>                                                                                                                                                                        | -                                                                                                         | R/W-0                                                                   | R/W-0                                                                   | R/W-0                                   |  |

| I2CEN            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I2CSIDL                                                                                                                            | SCLREL                                                                                                                                                                                       | STRICT                                                                                                    | A10M                                                                    | DISSLW                                                                  | SMEN                                    |  |

| bit 15           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         | bit 8                                   |  |

| R/W-0            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                              | HC/R/W-0                                                                                                                                                                                     | HC/R/W-0                                                                                                  | HC/R/W-0                                                                | HC/R/W-0                                                                | HC/R/W-0                                |  |

| GCEN             | STREN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ACKDT                                                                                                                              | ACKEN                                                                                                                                                                                        | RCEN                                                                                                      | PEN                                                                     | RSEN                                                                    | SEN                                     |  |

| bit 7            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |                                                                                                                                                                                              | -                                                                                                         |                                                                         |                                                                         | bit                                     |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HC = Hardware                                                                                                                      | e Clearable bit                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |

| R = Readable     | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W = Writable b                                                                                                                     | bit                                                                                                                                                                                          | U = Unimplem                                                                                              | nented bit, read                                                        | l as '0'                                                                |                                         |  |

| -n = Value at    | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                                                                                                                   |                                                                                                                                                                                              | '0' = Bit is clea                                                                                         | ared                                                                    | x = Bit is unkr                                                         | nown                                    |  |

| bit 15<br>bit 14 | 1 = Enables f<br>0 = Disables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Enable bit (writa<br>the I2Cx module<br>the I2Cx module<br>nted: Read as '0                                                        | e, and configure<br>e; all I <sup>2</sup> C pins a                                                                                                                                           | s the SDAx and                                                                                            |                                                                         | serial port pins                                                        | 3                                       |  |

|                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |

| bit 13           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cx Stop in Idle M                                                                                                                  |                                                                                                                                                                                              | vice enters Idle                                                                                          | mode                                                                    |                                                                         |                                         |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | s module operat<br>CLx Release Cor                                                                                                 |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |

| bit 11           | 0 = Holds the<br><u>If STREN = 1</u><br>User software<br>at the beginn<br>address byte<br><u>If STREN = 0</u><br>User software<br>data byte tran<br><b>STRICT</b> : I2C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | e may write '0' to<br>ning of every Sla<br>reception. Hard<br><u>):</u><br>e may only write<br>nsmission. Hard<br>x Strict Reserve | <ul> <li>(clock stretch)</li> <li>initiate a clock</li> <li>ave data byte t</li> <li>ware clears at t</li> <li>'1' to release t</li> <li>ware clears at t</li> <li>d Address Rule</li> </ul> | stretch and wri<br>ransmission. H<br>the end of every<br>he clock. Hardv<br>he end of every<br>Enable bit | ardware clears<br>y Slave data by<br>vare clears at t<br>y Slave addres | s at the end of<br>/te reception.<br>he beginning o<br>s byte reception | <sup>:</sup> every Slav<br>f every Slav |  |

|                  | <ul> <li>STRICT: I2Cx Strict Reserved Address Rule Enable bit</li> <li>1 = Strict Reserved Addressing is enforced; for reserved addresses, refer to Table 15-2.<br/>(In Slave Mode) – The device doesn't respond to reserved address space and addresses falling in that category are NACKed.<br/>(In Master Mode) – The device is allowed to generate addresses with reserved address space.</li> <li>0 = Reserved Addressing would be Acknowledged.<br/>(In Slave Mode) – The device will respond to an address falling in the reserved address space.</li> <li>0 = Reserved Addressing would be Acknowledged.<br/>(In Slave Mode) – The device will respond to an address falling in the reserved address space.<br/>When there is a match with any of the reserved addresses, the device will generate an ACK.<br/>(In Master Mode) – Reserved.</li> </ul> |                                                                                                                                    |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |

| bit 10           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t Slave Address                                                                                                                    | -                                                                                                                                                                                            |                                                                                                           |                                                                         |                                                                         |                                         |  |

|                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ) is a 10-bit Slav<br>) is a 7-bit Slave                                                                                           |                                                                                                                                                                                              |                                                                                                           |                                                                         |                                                                         |                                         |  |

| oit 9            | DISSLW: Sle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | w Rate Control                                                                                                                     | Disable bit                                                                                                                                                                                  |                                                                                                           |                                                                         |                                                                         |                                         |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e control is disab<br>e control is enab                                                                                            |                                                                                                                                                                                              |                                                                                                           |                                                                         | disabled for 1                                                          | MHz mode)                               |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ared to '0' at the                                                                                                                 | •                                                                                                                                                                                            |                                                                                                           |                                                                         | ally cleared to '                                                       | 0' at the end                           |  |

2: Automatically cleared to '0' at the beginning of Slave transmission.

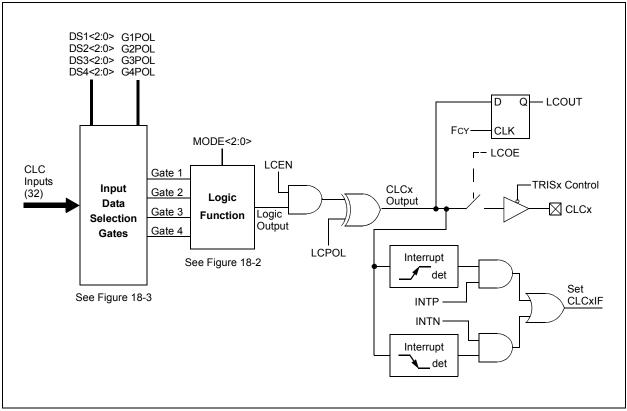

# 18.0 CONFIGURABLE LOGIC CELL (CLC)

- Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. For more information, refer to "Configurable Logic Cell (CLC)" (DS70005298) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- The CLC is identical for both Master core and Slave core (where the x represents the number of the specific module being addressed in Master or Slave).

- 3: All associated register names are the same on the Master core and the Slave core. The Slave code will be developed in a separate project in MPLAB<sup>®</sup> X IDE with the device selection, dsPIC33CH128MP508S1, where the S1 indicates the Slave device. The Master and Slave are CLC1 and CLC2.

FIGURE 18-1: CLCx MODULE

The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins. This provides greater flexibility and potential in embedded designs, since the CLC module can operate outside the limitations of software execution, and supports a vast amount of output designs.

There are four input gates to the selected logic function. These four input gates select from a pool of up to 32 signals that are selected using four data source selection multiplexers. Table 18-1 shows an overview of the module.

| TABLE 18-1: | <b>CLC MODULE OVERVIEW</b> |

|-------------|----------------------------|

|-------------|----------------------------|

|        | Number of CLC<br>Modules | Identical<br>(Modules) |  |  |  |

|--------|--------------------------|------------------------|--|--|--|

| Master | 4                        | Yes                    |  |  |  |

| Slave  | 4                        | Yes                    |  |  |  |

Figure 18-3 shows the details of the data source multiplexers and Figure 18-2 shows the logic input gate connections.

# REGISTER 18-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | <b>G3D2T:</b> Gate 3 Data Source 2 True Enable bit<br>1 = Data Source 2 signal is enabled for Gate 3<br>0 = Data Source 2 signal is disabled for Gate 3 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit                                                                                                          |

|       | <ul><li>1 = Data Source 2 inverted signal is enabled for Gate 3</li><li>0 = Data Source 2 inverted signal is disabled for Gate 3</li></ul>              |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit                                                                                                             |

|       | <ul><li>1 = Data Source 1 signal is enabled for Gate 3</li><li>0 = Data Source 1 signal is disabled for Gate 3</li></ul>                                |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit                                                                                                          |

|       | <ul><li>1 = Data Source 1 inverted signal is enabled for Gate 3</li><li>0 = Data Source 1 inverted signal is disabled for Gate 3</li></ul>              |

| <b>TABLE 21-3:</b> | SLAVE CONFIGURATION REGISTERS MAP |

|--------------------|-----------------------------------|

|--------------------|-----------------------------------|

| Register<br>Name | Bits 23-16 | Bit 15    | Bit 14 | Bit 13       | Bit 12     | Bit 11 | Bit 10 | Bit 9      | Bit 8            | Bit 7            | Bit 6   | Bit 5      | Bit 4 | Bit 3     | Bit 2       | Bit 1     | Bit 0  |

|------------------|------------|-----------|--------|--------------|------------|--------|--------|------------|------------------|------------------|---------|------------|-------|-----------|-------------|-----------|--------|

| FS1OSCSEL        | _          | —         | _      | _            | _          | _      | _      | -          | -                | S1IESO           | _       | _          | _     | _         | S1FN        | NOSC<2:0> |        |

| FS1OSC           | _          | _         | -      | _            | _          | -      | _      | _          | <sub>۲</sub> (1) | S1FCK            | SM<1:0> | _          | _     | _         | S10SCI0FNC  | _         | _      |

| FS1WDT           | _          | S1FWDTEN  |        | S18          | SWDTPS<4:0 | >      |        | S1WDTV     | VIN<1:0>         | S1WINDIS         | S1RCLKS | EL<1:0>    |       | S1        | RWDTPS<4:0> |           |        |

| FS1POR           | _          | _         | -      | _            | _          | -      | _      | _          | _                | _                | -       | _          | _     | _         | _           | _         | _      |

| FS1ICD           | _          | S1NOBTSWP | -      | S1ISOLAT     | _          | -      | _      | _          | _                | <sub>۲</sub> (1) | -       | _          | _     | _         | _           | S1ICS     | S<1:0> |

| FS1DEVOPT        | _          | S1MSRE    | S1SSRE | S1SPI1PIN    | _          | -      | _      | _          | _                | _                | -       | _          | _     | S1ALTI2C1 | _           | _         | _      |

| FS1ALTREG        | -          | —         | Ş      | S1CTXT4<2:0> |            | _      | S      | ICTXT3<2:0 | >                | —                | Sŕ      | 1CTXT2<2:0 | >     | _         | S1C         | TXT1<2:0> |        |

Legend: — = unimplemented bit, read as '1'; r = reserved bit.

Note 1: Bit is reserved, maintain as '1'.

# **REGISTER 21-19: FMBXHSEN CONFIGURATION REGISTER**

| U-1     | U-1    | U-1          | U-1                                                             | U-1    | U-1    | U-1    | U-1    |

|---------|--------|--------------|-----------------------------------------------------------------|--------|--------|--------|--------|