Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 27                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 20К х 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 36-UQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp503-i-m5 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 | U-0                                                                                                                 | R/W-0                                                      | R/W-0          | R/W-0               | R-0              | R-0             | R-0         |

|-----------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------|---------------------|------------------|-----------------|-------------|

| VAR             | —                                                                                                                   | US1                                                        | US0            | EDT <sup>(1)</sup>  | DL2              | DL1             | DL0         |

| bit 15          |                                                                                                                     |                                                            |                |                     |                  |                 | bit 8       |

| R/W-0           | R/W-0                                                                                                               |                                                            | R/W-0          | R/C-0               | R-0              | R/W-0           | R/W-0       |

|                 | -                                                                                                                   | R/W-1                                                      |                | IPL3 <sup>(2)</sup> | -                | -               | -           |

| SATA<br>bit 7   | SATB                                                                                                                | SATDW                                                      | ACCSAT         | IPL3 <sup>(-)</sup> | SFA              | RND             | IF<br>bit 0 |

|                 |                                                                                                                     |                                                            |                |                     |                  |                 | bit 0       |

| Legend:         |                                                                                                                     | C = Clearable                                              | e bit          |                     |                  |                 |             |

| R = Readable    | bit                                                                                                                 | W = Writable                                               | bit            | U = Unimplei        | mented bit, rea  | id as '0'       |             |

| -n = Value at I | POR                                                                                                                 | '1' = Bit is set                                           |                | '0' = Bit is cle    | eared            | x = Bit is unkr | nown        |

| bit 15          | 1 = Variable e                                                                                                      | e Exception Pro<br>exception proce                         | essing is enab | led                 |                  |                 |             |

| bit 14          | Unimplemen                                                                                                          | ted: Read as '                                             | 0'             |                     |                  |                 |             |

| bit 13-12       | US<1:0>: DS                                                                                                         | P Multiply Uns                                             | igned/Signed   | Control bits        |                  |                 |             |

|                 | 01 = DSP eng                                                                                                        | d<br>gine multiplies<br>gine multiplies<br>gine multiplies | are unsigned   | ٦                   |                  |                 |             |

| bit 11          | EDT: Early DO Loop Termination Control bit <sup>(1)</sup>                                                           |                                                            |                |                     |                  |                 |             |

|                 | 1 = Terminate<br>0 = No effect                                                                                      | es executing DO                                            | loop at the e  | nd of the curre     | nt loop iteratio | n               |             |

| bit 10-8        | DL<2:0>: DO                                                                                                         | Loop Nesting                                               | Level Status b | its                 |                  |                 |             |

|                 | 111 = Seven                                                                                                         | DO loops are a                                             | ctive          |                     |                  |                 |             |

|                 |                                                                                                                     | o loop is active<br>o loops are act                        |                |                     |                  |                 |             |

| bit 7           | SATA: ACCA                                                                                                          | Saturation En                                              | able bit       |                     |                  |                 |             |

|                 |                                                                                                                     | itor A saturatio<br>itor A saturatio                       |                |                     |                  |                 |             |

| bit 6           | SATB: ACCB                                                                                                          | Saturation En                                              | able bit       |                     |                  |                 |             |

|                 |                                                                                                                     | itor B saturatio<br>itor B saturatio                       |                |                     |                  |                 |             |

| bit 5           | SATDW: Data                                                                                                         | a Space Write                                              | from DSP Eng   | ine Saturation      | Enable bit       |                 |             |

|                 | <ul> <li>1 = Data Space write saturation is enabled</li> <li>0 = Data Space write saturation is disabled</li> </ul> |                                                            |                |                     |                  |                 |             |

| bit 4           | 1 = 9.31 satu                                                                                                       | cumulator Satu<br>ration (super s<br>ration (normal        | aturation)     | Select bit          |                  |                 |             |

| bit 3           | IPL3: CPU In                                                                                                        | terrupt Priority                                           | -              |                     |                  |                 |             |

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

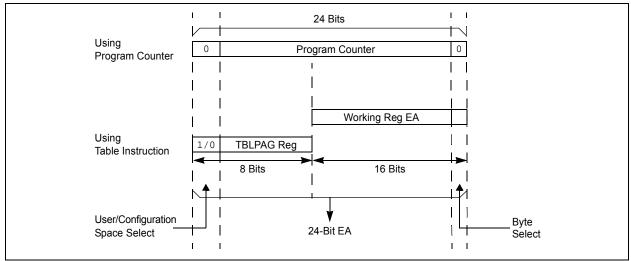

#### FIGURE 3-14: ADDRESSING FOR TABLE REGISTERS

#### 3.4.2 RESET CONTROL REGISTER

## REGISTER 3-15: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0                | U-0                                 | U-0            | U-0                   | U-0              | R/W-0            | R/W-0        |  |

|-----------------|----------------------|-------------------------------------|----------------|-----------------------|------------------|------------------|--------------|--|

| TRAPR           | IOPUWR               | —                                   | —              | _                     | —                | CM               | VREGS        |  |

| bit 15          |                      |                                     |                |                       |                  |                  | bit 8        |  |

| R/W-0           | R/W-0                | U-0                                 | R/W-0          | R/W-0                 | R/W-0            | R/W-1            | R/W-1        |  |

| EXTR            | SWR                  |                                     | WDTO           | SLEEP                 | IDLE             | BOR              | POR          |  |

| bit 7           | own                  |                                     | WBIO           | OLLLI                 | IDEE             | Bolt             | bit (        |  |

|                 |                      |                                     |                |                       |                  |                  |              |  |

| Legend:         |                      |                                     |                |                       |                  |                  |              |  |

| R = Readable    | bit                  | W = Writable                        | bit            | U = Unimpler          | nented bit, read | l as '0'         |              |  |

| -n = Value at F | POR                  | '1' = Bit is set                    |                | '0' = Bit is cle      | ared             | x = Bit is unki  | nown         |  |

|                 |                      | Deest Flee bit                      |                |                       |                  |                  |              |  |

| bit 15          |                      | Reset Flag bit                      |                |                       |                  |                  |              |  |

|                 |                      | onflict Reset ha                    |                | d                     |                  |                  |              |  |

| bit 14          | •                    |                                     |                |                       | ess Reset Flag   | bit              |              |  |

|                 |                      |                                     |                |                       | ode or Uninitial |                  | er used as a |  |

|                 | Address              | Pointer caused                      | l a Reset      |                       |                  | -                |              |  |

|                 | •                    | •                                   |                | Register Reset        | has not occurre  | d                |              |  |

| oit 13-10       | -                    | Unimplemented: Read as '0'          |                |                       |                  |                  |              |  |

| oit 9           | •                    | ation Mismatch                      | •              |                       |                  |                  |              |  |

|                 |                      | ration Mismato                      |                |                       |                  |                  |              |  |

| oit 8           | VREGS: Volta         | age Regulator                       | Standby Durin  | ig Sleep bit          |                  |                  |              |  |

|                 | •                    | egulator is acti<br>equlator goes i | •              | ep<br>node during Sle | еер              |                  |              |  |

| oit 7           | -                    | al Reset (MCL                       |                | <b>3</b> -            | 1-               |                  |              |  |

|                 |                      | Clear (pin) Res<br>Clear (pin) Res  |                |                       |                  |                  |              |  |

| bit 6           |                      | re RESET (Inst                      |                |                       |                  |                  |              |  |

|                 | 1 <b>= A</b> reset i | instruction has instruction has     | been execute   | ed                    |                  |                  |              |  |

| oit 5           |                      | ted: Read as '                      |                |                       |                  |                  |              |  |

| oit 4           | -                    | hdog Timer Tin                      |                | ŀ                     |                  |                  |              |  |

|                 |                      | e-out has occur                     |                | -                     |                  |                  |              |  |

|                 | 0 = WDT time         | e-out has not o                     | ccurred        |                       |                  |                  |              |  |

| bit 3           | SLEEP: Wake          | e-up from Slee                      | p Flag bit     |                       |                  |                  |              |  |

|                 |                      | is been in Slee<br>is not been in S | -              |                       |                  |                  |              |  |

| bit 2           | IDLE: Wake-u         | IDLE: Wake-up from Idle Flag bit    |                |                       |                  |                  |              |  |

|                 | 1 = Device ha        | s been in Idle                      | mode           |                       |                  |                  |              |  |

| L:1 A           |                      | is not been in I                    |                |                       |                  |                  |              |  |

| bit 1           |                      | out Reset Flag                      |                |                       |                  |                  |              |  |

|                 |                      | out Reset has<br>out Reset has      |                |                       |                  |                  |              |  |

| Note 1: All     | of the Reset sta     | tue hite can he                     | set or cleared | t in coffwara. S      | etting one of th | oso hite in coft | wara daga na |  |

cause a device Reset.

## REGISTER 3-99: DMTPSINTVL: DMT POST-CONFIGURE INTERVAL STATUS REGISTER LOW

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------------|-------|-------|-------|----------------------|-------|-------|-------|

|                                                                            |       |       | PSINT | <sup>-</sup> V<15:8> |       |       |       |

| bit 15                                                                     |       |       |       |                      |       |       | bit 8 |

|                                                                            |       |       |       |                      |       |       |       |

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|                                                                            |       |       | PSIN  | TV<7:0>              |       |       |       |

| bit 7                                                                      |       |       |       |                      |       |       | bit 0 |

|                                                                            |       |       |       |                      |       |       |       |

| Legend:                                                                    |       |       |       |                      |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |       |       |       |                      |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       |       |                      | nown  |       |       |

bit 15-0 **PSINTV<15:0>:** Lower DMT Window Interval Configuration Status bits This is always the value of the FDMTIVTL Configuration register.

#### REGISTER 3-100: DMTPSINTVH: DMT POST-CONFIGURE INTERVAL STATUS REGISTER HIGH

| R/W-0                                                                  | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0           | R/W-0            | R/W-0 |

|------------------------------------------------------------------------|-------|-------|-------|----------|-----------------|------------------|-------|

|                                                                        |       |       | PSINT | V<31:24> |                 |                  |       |

| bit 15                                                                 |       |       |       |          |                 |                  | bit 8 |

| R/W-0                                                                  | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0           | R/W-0            | R/W-0 |

|                                                                        |       |       | PSINT | V<23:16> |                 |                  |       |

| bit 7                                                                  |       |       |       |          |                 |                  | bit ( |

| Legend:                                                                |       |       |       |          |                 |                  |       |

| R = Readable bit W = Writable bit U = Unimplemented bit,               |       |       |       |          | nented bit, rea | <b>id as</b> '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk |       |       |       | nown     |                 |                  |       |

bit 15-0 **PSINTV<31:16>:** Higher DMT Window Interval Configuration Status bits This is always the value of the FDMTIVTH Configuration register.

## REGISTER 3-158: ADCON1H: ADC CONTROL REGISTER 1 HIGH

| U-0                  | U-0                                                                                                                                      | U-0              | U-0            | U-0               | U-0              | U-0             | U-0   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-------------------|------------------|-----------------|-------|

| —                    | —                                                                                                                                        | —                | —              | —                 | —                | —               | —     |

| bit 15               |                                                                                                                                          |                  |                |                   |                  |                 | bit 8 |

|                      |                                                                                                                                          |                  |                |                   |                  |                 |       |

| R/W-0                | R/W-1                                                                                                                                    | R/W-1            | U-0            | U-0               | U-0              | U-0             | U-0   |

| FORM                 | SHRRES1                                                                                                                                  | SHRRES0          | _              | —                 |                  |                 |       |

| bit 7                |                                                                                                                                          |                  |                |                   |                  |                 | bit 0 |

|                      |                                                                                                                                          |                  |                |                   |                  |                 |       |

| Legend:              |                                                                                                                                          |                  |                |                   |                  |                 |       |

| R = Readable bit W = |                                                                                                                                          | W = Writable     | bit            | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at F      | POR                                                                                                                                      | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|                      |                                                                                                                                          |                  |                |                   |                  |                 |       |

| bit 15-8             | Unimplemen                                                                                                                               | ted: Read as 'd  | )'             |                   |                  |                 |       |

| bit 7                | FORM: Fracti                                                                                                                             | onal Data Outp   | out Format bit |                   |                  |                 |       |

|                      | 1 = Fractional<br>0 = Integer                                                                                                            |                  |                |                   |                  |                 |       |

| bit 6-5              | sit 6-5 SHRRES<1:0>: Shared ADC Core Resolution Selection bits                                                                           |                  |                |                   |                  |                 |       |

|                      | <ul> <li>11 = 12-bit resolution</li> <li>10 = 10-bit resolution</li> <li>01 = 8-bit resolution</li> <li>00 = 6-bit resolution</li> </ul> |                  |                |                   |                  |                 |       |

| bit 4-0              | Unimplemented: Read as '0'                                                                                                               |                  |                |                   |                  |                 |       |

#### 4.2.5 INSTRUCTION ADDRESSING MODES

The addressing modes shown in Table 4-17 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.2.5.1 File Register Instructions

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

## 4.2.5.2 MCU Instructions

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

## TABLE 4-17: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

## REGISTER 4-11: ECCADDRL: ECC FAULT INJECT ADDRESS COMPARE REGISTER LOW

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------------|-------|-------|-------|-----------|-------|-------|-------|

|                                                                            |       |       | ECCAE | DDR<15:8> |       |       |       |

| bit 15                                                                     |       |       |       |           |       |       | bit 8 |

|                                                                            |       |       |       |           |       |       |       |

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|                                                                            |       |       | ECCA  | DDR<7:0>  |       |       |       |

| bit 7                                                                      |       |       |       |           |       |       | bit 0 |

|                                                                            |       |       |       |           |       |       |       |

| Legend:                                                                    |       |       |       |           |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |       |       |       |           |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       |       |           | nown  |       |       |

| •                                                                          |       |       |       |           |       |       |       |

bit 15-0 ECCADDR<15:0>: ECC Fault Injection Memory Address Match Compare bits

#### REGISTER 4-12: ECCADDRH: ECC FAULT INJECT ADDRESS COMPARE REGISTER HIGH

| R/W-0                                                     | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|--|

|                                                           |       |       | ECCAD | DR<31:24>                          |       |       |       |  |

| bit 15                                                    |       |       |       |                                    |       |       | bit 8 |  |

|                                                           |       |       |       |                                    |       |       |       |  |

| R/W-0                                                     | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|                                                           |       |       | ECCAD | DR<23:16>                          |       |       |       |  |

| bit 7                                                     |       |       |       |                                    |       |       | bit 0 |  |

|                                                           |       |       |       |                                    |       |       |       |  |

| Legend:                                                   |       |       |       |                                    |       |       |       |  |

| R = Readable bit W = Writable bit                         |       |       | it    | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x |       |       |       | x = Bit is unkr                    | nown  |       |       |  |

|                                                           |       |       |       |                                    |       |       |       |  |

bit 15-0 ECCADDR<31:16>: ECC Fault Injection Memory Address Match Compare bits

### 4.6.6 I/O HELPFUL TIPS

- 1. In some cases, certain pins, as defined in Table 24-18 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or lesser than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low-side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins, by default, after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Select for PORTx registers, in the I/O ports module (i.e., ANSELx), by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx =  $0 \times 0$ , while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in Section 24.0 "Electrical Characteristics" of this data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted.

#### REGISTER 4-47: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| R/W-0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| QEIHOM1R7 | QEIHOM1R6 | QEIHOM1R5 | QEIHOM1R4 | QEIHOM1R3 | QEIHOM1R2 | QEIHOM1R1 | QEIHOM1R0 |

| bit 15    | •         |           |           |           |           | •         | bit 8     |

| R/W-0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| QEINDX1R7 | QEINDX1R6 | QEINDX1R5 | QEINDX1R4 | QEINDX1R3 | QEINDX1R2 | QEINDX1R1 | QEINDX1R0 |

| bit 7     |           |           |           |           |           |           | bit 0     |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **QEIHOM1R<7:0>:** Assign QEI Home 1 Input (S1QEIHOM1) to the Corresponding S1RPn Pin bits See Table 4-27.

## REGISTER 4-48: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| U1DSRR7 | U1DSRR6 | U1DSRR5 | U1DSRR4 | U1DSRR3 | U1DSRR2 | U1DSRR1 | U1DSRR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| U1RXR7 | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **U1DSRR<7:0>:** Assign UART1 Data-Set-Ready (S1U1DSR) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 **U1RXR<7:0>:** Assign UART1 Receive (S1U1RX) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 **QEINDX1R<7:0>:** Assign QEI Index 1 Input (S1QEINDX1) to the Corresponding S1RPn Pin bits See Table 4-27.

| R/W-0           | R/W-0                                                                                                                                                                                               | R/W-0                                                                                                                                            | R/W-0                                                                                                 | R/W-0                                                                  | R/W-0                         | R/W-0           | R/W-0            |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------|-----------------|------------------|--|--|

| CLKSEL1         | CLKSEL0                                                                                                                                                                                             | CLKDIV5                                                                                                                                          | CLKDIV4                                                                                               | CLKDIV3                                                                | CLKDIV2                       | CLKDIV1         | CLKDIV0          |  |  |

| bit 15          |                                                                                                                                                                                                     |                                                                                                                                                  |                                                                                                       |                                                                        |                               |                 | bit 8            |  |  |

|                 |                                                                                                                                                                                                     |                                                                                                                                                  |                                                                                                       |                                                                        |                               |                 |                  |  |  |

| R/W-0           | U-0                                                                                                                                                                                                 | U-0                                                                                                                                              | U-0                                                                                                   | U-0                                                                    | U-0                           | R/W-0           | R/W-0            |  |  |

| SHREN           |                                                                                                                                                                                                     |                                                                                                                                                  |                                                                                                       |                                                                        |                               | C1EN            | C0EN             |  |  |

| bit 7 bit 0     |                                                                                                                                                                                                     |                                                                                                                                                  |                                                                                                       |                                                                        |                               |                 |                  |  |  |

| <u> </u>        |                                                                                                                                                                                                     |                                                                                                                                                  |                                                                                                       |                                                                        |                               |                 |                  |  |  |

| Legend:         |                                                                                                                                                                                                     |                                                                                                                                                  |                                                                                                       |                                                                        |                               | ( <b>a</b> )    |                  |  |  |

| R = Readable    |                                                                                                                                                                                                     | W = Writable k                                                                                                                                   | bit                                                                                                   | •                                                                      | ented bit, read               |                 |                  |  |  |

| -n = Value at I | POR                                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                 |                                                                                                       | '0' = Bit is clea                                                      | ared                          | x = Bit is unkn | IOWN             |  |  |

| bit 15-14       | CLKSEL<1:0<br>11 = FvCo/4<br>10 = AFvCoDI<br>01 = Fosc                                                                                                                                              | >: ADC Module                                                                                                                                    | Clock Source                                                                                          | Selection bits                                                         |                               |                 |                  |  |  |

|                 | 00 = FP (Fost                                                                                                                                                                                       | c/2)                                                                                                                                             |                                                                                                       |                                                                        |                               |                 |                  |  |  |

|                 | module clock<br>TCORESRC clo<br>register or the<br>111111 = 64<br><br>000011 = 4 S<br>000010 = 3 S<br>000001 = 2 S<br>000000 = 1 S                                                                  | source selected<br>ock to get a cor<br>SHRADCS<6:<br>Source Clock Pe<br>Source Clock Pe<br>Source Clock Pe<br>Source Clock Pe<br>Source Clock Pe | d by the CLKS<br>e-specific TAD<br>0> bits in the A<br>Periods<br>eriods<br>eriods<br>eriods<br>eriod | y all ADC cores<br>EL<1:0> bits. T<br>CORE clock usii<br>ADCON2L regis | hen, each ADC<br>ng the ADCS< | core individua  | ally divides the |  |  |

| bit 7           | 1 = Shared Al                                                                                                                                                                                       | red ADC Core I<br>DC core is enal<br>DC core is disa                                                                                             | bled                                                                                                  |                                                                        |                               |                 |                  |  |  |

| bit 6-2         | Unimplement                                                                                                                                                                                         | ted: Read as 'o                                                                                                                                  | ,                                                                                                     |                                                                        |                               |                 |                  |  |  |

| bit 1           | C1EN: Dedicated ADC Core 1 Enable bits<br>1 = Dedicated ADC Core 1 is enabled                                                                                                                       |                                                                                                                                                  |                                                                                                       |                                                                        |                               |                 |                  |  |  |

| bit 0           | <ul> <li>0 = Dedicated ADC Core 1 is disabled</li> <li>C0EN: Dedicated ADC Core 0 Enable bits</li> <li>1 = Dedicated ADC Core 0 is enabled</li> <li>0 = Dedicated ADC Core 0 is disabled</li> </ul> |                                                                                                                                                  |                                                                                                       |                                                                        |                               |                 |                  |  |  |

## REGISTER 4-88: ADCON3H: ADC CONTROL REGISTER 3 HIGH

## REGISTER 14-1: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

| bit 7 |    | SSEN: Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                                                        |

|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |    | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the Slave select input 0 = $\overline{SSx}$ pin is not used by the macro ( $\overline{SSx}$ pin will be controlled by the port I/O) |

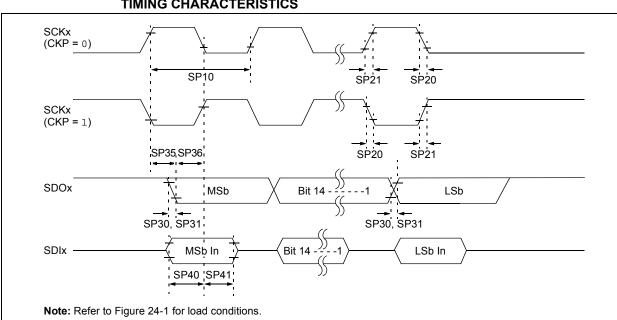

| bit 6 |    | CKP: Clock Polarity Select bit                                                                                                                                                                                                   |

|       |    | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                         |

| bit 5 |    | MSTEN: Master Mode Enable bit                                                                                                                                                                                                    |

|       |    | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                                                |

| bit 4 |    | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                                              |

|       |    | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                                                 |

| bit 3 |    | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                                             |

|       |    | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                                                 |

| bit 2 |    | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                                                   |

|       |    | 1 = MCLK is used by the BRG<br>0 = PBCLK is used by the BRG                                                                                                                                                                      |

| bit 1 |    | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                                                          |

|       |    | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                                               |

| bit 0 |    | ENHBUF: Enhanced Buffer Enable bit                                                                                                                                                                                               |

|       |    | <ul> <li>1 = Enhanced Buffer mode is enabled</li> <li>0 = Enhanced Buffer mode is disabled</li> </ul>                                                                                                                            |

| Note  | 1: | When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.                                                                                                                             |

|       | 2: | When FRMEN = 1, SSEN is not used.                                                                                                                                                                                                |

- 3: MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

NOTES:

## **REGISTER 21-16: FMBXM CONFIGURATION REGISTER (CONTINUED)**

| bit 9 | <ul> <li>MBXM9: Mailbox Data Register Channel Direction Fuses bits</li> <li>1 = Mailbox Register #9 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #9 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8 | <ul> <li>MBXM8: Mailbox Data Register Channel Direction Fuses bits</li> <li>1 = Mailbox Register #8 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #8 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 7 | <ul> <li>MBXM7: Mailbox Data Register Channel Direction Fuses bits</li> <li>1 = Mailbox Register #7 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #7 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 6 | <ul> <li>MBXM6: Mailbox Data Register Channel Direction Fuses bits</li> <li>1 = Mailbox Register #6 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #6 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 5 | <b>MBXM5:</b> Mailbox Data Register Channel Direction Fuses bits<br>1 = Mailbox Register #5 is configured for Master data read (Slave to Master data transfer)<br>0 = Mailbox Register #5 is configured for Master data write (Master to Slave data transfer)                          |

| bit 4 | <ul> <li>MBXM4: Mailbox Data Register Channel Direction Fuses bits</li> <li>1 = Mailbox Register #4 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #4 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 3 | <b>MBXM3:</b> Mailbox Data Register Channel Direction Fuses bits<br>1 = Mailbox Register #3 is configured for Master data read (Slave to Master data transfer)<br>0 = Mailbox Register #3 is configured for Master data write (Master to Slave data transfer)                          |

| bit 2 | <ul> <li>MBXM2: Mailbox Data Register Channel Direction Fuses bits</li> <li>1 = Mailbox Register #2 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #2 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 1 | <ul> <li>MBXM1: Mailbox Data Register Channel Direction Fuses bits</li> <li>1 = Mailbox Register #1 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #1 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

| bit 0 | <ul> <li>MBXM0: Mailbox Data Register Channel Direction Fuses bits</li> <li>1 = Mailbox Register #0 is configured for Master data read (Slave to Master data transfer)</li> <li>0 = Mailbox Register #0 is configured for Master data write (Master to Slave data transfer)</li> </ul> |

## REGISTER 21-30: FS1DEVOPT CONFIGURATION REGISTER (SLAVE)

| U-1          | U-1       | U-1                                  | U-1           | U-1               | U-1                | U-1             | U-1             |

|--------------|-----------|--------------------------------------|---------------|-------------------|--------------------|-----------------|-----------------|

| _            |           | —                                    | _             | —                 | _                  | —               | _               |

| bit 23       | ·         |                                      |               |                   |                    |                 | bit 16          |

|              |           |                                      |               |                   |                    |                 |                 |

| R/PO-1       | R/PO-1    | R/PO-1                               | U-1           | U-1               | U-1                | U-1             | U-1             |

| S1MSRE       | S1SSRE    | S1SPI1PIN <sup>(1)</sup>             | _             | _                 | —                  | —               | _               |

| bit 15       |           |                                      |               |                   |                    |                 | bit 8           |

|              |           |                                      |               |                   |                    |                 |                 |

| U-1          | U-1       | U-1                                  | U-1           | R/PO-1            | U-1                | U-1             | U-1             |

|              |           |                                      |               | S1ALTI2C1         | —                  |                 |                 |

| bit 7        |           |                                      |               |                   |                    |                 | bit 0           |

|              |           |                                      |               |                   |                    |                 |                 |

| Legend:      |           | PO = Program (                       | Once bit      |                   |                    |                 |                 |

| R = Readab   |           | W = Writable bit                     | t             | U = Unimplem      |                    |                 |                 |

| -n = Value a | It POR    | '1' = Bit is set                     |               | '0' = Bit is clea | ared               | x = Bit is unkr | nown            |

|              |           |                                      |               |                   |                    |                 |                 |

| bit 23-16    | -         | nted: Read as '1'                    |               |                   |                    |                 |                 |

| bit 15       |           | aster Slave Rese                     |               |                   | a a dia 10/atala d | T: T:           |                 |

|              |           | ster software-orie                   |               |                   |                    |                 | but Reset, Trap |

|              |           | ster software-orie                   |               |                   |                    |                 | out Reset, Trap |

|              | Reset, I  | llegal Instruction I                 | Reset) will n | ot cause the Slav | ve subsystem       | to reset        |                 |

| bit 14       |           | ave Reset Enable                     |               |                   |                    |                 |                 |

|              |           | nerated Resets w                     |               |                   |                    |                 |                 |

| h:+ 40       | -         | nerated Resets w<br>Slave SPI1 Fast  |               |                   | e dit in the IVIS  | module          |                 |

| bit 13       |           | Plave SPIT Fast<br>Pl1 uses PPS (I/O |               |                   | ith dovice pipe    |                 |                 |

|              |           | PI1 uses direct co                   |               |                   |                    | >               |                 |

| bit 12-4     |           | nted: Read as '1'                    |               |                   |                    |                 |                 |

| bit 3        | -         | Alternate I2C1 P                     |               | bit               |                    |                 |                 |

|              |           | ocation for SCL1/                    |               |                   |                    |                 |                 |

|              |           | e location for SCL                   |               | s (ASCL1/ASDA1    | l)                 |                 |                 |

| bit 2-0      | Unimpleme | nted: Read as '1'                    |               |                   |                    |                 |                 |

|              |           |                                      |               |                   |                    |                 |                 |

Note 1: Fixed pin option is only available for higher pin packages (48-pin, 64-pin and 80-pin).

| Base<br>Instr<br># | Assembly<br>Mnemonic |         |                                 | Description                                                                                            | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|---------|---------------------------------|--------------------------------------------------------------------------------------------------------|---------------|-------------------------------|--------------------------|

| 60                 | MIN                  | MIN Acc |                                 | If Accumulator A Less than B Load<br>Accumulator with B or vice versa                                  | 1             | 1                             | N,OV,Z                   |

|                    |                      | MIN.V   | Acc, Wd                         | If Accumulator A Less than B Accumulator<br>Force Minimum Data Range Limit with Limit<br>Excess Result | 1             | 1                             | N,OV,Z                   |

|                    |                      | MINZ    | Acc                             | Accumulator Force Minimum Data Range Limit                                                             | 1             | 1                             | N,OV,Z                   |

|                    |                      | MINZ.V  | Acc, Wd                         | Accumulator Force Minimum Data Range Limit with Limit Excess Result                                    | 1             | 1                             | N,OV,Z                   |

| 61                 | MOV                  | MOV     | f,Wn                            | Move f to Wn                                                                                           | 1             | 1                             | None                     |

|                    |                      | MOV     | f                               | Move f to f                                                                                            | 1             | 1                             | None                     |

|                    |                      | MOV     | f,WREG                          | Move f to WREG                                                                                         | 1             | 1                             | None                     |

|                    |                      | MOV     | #lit16,Wn                       | Move 16-bit Literal to Wn                                                                              | 1             | 1                             | None                     |

|                    |                      | MOV.b   | #lit8,Wn                        | Move 8-bit Literal to Wn                                                                               | 1             | 1                             | None                     |

|                    |                      | MOV     | Wn,f                            | Move Wn to f                                                                                           | 1             | 1                             | None                     |

|                    |                      | MOV     | Wso,Wdo                         | Move Ws to Wd                                                                                          | 1             | 1                             | None                     |

|                    |                      | MOV     | WREG, f                         | Move WREG to f                                                                                         | 1             | 1                             | None                     |

|                    |                      | MOV.D   | Wns,Wd                          | Move Double from W(ns):W(ns + 1) to Wd                                                                 | 1             | 2                             | None                     |

|                    |                      | MOV.D   | Ws,Wnd                          | Move Double from Ws to<br>W(nd + 1):W(nd)                                                              | 1             | 2                             | None                     |

| 62                 | MOVPAG               | MOVPAG  | #lit10,DSRPAG                   | Move 10-bit Literal to DSRPAG                                                                          | 1             | 1                             | None                     |

|                    |                      | MOVPAG  | #lit8,TBLPAG                    | Move 8-bit Literal to TBLPAG                                                                           | 1             | 1                             | None                     |

|                    |                      | MOVPAG  | Ws, DSRPAG                      | Move Ws<9:0> to DSRPAG                                                                                 | 1             | 1                             | None                     |

|                    |                      | MOVPAG  | Ws, TBLPAG                      | Move Ws<7:0> to TBLPAG                                                                                 | 1             | 1                             | None                     |

| 64                 | MOVSAC               | MOVSAC  | Acc,Wx,Wxd,Wy,Wyd,AWB           | Prefetch and Store Accumulator                                                                         | 1             | 1                             | None                     |

| 65                 | MPY                  | MPY     | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd         | Multiply Wm by Wn to Accumulator                                                                       | 1             | 1                             | OA,OB,OAB<br>SA,SB,SAB   |

|                    |                      | MPY     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd         | Square Wm to Accumulator                                                                               | 1             | 1                             | OA,OB,OAB<br>SA,SB,SAB   |

| 66                 | MPY.N                | MPY.N   | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd         | -(Multiply Wm by Wn) to Accumulator                                                                    | 1             | 1                             | None                     |

| 67                 | MSC                  | MSC     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd,<br>AWB | Multiply and Subtract from Accumulator                                                                 | 1             | 1                             | OA,OB,OAB<br>SA,SB,SAB   |

| 68                 | MUL                  | MUL.SS  | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = Signed(Wb) * Signed(Ws)                                                               | 1             | 1                             | None                     |

|                    |                      | MUL.SS  | Wb,Ws,Acc                       | Accumulator = Signed(Wb) * Signed(Ws)                                                                  | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = Signed(Wb) * Unsigned(Ws)                                                             | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Acc                       | Accumulator = Signed(Wb) * Unsigned(Ws)                                                                | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Acc                    | Accumulator = Signed(Wb) * Unsigned(lit5)                                                              | 1             | 1                             | None                     |

|                    |                      | MUL.US  | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = Unsigned(Wb) * Signed(Ws)                                                             | 1             | 1                             | None                     |

|                    |                      | MUL.US  | Wb,Ws,Acc                       | Accumulator = Unsigned(Wb) * Signed(Ws)                                                                | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = Unsigned(Wb) *<br>Unsigned(Ws)                                                        | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Acc                    | Accumulator = Unsigned(Wb) * Unsigned(lit5)                                                            | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Acc                       | Accumulator = Unsigned(Wb) * Unsigned(Ws)                                                              | 1             | 1                             | None                     |

|                    |                      | MULW.SS | Wb,Ws,Wnd                       | Wnd = Signed(Wb) * Signed(Ws)                                                                          | 1             | 1                             | None                     |

|                    |                      | MULW.SU | Wb,Ws,Wnd                       | Wnd = Signed(Wb) * Unsigned(Ws)                                                                        | 1             | 1                             | None                     |

|                    |                      | MULW.US | Wb,Ws,Wnd                       | Wnd = Unsigned(Wb) * Signed(Ws)                                                                        | 1             | 1                             | None                     |

|                    |                      | MULW.UU | Wb,Ws,Wnd                       | Wnd = Unsigned(Wb) * Unsigned(Ws)                                                                      | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                    | {Wnd + 1, Wnd} = Signed(Wb) * Unsigned(lit5)                                                           | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                    | Wnd = Signed(Wb) * Unsigned(lit5)                                                                      | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                    | {Wnd + 1, Wnd} = Unsigned(Wb) *<br>Unsigned(lit5)                                                      | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                    | Wnd = Unsigned(Wb) * Unsigned(lit5)                                                                    | 1             | 1                             | None                     |

|                    |                      | MUL     | f                               | W3:W2 = f * WREG                                                                                       | 1             | 1                             | None                     |