Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit Dual-Core                                                                |

| Speed                      | 180MHz, 200MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 88KB (88K x 8)                                                                  |

| Program Memory Type        | FLASH, PRAM                                                                     |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 34x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ch64mp506-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADLE 3-0 | <b>.</b> . | ASIEK SFK DL                            |           |         |                                         |            | -       |                                         |

|-----------|------------|-----------------------------------------|-----------|---------|-----------------------------------------|------------|---------|-----------------------------------------|

| Register  | Address    | All Resets                              | Register  | Address | All Resets                              | Register   | Address | All Resets                              |

| Timers    |            |                                         | INT1TMRH  | 15E     | 00000000000000000                       | MSI1MBX3D  | 1E0     | 000000000000000000                      |

| T1CON     | 100        | 0-000000-00-00-                         | INT1HLDL  | 160     | 00000000000000000                       | MSI1MBX4D  | 1E2     | 000000000000000000                      |

| TMR1      | 104        | 000000000000000000000000000000000000000 | INT1HLDH  | 162     | 000000000000000000                      | MSI1MBX5D  | 1E4     | 000000000000000000                      |

| PR1       | 108        | 000000000000000000000000000000000000000 | INDX1CNTL | 164     | 000000000000000000                      | MSI1MBX6D  | 1E6     | 000000000000000000                      |

| QEI       |            |                                         | INDX1CNTH | 166     | 000000000000000000                      | MSI1MBX7D  | 1E8     | 000000000000000000                      |

| QEI1CON   | 140        | 000000000000000000000000000000000000000 | INDX1HLDL | 168     | 000000000000000000                      | MSI1MBX8D  | 1EA     | 000000000000000000                      |

| QEI1IOCL  | 144        | 000000000000xxxx                        | INDX1HLDH | 16A     | 000000000000000000                      | MSI1MBX9D  | 1EC     | 000000000000000000                      |

| QEI1IOCH  | 146        | 0                                       | QEI1GECL  | 16C     | 000000000000000000                      | MSI1MBX10D | 1EE     | 000000000000000000                      |

| QEI1STAT  | 148        | 000000000000000                         | QEI1GECH  | 16E     | 00000000000000000                       | MSI1MBX11D | 1F0     | 000000000000000000                      |

| POS1CNTL  | 14C        | 000000000000000000                      | QEI1LECL  | 170     | 00000000000000000                       | MSI1MBX12D | 1F2     | 000000000000000000                      |

| POS1CNTH  | 14E        | 000000000000000000000000000000000000000 | QEI1LECH  | 172     | 000000000000000000                      | MSI1MBX13D | 1F4     | 000000000000000000                      |

| POS1HLDL  | 150        | 000000000000000000000000000000000000000 | MSI1CON   | 1D2     | 0xx0000000000                           | MSI1MBX14D | 1F6     | 000000000000000000000000000000000000000 |

| POS1HLDH  | 152        | 000000000000000000000000000000000000000 | MSI1STAT  | 1D4     | 000000000000000000000000000000000000000 | MSI1MBX15D | 1F8     | 000000000000000000000000000000000000000 |

| VEL1CNTL  | 154        | 000000000000000000000000000000000000000 | MSI1KEY   | 1D6     | 00000000                                | MSI1FIFOCS | 1FA     | 0000000000                              |

| VEL1CNTH  | 156        | 000000000000000000000000000000000000000 | MSI1MBXS  | 1D8     | 00000000                                | MRSWFDATA  | 1FC     | 000000000000000000000000000000000000000 |

| VEL1HLDL  | 158        | 000000000000000000                      | MSI1MBX0D | 1DA     | 000000000000000000                      | MWSRFDATA  | 1FE     | 000000000000000000                      |

| VEL1HLDH  | 15A        | 000000000000000000                      | MSI1MBX1D | 1DC     | 000000000000000000                      |            |         |                                         |

| INT1TMRL  | 15C        | 000000000000000000                      | MSI1MBX2D | 1DE     | 000000000000000000                      |            |         |                                         |

TABLE 3-5: MASTER SFR BLOCK 100h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address and Reset values are in hexadecimal and binary, respectively.

# **REGISTER 3-15: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

#### 3.5 Master Interrupt Controller

Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33CH128MP508 family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33CH128MP508 family CPU.

The interrupt controller has the following features:

- Six Processor Exceptions and Software Traps

- · Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- · Fixed Interrupt Entry and Return Latencies

- Alternate Interrupt Vector Table (AIVT) for Debug Support

#### 3.5.1 INTERRUPT VECTOR TABLE

The dsPIC33CH128MP508 family Interrupt Vector Table (IVT), shown in Figure 3-17, resides in program memory, starting at location, 000004h. The IVT contains six non-maskable trap vectors and up to 246 sources of interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 3.5.1.1 Alternate Interrupt Vector Table

The Alternate Interrupt Vector Table (AIVT), shown in Figure 3-18, is available only when the Boot Segment (BS) is defined and the AIVT has been enabled. To enable the Alternate Interrupt Vector Table, the Configuration bit, AIVTDIS in the FSEC register, must be programmed and the AIVTEN bit must be set (INTCON2<8> = 1). When the AIVT is enabled, all interrupt and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment, defined by BSLIM<12:0>. The second half of the page is no longer usable space. The Boot Segment must be at least two pages to enable the AIVT.

**Note:** Although the Boot Segment must be enabled in order to enable the AIVT, application code does not need to be present inside of the Boot Segment. The AIVT (and IVT) will inherit the Boot Segment code protection.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

#### 3.5.2 RESET SEQUENCE

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33CH128MP508 family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

## TABLE 3-26: MASTER INTERRUPT PRIORITY REGISTERS

| Register | Address | Bit 15 | Bit14      | Bit 13     | Bit 12     | Bit 11 | Bit 10     | Bit 9      | Bit 8      | Bit 7 | Bit 6      | Bit 5      | Bit 4      | Bit 3 | Bit 2      | Bit 1      | Bit 0     |

|----------|---------|--------|------------|------------|------------|--------|------------|------------|------------|-------|------------|------------|------------|-------|------------|------------|-----------|

| IPC0     | 840h    | _      | CNBIP2     | CNBIP1     | CNBIP0     | _      | CNAIP2     | CNAIP1     | CNAIP0     | _     | T1IP2      | T1IP1      | T1IP0      | _     | INT0IP2    | INT0IP1    | INT0IP0   |

| IPC1     | 842h    | _      | CCT1IP2    | CCT1IP1    | CCT1IP0    | _      | CCP1IP2    | CCP1IP1    | CCP1IP0    | _     | _          | _          | _          | _     | DMA0IP2    | DMA0IP1    | DMA0IP0   |

| IPC2     | 844h    | _      | U1RXIP2    | U1RXIP1    | U1RXIP0    | _      | SPI1TXIP2  | SPI1TXIP1  | SPI1TXIP0  | _     | SPI1RXIP2  | SPI1RXIP1  | SPI1RXIP0  | _     | DMA1IP2    | DMA1IP1    | DMA1IP0   |

| IPC3     | 846h    | _      | INT1IP2    | INT1IP1    | INT1IP0    | _      | NVMIP2     | NVMIP1     | NVMIP0     | _     | ECCSBEIP2  | ECCSBEIP1  | ECCSBEIP0  | _     | U1TXIP2    | U1TXIP1    | U1TXIP0   |

| IPC4     | 848h    | _      | CNCIP2     | CNCIP1     | CNCIP0     |        | DMA2IP2    | DMA2IP1    | DMA2IP0    | —     | MI2C1IP2   | MI2C1IP1   | MI2C1IP0   | —     | SI2C1IP2   | SI2C1IP1   | SI2C1IP0  |

| IPC5     | 84Ah    | _      | CCP2IP2    | CCP2IP1    | CCP2IP0    |        | DMA4IP2    | DMA4IP1    | DMA4IP0    | —     | DMA3IP2    | DMA3IP1    | DMA3IP20   | —     | INT2IP2    | INT2IP1    | INT2IP0   |

| IPC6     | 84Ch    | _      | U2RXIP2    | U2RXIP1    | U2RXIP0    | _      | INT3IP2    | INT3IP1    | INT3IP0    | _     | CAN1IP2    | CAN1IP1    | CAN1IP0    | _     | CCT2IP2    | CCT2IP1    | CCT2IP0   |

| IPC7     | 84Eh    | _      | C1RXIP2    | C1RXIP1    | C1RXIP0    | _      | SPI2TXIP2  | SPI2TXIP1  | SPI2TXIP0  | _     | SPI2RXIP2  | SPI2RXIP1  | SPI2RXIP0  | _     | U2TXIP2    | U2TXIP1    | U2TXIP0   |

| IPC8     | 850h    | _      | CCP3IP2    | CCP3IP1    | CCP3IP0    | —      | DMA5IP2    | DMA5IP1    | DMA5IP0    | _     | _          | _          | _          | _     | _          | _          | _         |

| IPC9     | 852h    | _      | _          |            | _          |        | MI2C2IP2   | MI2C2IP1   | MI2C2IP0   | —     | SI2C2IP2   | SI2C2IP1   | SI2C2IP0   | _     | CCT3IP2    | CCT3IP1    | CCT3IP0   |

| IPC10    | 854h    | _      | CCP5IP2    | CCP5IP1    | CCP5IP0    |        | _          |            | _          | —     | CCT4IP2    | CCT4IP1    | CCT4IP0    | _     | CCP4IP2    | CCP4IP1    | CCP4IP0   |

| IPC11    | 856h    | _      | CCT6IP2    | CCT6IP1    | CCT6IP0    |        | CCP6IP2    | CCP6IP1    | CCP6IP0    | —     | DMTIP2     | DMTIP1     | DMTIP0     | _     | CCT5IP2    | CCT5IP1    | CCT5IP0   |

| IPC12    | 858h    | _      | CRCIP2     | CRCIP1     | CRCIP0     |        | U2EIP2     | U2EIP1     | U2EIP0     | —     | U1EIP2     | U1EIP1     | U1EIP0     | _     | QEI1IP2    | QEI1IP1    | QEI1IP0   |

| IPC13    | 85Ah    | _      | —          |            | _          |        |            |            | _          | —     | —          |            | —          | _     | C1TXIP2    | C1TXIP1    | C1TXIP0   |

| IPC14    | 85Ch    | _      | —          |            | _          |        |            |            | _          | —     | —          |            | —          | _     |            |            |           |

| IPC15    | 85Eh    | _      | PTGSTEPIP2 | PTGSTEPIP1 | PTGSTEPIP0 |        | JTAGIP2    | JTAGIP1    | JTAGIP0    | —     | ICDIP2     | ICDIP1     | ICDIP0     | _     | _          |            | —         |

| IPC16    | 860h    | _      | PWM1IP2    | PWM1IP1    | PWM1IP0    |        |            |            | _          | —     | I2C2BCIP2  | I2C2BCIP1  | I2C2BCIP0  | _     | I2C1BCIP2  | I2C1BCIP1  | I2C1BCIP  |

| IPC17    | 862h    |        | —          | _          | —          | _      | PWM4IP2    | PWM4IP1    | PWM4IP0    | —     | PWM3IP2    | PWM3IP1    | PWM3IP0    | _     | PWM2IP2    | PWM2IP1    | PWM2IP0   |

| IPC18    | 864h    |        | CNDIP2     | CNDIP1     | CNDIP0     | _      | _          | —          | —          | —     | —          | —          | —          | _     | —          | _          | _         |

| IPC19    | 866h    | _      | _          | _          | —          | _      | _          | _          | _          | _     | CMP1IP2    | CMP1IP1    | CMP1IP0    | _     | CNEIP2     | CNEIP1     | CNEIP0    |

| IPC20    | 868h    | —      | PTG1IP2    | PTG1IP1    | PTG1IP0    | _      | PTG0IP2    | PTG0IP1    | PTG0IP0    | _     | PTGWDTIP2  | PTGWDTIP1  | PTGWDTIP0  |       | —          | _          | —         |

| IPC21    | 86Ah    | _      | SENT1EIP2  | SENT1EIP1  | SENT1EIP0  | _      | SENT1IP2   | SENT1IP1   | SENT1IP0   | _     | PTG3IP2    | PTG3IP1    | PTG3IP0    | _     | PTG2IP2    | PTG2IP1    | PTG2IP0   |

| IPC22    | 86Ch    |        | ADCAN0IP2  | ADCAN0IP1  | ADCAN0IP0  | _      | ADCIP2     | ADCIP1     | ADCIP0     | —     | SENT2EIP2  | SENT2EIP1  | SENT2EIP0  | _     | SENT2IP2   | SENT2IP1   | SENT2IP0  |

| IPC23    | 86Eh    | _      | ADCAN4IP2  | ADCAN4IP1  | ADCAN4IP0  | _      | ADCAN3IP2  | ADCAN3IP1  | ADCAN3IP0  | _     | ADCAN2IP2  | ADCAN2IP1  | ADCAN2IP0  | _     | ADCAN1IP2  | ADCAN1IP1  | ADCAN1IF  |

| IPC24    | 870h    | —      | ADCAN8IP2  | ADCAN8IP1  | ADCAN8IP0  | _      | ADCAN7IP2  | ADCAN7IP1  | ADCAN7IP0  | _     | ADCAN6IP2  | ADCAN6IP1  | ADCAN6IP0  |       | ADCAN5IP2  | ADCAN5IP1  | ADCAN5IF  |

| IPC25    | 872h    | _      | ADCAN12IP2 | ADCAN12IP1 | ADCAN12IP0 | _      | ADCAN11IP2 | ADCAN11IP1 | ADCAN11IP0 | _     | ADCAN10IP2 | ADCAN10IP1 | ADCAN10IP0 | _     | ADCAN9IP2  | ADCAN9IP1  | ADCAN9IF  |

| IPC26    | 874h    | —      | ADCAN16IP2 | ADCAN16IP2 | ADCAN16IP2 | _      | ADCAN15IP2 | ADCAN15IP1 | ADCAN15IP0 | _     | ADCAN14IP2 | ADCAN14IP1 | ADCAN14IP0 |       | ADCAN13IP2 | ADCAN13IP1 | ADCAN13I  |

| IPC27    | 876h    | —      | ADCAN20IP2 | ADCAN20IP1 | ADCAN20IP0 | _      | ADCAN19IP2 | ADCAN19IP1 | ADCAN19IP0 | _     | ADCAN18IP2 | ADCAN18IP1 | ADCAN18IP0 |       | ADCAN17IP2 | ADCAN17IP1 | ADCAN17I  |

| IPC28    | 878h    | —      | ADFLTIP2   | ADFLTIP1   | ADFLTIP0   | _      | _          | _          | —          | _     | _          | _          | _          |       | —          | _          |           |

| IPC29    | 87Ah    | —      | ADCMP3IP2  | ADCMP3IP1  | ADCMP3IP0  | _      | ADCMP2IP2  | ADCMP2IP1  | ADCMP2IP0  | _     | ADCMP1IP2  | ADCMP1IP1  | ADCMP1IP0  |       | ADCMP0IP2  | ADCMP0IP1  | ADCMP0IF  |

| IPC30    | 87Ch    | —      | ADFLTR3IP2 | ADFLTR3IP1 | ADFLTR3IP0 | —      | ADFLTR2IP2 | ADFLTR2IP1 | ADFLTR2IP0 | _     | ADFLTR1IP2 | ADFLTR1IP1 | ADFLTR1IP0 | _     | ADFLTR0IP2 | ADFLTR0IP1 | ADFLTR0IF |

| IPC31    | 87Eh    | —      | SPI2GIP0   | SPI2GIP1   | SPI2GIP0   | —      | SPI1GIP2   | SPI1GIP1   | SPI1GIP0   | _     | CLC2PIP2   | CLC2PIP1   | CLC2PIP0   | _     | CLC1PIP2   | CLC1PIP1   | CLC1PIP   |

| IPC32    | 880h    | —      | MSIBIP2    | MSIBIP1    | MSIBIP0    | —      | MSIAIP2    | MSIAIP1    | MSIAIP0    | _     | MSIS1IP2   | MSIS1IP1   | MSIS1IP0   | _     | _          | _          | _         |

| IPC33    | 882h    | -      | MSIFIP2    | MSIFIP1    | MSIFIP0    |        | MSIEIP2    | MSIEIP1    | MSIEIP0    | _     | MSIDIP2    | MSIDIP1    | MSIDIP0    | —     | MSICIP2    | MSICIP1    | MSICIP0   |

| IPC34    | 884h    | _      | MSIWFEIP2  | MSIWFEIP1  | MSIWFEIP0  | _      | MSIDTIP2   | MSIDTIP1   | MSIDTIP0   | _     | MSIHIP2    | MSIHIP1    | MSIHIP0    | _     | MSIGIP2    | MSIGIP1    | MSIGIP0   |

Legend: — = Unimplemented.

# dsPIC33CH128MP508 FAMILY

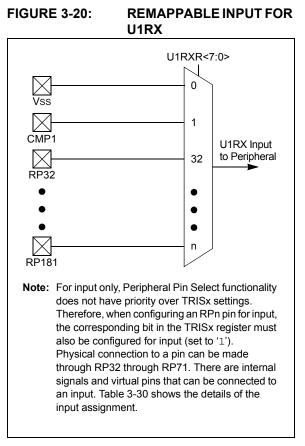

Example 3-2 provides a configuration for bidirectional communication with flow control using UART1. The following input and output functions are used:

- Input Functions: U1RX, U1CTS

- Output Functions: U1TX, U1RTS

#### EXAMPLE 3-2: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS

| //                                             |

|------------------------------------------------|

| * * * * * * * * * * * * * * * * * * * *        |

| // Unlock Registers                            |

| //*************************************        |

| <pre>builtin_write_RPCON(0x0000);</pre>        |

| //**************                               |

| // Configure Input Functions (See Table 3-31)  |

| // Assign UlRx To Pin RP35                     |

| / / **************                             |

| _U1RXR = 35;                                   |

| // Assign UlCTS To Pin RP36                    |

| / / *************                              |

| _U1CTSR = 36;                                  |

| //*************************************        |

| // Configure Output Functions (See Table 3-33) |

| / / ***********************************        |

| // Assign UlTx To Pin RP37                     |

| / / *************                              |

| _RP37 = 1;                                     |

| / / ***********                                |

| // Assign UlRTS To Pin RP38                    |

| / / *************                              |

| _RP38 = 2;                                     |

| //*************************************        |

| // Lock Registers                              |

| / / ***********************************        |

| builtin_write_RPCON(0x0800);                   |

|                                                |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| OCFBR7 | OCFBR6 | OCFBR5 | OCFBR4 | OCFBR3 | OCFBR2 | OCFBR1 | OCFBR0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

#### REGISTER 3-47: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| OCFAR7 | OCFAR6 | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **OCFBR<7:0>:** Assign SCCP Fault B (OCFB) Input to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **OCFAR<7:0>:** Assign SCCP Fault A (OCFA) Input to the Corresponding RPn Pin bits See Table 3-30.

#### REGISTER 3-48: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCI9R7 | PCI9R6 | PCI9R5 | PCI9R4 | PCI9R3 | PCI9R2 | PCI9R1 | PCI9R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCI8R7 | PCI8R6 | PCI8R5 | PCI8R4 | PCI8R3 | PCI8R2 | PCI8R1 | PCI8R0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:                                                              |                  |                      |                    |  |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-8 **PCI9R<7:0>:** Assign PWM Input 9 (PCI9) to the Corresponding RPn Pin bits See Table 3-30.

bit 7-0 **PCI8R<7:0>:** Assign PWM Input 8 (PCI8) to the Corresponding RPn Pin bits See Table 3-30.

#### REGISTER 3-135: C1FIFOSTAX: CAN FIFO STATUS REGISTER x (x = 1 TO 7) (CONTINUED)

| bit 2 | <b>TFERFFIF:</b> Transmit/Receive FIFO Empty/Full Interrupt Flag bit<br><u>TXEN = 1 (FIFO configured as a transmit FIFO):</u><br>Transmit FIFO Empty Interrupt Flag<br>1 = FIFO is empty<br>0 = FIFO is not empty, at least one message is queued to be transmitted<br><u>TXEN = 0 (FIFO configured as a receive FIFO):</u><br>Receive FIFO Full Interrupt Flag<br>1 = FIFO is full<br>0 = FIFO is not full                                                                                                       |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>TFHRFHIF:</b> Transmit/Receive FIFO Half Empty/Half Full Interrupt Flag bit $\underline{TXEN = 1}$ (FIFO configured as a transmit FIFO):<br>Transmit FIFO Half Empty Interrupt Flag $1 = FIFO$ is $\leq$ half full $0 = FIFO$ is $>$ half full $\underline{TXEN = 0}$ (FIFO configured as a receive FIFO):<br>Receive FIFO Half Full Interrupt Flag $1 = FIFO$ is $\geq$ half full $0 = FIFO$ is $\geq$ half full $0 = FIFO$ is $\geq$ half full $0 = FIFO$ is $\leq$ half full $0 = FIFO$ is $\leq$ half full |

| bit 0 | <b>TFNRFNIF:</b> Transmit/Receive FIFO Not Full/Not Empty Interrupt Flag bit<br><u>TXEN = 1 (FIFO configured as a transmit FIFO):</u><br>Transmit FIFO Not Full Interrupt Flag<br>1 = FIFO is not full<br>0 = FIFO is full<br><u>TXEN = 0 (FIFO configured as a receive FIFO):</u><br>Receive FIFO Not Empty Interrupt Flag<br>1 = FIFO is not empty, has at least one message<br>0 = FIFO is empty                                                                                                               |

- **Note 1:** FIFOCI<4:0> gives a zero-indexed value to the message in the FIFO. If the FIFO is four messages deep (FSIZE<4:0> = 3), FIFOCIx will take on a value of 0 to 3, depending on the state of the FIFO.

- 2: These bits are updated when a message completes (or aborts) or when the FIFO is reset.

- **3:** This bit is reset on any read of this register or when the TXQ is reset. The bits are cleared when TXREQ is set or using an SPI write.

## REGISTER 3-189: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0                                                                      | R/W-0 | R/W-0  | R/W-0     | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------|----------------------------------------------------------------------------|-------|--------|-----------|-------|-------|-------|--|

|                 |                                                                            |       | PTGT1L | -IM<15:8> |       |       |       |  |

| bit 15          |                                                                            |       |        |           |       |       | bit 8 |  |

|                 |                                                                            |       |        |           |       |       |       |  |

| R/W-0           | R/W-0                                                                      | R/W-0 | R/W-0  | R/W-0     | R/W-0 | R/W-0 | R/W-0 |  |

|                 |                                                                            |       | PTGT1  | LIM<7:0>  |       |       |       |  |

| bit 7           |                                                                            |       |        |           |       |       | bit 0 |  |

|                 |                                                                            |       |        |           |       |       |       |  |

| Legend:         |                                                                            |       |        |           |       |       |       |  |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |       |        |           |       |       |       |  |

| -n = Value at F | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |        |           |       |       |       |  |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits General Purpose Timer1 Limit register.

Note 1: These bits are read-only when the module is executing Step commands.

#### REGISTER 3-190: PTGSDLIM: PTG STEP DELAY LIMIT REGISTER<sup>(1)</sup>

| R/W-0        | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------------|-------|------------------|--------|------------------------------------|-------|-------|-------|--|--|

|              |       |                  | PTGSDI | _IM<15:8>                          |       |       |       |  |  |

| bit 15       |       |                  |        |                                    |       |       | bit 8 |  |  |

|              |       |                  |        |                                    |       |       |       |  |  |

| R/W-0        | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|              |       |                  | PTGSD  | LIM<7:0>                           |       |       |       |  |  |

| bit 7        |       |                  |        |                                    |       |       | bit 0 |  |  |

|              |       |                  |        |                                    |       |       |       |  |  |

| Legend:      |       |                  |        |                                    |       |       |       |  |  |

| R = Readable | bit   | W = Writable bit |        | U = Unimplemented bit, read as '0' |       |       |       |  |  |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits This register holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

'0' = Bit is cleared

Note 1: These bits are read-only when the module is executing Step commands.

'1' = Bit is set

-n = Value at POR

x = Bit is unknown

# **REGISTER 4-15: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI15R7 | PCI15R6 | PCI15R5 | PCI15R4 | PCI15R3 | PCI15R2 | PCI15R1 | PCI15R0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

#### REGISTER 4-55: RPINR43: PERIPHERAL PIN SELECT INPUT REGISTER 43

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI14R7 | PCI14R6 | PCI14R5 | PCI14R4 | PCI14R3 | PCI14R2 | PCI14R1 | PCI14R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **PCI15R<7:0>:** Assign PWM Input 15 (S1PCI15) to the Corresponding S1RPn Pin bits See Table 4-27.

bit 7-0 PCI14R<7:0>: Assign PWM Input 14 (S1PCI14) to the Corresponding S1RPn Pin bits See Table 4-27.

#### REGISTER 4-56: RPINR44: PERIPHERAL PIN SELECT INPUT REGISTER 44

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI16R7 | PCI16R6 | PCI16R5 | PCI16R4 | PCI16R3 | PCI16R2 | PCI16R1 | PCI16R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **PCI16<7:0>:** Assign PWM Input 16 (S1PCI16) to the Corresponding S1RPn Pin bits See Table 4-27.

#### 4.7 High-Speed, 12-Bit Analog-to-Digital Converter (Slave ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33CH128MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (DS70005213) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: This section describes the Slave ADC.

dsPIC33CH128MP508S1 devices have a high-speed, 12-bit Analog-to-Digital Converter (ADC) that features a low conversion latency, high resolution and oversampling capabilities to improve performance in AC/DC, DC/DC power converters. The Slave implements the ADC with three SAR cores, two dedicated and one shared.

#### 4.7.1 SLAVE ADC FEATURES OVERVIEW

The High-Speed, 12-Bit Multiple SARs Analog-to-Digital Converter (ADC) includes the following features:

- Three ADC Cores: Two Dedicated Cores and One Shared (common) Core

- User-Configurable Resolution of up to 12 Bits for each Core

- Up to 3.5 Msps Conversion Rate per Channel at 12-Bit Resolution

- Low-Latency Conversion

- Up to 20 Analog Input Channels, with a Separate 16-Bit Conversion Result Register for each Input

- Conversion Result can be Formatted as Unsigned or Signed Data, on a per Channel Basis, for All Channels

- Simultaneous Sampling of up to Three Analog

Inputs

- · Channel Scan Capability

- Multiple Conversion Trigger Options for each Core, including:

- PWM triggers from Master and Slave CPU cores

- SCCP modules triggers

- CLC modules triggers

- External pin trigger event (ADTRG31)

- Software trigger

- Four Integrated Digital Comparators with Dedicated Interrupts:

- Multiple comparison options

- Assignable to specific analog inputs

- Four Oversampling Filters with Dedicated Interrupts:

- Provide increased resolution

- Assignable to a specific analog input

- CVD Hardware for Capacitive Touch and Capacitance Measurement Applications

The module consists of three independent SAR ADC cores. Simplified block diagrams of the Multiple SARs 12-Bit ADC are shown in Figure 4-20 and Figure 4-21.

The analog inputs (channels) are connected through multiplexers and switches to the Sample-and-Hold (S&H) circuit of each ADC core. The core uses the channel information (the output format, the Measurement mode and the input number) to process the analog sample. When conversion is complete, the result is stored in the result buffer for the specific analog input, and passed to the digital filter and digital comparator if they were configured to use data from this particular channel.

The ADC module can sample up to three inputs at a time (two inputs from the dedicated SAR cores and one from the shared SAR core). If multiple ADC inputs request conversion on the shared core, the module will convert them in a sequential manner, starting with the lowest order input.

The ADC provides each analog input the ability to specify its own trigger source. This capability allows the ADC to sample and convert analog inputs that are associated with PWM generators operating on independent time bases.

| HSC/R-0                                            | HSC/R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0              | r-0      | r-0               | r-0                                    | R/W-0       | R/W-0    |  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|-------------------|----------------------------------------|-------------|----------|--|--|

| REFRDY                                             | REFERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                | r        | r                 | r                                      | SHRSAMC9    | SHRSAMC8 |  |  |

| bit 15                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |          | •                 |                                        | •           | bit 8    |  |  |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |          |                   |                                        |             |          |  |  |

| R/W-0                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0            | R/W-0    | R/W-0             | R/W-0                                  | R/W-0       | R/W-0    |  |  |

| SHRSAMC7                                           | SHRSAMC6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SHRSAMC5         | SHRSAMC4 | SHRSAMC3          | SHRSAMC2                               | SHRSAMC1    | SHRSAMC0 |  |  |

| bit 7 bit 0                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |          |                   |                                        |             |          |  |  |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |          |                   |                                        |             |          |  |  |

| Legend:                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | r = Reserved I   | oit      | U = Unimplem      | ented bit, read                        | as '0'      |          |  |  |

| R = Readable                                       | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable b   | oit      | HSC = Hardwa      | are Settable/Cl                        | earable bit |          |  |  |

| -n = Value at F                                    | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | '1' = Bit is set |          | '0' = Bit is clea | )' = Bit is cleared x = Bit is unknown |             |          |  |  |

| bit 15<br>bit 14<br>bit 13<br>bit 12-10<br>bit 9-0 | t POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         REFRDY: Band Gap and Reference Voltage Ready Flag bit       1 = Band gap is ready       0 = Band gap is not ready         REFERR: Band Gap or Reference Voltage Error Flag bit       1 = Band gap was removed after the ADC module was enabled (ADON = 1)         0 = No band gap error was detected       Unimplemented: Read as '0'         Reserved: Maintain as '0'       SHRSAMC<9:0>: Shared ADC Core Sample Time Selection bits         These bits specify the number of shared ADC Core Clock Periods (TADCORE) for the shared ADC c sample time.         1111111111       = 1025 TADCORE |                  |          |                   |                                        |             |          |  |  |

#### REGISTER 4-86: ADCON2H: ADC CONTROL REGISTER 2 HIGH

#### REGISTER 6-2: CLKDIV: CLOCK DIVIDER REGISTER (MASTER) (CONTINUED)

- bit 3-0 **PLLPRE<3:0>:** PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler)<sup>(4)</sup> 11111 = Reserved

- 1001 = Reserved 1000 = Input divided by 8 0111 = Input divided by 7 0110 = Input divided by 6 0101 = Input divided by 5 0100 = Input divided by 4 0011 = Input divided by 3 0010 = Input divided by 2 0001 = Input divided by 1 (power-on default selection) 0000 = Reserved

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 2: This bit is cleared when the ROI bit is set and an interrupt occurs.

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

- 4: PLLPRE<3:0> may be updated while the PLL is operating, but the VCO may overshoot.

| U-0           | U-0         | U-0                                                         | U-0        | U-0               | U-0             | U-0             | U-0    |  |  |  |  |

|---------------|-------------|-------------------------------------------------------------|------------|-------------------|-----------------|-----------------|--------|--|--|--|--|

| _             |             | —                                                           | _          |                   | _               | —               | —      |  |  |  |  |

| bit 15        |             |                                                             |            |                   |                 |                 | bit 8  |  |  |  |  |

|               |             |                                                             |            |                   |                 |                 |        |  |  |  |  |

| R/W-0         | R/W-0       | R/W-0                                                       | R/W-0      | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

| CCP8MD        | CCP7MD      | CCP6MD                                                      | CCP5MD     | CCP4MD            | CCP3MD          | CCP2MD          | CCP1MD |  |  |  |  |

| bit 7         |             |                                                             |            |                   |                 |                 | bit 0  |  |  |  |  |

| Legend:       |             |                                                             |            |                   |                 |                 |        |  |  |  |  |

| R = Readab    | le bit      | W = Writable I                                              | oit        | U = Unimplem      | ented bit, read | l as '0'        |        |  |  |  |  |

| -n = Value a  |             | '1' = Bit is set                                            |            | '0' = Bit is clea |                 | x = Bit is unkr | iown   |  |  |  |  |

|               |             |                                                             |            |                   |                 |                 |        |  |  |  |  |

| bit 15-8      | Unimplement | ted: Read as 'd                                             | )'         |                   |                 |                 |        |  |  |  |  |

| bit 7         | CCP8MD: SC  | CP8 Module D                                                | isable bit |                   |                 |                 |        |  |  |  |  |

|               |             | odule is disable                                            |            |                   |                 |                 |        |  |  |  |  |

|               |             | odule is enable                                             |            |                   |                 |                 |        |  |  |  |  |

| bit 6         |             | CP7 Module D                                                |            |                   |                 |                 |        |  |  |  |  |

|               |             | odule is disable                                            |            |                   |                 |                 |        |  |  |  |  |

| bit 5         |             | CP6 Module D                                                |            |                   |                 |                 |        |  |  |  |  |

|               |             | odule is disable                                            |            |                   |                 |                 |        |  |  |  |  |

|               | 0 = SCCP6 m | odule is enable                                             | ed         |                   |                 |                 |        |  |  |  |  |

| bit 4         | CCP5MD: SC  | CP5 Module D                                                | isable bit |                   |                 |                 |        |  |  |  |  |

|               |             | 25 module is disabled                                       |            |                   |                 |                 |        |  |  |  |  |

| <b>h</b> :+ 0 |             | odule is enable                                             |            |                   |                 |                 |        |  |  |  |  |

| bit 3         |             | CP4 Module D                                                |            |                   |                 |                 |        |  |  |  |  |

|               |             | 1 = SCCP4 module is disabled<br>0 = SCCP4 module is enabled |            |                   |                 |                 |        |  |  |  |  |

| bit 2         | CCP3MD: SC  | CP3 Module D                                                | isable bit |                   |                 |                 |        |  |  |  |  |

|               | 1 = SCCP3 m | odule is disable                                            | ed         |                   |                 |                 |        |  |  |  |  |

|               | 0 = SCCP3 m | CP3 module is enabled                                       |            |                   |                 |                 |        |  |  |  |  |

| bit 1         |             | CP2 Module D                                                |            |                   |                 |                 |        |  |  |  |  |

|               |             | odule is disable                                            |            |                   |                 |                 |        |  |  |  |  |

| bit 0         |             | CP1 Module D                                                |            |                   |                 |                 |        |  |  |  |  |

|               |             | odule is disable                                            |            |                   |                 |                 |        |  |  |  |  |

|               |             |                                                             | ~ ~        |                   |                 |                 |        |  |  |  |  |

#### REGISTER 7-3: PMD2: MASTER PERIPHERAL MODULE DISABLE 2 CONTROL REGISTER HIGH

### **REGISTER 9-10: PWMEVTy: PWM EVENT OUTPUT CONTROL REGISTER y<sup>(5)</sup> (CONTINUED)**

bit 2-0 EVTyPGS<2:0>: PWM Event Source Selection bits<sup>(2)</sup>

- 111 = PG8 110 = PG7 101 = PG6 100 = PG5 011 = PG4 010 = PG3 001 = PG2 000 = PG1

- **Note 1:** The event signal is stretched using the peripheral clock because different PGs may be operating from different clock sources. The leading edge of the event pulse is produced in the clock domain of the PWM Generator. The trailing edge of the stretched event pulse is produced in the peripheral clock domain.

- 2: No event will be produced if the selected PWM Generator is not present.

- 3: This is the PWM Generator output signal prior to output mode logic and any output override logic.

- 4: This signal should be the PGx\_clk domain signal prior to any synchronization into the system clock domain.

- **5:** 'y' denotes a common instance (A-F).

| R/W-0        | R/W-0                                                                                                                                                                                               | R/W-0                                            | R/W-0           | R/W-0                                     | R/W-0                    | R/W-0                    | R/W-0                    |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|-------------------------------------------|--------------------------|--------------------------|--------------------------|--|--|--|--|

| ADTR1PS4     | ADTR1PS3                                                                                                                                                                                            | ADTR1PS2                                         | ADTR1PS1        | ADTR1PS0                                  | ADTR1EN3                 | ADTR1EN2                 | ADTR1EN1                 |  |  |  |  |

| bit 15       |                                                                                                                                                                                                     |                                                  |                 |                                           |                          |                          | bit 8                    |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

| U-0          | U-0                                                                                                                                                                                                 | U-0                                              | R/W-0           | R/W-0                                     | R/W-0                    | R/W-0                    | R/W-0                    |  |  |  |  |

| —            | _                                                                                                                                                                                                   | _                                                | UPDTRG1         | UPDTRG0                                   | PGTRGSEL2 <sup>(1)</sup> | PGTRGSEL1 <sup>(1)</sup> | PGTRGSEL0 <sup>(1)</sup> |  |  |  |  |

| bit 7        |                                                                                                                                                                                                     |                                                  |                 |                                           |                          |                          | bit 0                    |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

| Legend:      |                                                                                                                                                                                                     |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

| R = Readal   |                                                                                                                                                                                                     | W = Writable                                     | bit             |                                           | mented bit, read         | as '0'                   |                          |  |  |  |  |

| -n = Value a | at POR                                                                                                                                                                                              | '1' = Bit is se                                  | t               | '0' = Bit is cle                          | eared                    | x = Bit is unknow        | n                        |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

| bit 15-11    |                                                                                                                                                                                                     |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

|              | 11111 <b>= 1</b> :3                                                                                                                                                                                 | 2                                                |                 |                                           |                          |                          |                          |  |  |  |  |

|              | 00010 <b>= 1</b> :3                                                                                                                                                                                 |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

|              | 00001 = 1:2                                                                                                                                                                                         |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

|              | 00000 = 1:1                                                                                                                                                                                         |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

| bit 10       |                                                                                                                                                                                                     |                                                  |                 |                                           | ompare Event En          |                          |                          |  |  |  |  |

|              | <ul> <li>1 = PGxTRIGC register compare event is enabled as trigger source for ADC Trigger 1</li> <li>0 = PGxTRIGC register compare event is disabled as trigger source for ADC Trigger 1</li> </ul> |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

| bit 9        |                                                                                                                                                                                                     | -                                                | -               |                                           | mpare Event En           |                          |                          |  |  |  |  |

| bit 0        |                                                                                                                                                                                                     |                                                  |                 |                                           | s trigger source for     |                          |                          |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                  |                 |                                           |                          | or ADC Trigger 1         |                          |  |  |  |  |

| bit 8        | ADTR1EN1                                                                                                                                                                                            | ADC Trigger                                      | 1 Source is F   | PGxTRIGA Co                               | mpare Event En           | able bit                 |                          |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                  |                 |                                           | s trigger source for     |                          |                          |  |  |  |  |

|              |                                                                                                                                                                                                     | -                                                | -               | t is disabled a                           | s trigger source f       | or ADC Trigger 1         |                          |  |  |  |  |

| bit 7-5      | -                                                                                                                                                                                                   | nted: Read a                                     |                 |                                           |                          |                          |                          |  |  |  |  |

| bit 4-3      |                                                                                                                                                                                                     | :0>: Update T                                    |                 |                                           |                          |                          |                          |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                  |                 |                                           | sets the UPDAT           |                          |                          |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                  |                 |                                           | s the UPDATE bi          |                          |                          |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                  |                 | GxSTAT<4>)                                |                          |                          |                          |  |  |  |  |

|              | PGTRGSEL<2:0>: PWM Generator Trigger Output Selection bits <sup>(1)</sup>                                                                                                                           |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

| bit 2-0      | TOINCOLL                                                                                                                                                                                            | 111 = Reserved                                   |                 |                                           |                          |                          |                          |  |  |  |  |

| bit 2-0      | 111 = Rese                                                                                                                                                                                          |                                                  |                 |                                           |                          |                          |                          |  |  |  |  |

| bit 2-0      | 111 = Rese<br>110 = Rese                                                                                                                                                                            | rved                                             |                 |                                           |                          |                          |                          |  |  |  |  |

| bit 2-0      | 111 = Rese                                                                                                                                                                                          | rved<br>rved                                     |                 |                                           |                          |                          |                          |  |  |  |  |

| bit 2-0      | 111 = Rese<br>110 = Rese<br>101 = Rese<br>100 = Rese<br>011 = PGxT                                                                                                                                  | rved<br>rved<br>rved<br>RIGC compa               |                 | e PWM Gener                               |                          |                          |                          |  |  |  |  |

| bit 2-0      | 111 = Reset<br>110 = Reset<br>101 = Reset<br>100 = Reset<br>011 = PGxT<br>010 = PGxT                                                                                                                | rved<br>rved<br>rved<br>RIGC compa<br>RIGB compa | re event is the | e PWM Gener<br>e PWM Gener<br>e PWM Gener | ator trigger             |                          |                          |  |  |  |  |

#### REGISTER 9-19: PGxEVTL: PWM GENERATOR x EVENT REGISTER LOW

Note 1: These events are derived from the internal PWM Generator time base comparison events.

Table 12-2 shows the truth table that describes how the Quadrature signals are decoded.

# TABLE 12-2:TRUTH TABLE FOR<br/>QUADRATURE ENCODER

| Quad | rent<br>rature<br>ate | Previous<br>Quadrature<br>State |    | Action                       |  |  |

|------|-----------------------|---------------------------------|----|------------------------------|--|--|

| QA   | QB                    | QA                              | QB |                              |  |  |

| 1    | 1                     | 1                               | 1  | No count or direction change |  |  |

| 1    | 1                     | 1                               | 0  | Count up                     |  |  |

| 1    | 1                     | 0                               | 1  | Count down                   |  |  |

| 1    | 1                     | 0                               | 0  | Invalid state change; ignore |  |  |

| 1    | 0                     | 1                               | 1  | Count down                   |  |  |

| 1    | 0                     | 1                               | 0  | No count or direction change |  |  |

| 1    | 0                     | 0                               | 1  | Invalid state change; ignore |  |  |

| 1    | 0                     | 0                               | 0  | Count up                     |  |  |

| 0    | 1                     | 1                               | 1  | Count up                     |  |  |

| 0    | 1                     | 1                               | 0  | Invalid state change; ignore |  |  |

| 0    | 1                     | 0                               | 1  | No count or direction change |  |  |

| 0    | 1                     | 0                               | 0  | Count down                   |  |  |

| 0    | 0                     | 1                               | 1  | Invalid state change; ignore |  |  |

| 0    | 0                     | 1                               | 0  | Count down                   |  |  |

| 0    | 0                     | 0                               | 1  | Count up                     |  |  |

| 0    | 0                     | 0                               | 0  | No count or direction change |  |  |

Figure 12-2 illustrates the simplified block diagram of the QEI module. The QEI module consists of decoder logic to interpret the Phase A (QEAx) and Phase B (QEBx) signals, and an up/down counter to accumulate the count. The counter pulses are generated when the Quadrature state changes. The count direction information must be maintained in a register until a direction change is detected. The module also includes digital noise filters, which condition the input signal. The QEI module consists of the following major features:

- Four Input Pins: Two Phase Signals, an Index Pulse and a Home Pulse

- Programmable Digital Noise Filters on Inputs

- Quadrature Decoder providing Counter Pulses and Count Direction

- Count Direction Status

- 4x Count Resolution

- Index (INDXx) Pulse to Reset the Position Counter

- General Purpose 32-Bit Timer/Counter mode

- · Interrupts generated by QEI or Counter Events

- 32-Bit Velocity Counter

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 32-Bit Position Initialization/Capture Register

- 32-Bit Compare Less Than and Greater Than Registers

- External Up/Down Count mode

- · External Gated Count mode

- External Gated Timer mode

- Interval Timer mode

NOTES:

| R/W-0      | U-0                          | R/W-0                                                          | R/W-0                        | R/W-0                   | R/W-0                   | R/W-0                 | R/W-0                 |  |

|------------|------------------------------|----------------------------------------------------------------|------------------------------|-------------------------|-------------------------|-----------------------|-----------------------|--|

| RXWIE      |                              | RXMSK5 <sup>(1)</sup>                                          | RXMSK4 <sup>(1,4)</sup>      | RXMSK3 <sup>(1,3)</sup> | RXMSK2 <sup>(1,2)</sup> | RXMSK1 <sup>(1)</sup> | RXMSK0 <sup>(1)</sup> |  |

| bit 15     |                              | TORMOTO                                                        | 101010104                    | TOTHORS                 |                         |                       | bit 8                 |  |

| DIL 15     |                              |                                                                |                              |                         |                         |                       | DILC                  |  |

| R/W-0      | U-0                          | R/W-0                                                          | R/W-0                        | R/W-0                   | R/W-0                   | R/W-0                 | R/W-0                 |  |

| TXWIEI     | м —                          | TXMSK5 <sup>(1)</sup>                                          | TXMSK4 <sup>(1,4)</sup>      | TXMSK3 <sup>(1,3)</sup> | TXMSK2 <sup>(1,2)</sup> | TXMSK1 <sup>(1)</sup> | TXMSK0 <sup>(1)</sup> |  |

| bit 7      |                              |                                                                | •                            |                         |                         |                       | bit (                 |  |

| Legend:    |                              |                                                                |                              |                         |                         |                       |                       |  |

| R = Reada  | able bit                     | W = Writable I                                                 | bit                          | U = Unimplem            | ented bit, read         | as '0'                |                       |  |

| -n = Value | at POR                       | '1' = Bit is set                                               |                              | '0' = Bit is clea       |                         | x = Bit is unknown    |                       |  |