# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 17                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 14x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 20-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f785-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.6 PCON Register

The Power Control register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Timer (WDT) Reset (WDT) and an external MCLR Reset.

#### REGISTER 2-6: PCON: POWER CONTROL REGISTER

| U-0                                                                  | U-0                                                                                                                                                                                           | U-0              | R/W-1 | U-0                   | U-0  | R/W-0           | R/W-x |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-----------------------|------|-----------------|-------|--|--|--|

|                                                                      | —                                                                                                                                                                                             | _                | —     | SBOREN <sup>(1)</sup> | _    | —               | POR   |  |  |  |

| bit 7                                                                |                                                                                                                                                                                               |                  |       |                       |      |                 | bit 0 |  |  |  |

|                                                                      |                                                                                                                                                                                               |                  |       |                       |      |                 |       |  |  |  |

| Legend:                                                              |                                                                                                                                                                                               |                  |       |                       |      |                 |       |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                                                                                                                               |                  |       |                       |      |                 |       |  |  |  |

| -n = Value at P                                                      | OR                                                                                                                                                                                            | '1' = Bit is set |       | '0' = Bit is cle      | ared | x = Bit is unkn | iown  |  |  |  |

| bit 7-5<br>bit 4                                                     |                                                                                                                                                                                               |                  |       |                       |      |                 |       |  |  |  |

| bit 3-2                                                              | Unimplement                                                                                                                                                                                   | ted: Read as '   | )'    |                       |      |                 |       |  |  |  |

| bit 1                                                                | <b>POR:</b> Power-on Reset Status bit<br>1 = No Power-on Reset occurred<br>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                              |                  |       |                       |      |                 |       |  |  |  |

| bit 0                                                                | <ul> <li>BOR: Brown-out Reset Status bit</li> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)</li> </ul> |                  |       |                       |      |                 |       |  |  |  |

**Note 1:** BOREN<1:0> = 01 in Configuration Word for this bit to control the  $\overline{\text{BOR}}$ .

#### 3.4.2.2 OSCTUNE Register

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-1).

The OSCTUNE register has a nominal tuning range of  $\pm 12\%$ . The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number. Due to process variation, the monotonicity and frequency step cannot be specified.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. The HFINTOSC clock will stabilize within 1 ms. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### R/W-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 TUN4 TUN3 TUN2 TUN1 **TUN0** bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknownbit 7-5 Unimplemented: Read as '0' bit 4-0 TUN<4:0>: Frequency Tuning bits 01111 = Maximum frequency 01110 =00001 = 00000 = Center frequency. Oscillator module is running at the calibrated frequency. 111111 =10000 = Minimum frequency

#### REGISTER 3-1: OSCTUNE: OSCILLATOR TUNING REGISTER

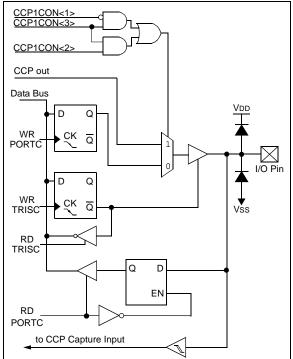

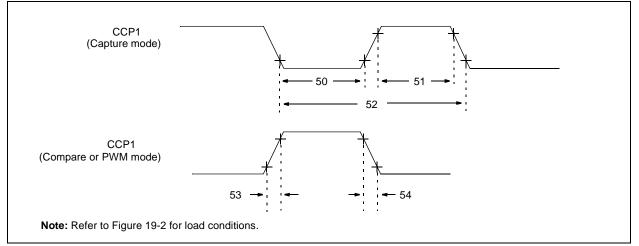

#### 4.4.1.8 RC5/CCP1

The RC5 is configurable to function as one of the following:

- General purpose I/O

- Digital input for the capture/compare

- Digital output for the CCP

FIGURE 4-14: BLOCK DIAGRAM OF RC5

#### TABLE 4-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all other Resets |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------|

| ANSEL1  | —      | _      | —      | —      | ANS11  | ANS10  | ANS9   | ANS8   | 1111                 | 1111                      |

| CCP1CON | —      | —      | DC1B1  | DC1B0  | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | 0000 0000            | 0000 0000                 |

| OPA1CON | OPAON  | —      | —      | _      | —      | —      | —      | —      | 0                    | 0                         |

| OPA2CON | OPAON  | —      | —      | _      | —      | —      | —      | —      | 0                    | 0                         |

| PORTC   | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx xxxx            | uuuu uuuu                 |

| PWMCON0 | PRSEN  | PASEN  | BLANK2 | BLANK1 | SYNC1  | SYNC0  | PH2EN  | PH1EN  | 0000 0000            | 0000 0000                 |

| TRISC   | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

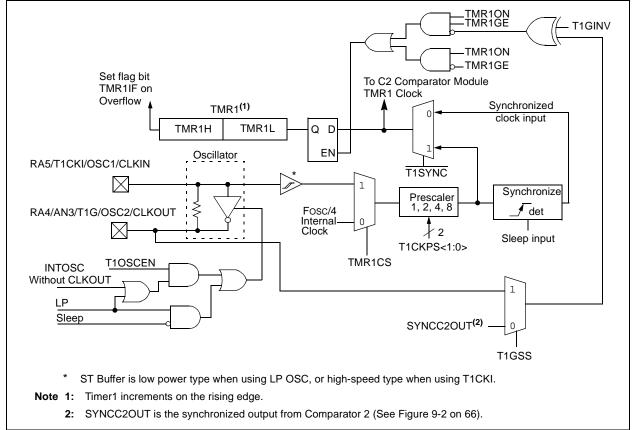

## 6.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is the 16-bit counter of the PIC16F785/HV785. Figure 6-1 shows the basic block diagram of the Timer1 module. Timer1 has the following features:

- 16-bit timer/counter (TMR1H:TMR1L)

- Readable and writable

- · Internal or external clock selection

- Synchronous or asynchronous operation

- Interrupt on overflow from FFFFh to 0000h

- Wake-up upon overflow (Asynchronous mode)

- Optional external enable input:

- Selectable gate source; T1G or C2 output (T1GSS)

- Selectable gate polarity (T1GINV)

- · Optional LP oscillator

The Timer1 Control register (T1CON), shown in Register 6-1, is used to enable/disable Timer1 and select the various features of the Timer1 module.

#### 6.5 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  of the T1CON Register is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | The ANSEL0 (91h) register must be initial- |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | ized to configure an analog channel as a   |  |  |  |  |  |  |

|       | digital input. Pins configured as analog   |  |  |  |  |  |  |

|       | inputs will read '0'.                      |  |  |  |  |  |  |

#### 6.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

### 6.6 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN of the T1CON Register. The oscillator is a low power oscillator rated for 32.768 kHz. It will continue to run during Sleep. It is primarily intended for a 32.768 kHz tuning fork crystal.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the primary system clock is also the LP oscillator or is derived from the internal oscillator. As with the system LP oscillator, the user must provide a software time delay to ensure proper oscillator start-up.

Sleep mode will not disable the system clock when the system clock and Timer1 share the LP oscillator.

TRISA<5> and TRISA<4> bits are set when the Timer1 oscillator is enabled. RA5 and RA4 read as '0' and TRISA<5> and TRISA<4> bits read as '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

### 6.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To setup the timer to wake the device:

- Timer1 of the T1CON Register must be on

- TMR1IE bit of the PIE1 Register must be set

- · PEIE bit of the INTCON Register must be set

The device will wake-up on an overflow. If the GIE bit of the INTCON Register is set, the device will wake-up and jump to the Interrupt Service Routine (0004h) on an overflow. If the GIE bit is clear, execution will continue with the next instruction.

| Bit 7                                                                       | Bit 6                                                         | Bit 5                                                                           | Bit 4                                                                                                                  | Bit 3                                                                                                                                                         | Bit 2                                                                                                                                                                                              | Bit 1                                                                                                                                                                                                                                    | Bit 0                                                                                                                                                                                                                                                           | Value on<br>POR, BOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Value on all other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANS7                                                                        | ANS6                                                          | ANS5                                                                            | ANS4                                                                                                                   | ANS3                                                                                                                                                          | ANS2                                                                                                                                                                                               | ANS1                                                                                                                                                                                                                                     | ANS0                                                                                                                                                                                                                                                            | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MC10UT                                                                      | MC2OUT                                                        | —                                                                               | —                                                                                                                      | —                                                                                                                                                             | —                                                                                                                                                                                                  | T1GSS                                                                                                                                                                                                                                    | C2SYNC                                                                                                                                                                                                                                                          | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GIE                                                                         | PEIE                                                          | TOIE                                                                            | INTE                                                                                                                   | RAIE                                                                                                                                                          | TOIF                                                                                                                                                                                               | INTF                                                                                                                                                                                                                                     | RAIF                                                                                                                                                                                                                                                            | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EEIE                                                                        | ADIE                                                          | CCP1IE                                                                          | C2IE                                                                                                                   | C1IE                                                                                                                                                          | OSFIE                                                                                                                                                                                              | TMR2IE                                                                                                                                                                                                                                   | TMR1IE                                                                                                                                                                                                                                                          | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EEIF                                                                        | ADIF                                                          | CCP1IF                                                                          | C2IF                                                                                                                   | C1IF                                                                                                                                                          | OSFIF                                                                                                                                                                                              | TMR2IF                                                                                                                                                                                                                                   | TMR1IF                                                                                                                                                                                                                                                          | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| T1GINV                                                                      | TMR1GE                                                        | T1CKPS1                                                                         | T1CKPS0                                                                                                                | T1OSCEN                                                                                                                                                       | T1SYNC                                                                                                                                                                                             | TMR1CS                                                                                                                                                                                                                                   | TMR1ON                                                                                                                                                                                                                                                          | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                                                               |                                                                                 |                                                                                                                        |                                                                                                                                                               |                                                                                                                                                                                                    |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                 | xxxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |                                                               |                                                                                 |                                                                                                                        |                                                                                                                                                               |                                                                                                                                                                                                    |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                 | xxxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | ANS7<br>MC1OUT<br>GIE<br>EEIE<br>EEIF<br>T1GINV<br>Holding Re | ANS7ANS6MC1OUTMC2OUTGIEPEIEEEIEADIEEEIFADIFT1GINVTMR1GEHolding Register for the | ANS7ANS6ANS5MC1OUTMC2OUT—GIEPEIETOIEEEIEADIECCP1IEEEIFADIFCCP1IFT1GINVTMR1GET1CKPS1Holding Register for the Least Sign | ANS7ANS6ANS5ANS4MC1OUTMC2OUT——GIEPEIETOIEINTEEEIEADIECCP1IEC2IEEEIFADIFCCP1IFC2IFT1GINVTMR1GET1CKPS1T1CKPS0Holding Register for the Least Significant Byte of | ANS7ANS6ANS5ANS4ANS3MC1OUTMC2OUT———GIEPEIET0IEINTERAIEEEIEADIECCP1IEC2IEC1IEEEIFADIFCCP1IFC2IFC1IFT1GINVTMR1GET1CKPS1T1CKPS0T1OSCENHolding Register for the Least Significant Byte of the 16-bit T | ANS7ANS6ANS5ANS4ANS3ANS2MC1OUTMC2OUT—————GIEPEIETOIEINTERAIETOIFEEIEADIECCP1IEC2IEC1IEOSFIEEEIFADIFCCP1IFC2IFC1IFOSFIFT1GINVTMR1GET1CKPS1T1CKPS0T1OSCENT1SYNCHolding Register for the Least Significant Byte of the 16-bit TJR1 Register | ANS7ANS6ANS5ANS4ANS3ANS2ANS1MC1OUTMC2OUT————T1GSSGIEPEIET0IEINTERAIET0IFINTFEEIEADIECCP1IEC2IEC1IEOSFIETMR2IEEEIFADIFCCP1IFC2IFC1IFOSFIFTMR2IFT1GINVTMR1GET1CKPS1T1OSCENT1SYNCTMR1CSHolding Rejister for the Least Significant Byte of the 16-bit TWR1 Register | ANS7         ANS6         ANS5         ANS4         ANS3         ANS2         ANS1         ANS0           MC1OUT         MC2OUT         —         —         —         —         T1GSS         C2SYNC           GIE         PEIE         T0IE         INTE         RAIE         T0IF         INTF         RAIF           EEIE         ADIE         CCP1IE         C2IE         C1IE         OSFIE         TMR2IE         TMR1IE           EEIF         ADIF         CCP1IF         C2IF         C1IF         OSFIF         TMR2IF         TMR1IE           T1GINV         TMR1GE         T1CKPS1         T1OSCEN         T1SYNC         TMR1CS         TMR1ON           Holding Rejister for the Least Significant Byte of the 16-bit TKR1 Register         TMR1CS         TMR1ON         TMR1CS         TMR1ON | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         POR, BOR           ANS7         ANS6         ANS5         ANS4         ANS3         ANS2         ANS1         ANS0         1111 1111           MC1OUT         MC2OUT         —         —         —         —         T1GSS         C2SYNC         0010           GIE         PEIE         T0IE         INTE         RAIE         T0IF         INTF         RAIF         0000 0000           EEIE         ADIE         CCP1IE         C2IE         C1IE         OSFIE         TMR2IE         TMR1IE         0000 0000           EEIF         ADIF         CCP1IF         C2IF         C1IF         OSFIF         TMR2IE         TMR1IE         0000 0000           T1GINV         TMR1GE         T1CKPS0         T1OSCEN         T1SYNC         TMR1ON         0000 0000           Holding Rejster for the Least Significant Byte of the 16-bit TWR1 Register         xxxx xxxxx         xxxx xxxxx |

TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER1

Legend: - x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

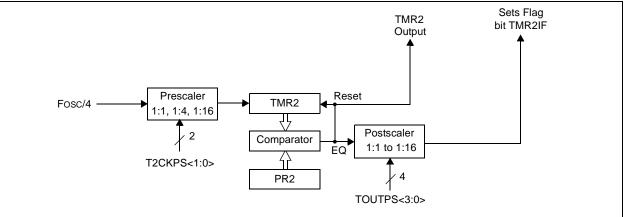

#### 7.2 Timer2 Interrupt

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2

| Name   | Bit 7                                        | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other Resets |

|--------|----------------------------------------------|---------------|---------|---------|---------|--------|---------|---------|----------------------|------------------------------|

| INTCON | GIE                                          | PEIE          | T0IE    | INTE    | RAIE    | T0IF   | INTF    | RAIF    | 0000 0000            | 0000 0000                    |

| PIE1   | EEIE                                         | ADIE          | CCP1IE  | C2IE    | C1IE    | OSFIE  | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                    |

| PIR1   | EEIF                                         | ADIF          | CCP1IF  | C2IF    | C1IF    | OSFIF  | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                    |

| PR2    | Timer2 Mo                                    | dule Period r | egister |         | •       |        |         |         | 1111 1111            | 1111 1111                    |

| T2CON  | —                                            | TOUTPS3       | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                    |

| TMR2   | Holding Register for the 8-bit TMR2 Register |               |         |         |         |        |         |         | 0000 0000            | 0000 0000                    |

Legend: -x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

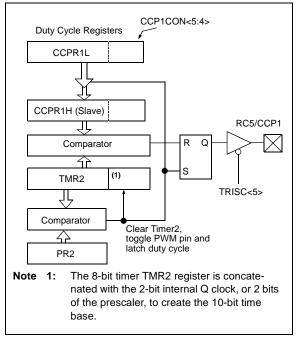

#### 8.3 CCP PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the RC5/CCP1 pin. Since the RC5/CCP1 pin is multiplexed with the PORTC data latch, the TRISC<5> must be cleared to make the RC5/CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force   |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | the PWM output latch to the default        |  |  |  |  |  |  |  |  |  |

|       | inactive levels. This is not the PORTC I/O |  |  |  |  |  |  |  |  |  |

|       | data latch.                                |  |  |  |  |  |  |  |  |  |

Figure 8-3 shows a simplified block diagram of PWM operation.

For a step by step procedure on how to set up the CCP module for PWM operation, see **Section 8.3.5** "**Setup for PWM Operation**".

#### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

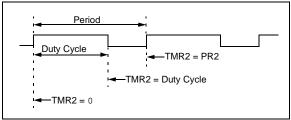

The PWM output (Figure 8-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 8-4: CCP PWM OUTPUT

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the formula of Equation 8-1.

#### EQUATION 8-1: PWM PERIOD

$$PWM \ period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$$

$$(TMR2 \ prescale \ value)$$

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The RC5/CCP1 pin is set. (exception: if PWM duty cycle = 0%, the pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

- Note: The Timer2 postscaler (see Section 7.1 "Timer2 Operation") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 9.1.2.2 Control Register CM2CON1

Comparator C2 has one additional feature: its output can be synchronized to the Timer1 clock input. Setting C2SYNC of the CM2CON1 Register synchronizes the output of Comparator 2 to the falling edge of the Timer1 clock input (see Figure 9-2 and Register 9-3).

The CM2CON1 register also contains mirror copies of both comparator outputs, MC1OUT and MC2OUT of the CM2CON1 Register. The ability to read both outputs simultaneously from a single register eliminates the timing skew of reading separate registers.

**Note:** Obtaining the status of C1OUT or C2OUT by reading CM2CON1 does not affect the comparator interrupt mismatch registers.

#### REGISTER 9-3: CM2CON1: COMPARATOR C2 CONTROL REGISTER 1

| R-0    | R-0    | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-0  |

|--------|--------|-----|-----|-----|-----|-------|--------|

| MC1OUT | MC2OUT | —   | —   | —   | —   | T1GSS | C2SYNC |

| bit 7  |        |     |     |     |     |       | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 6 MC2OUT: Mirror Copy of C2OUT bit (CM2CON0<6>)

bit 5-2 Unimplemented: Read as '0'

- bit 1 T1GSS: Timer1 Gate Source Select bit

- 1 = Timer1 gate source is RA4/AN3/T1G/OSC2/CLKOUT

- 0 = Timer1 gate source is SYNCC2OUT.

- bit 0 C2SYNC: C2 Output Synchronous Mode bit

- 1 = C2 output is synchronous to falling edge of TMR1 clock

- 0 = C2 output is asynchronous

#### 9.2 Comparator Outputs

The comparator outputs are read through the CM1CON0, COM2CON0 or CM2CON1 registers. CM1CON0 and CM2CON0 each contain the individual comparator output of Comparator 1 and Comparator 2, respectively. CM2CON2 contains a mirror copy of both comparator outputs facilitating a simultaneous read of both comparators. These bits are read-only. The comparator outputs may also be directly output to the RA2/AN2/T0CKI/INT/C1OUT and RC4/C2OUT/PH2

I/O pins. When enabled, multiplexers in the output path of the RA2 and RC4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 9-1 and Figure 9-2 show the output block diagrams for Comparators 1 and 2, respectively.

The TRIS bits will still function as an output enable/ disable for the RA2/AN2/T0CKI/INT/C1OUT and RC4/ C2OUT/PH2 pins while in this mode.

The polarity of the comparator outputs can be changed using the C1POL and C2POL bits of the CMxCON0 Register.

Timer1 gate source can be configured to use the T1G pin or Comparator 2 output as selected by the T1GSS bit of the CM2CON1 Register. The Timer1 gate feature can be used to time the duration or interval of analog events. The output of Comparator 2 can also be synchronized with Timer1 by setting the C2SYNC bit of the CM2CON1 Register. When enabled, the output of Comparator 2 is latched on the falling edge of the Timer1 clock source. If a prescaler is used with Timer1, Comparator 2 is latched after the prescaler. To prevent a race condition, the Comparator 2 output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator 2 Block Diagram (Figure 9-2) and the Timer1 Block Diagram (Figure 6-1) for more information.

It is recommended to synchronize Comparator 2 with Timer1 by setting the C2SYNC bit when Comparator 2 is used as the Timer1 gate source. This ensures Timer1 does not miss an increment if Comparator 2 changes during an increment.

#### 9.3 Comparator Interrupts

The comparator interrupt flags are set whenever there is a change in the output value of its respective comparator. Software will need to maintain information about the status of the output bits, as read from CM2CON0<7:6>, to determine the actual change that has occurred. The CxIF bits, PIR1<4:3>, are the Comparator Interrupt Flags. Each comparator interrupt bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CxIE bits of the PIE1 Register and the PEIE bit of the INTCON Register must be set to enable the interrupts. In addition, the GIE bit must also be set. If any of these bits are cleared, the interrupt is not enabled, though the CxIF bits will still be set if an interrupt condition occurs.

The comparator interrupt of the PIC16F785/HV785 differs from previous designs in that the interrupt flag is set by the mismatch edge and not the mismatch level. This means that the interrupt flag can be reset without the additional step of reading or writing the CMxCON0 register to clear the mismatch registers. When the mismatch registers are not cleared, an interrupt will not occur when the comparator output returns to the previous state. When the mismatch registers are cleared, an interrupt will occur when the comparator returns to the previous state.

| Note 1: | If a change in the CMxCON0 register<br>(CxOUT) should occur when a read<br>operation is being executed (start of the<br>Q2 cycle), then the CxIF of the PIR1 Reg-<br>ister interrupt flag may not get set.                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When either comparator is first enabled, bias circuitry in the Comparator module may cause an invalid output from the comparator until the bias circuitry is stable. Allow about 1 $\mu$ s for bias settling then clear the mismatch condition and interrupt flags before enabling comparator interrupts. |

#### 9.4 Effects of Reset

A Reset forces all registers to their Reset state. This disables both comparators.

#### **10.2 VR Reference Module**

The VR Reference module generates a 1.2V nominal output voltage for use by the ADC and comparators. The output voltage can also be brought out to the VREF pin for user applications. This module uses a bandgap as a reference. See Table 19-9 for detailed specifications. Register 10-2 shows the control register for the VR module.

#### REGISTER 10-2: REFCON: VOLTAGE REFERENCE CONTROL REGISTER

| U-0   | U-0 | R-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0   |

|-------|-----|------|-------|-------|-------|-------|-------|

| —     | —   | BGST | VRBB  | VREN  | VROE  | CVROE | —     |

| bit 7 |     |      |       |       |       |       | bit 0 |

|       |     |      |       |       |       |       |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | BGST: Band Gap Reference Voltage Stable Flag bit                                                                                                          |

|         | 1 = Reference is stable                                                                                                                                   |

|         | 0 = Reference is not stable                                                                                                                               |

| bit 4   | VRBB: Voltage Reference Buffer Bypass bit                                                                                                                 |

|         | <ul> <li>1 = VREF output is not buffered. Power is removed from buffer amplifier.</li> <li>0 = VREF output is buffered<sup>(1)</sup></li> </ul>           |

| bit 3   | VREN: Voltage Reference Enable bit (VR = 1.2V nominal) <sup>(2)</sup>                                                                                     |

|         | 1 = VR reference is enabled                                                                                                                               |

|         | 0 = VR reference is disabled and does not consume any current                                                                                             |

| bit 2   | VROE: Voltage Reference Output Enable bit                                                                                                                 |

|         | <u>If CVROE = 0:</u>                                                                                                                                      |

|         | 1 = VREF output on RA1/AN1/C12IN0-/VREF/ICSPCLK pin is 1.2 volt VR analog reference<br>0 = Disabled, 1.2 volt VR analog reference is used internally only |

|         | <u>If CVROE = 1:</u>                                                                                                                                      |

|         | VROE has no effect.                                                                                                                                       |

| bit 1   | CVROE: Comparator Voltage Reference Output Enable bit (see Figure 10-2)                                                                                   |

|         | 1 = VREF output on RA1/AN1/C12IN0-/VREF/ICSPCLK pin is CVREF voltage                                                                                      |

|         | 0 = VREF output on RA1/AN1/C12IN0-/VREF/ICSPCLK pin is controlled by VROE                                                                                 |

| bit 0   | Unimplemented: Read as '0'                                                                                                                                |

| Note 1: | Buffer amplifier common mode limitations require VREF $\leq$ (VDD - 1.4)V for buffered output.                                                            |

2: VREN is fixed high for PIC16HV785 device.

#### 12.2 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 12-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 12-4. **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . As the impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 12-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

#### EQUATION 12-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega$  5.0V VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + Tc + TCOFF$

$$= 5\mu s + Tc + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

The value for Tc can be approximated with the following equations:

T

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad ;[1] V_{chold charged to within 1/2 lsb}$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{chold charge response to Vapplied}$$

$$V_{APPLIED}\left(1-e^{\frac{-1C}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{2047}\right) \quad ;Combining [1] and [2]$$

Solving for Tc:

$$Tc = -CHOLD(Ric + Rss + Rs) \ln(1/2047)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)

= 1.37\mus

e:

Therefore:

$$Tacq = 5\mu s + 1.37\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.62\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

| R/W-0         | R/W-0                                                                                                                                                                                 | R/W-0                                                                                                                 | R/W-0                                                                                                                                                 | R/W-0                                                                                       | R/W-0                                                  | R/W-0                         | R/W-0 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------|-------|

| POL           | C2EN                                                                                                                                                                                  | C1EN                                                                                                                  | PH4                                                                                                                                                   | PH3                                                                                         | PH2                                                    | PH1                           | PH0   |

| bit 7         |                                                                                                                                                                                       |                                                                                                                       |                                                                                                                                                       |                                                                                             |                                                        |                               | bit ( |

| Legend:       |                                                                                                                                                                                       |                                                                                                                       |                                                                                                                                                       |                                                                                             |                                                        |                               |       |

| R = Readabl   | le bit                                                                                                                                                                                | W = Writable                                                                                                          | bit                                                                                                                                                   | U = Unimplei                                                                                | mented bit, rea                                        | d as '0'                      |       |

| -n = Value at |                                                                                                                                                                                       | '1' = Bit is set                                                                                                      |                                                                                                                                                       | '0' = Bit is cle                                                                            |                                                        | x = Bit is unkr               | nown  |

| bit 7         | 1 = PH2 Pir                                                                                                                                                                           | Dutput Polarity b<br>n is active low<br>n is active high                                                              | it                                                                                                                                                    |                                                                                             |                                                        |                               |       |

| bit 6         | <b>C2EN:</b> Com<br><u>When COM</u><br>1 = PH<br>0 = PH<br><u>When COM</u>                                                                                                            | parator 2 Enable<br>$OD < 1:0> = 00^{(1)}$<br>2 is reset when<br>2 ignores Comp<br>OD < 1:0> = 1x c<br>has no effect  | )<br>C2OUT goes<br>parator 2                                                                                                                          | high                                                                                        |                                                        |                               |       |

| bit 5         | <u>When COM</u><br>1 = PH<br>0 = PH<br><u>When COM</u>                                                                                                                                | parator 1 Enable<br>OD < 1:0 > = 0.0 (1<br>2 is reset when<br>2 ignores Comp<br>OD < 1:0 > = 1.X comp<br>as no effect | )<br>C1OUT goes<br>parator 1                                                                                                                          | high                                                                                        |                                                        |                               |       |

| bit 4-0       | When COM           00000           00001           11111           When COM           00000           000001              11111           When COM           00001              11111 | = PH2 is delay<br>= •••<br>= PH2 is delay<br>$OD < 1:0 > = 1x^{(1)}$<br>= Complement                                  | pwm_clk period<br>elative to this t<br>ed by 1 pwm_<br>ed by 31 pwm<br>)<br>ary drive term<br>2 delays are e<br>ary drive term<br>ary drive term<br>) | ime.<br>_clk pulse<br>n_clk pulses<br>ninates 1 pwm_<br>xpressed relati<br>ination is delay | _clk period afte<br>ive to this time.<br>yed by 1 pwm_ | r falling edge o<br>clk pulse |       |

#### REGISTER 13-4: PWMPH2: PWM PHASE 2 CONTROL REGISTER

Note 1: See PWMCON1 register (Register 13-5).

#### WAKE-UP FROM SLEEP THROUGH INTERRUPT<sup>(1)</sup> FIGURE 15-10:

| OSC1                        | ; Q1   Q2   Q3   Q4;<br>'へ へ へ へ ′ | Q1 Q2 Q3  Q4;   | Q1            | MMM             | Q1  Q2  Q3  Q4  | ¦ Q1  Q2  Q3  Q4<br>'∽ ∽ ∽ ∽ | Q1 Q2 Q3 Q4;                          | Q1 Q2 Q3 Q4¦   |

|-----------------------------|------------------------------------|-----------------|---------------|-----------------|-----------------|------------------------------|---------------------------------------|----------------|

| CLKOUT <sup>(4)</sup>       |                                    |                 |               | Tost(2)         |                 |                              |                                       |                |

| INT pin                     |                                    |                 |               | 1               |                 | I                            | 1 1                                   | <u> </u>       |

| INTF flag<br>(INTCON<1>)    |                                    |                 | `\            |                 | Interrupt Laten | cy <sup>(3)</sup>            | ;;<br>;►;                             |                |

| GIE bit<br>(INTCON<7>)      |                                    |                 | Processor     |                 |                 | ·<br>·<br>·                  | · · · · · · · · · · · · · · · · · · · |                |

| INSTRUCTION                 | -                                  | ;               |               | — — ,<br>,<br>, |                 | ;<br>'<br>!                  | ;;                                    | ;-             |

| PC                          | X <u>PC</u> X                      | PC + 1          | X <u>PC</u> + | +2              | ( PC + 2        | X PC + 2                     | <u>χ 0004h</u>                        | ( <u>0005h</u> |

| Instruction {<br>Fetched {  | Inst(PC) = Sleep                   | Inst(PC + 1)    | <br>          | 1               | Inst(PC + 2)    | I                            | Inst(0004h)                           | Inst(0005h)    |

| Instruction {<br>Executed { | Inst(PC - 1)                       | Sleep           |               | 1               | Inst(PC + 1)    | Dummy cycle                  | Dummy cycle                           | Inst(0004h)    |

| Note 1:                     | XT, HS or LP Oscilla               | ator mode assum | ed            |                 |                 |                              |                                       |                |

- TOST = 1024TOSC (drawing not to scale). This delay does not apply to EC, RC and INTOSC Oscillator modes or Two-Speed Start-up 2: (see Section 3.6 "Two-Speed Clock Start-up Mode").

- GIE = 1 assumed. In this case after wake-up, the processor jumps to 0004h. 3:

- If GIE = 0, execution will continue in-line

- CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference. 4:

#### 15.7 **Code Protection**

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using ICSP<sup>™</sup> for verification purposes.

| Note: | If the code protection is turned off, the |

|-------|-------------------------------------------|

|       | entire data EEPROM and Flash program      |

|       | memory will be erased by performing a     |

|       | bulk erase command. See the               |

|       | "PIC16F785/HV785 Memory Program-          |

|       | ming Specification" (DS41237) for more    |

|       | information.                              |

#### 15.8 **ID** Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. Only the Least Significant 7 bits of the ID locations are used.

#### 15.9 In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

The PIC16F785/HV785 microcontrollers can be serially programmed while in the end application circuit. This is simply done with five lines:

- Clock

- Data

- Power

- Ground

- Programming voltage

This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The device is placed into a Program/Verify mode by holding the RA0 and RA1 pins low, while raising the MCLR (VPP) pin from VIL to VIHH. See the "PIC16F785/ HV785 Memory Programming Specification" (DS41237) for more information. RA0 becomes the programming data and RA1 becomes the programming clock. Both RA0 and RA1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Program/Verify mode, the Program Counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the "PIC16F785/HV785 Memory Programming Specification" (DS41237).

A typical In-Circuit Serial Programming connection is shown in Figure 15-11.

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                             |