Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

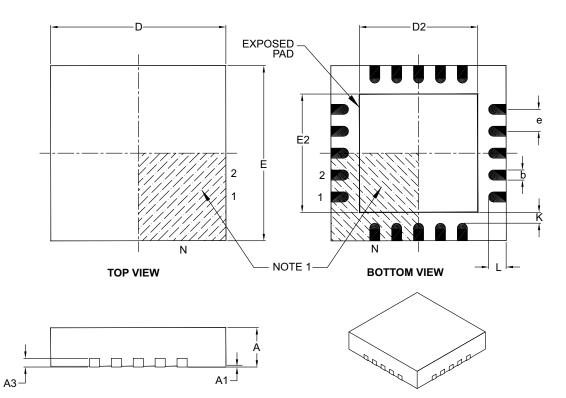

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv785-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                       | 5   |

|-------|-------------------------------------------------------|-----|

| 2.0   | Memory Organization                                   | 9   |

| 3.0   | Clock Sources                                         | 23  |

| 4.0   | I/O Ports                                             | 35  |

| 5.0   | Timer0 Module                                         | 49  |

| 6.0   | Timer1 Module with Gate Control                       | 51  |

| 7.0   | Timer2 Module                                         | 55  |

| 8.0   | Capture/Compare/PWM (CCP) Module                      | 57  |

| 9.0   | Comparator Module                                     |     |

| 10.0  | Voltage References                                    | 70  |

| 11.0  | Operational Amplifier (OPA) Module                    | 75  |

| 12.0  | Analog-to-Digital Converter (A/D) Module              | 79  |

| 13.0  | Two-Phase PWM                                         | 91  |

| 14.0  | Data EEPROM Memory                                    | 103 |

| 15.0  | Special Features of the CPU                           | 107 |

| 16.0  | Voltage Regulator                                     | 126 |

| 17.0  | Instruction Set Summary                               |     |

| 18.0  | Development Support                                   | 137 |

| 19.0  | Electrical Specifications                             | 141 |

|       | DC and AC Characteristics Graphs and Tables           |     |

| 21.0  | Packaging Information                                 | 187 |

|       | ndix A: Data Sheet Revision History                   |     |

| Appe  | ndix B: Migrating from other PIC <sup>®</sup> Devices | 193 |

| Index |                                                       | 195 |

| The N | /icrochip Web Site                                    | 201 |

| Custo | mer Change Notification Service                       | 201 |

| Custo | mer Support                                           | 201 |

|       | er Response                                           | -   |

| Produ | Ict Identification System                             | 203 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 2.2.2.2 OPTION\_REG Register

The Option register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RA2/INT interrupt, the TMR0 and the weak pull-ups on PORTA.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT by setting PSA bit to '1' in the OPTION Register. See Section 5.4 "Prescaler".

## REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RAPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       | •     |       |       | bit 0 |

| Legend:                                                                     |                |                                                      |                                                                             |                                                           |                                      |                    |  |

|-----------------------------------------------------------------------------|----------------|------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------|--------------------|--|

| R = Readable bit                                                            |                | W = Writable bit                                     |                                                                             | U =                                                       | U = Unimplemented bit, read as '0'   |                    |  |

| -n = Value                                                                  | at POR         | '1' = B                                              | t is set                                                                    | 'O' =                                                     | Bit is cleared                       | x = Bit is unknown |  |

| bit 7 <b>RAPU:</b> PORTA Pull-up Enable bit 1 = PORTA pull-ups are disabled |                |                                                      |                                                                             |                                                           |                                      |                    |  |

|                                                                             | 0 <b>= POR</b> | TA pull-ups a                                        | are enabled b                                                               | oy individual p                                           | ort latch values in                  | WPUA register      |  |

| bit 6                                                                       | INTEDG         | : Interrupt Ec                                       | lge Select bit                                                              | t                                                         |                                      |                    |  |

|                                                                             |                |                                                      | •                                                                           |                                                           | /INT/C1OUT pin<br>/INT/C1OUT pin     |                    |  |

| bit 5                                                                       |                | MR0 Clock S                                          |                                                                             | t bit<br>/INT/C1OUT                                       | nin                                  |                    |  |

|                                                                             |                | nal instructio                                       |                                                                             |                                                           |                                      |                    |  |

| bit 4                                                                       | TOSE: T        | MR0 Source                                           | Edge Select                                                                 | bit                                                       |                                      |                    |  |

|                                                                             |                | •                                                    |                                                                             |                                                           | /AN2/T0CKI/INT/C<br>/AN2/T0CKI/INT/C | •                  |  |

| bit 3                                                                       | PSA: Pro       | escaler Assig                                        | nment bit                                                                   |                                                           |                                      |                    |  |

|                                                                             |                | caler is assig<br>caler is assig                     |                                                                             | /DT<br>imer0 module                                       |                                      |                    |  |

| bit 2-0                                                                     | PS<2:0>        | : Prescaler F                                        | Rate Select b                                                               | its                                                       |                                      |                    |  |

|                                                                             |                | Bit Value                                            | TMR0 Rate                                                                   | WDT Rate <sup>(1)</sup>                                   | 1                                    |                    |  |

|                                                                             |                | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256 | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128 |                                      |                    |  |

Note 1: A dedicated 16-bit WDT postscaler is available for the PIC16F785/HV785. See Section 15.5 "Watchdog Timer (WDT)" for more information.

### REGISTER 4-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1                 | R/W-1                 | R-1                   | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----------------------|-----------------------|-----------------------|--------|--------|--------|

|       | —   | TRISA5 <sup>(2)</sup> | TRISA4 <sup>(2)</sup> | TRISA3 <sup>(1)</sup> | TRISA2 | TRISA1 | TRISA0 |

| bit 7 |     |                       |                       |                       |        |        | bit 0  |

|       |     |                       |                       |                       |        |        |        |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                        |

|---------|---------------------------------------------------------------------------------------------------|

| bit 5-0 | TRISA<5:0>: PORTA Tri-State Control bit <sup>(1), (2)</sup>                                       |

|         | 1 = PORTA pin configured as an input (tri-stated)                                                 |

|         | 0 = PORTA pin configured as an output                                                             |

| bit 0   | C: Carry/ $\overline{\text{Borrow}}$ bit (addwf, addlw, sublw, subwf instructions) <sup>(1)</sup> |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                              |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                             |

Note 1: TRISA<3> always reads '1'.

**2:** TRISA<5:4> always reads '1' in XT, HS and LP OSC modes.

## 4.2 Additional Pin Functions

Every PORTA pin on the PIC16F785/HV785 has an interrupt-on-change option and a weak pull-up option. The next three sections describe these functions.

#### 4.2.1 WEAK PULL-UPS

Each of the PORTA pins has an individually configurable internal weak pull-up. Control bits WPUAx enable or disable each pull-up. Refer to Register 4-3. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RAPU bit in the (OPTION Register. The weak pull-up on RA3 is automatically enabled when RA3 is configured as MCLR.

### REGISTER 4-3: WPUA: WEAK PULL-UP REGISTER

| U-0   | U-0 | R/W-1                | R/W-1                | R/W-1                | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|----------------------|----------------------|----------------------|-------|-------|-------|

| —     | —   | WPUA5 <sup>(4)</sup> | WPUA4 <sup>(4)</sup> | WPUA3 <sup>(3)</sup> | WPUA2 | WPUA1 | WPUA0 |

| bit 7 |     |                      |                      |                      |       |       | bit 0 |

|       |     |                      |                      |                      |       |       |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

**Note 1:** Global RAPU must be enabled for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in Output mode (TRISA = 0).

3: The RA3 pull-up is automatically enabled when configured as MCLR in the Configuration Word.

**4:** WPUA<5:4> always reads '1' in XT, HS and LP OSC modes.

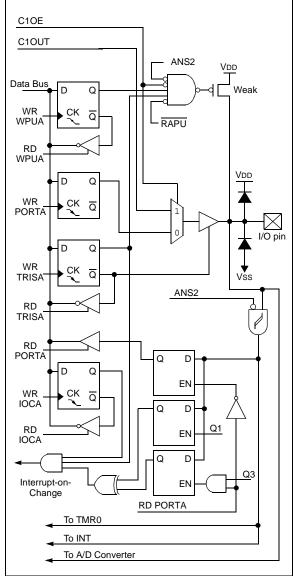

### 4.2.3.3 RA2/AN2/T0CKI/INT/C1OUT

Figure 4-3 shows the diagram for this pin. The RA2 pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D

- Clock input for TMR0

- External edge triggered interrupt

- Digital output from Comparator 1

## FIGURE 4-3:BLOCK DIAGRAM OF RA2

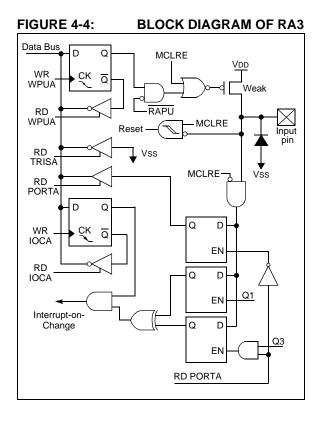

## 4.2.3.4 RA3/MCLR/VPP

Figure 4-4 shows the diagram for this pin. The RA3 pin is configurable to function as one of the following:

- General purpose input

- Master Clear Reset with weak pull-up

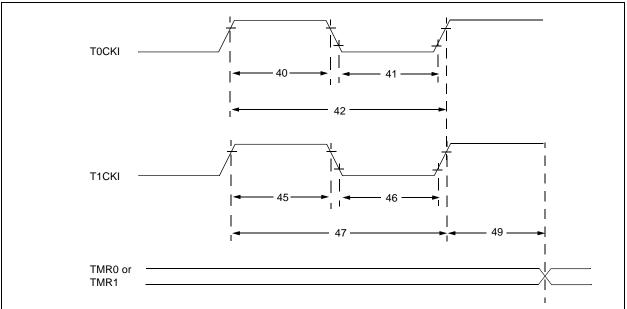

### 5.3 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 5.4 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. For simplicity, this counter will be referred to as "prescaler" throughout this Data Sheet. The prescaler assignment is controlled in software by the control bit PSA of the OPTION Register. Clearing the PSA bit will assign the prescaler to Timer0. Prescale values are selectable via the PS<2:0> bits of the OPTION Register.

The prescaler is not readable or writable. When assigned to the TimerO module, all instructions writing to the TMRO register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer.

### 5.4.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 5-1 and Example 5-2) must be executed when changing the prescaler assignment between Timer0 and WDT.

| EXAMPLE 5-1: | CHANGING PRESCALER |

|--------------|--------------------|

|              | (TIMER0→WDT)       |

|        |             | ,                    |

|--------|-------------|----------------------|

| BCF    | STATUS, RPO | ;Bank 0              |

| BCF    | STATUS, RP1 | ;                    |

| CLRWDT |             | ;Clear WDT           |

| CLRF   | TMR0        | ;Clear TMR0 and      |

|        |             | ; prescaler          |

| BSF    | STATUS, RPO | ;Bank 1              |

|        |             |                      |

| MOVLW  | b'00101111' | ;Required if desired |

| MOVWF  | OPTION_REG  | ; PS2:PS0 is         |

| CLRWDT |             | ; 000 or 001         |

|        |             | ;                    |

| MOVLW  | b'00101xxx' | ;Set postscaler to   |

| MOVWF  | OPTION_REG  | ; desired WDT rate   |

| BCF    | STATUS, RP0 | ;Bank 0              |

|        | •           |                      |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 5-2. This precaution must be taken even if the WDT is disabled.

# EXAMPLE 5-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | Clear WDT and   |

|--------|-------------|-----------------|

|        |             | ; prescaler     |

| BSF    | STATUS, RPO | ;Bank 1         |

| BCF    | STATUS, RP1 | ;               |

|        |             |                 |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0,   |

|        |             | ; prescale, and |

|        |             | ; clock source  |

| MOVWF  | OPTION_REG  | ;               |

| BCF    | STATUS, RPO | ;Bank 0         |

|        |             |                 |

#### TABLE 5-1: REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on all<br>other Resets |

|------------|------------------------|--------|--------|--------|--------|--------|--------|-----------|----------------------|------------------------------|

| ANSEL0     | ANS7                   | ANS6   | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0      | 1111 1111            | 1111 1111                    |

| INTCON     | GIE                    | PEIE   | TOIE   | INTE   | RAIE   | T0IF   | INTF   | RAIF      | 0000 0000            | 0000 0000                    |

| OPTION_REG | RAPU                   | INTEDG | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0       | 1111 1111            | 1111 1111                    |

| TMR0       | Timer0 Module Register |        |        |        |        |        |        | XXXX XXXX | uuuu uuuu            |                              |

| TRISA      | —                      | —      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0    | 11 1111              | 11 1111                      |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

## 6.5 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  of the T1CON Register is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | The ANSEL0 (91h) register must be initial- |  |  |  |

|-------|--------------------------------------------|--|--|--|

|       | ized to configure an analog channel as a   |  |  |  |

|       | digital input. Pins configured as analog   |  |  |  |

|       | inputs will read '0'.                      |  |  |  |

#### 6.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

## 6.6 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN of the T1CON Register. The oscillator is a low power oscillator rated for 32.768 kHz. It will continue to run during Sleep. It is primarily intended for a 32.768 kHz tuning fork crystal.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the primary system clock is also the LP oscillator or is derived from the internal oscillator. As with the system LP oscillator, the user must provide a software time delay to ensure proper oscillator start-up.

Sleep mode will not disable the system clock when the system clock and Timer1 share the LP oscillator.

TRISA<5> and TRISA<4> bits are set when the Timer1 oscillator is enabled. RA5 and RA4 read as '0' and TRISA<5> and TRISA<4> bits read as '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

## 6.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To setup the timer to wake the device:

- Timer1 of the T1CON Register must be on

- TMR1IE bit of the PIE1 Register must be set

- · PEIE bit of the INTCON Register must be set

The device will wake-up on an overflow. If the GIE bit of the INTCON Register is set, the device will wake-up and jump to the Interrupt Service Routine (0004h) on an overflow. If the GIE bit is clear, execution will continue with the next instruction.

| Bit 7                                                                       | Bit 6                                                         | Bit 5                                                                           | Bit 4                                                                                                                  | Bit 3                                                                                                                                                         | Bit 2                                                                                                                                                                                              | Bit 1                                                                                                                                                                                                                                    | Bit 0                                                                                                                                                                                | Value on<br>POR, BOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Value on all other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANS7                                                                        | ANS6                                                          | ANS5                                                                            | ANS4                                                                                                                   | ANS3                                                                                                                                                          | ANS2                                                                                                                                                                                               | ANS1                                                                                                                                                                                                                                     | ANS0                                                                                                                                                                                 | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MC10UT                                                                      | MC2OUT                                                        | —                                                                               | —                                                                                                                      | —                                                                                                                                                             | —                                                                                                                                                                                                  | T1GSS                                                                                                                                                                                                                                    | C2SYNC                                                                                                                                                                               | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GIE                                                                         | PEIE                                                          | TOIE                                                                            | INTE                                                                                                                   | RAIE                                                                                                                                                          | TOIF                                                                                                                                                                                               | INTF                                                                                                                                                                                                                                     | RAIF                                                                                                                                                                                 | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EEIE                                                                        | ADIE                                                          | CCP1IE                                                                          | C2IE                                                                                                                   | C1IE                                                                                                                                                          | OSFIE                                                                                                                                                                                              | TMR2IE                                                                                                                                                                                                                                   | TMR1IE                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EEIF                                                                        | ADIF                                                          | CCP1IF                                                                          | C2IF                                                                                                                   | C1IF                                                                                                                                                          | OSFIF                                                                                                                                                                                              | TMR2IF                                                                                                                                                                                                                                   | TMR1IF                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| T1GINV                                                                      | TMR1GE                                                        | T1CKPS1                                                                         | T1CKPS0                                                                                                                | T1OSCEN                                                                                                                                                       | T1SYNC                                                                                                                                                                                             | TMR1CS                                                                                                                                                                                                                                   | TMR1ON                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                                                               |                                                                                 |                                                                                                                        |                                                                                                                                                               |                                                                                                                                                                                                    | xxxx xxxx                                                                                                                                                                                                                                | uuuu uuuu                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |                                                               |                                                                                 |                                                                                                                        |                                                                                                                                                               |                                                                                                                                                                                                    |                                                                                                                                                                                                                                          | xxxx xxxx                                                                                                                                                                            | uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                             | ANS7<br>MC1OUT<br>GIE<br>EEIE<br>EEIF<br>T1GINV<br>Holding Re | ANS7ANS6MC1OUTMC2OUTGIEPEIEEEIEADIEEEIFADIFT1GINVTMR1GEHolding Register for the | ANS7ANS6ANS5MC1OUTMC2OUT—GIEPEIETOIEEEIEADIECCP1IEEEIFADIFCCP1IFT1GINVTMR1GET1CKPS1Holding Register for the Least Sign | ANS7ANS6ANS5ANS4MC1OUTMC2OUT——GIEPEIETOIEINTEEEIEADIECCP1IEC2IEEEIFADIFCCP1IFC2IFT1GINVTMR1GET1CKPS1T1CKPS0Holding Register for the Least Significant Byte of | ANS7ANS6ANS5ANS4ANS3MC1OUTMC2OUT———GIEPEIET0IEINTERAIEEEIEADIECCP1IEC2IEC1IEEEIFADIFCCP1IFC2IFC1IFT1GINVTMR1GET1CKPS1T1CKPS0T1OSCENHolding Register for the Least Significant Byte of the 16-bit T | ANS7ANS6ANS5ANS4ANS3ANS2MC1OUTMC2OUT—————GIEPEIETOIEINTERAIETOIFEEIEADIECCP1IEC2IEC1IEOSFIEEEIFADIFCCP1IFC2IFC1IFOSFIFT1GINVTMR1GET1CKPS1T1CKPS0T1OSCENT1SYNCHolding Register for the Least Significant Byte of the 16-bit TJR1 Register | ANS7ANS6ANS5ANS4ANS3ANS2ANS1MC1OUTMC2OUT————T1GSSGIEPEIET0IEINTERAIET0IFINTFEEIEADIECCP1IEC2IEC1IEOSFIETMR2IEEEIFADIFCCP1IFC2IFC1IFOSFIFTMR2IFT1GINVTMR1GET1CKPS0T1OSCENT1SYNCTMR1CS | ANS7         ANS6         ANS5         ANS4         ANS3         ANS2         ANS1         ANS0           MC1OUT         MC2OUT         —         —         —         —         T1GSS         C2SYNC           GIE         PEIE         T0IE         INTE         RAIE         T0IF         INTF         RAIF           EEIE         ADIE         CCP1IE         C2IE         C1IE         OSFIE         TMR2IE         TMR1IE           EEIF         ADIF         CCP1IF         C2IF         C1IF         OSFIF         TMR2IF         TMR1IF           T1GINV         TMR1GE         T1CKPS1         T1OSCEN         T1SYNC         TMR1CS         TMR1ON           Holding Rejister for the Least Significant Byte of the 16-bit TKT1 Register         TMR1CS         TMR1ON         TMR1CS         TMR1ON | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         POR, BOR           ANS7         ANS6         ANS5         ANS4         ANS3         ANS2         ANS1         ANS0         1111 1111           MC1OUT         MC2OUT         —         —         —         —         T1GSS         C2SYNC         0010           GIE         PEIE         T0IE         INTE         RAIE         T0IF         INTF         RAIF         0000 0000           EEIE         ADIE         CCP1IE         C2IE         C1IE         OSFIE         TMR2IE         TMR1IE         0000 0000           EEIF         ADIF         CCP1IF         C2IF         C1IF         OSFIF         TMR2IE         TMR1IE         0000 0000           T1GINV         TMR1GE         T1CKPS0         T1OSCEN         T1SYNC         TMR1ON         0000 0000           Holding Rejster for the Least Significant Byte of the 16-bit TWR1 Register         xxxx xxxxx         xxxx xxxxx |

TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER1

Legend: - x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

## 9.1.2.2 Control Register CM2CON1

Comparator C2 has one additional feature: its output can be synchronized to the Timer1 clock input. Setting C2SYNC of the CM2CON1 Register synchronizes the output of Comparator 2 to the falling edge of the Timer1 clock input (see Figure 9-2 and Register 9-3).

The CM2CON1 register also contains mirror copies of both comparator outputs, MC1OUT and MC2OUT of the CM2CON1 Register. The ability to read both outputs simultaneously from a single register eliminates the timing skew of reading separate registers.

**Note:** Obtaining the status of C1OUT or C2OUT by reading CM2CON1 does not affect the comparator interrupt mismatch registers.

### REGISTER 9-3: CM2CON1: COMPARATOR C2 CONTROL REGISTER 1

| R-0    | R-0    | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-0  |

|--------|--------|-----|-----|-----|-----|-------|--------|

| MC1OUT | MC2OUT | —   | —   | —   | —   | T1GSS | C2SYNC |

| bit 7  |        |     |     |     |     |       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 6 MC2OUT: Mirror Copy of C2OUT bit (CM2CON0<6>)

bit 5-2 Unimplemented: Read as '0'

- bit 1 T1GSS: Timer1 Gate Source Select bit

- 1 = Timer1 gate source is RA4/AN3/T1G/OSC2/CLKOUT

- 0 = Timer1 gate source is SYNCC2OUT.

- bit 0 C2SYNC: C2 Output Synchronous Mode bit

- 1 = C2 output is synchronous to falling edge of TMR1 clock

- 0 = C2 output is asynchronous

## 10.0 VOLTAGE REFERENCES

There are two voltage references available in the PIC16F785/HV785: The voltage referred to as the comparator reference (CVREF) is a variable voltage based on VDD; The voltage referred to as the VR reference (VR) is a fixed voltage derived from a stable band gap source. Each source may be individually routed internally to the comparators or output, buffered or unbuffered, on the RA1/AN1/C12IN0-/VREF/ICSPCLK pin.

## 10.1 Comparator Reference

The comparator module also allows the selection of an internally generated voltage reference for one of the comparator inputs. The VRCON register (Register 10-1) controls the voltage reference module shown in Figure 10-1.

# 10.1.1 CONFIGURING THE VOLTAGE REFERENCE

The voltage reference can output 32 distinct voltage levels, 16 in a high range and 16 in a low range.

The following equation determines the output voltages:

#### EQUATION 10-1: CVREF OUTPUT VOLTAGE

$$VRR = 1 (low range):$$

$$CVREF = VR < 3:0 > x VDD/24$$

$$VRR = 0 (high range):$$

$$CVREF = (VDD/4) + (VR < 3:0 > x VDD/32)$$

#### 10.1.2 VOLTAGE REFERENCE ACCURACY/ERROR

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 10-1) keep CVREF from approaching VSS or VDD. The exception is when the module is disabled by clearing all CVROE, C1VREN and C2VREN bits. When disabled with VR<3:0> = 0000 and VRR = 1 the reference voltage will be VSS. This allows the comparators to detect a zero-crossing and not consume CVREF module current.

The voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the comparator voltage reference can be found in Table 19-8.

## 12.2 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 12-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 12-4. **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . As the impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 12-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

## EQUATION 12-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega$  5.0V VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + Tc + TCOFF$

$$= 5\mu s + Tc + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

The value for Tc can be approximated with the following equations:

T

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad ;[1] V_{chold charged to within 1/2 lsb}$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{chold charge response to Vapplied}$$

$$V_{APPLIED}\left(1-e^{\frac{-1C}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{2047}\right) \quad ;Combining [1] and [2]$$

Solving for Tc:

$$Tc = -CHOLD(Ric + Rss + Rs) \ln(1/2047)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)

= 1.37\mus

e:

Therefore:

$$Tacq = 5\mu s + 1.37\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.62\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

| REGISTER 1    | 3-2: PWMC                                 | LK: PWM CL                                          |                    | TROL REGIS       | TER              |                 |       |

|---------------|-------------------------------------------|-----------------------------------------------------|--------------------|------------------|------------------|-----------------|-------|

| R/W-0         | R/W-0                                     | R/W-0                                               | R/W-0              | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| PWMASE        | PWMP1                                     | PWMP0                                               | PER4               | PER3             | PER2             | PER1            | PER0  |

| bit 7         |                                           |                                                     |                    |                  |                  |                 | bit ( |

| Legend:       |                                           |                                                     |                    |                  |                  |                 |       |

| R = Readable  | bit                                       | W = Writable                                        | bit                | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at | POR                                       | '1' = Bit is set                                    |                    | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|               |                                           |                                                     |                    |                  |                  |                 |       |

| bit 7         | 0 = PWM c                                 | WM Auto-Shuto<br>outputs are ope<br>down event has  | rating             |                  | inactive.        |                 |       |

| bit 6-5       | PWMP<1:0>:                                | PWM Clock P                                         | rescaler bits      |                  |                  |                 |       |

|               | 00 = pwm_c                                |                                                     |                    |                  |                  |                 |       |

|               |                                           | $lk = Fosc \div 2$                                  |                    |                  |                  |                 |       |

|               | $10 = pwm_c$                              |                                                     |                    |                  |                  |                 |       |

| 1.1.4.0       | •                                         | $k = Fosc \div 8$                                   |                    |                  |                  |                 |       |

| bit 4-0       | 00000 = Not<br>00001 = Per<br>0•••• = ••• | WM Period bits<br>used. (Period =<br>iod = 2/pwm_cl | = 1/pwm_clk)<br>k2 |                  |                  |                 |       |

|               | 10000 = Per<br>1•••• = •••                | iod = 17/pwm_                                       | clk                |                  |                  |                 |       |

|               |                                           | iod = 31/pwm_<br>iod = 32/pwm_                      |                    |                  |                  |                 |       |

## REGISTER 13-2: PWMCLK: PWM CLOCK CONTROL REGISTER

## 13.9 Complementary Output Mode

The Two-Phase PWM module may be configured to operate in a Complementary Output mode where PH1 and PH2 are always 180 degrees out-of-phase (see Figure 13-5). Three complementary modes are available and are selected by the COMOD<1:0> bits in the PWMCON1 register (see Register 13-5). The difference between the modes is the method by which the PH1 and PH2 outputs switch from the active to the inactive state during the PWM period.

In Complementary mode, there are three methods by which the duty cycle can be controlled. These modes are selected with the COMOD<1:0> bits (see Register 13-5). In each of these modes, the duty cycle is started when the pwm\_count = PWMPH1<4:0> and terminates on one of the following:

- Feedback through C1 or C2

- When the pwm\_count equals PWMPH1<4:0>

- · Combined feedback and pwm\_count match

When COMOD<1:0> = 01, the duty cycle is controlled only by feedback through comparator C1 or C2. In this mode, the active drive cycle starts when pwm\_count equals PWMPH1<4:0> and terminates when comparator C1's output goes high (if enabled by PWMPH1<5> = 1) or when comparator C2 output goes high (if enabled by PWMPH1<6> = 1).

When COMOD<1:0> = 10, the duty cycle is controlled only by the PWM Phase counter. In this mode, the active drive cycle starts when the pwm\_count equals PWMPH1<4:0> and terminates when the pwm\_count equals PWMPH2<4:0>. For example, free running 50% duty cycle can be accomplished by setting COMOD<1:0> = 10 and choosing appropriate values for PWMPH1<4:0> and PWMPH2<4:0>.

When COMOD<1:0> = 11, the duty cycle is controlled by the phase counter or feedback through comparator C1 or C2. For example, in this mode, the maximum duty cycle is determined by the values of PWMPH1<4:0> (duty cycle start) and PWMPH2<4:0> (duty cycle end). The duty cycle can be terminated earlier than the maximum by feedback through comparator C1 or C2.

#### 13.9.1 DEAD BAND CONTROL

The Complementary Output mode facilitates driving series connected MOSFET drivers by providing dead band drive timing between each phase output (see Figure 13-6). Dead band times are selectable by the CMDLY<4:0> bits of the PWMCON1 register. Delays from 0 to 155 nanoseconds (typical) with a resolution of 5 nanoseconds (typical) are available.

## 13.9.2 OVERLAP CONTROL

Overlap timing can be accomplished by configuring the Complementary mode for the desired output polarity and overlap time (as dead time) then swapping the output connections and inverting the outputs. For example, to configure a complementary drive for 55 ns of overlap and an active-high drive output on PH1 and an active-low drive output on PH2, set the PWM control registers as follows:

- Connect PH1 driver to PH2 output

- Connect PH2 driver to PH1 output

- Initialize PORTC<1> to 1 (PH2 driver off)

- Initialize PORTC<4> to 0 (PH1 driver off)

- Set TRISC<1,4> to 0 for output

- Set PWMPH1<POL> to 1 (Inverted PH1)

- Set PWMPH2<POL> to 1 (Non-Inverted PH2)

- Set PWMCON1 for 55 ns delay and desired termination (comparator, count or both)

- Set PWMCON0 desired SYNC and auto-shutdown configuration and to enable PH1 and PH2

#### 13.9.3 SHUTDOWN IN COMPLEMENTARY MODE

During shutdown the PH1 and PH2 complementary outputs are forced to their inactive states (see Figure 13-5). When shutdown ceases the PWM outputs revert to their start-up states for the first cycle which is PH1 inactive (output undriven) and PH2 active (output driven).

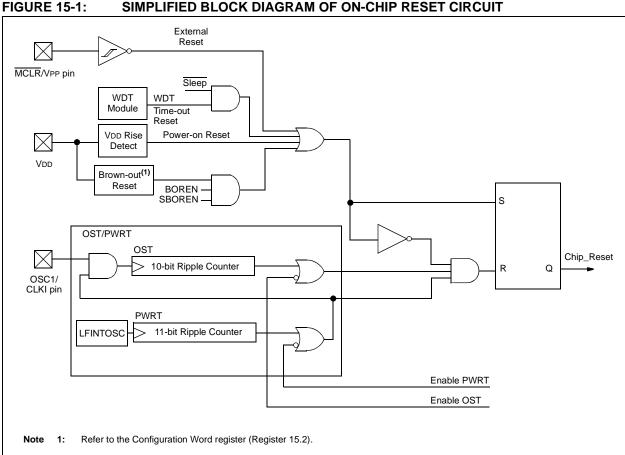

## 15.0 SPECIAL FEATURES OF THE CPU

The PIC16F785/HV785 has a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving features and offer code protection.

These features are:

- Reset:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Oscillator selection

- Sleep

- Code protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

The PIC16F785/HV785 has two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Power-up Timer to provide at least a 64 ms Reset. With these three functions on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through an external Reset, Watchdog Timer Wake-up or interrupt.

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options (see Register 15.2).

## 15.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 15.2. These bits are mapped in program memory location 2007h.

Note: Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See "*PIC16F785/HV785 Memory Programming Specification*" (DS41237) for more information.

#### 15.2 Reset

The PIC16F785/HV785 differentiates between various kinds of Reset:

- Power-on Reset (POR)

- · WDT Reset during normal operation

- WDT Reset during Sleep

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

#### They are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 15-2. These bits are used in software to determine the nature of the Reset. See Table 15-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 15-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Section 19.0 "Electrical Specifications" for pulse width specifications.

#### SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| IABLE 15-4: |         |                      | ON FOR REGISTER                                           | Wake-up from Sleep through interrupt    |

|-------------|---------|----------------------|-----------------------------------------------------------|-----------------------------------------|

| Register    | Address | Power-on Reset       | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through WDT Time-out |

| W           | —       | xxxx xxxx            | uuuu uuuu                                                 | սսսս սսսս                               |

| INDF        | 00h/80h | xxxx xxxx            | xxxx xxxx                                                 | սսսս սսսս                               |

| TMR0        | 01h     | xxxx xxxx            | uuuu uuuu                                                 | սսսս սսսս                               |

| PCL         | 02h/82h | 0000 0000            | 0000 0000                                                 | PC + 1 <sup>(3)</sup>                   |

| STATUS      | 03h/83h | 0001 1xxx            | 000q quuu <sup>(4)</sup>                                  | uuuq quuu <sup>(4)</sup>                |

| FSR         | 04h/84h | xxxx xxxx            | uuuu uuuu                                                 | սսսս սսսս                               |

| PORTA       | 05h     | x0 x000 <b>(6)</b>   | u0 u000 <sup>(7)</sup>                                    | uu uuuu                                 |

| PORTB       | 06h     | xx00(6)              | uu00 <sup>(7)</sup>                                       | uuuu                                    |

| PORTC       | 07h     | 00xx 0000 <b>(6)</b> | 00uu uuuu <sup>(7)</sup>                                  | սսսս սսսս                               |

| PCLATH      | 0Ah/8Ah | 0 0000               | 0 0000                                                    | u uuuu                                  |

| INTCON      | 0Bh/8Bh | 0000 0000            | 0000 0000                                                 | uuuu uuuu <sup>(2)</sup>                |

| PIR1        | 0Ch     | 0000 0000            | 0000 0000                                                 | uuuu uuuu <sup>(2)</sup>                |

| TMR1L       | 0Eh     | xxxx xxxx            | uuuu uuuu                                                 | սսսս սսսս                               |

| TMR1H       | 0Fh     | xxxx xxxx            | uuuu uuuu                                                 | սսսս սսսս                               |

| T1CON       | 10h     | 0000 0000            | uuuu uuuu                                                 | սսսս սսսս                               |

| TMR2        | 11h     | 0000 0000            | 0000 0000                                                 | սսսս սսսս                               |

| T2CON       | 12h     | -000 0000            | -000 0000                                                 | -uuu uuuu                               |

| CCPR1L      | 13h     | xxxx xxxx            | uuuu uuuu                                                 | սսսս սսսս                               |