Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv785-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

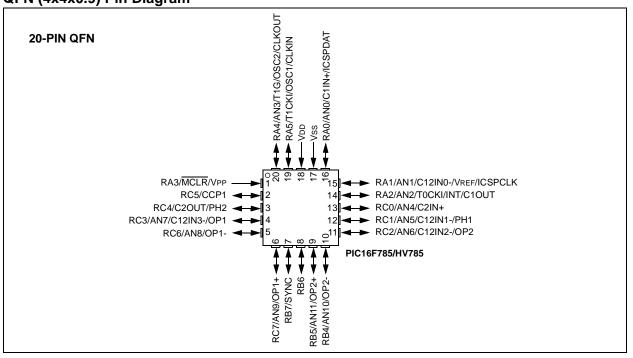

## QFN (4x4x0.9) Pin Diagram

#### TABLE 2: QFN PIN SUMMARY

| I/O                | Pin | Analog   | Comp.   | Op<br>Amps | PWM  | Timers | ССР  | Interrupt | Pull-ups | Basic       |

|--------------------|-----|----------|---------|------------|------|--------|------|-----------|----------|-------------|

| RA0                | 16  | AN0      | C1IN+   | —          | _    | —      | _    | IOC       | Y        | ICSPDAT     |

| RA1                | 15  | AN1/VREF | C12IN0- |            |      | —      |      | IOC       | Y        | ICSPCLK     |

| RA2                | 14  | AN2      | C1OUT   |            | _    | T0CKI  | _    | INT/IOC   | Y        | —           |

| RA3 <sup>(1)</sup> | 1   | _        | _       | _          | _    | _      | _    | IOC       | Y        | MCLR/Vpp    |

| RA4                | 20  | AN3      | —       | _          | _    | T1G    | _    | IOC       | Y        | OSC2/CLKOUT |

| RA5                | 19  | —        | —       | _          | _    | T1CKI  | _    | IOC       | Y        | OSC1/CLKIN  |

| RB4                | 10  | AN10     | —       | OP2-       | _    | —      | —    | _         | —        | —           |

| RB5                | 9   | AN11     | _       | OP2+       |      | —      |      |           | _        | —           |

| RB6 <sup>(2)</sup> | 8   | —        | —       | —          | —    | —      | —    | —         | —        | —           |

| RB7                | 7   | —        | _       |            | SYNC | —      |      |           | _        | —           |

| RC0                | 13  | AN4      | C2IN+   |            | _    | —      | _    | _         | —        | —           |

| RC1                | 12  | AN5      | C12IN1- |            | PH1  | —      | _    | -         | —        | —           |

| RC2                | 11  | AN6      | C12IN2- | OP2        | _    | —      | _    | _         | _        | —           |

| RC3                | 4   | AN7      | C12IN3- | OP1        |      | —      |      |           | _        | —           |

| RC4                | 3   | —        | C2OUT   |            | PH2  | —      | _    | —         | —        | —           |

| RC5                | 2   | —        | _       |            |      | —      | CCP1 |           | _        | —           |

| RC6                | 5   | AN8      |         | OP1-       | _    |        |      | _         | _        | —           |

| RC7                | 6   | AN9      | —       | OP1+       | —    | —      | _    | —         | _        | —           |

| _                  | 18  |          |         | _          | _    | —      | _    | —         | _        | Vdd         |

| _                  | 17  | _        | _       |            | _    | _      | _    | _         |          | Vss         |

Note 1: Input only.

2: Open drain.

#### 2.2.2.2 OPTION\_REG Register

The Option register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RA2/INT interrupt, the TMR0 and the weak pull-ups on PORTA.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT by setting PSA bit to '1' in the OPTION Register. See Section 5.4 "Prescaler".

#### REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RAPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       | •     |       |       | bit 0 |

| Legend:    |                |                                                      |                                                                             |                                                           |                                      |                    |

|------------|----------------|------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------|--------------------|

| R = Reada  | ble bit        | W = W                                                | ritable bit                                                                 | U =                                                       | Unimplemented bi                     | t, read as '0'     |

| -n = Value | at POR         | '1' = B                                              | t is set                                                                    | 'O' =                                                     | Bit is cleared                       | x = Bit is unknown |

| bit 7      |                |                                                      |                                                                             |                                                           |                                      |                    |

|            | 0 <b>= POR</b> | TA pull-ups a                                        | are enabled b                                                               | oy individual p                                           | ort latch values in                  | WPUA register      |

| bit 6      | INTEDG         | : Interrupt Ec                                       | lge Select bit                                                              | t                                                         |                                      |                    |

|            |                |                                                      | •                                                                           |                                                           | /INT/C1OUT pin<br>/INT/C1OUT pin     |                    |

| bit 5      |                | MR0 Clock S                                          |                                                                             | t bit<br>/INT/C1OUT                                       | nin                                  |                    |

|            |                | nal instructio                                       |                                                                             |                                                           |                                      |                    |

| bit 4      | TOSE: T        | MR0 Source                                           | Edge Select                                                                 | bit                                                       |                                      |                    |

|            |                | •                                                    |                                                                             |                                                           | /AN2/T0CKI/INT/C<br>/AN2/T0CKI/INT/C | •                  |

| bit 3      | PSA: Pro       | escaler Assig                                        | nment bit                                                                   |                                                           |                                      |                    |

|            |                | caler is assig                                       |                                                                             | /DT<br>imer0 module                                       |                                      |                    |

| bit 2-0    | PS<2:0>        | : Prescaler F                                        | Rate Select b                                                               | its                                                       |                                      |                    |

|            |                | Bit Value                                            | TMR0 Rate                                                                   | WDT Rate <sup>(1)</sup>                                   | 1                                    |                    |

|            |                | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256 | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128 |                                      |                    |

Note 1: A dedicated 16-bit WDT postscaler is available for the PIC16F785/HV785. See Section 15.5 "Watchdog Timer (WDT)" for more information.

### 3.2 Clock Source Modes

Clock Source modes can be classified as external or internal.

- External Clock modes rely on external circuitry for the clock source. Examples are oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT, and HS modes) and resistorcapacitor (RC mode) circuits.

- Internal clock sources are contained internally within the PIC16F785/HV785. The PIC16F785/ HV785 has two internal oscillators; the 8 MHz High-frequency Internal Oscillator (HFINTOSC) and 31 kHz Low-frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS) bit (see **Section 3.5 "Clock Switching**").

#### 3.3 External Clock Modes

#### 3.3.1 OSCILLATOR START-UP TIMER (OST)

When the PIC16F785/HV785 is configured for any of the Crystal Oscillator modes (LP, XT or HS), the Oscillator Start-up Timer (OST) is enabled, which extends the Reset period to allow the oscillator additional time to stabilize. The OST counts 1024 clock periods present on the OSC1 pin following a Power-on Reset (POR), a wake from Sleep, or when the Power-up Timer (PWRT) has expired (if the PWRT is enabled). During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the PIC16F785/HV785. Table 3-1 shows examples where the oscillator delay is invoked.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section 3.6 "Two-Speed Clock Start-up Mode"**).

| Switch From          | Switch<br>To    | Frequency               | Oscillator Delay                                    | Comments                                                                         |  |  |  |

|----------------------|-----------------|-------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| Sleep/POR            | INTRC<br>INTOSC | 31 kHz<br>125 kHz-8 MHz | 5 μs-10 μs (approx.)<br>CPU Start-up <sup>(1)</sup> | Following a wake-up from Sleep mode or POR, CPU start-up is invoked to allow the |  |  |  |

| Sleep                | EC, RC          | DC – 20 MHz             |                                                     | CPU to become ready for code execution.                                          |  |  |  |

| LFINTOSC<br>(31 kHz) | EC, RC          | DC – 20 MHz             |                                                     |                                                                                  |  |  |  |

| Sleep/POR            | LP, XT,<br>HS   | 31 kHz-20 MHz           | 1024 Clock Cycles<br>(OST)                          |                                                                                  |  |  |  |

| LFINTOSC<br>(31 kHz) | INTOSC          | 125 kHz-8 MHz           | 1 μs (approx.)                                      |                                                                                  |  |  |  |

#### TABLE 3-1: OSCILLATOR DELAY EXAMPLES

**Note 1:** The 5 μs-10 μs start-up delay is based on a 1 MHz System Clock.

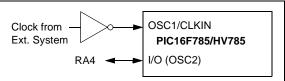

#### 3.3.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to OSC1 pin and the RA4 pin is available for general purpose I/O. Figure 3-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC16F785/HV785 design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

## FIGURE 3-2:

#### EXTERNAL CLOCK (EC) MODE OPERATION

#### 3.7.1 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, the execution of a SLEEP instruction, or a modification of the SCS bit. While in Fail-Safe condition, the PIC16F785/HV785 uses the internal oscillator as the system clock source. The IRCF bits in the OSCCON Register can be modified to adjust the internal oscillator frequency without exiting the Fail-Safe condition.

The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

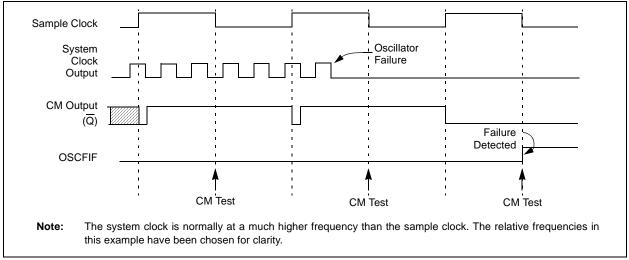

#### FIGURE 3-9: FSCM TIMING DIAGRAM

#### 3.7.2 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited a Reset or Sleep condition and the Oscillator Start-up Timer (OST) has expired. If the external clock is EC or RC mode, monitoring will begin immediately following these events.

For LP, XT or HS mode, the external oscillator may require a start-up time considerably longer than the FSCM sample clock time; a false clock failure may be detected (see Figure 3-9). To prevent this, the internal oscillator is automatically configured as the system clock and functions until the external clock is stable (the OST has timed out). This is identical to Two-Speed Start-up mode. Once the external oscillator is stable, the LFINTOSC returns to its role as the FSCM source.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit in the OSCCON Register to verify the oscillator start-up and system clock switchover has successfully completed.

#### 8.3.3 OPERATION IN SLEEP MODE

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the RC5/CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state.

## 8.3.3.1 OPERATION WITH FAIL-SAFE CLOCK MONITOR

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the CCP to be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See **Section 3.0** "**Clock Sources**" for additional details.

#### 8.3.4 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 8.3.5 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Configure the PWM pin (RC5/CCP1) as an input by setting the TRISC<5> bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- 4. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 5. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit of the PIR1 Register.

- Set the TMR2 prescale value by loading the T2CKPS bits of the T2CON Register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON Register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until TMR2 overflows (TMR2IF bit is set).

- Enable the RC5/CCP1 pin output by clearing the TRISC<5> bit.

| Name    | Bit 7                  | Bit 6       | Bit 5        | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|---------|------------------------|-------------|--------------|-----------|---------|--------|---------|-----------|----------------------|---------------------------|

| CCP1CON | -                      | —           | DC1B1        | DC1B0     | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0    | 0000 0000            | 0000 0000                 |

| CCPR1L  | Capture/C              | ompare/PWI  | V Register 1 | Low Byte  |         |        |         |           | XXXX XXXX            | uuuu uuuu                 |

| CCPR1H  | Capture/C              | ompare/PWI  | V Register 1 | High Byte |         |        |         |           | XXXX XXXX            | uuuu uuuu                 |

| INTCON  | GIE                    | PEIE        | TOIE         | INTE      | RAIE    | TOIF   | INTF    | RAIF      | 0000 0000            | 0000 0000                 |

| PIE1    | EEIE                   | ADIE        | CCP1IE       | C2IE      | C1IE    | OSFIE  | TMR2IE  | TMR1IE    | 0000 0000            | 0000 0000                 |

| PIR1    | EEIF                   | ADIF        | CCP1IF       | C2IF      | C1IF    | OSFIF  | TMR2IF  | TMR1IF    | 0000 0000            | 0000 0000                 |

| PR2     | Timer2 Mo              | dule Period | Register     |           |         |        |         |           | 1111 1111            | 1111 1111                 |

| T2CON   | -                      | TOUTPS3     | TOUTPS2      | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0   | -000 0000            | -000 0000                 |

| TMR2    | Timer2 Module Register |             |              |           |         |        |         | 0000 0000 | 0000 0000            |                           |

| TRISC   | TRISC7                 | TRISC6      | TRISC5       | TRISC4    | TRISC3  | TRISC2 | TRISC1  | TRISC0    | 11 1111              | 11 1111                   |

#### TABLE 8-4:REGISTERS ASSOCIATED WITH CCP AND TIMER2

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the CCP or Timer2 modules.

#### 9.2 Comparator Outputs

The comparator outputs are read through the CM1CON0, COM2CON0 or CM2CON1 registers. CM1CON0 and CM2CON0 each contain the individual comparator output of Comparator 1 and Comparator 2, respectively. CM2CON2 contains a mirror copy of both comparator outputs facilitating a simultaneous read of both comparators. These bits are read-only. The comparator outputs may also be directly output to the RA2/AN2/T0CKI/INT/C1OUT and RC4/C2OUT/PH2

I/O pins. When enabled, multiplexers in the output path of the RA2 and RC4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 9-1 and Figure 9-2 show the output block diagrams for Comparators 1 and 2, respectively.

The TRIS bits will still function as an output enable/ disable for the RA2/AN2/T0CKI/INT/C1OUT and RC4/ C2OUT/PH2 pins while in this mode.

The polarity of the comparator outputs can be changed using the C1POL and C2POL bits of the CMxCON0 Register.

Timer1 gate source can be configured to use the T1G pin or Comparator 2 output as selected by the T1GSS bit of the CM2CON1 Register. The Timer1 gate feature can be used to time the duration or interval of analog events. The output of Comparator 2 can also be synchronized with Timer1 by setting the C2SYNC bit of the CM2CON1 Register. When enabled, the output of Comparator 2 is latched on the falling edge of the Timer1 clock source. If a prescaler is used with Timer1, Comparator 2 is latched after the prescaler. To prevent a race condition, the Comparator 2 output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator 2 Block Diagram (Figure 9-2) and the Timer1 Block Diagram (Figure 6-1) for more information.

It is recommended to synchronize Comparator 2 with Timer1 by setting the C2SYNC bit when Comparator 2 is used as the Timer1 gate source. This ensures Timer1 does not miss an increment if Comparator 2 changes during an increment.

#### 9.3 Comparator Interrupts

The comparator interrupt flags are set whenever there is a change in the output value of its respective comparator. Software will need to maintain information about the status of the output bits, as read from CM2CON0<7:6>, to determine the actual change that has occurred. The CxIF bits, PIR1<4:3>, are the Comparator Interrupt Flags. Each comparator interrupt bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CxIE bits of the PIE1 Register and the PEIE bit of the INTCON Register must be set to enable the interrupts. In addition, the GIE bit must also be set. If any of these bits are cleared, the interrupt is not enabled, though the CxIF bits will still be set if an interrupt condition occurs.

The comparator interrupt of the PIC16F785/HV785 differs from previous designs in that the interrupt flag is set by the mismatch edge and not the mismatch level. This means that the interrupt flag can be reset without the additional step of reading or writing the CMxCON0 register to clear the mismatch registers. When the mismatch registers are not cleared, an interrupt will not occur when the comparator output returns to the previous state. When the mismatch registers are cleared, an interrupt will occur when the comparator returns to the previous state.

| Note 1: | If a change in the CMxCON0 register<br>(CxOUT) should occur when a read<br>operation is being executed (start of the<br>Q2 cycle), then the CxIF of the PIR1 Reg-<br>ister interrupt flag may not get set.                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When either comparator is first enabled, bias circuitry in the Comparator module may cause an invalid output from the comparator until the bias circuitry is stable. Allow about 1 $\mu$ s for bias settling then clear the mismatch condition and interrupt flags before enabling comparator interrupts. |

#### 9.4 Effects of Reset

A Reset forces all registers to their Reset state. This disables both comparators.

## 13.0 TWO-PHASE PWM

The two-phase PWM (Pulse Width Modulator) is a stand-alone peripheral that supports:

- Single or dual-phase PWM

- Single complementary output PWM with overlap/ delay

- Sync input/output to cascade devices for additional phases

Setting either, or both, of the PH1EN or PH2EN bits of the PWMCON0 register will activate the PWM module (see Register 13-1). If PH1 is used then TRISC<1> must be cleared to configure the pin as an output. The same is true for TRISC<4> when using PH2. Both PH1EN and PH2EN must be set when using Complementary mode.

#### 13.1 PWM Period

The PWM period is derived from the main clock (Fosc), the PWM prescaler and the period counter (see Figure 13-1). The prescale bits of the PWMP Register, (see Register 13-2) determine the value of the clock divider which divides the system clock (Fosc) to the pwm\_clk. This pwm\_clk is used to drive the PWM counter. In Master mode, the PWM counter is reset when the count reaches the period count of the PER Register, (see Register 13-2), which determines the frequency of the PWM. The relationship between the PWM frequency, prescale and period count is shown in Equation 13-1.

#### EQUATION 13-1: PWM FREQUENCY

$$PWM_{FREQ} = \frac{FOSC}{(2^{PWMP} \cdot (PER + 1))}$$

The maximum PWM frequency is Fosc/2, since the period count must be greater than zero.

In Slave mode, the period counter is reset by the SYNC input, which is the master device period counter reset. For proper operation, the slave period count should be equal to or greater than that of the master.

## 13.2 PWM Phase

Each enabled phase output is driven active when the phase counter matches the corresponding PWM phase count in the PH Register (see Register 13-3 and Register 13-4). The phase output remains true until terminated by a feedback signal from either of the comparators or the auto-shutdown activates.

Phase granularity is a function of the period count value. For example, if PER<4:0> = 3, each output can be shifted in 90° steps (see Equation 13-2).

#### EQUATION 13-2: PHASE RESOLUTION

$Phase_{DEG} = \frac{360}{(PER+1)}$

## 13.3 PWM Duty Cycle

Each PWM output is driven inactive, terminating the drive period, by asynchronous feedback through the internal comparators. The duty cycle resolution is in effect infinitely adjustable. Either or both comparators can be used to reset the PWM by setting the corresponding comparator enable bit (CxEN, see Register 13-3). Duty cycles of 100% can be obtained by suppressing the feedback which would otherwise terminate the pulse.

The comparator outputs can be "held off", or blanked, by enabling the corresponding BLANK bit (BLANKx, see Register 13-1) for each phase. The blank bit disables the comparator outputs for 1/2 of a system clock (Fosc), thus ensuring at least Tosc/2 active time for the PWM output. Blanking avoids early termination of the PWM output which may result due to switching transients at the beginning of the cycle.

## 13.4 Master/Slave Operation

Multiple chips can operate together to achieve additional phases by operating one as the master and the others as slaves. When the PWM is configured as a master, the RB7/SYNC pin is an output and generates a high output for one pwm\_clk period at the end of each PWM period (see Figure 13-4).

When the PWM is configured as a slave, the RB7/ SYNC pin is an input. The high input from a master in this configuration resets the PWM period counter which synchronizes the slave unit at the end of each PWM period. Proper operation of a slave device requires a common external FOSC clock source to drive the master and slave. The PWM prescale value of the slave device must also be identical to that of the master. As mentioned previously, the slave period count value must be greater than or equal to that of the master.

The PWM Counter will be reset and held at zero when both PH1EN and PH2EN of the PWMCON0 Register are false. If the PWM is configured as a slave, the PWM Counter will remain reset at zero until the first SYNC input is received.

| REGISTER     | K 13-3: PWMF      | PH1: PWM PI                                             | HASE 1 CO                                              |                    | STER             |                   |                |

|--------------|-------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------|------------------|-------------------|----------------|

| R/W-0        | R/W-0             | R/W-0                                                   | R/W-0                                                  | R/W-0              | R/W-0            | R/W-0             | R/W-0          |

| POL          | C2EN              | C1EN                                                    | PH4                                                    | PH3                | PH2              | PH1               | PH0            |

| bit 7        |                   |                                                         |                                                        |                    |                  |                   | bit            |

| Legend:      |                   |                                                         |                                                        |                    |                  |                   |                |

| R = Readal   | ble bit           | W = Writable                                            | bit                                                    | U = Unimplen       | nented bit, rea  | d as '0'          |                |

| -n = Value a |                   | '1' = Bit is set                                        |                                                        | 0' = Bit is clear  |                  | x = Bit is unkr   | nown           |

|              |                   |                                                         |                                                        |                    |                  |                   | IOWIT          |

| bit 7        | <b>POL:</b> PH1 O | utput Polarity b                                        | it                                                     |                    |                  |                   |                |

|              | 1 = PH1 Pin       | -                                                       |                                                        |                    |                  |                   |                |

|              |                   | is active-high                                          |                                                        |                    |                  |                   |                |

| bit 6        |                   | parator 2 Enabl                                         | e bit                                                  |                    |                  |                   |                |

|              |                   | $D < 1:0 > = 00^{(1)}$                                  |                                                        |                    |                  |                   |                |

|              |                   | is reset when                                           |                                                        | hiah               |                  |                   |                |

|              |                   | l ignores Comp                                          |                                                        | 5                  |                  |                   |                |

|              | When COMC         | <u>)D&lt;1:0&gt; = X1</u> (1                            | )                                                      |                    |                  |                   |                |

|              |                   |                                                         |                                                        | when C2OUT         | goes high        |                   |                |

|              |                   | nparator 2 is ig                                        |                                                        |                    |                  |                   |                |

|              |                   | <u>)D&lt;1:0&gt; = 10</u> <sup>(1</sup><br>as no effect | )                                                      |                    |                  |                   |                |

| bit 5        |                   | parator 1 Enabl                                         | e bit                                                  |                    |                  |                   |                |

|              |                   | $D < 1:0 > = 00^{(1)}$                                  |                                                        |                    |                  |                   |                |

|              |                   | is reset when                                           |                                                        | hiah               |                  |                   |                |

|              | 0 = PH1           | l ignores Comp                                          | parator 1                                              | 0                  |                  |                   |                |

|              |                   | $D = X1^{(1)}$                                          |                                                        |                    |                  |                   |                |

|              |                   |                                                         |                                                        | when C1OUT         | goes high        |                   |                |

|              |                   | nparator 1 is ig                                        |                                                        |                    |                  |                   |                |

|              |                   | $D < 1:0 > = 10^{(1)}$                                  | ,                                                      |                    |                  |                   |                |

| 1 1 4 9      |                   | as no effect                                            |                                                        |                    |                  |                   |                |

| bit 4-0      |                   | VM Phase bits<br>)D<1:0> = 0.0 <sup>(1</sup>            | <b>`</b>                                               |                    |                  |                   |                |

|              |                   |                                                         |                                                        | d ofter falling or | dag of SVNC p    | ulse. All other P |                |

|              | 00000 =           | expressed rela                                          | -                                                      | -                  | lige of Strike p | uise. All other F | TTT uelays al  |

|              | 00001 =           | PH1 is delaye                                           |                                                        |                    |                  |                   |                |

|              | •••••=            | •                                                       |                                                        | ···· [- •·· • •    |                  |                   |                |

|              | 11111 =           | PH1 is delaye                                           | d by 31 pwm_                                           | _clk pulses        |                  |                   |                |

|              | When COMC         | $D_{-1} = x_1$                                          | v 1 v(1)                                               |                    |                  |                   |                |

|              | 00000 =           |                                                         |                                                        |                    |                  |                   |                |

|              | 00000 -           |                                                         | ry drive starts                                        |                    | od after falling | edge of SYNC p    | oulse. All oth |

|              |                   | Complementa<br>delays are exp                           | ry drive starts<br>pressed relativ                     |                    |                  |                   | oulse. All oth |

|              | 00001 =           | Complementa<br>delays are exp<br>Complementa            | ry drive starts<br>pressed relativ<br>ry drive start i | e to this time.    | pwm_clk pulse    | 9                 | oulse. All oth |

#### 14.2 Reading the EEPROM Data Memory

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD of the EECON1 Register, as shown in Example 14-1. The data is available, in the very next cycle, in the EEDAT register. Therefore, it can be read in the next instruction. EEDAT holds this value until another read, or until it is written to by the user (during a write operation).

| EXAMPLE 14-1:            | DATA EEPROM READ |

|--------------------------|------------------|

| $\Box A A W F L \Box 14$ |                  |

| BSF   | STATUS, RPO | ;Bank 1          |

|-------|-------------|------------------|

| BCF   | STATUS, RP1 | ;                |

| MOVLW | CONFIG_ADDR | ;                |

| MOVWF | EEADR       | ;Address to read |

| BSF   | EECON1,RD   | ;EE Read         |

| MOVF  | EEDAT,W     | ;Move data to W  |

|       |             |                  |

### 14.3 Writing to the EEPROM Data Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDAT register. Then the user must follow a specific sequence to initiate the write for each byte, as shown in Example 14-2.

| EXAMPLE 14-2: | DATA EEPROM WRITE |

|---------------|-------------------|

| $\Box$        |                   |

|          | BSF   | STATUS, RPO | ;Bank 1          |

|----------|-------|-------------|------------------|

|          | BCF   | STATUS, RP1 | ;                |

|          | BSF   | EECON1,WREN | ;Enable write    |

|          | BCF   | INTCON,GIE  | ;Disable INTs    |

|          | BTFSC | INTCON,GIE  | ;See AN-576      |

|          | GOTO  | \$-2        | ;                |

|          | MOVLW | 55h         | ;Unlock write    |

| e eg     | MOVWF | EECON2      | ;                |

| Required | MOVLW | AAh         | ;                |

| ed       | MOVWF | EECON2      | ;                |

| щ        | BSF   | EECON1,WR   | ;Start the write |

|          | BSF   | INTCON,GIE  | ;Enable INTs     |

|          |       |             |                  |

The write will not initiate if the sequence in Example 14-2 is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment. A cycle count is executed during the required sequence. Any number that is not equal to the required cycles to execute the required sequence will prevent the data from being written into the EEPROM.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware. After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in the hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. The EEIF bit of the PIR1 Register must be cleared by software.

## 14.4 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM should be verified (see Example 14-3) to the desired value to be written.

| EXAMPLE | 14-3: | WRITE | VERIFY |

|---------|-------|-------|--------|

|         |       |       |        |

| BSF   | STATUS, RPO | ;Bank 1             |

|-------|-------------|---------------------|

| BCF   | STATUS, RP1 | ;                   |

| MOVF  | EEDAT,W     | ;EEDAT not changed  |

|       |             | from previous write |

| BSF   | EECON1,RD   | ;YES, Read the      |

|       |             | ; value written     |

| XORWF | EEDAT,W     | ;                   |

| BTFSS | STATUS, Z   | ;Is data the same   |

| GOTO  | WRITE_ERR   | ;No, handle error   |

|       |             | ;Yes, continue      |

|       |             |                     |

### 14.4.1 USING THE DATA EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM (specification D124) without exceeding the total number of write cycles to a single byte (specifications D120 and D120A). If this is the case, then a refresh of the array must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

## 14.5 Protect Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit helps prevent an accidental write during a brown-out, power glitch and software malfunction.

| TABLE 15-4: | INITIALIZATION CONDITION FOR REGISTERS (CONTINUED) |                |                                                           |                                                                                 |  |  |  |  |  |

|-------------|----------------------------------------------------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|

| Register    | Address                                            | Power-on Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through interrupt<br>Wake-up from Sleep through WDT Time-out |  |  |  |  |  |

| VRCON       | 99h                                                | 000- 0000      | 000- 0000                                                 | uuu- uuuu                                                                       |  |  |  |  |  |

| EEDAT       | 9Ah                                                | 0000 0000      | 0000 0000                                                 | <u>uuuu</u> uuuu                                                                |  |  |  |  |  |

| EEADR       | 9Bh                                                | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                       |  |  |  |  |  |

| EECON1      | 9Ch                                                | x000           | q000                                                      | uuuu                                                                            |  |  |  |  |  |

| EECON2      | 9Dh                                                |                |                                                           |                                                                                 |  |  |  |  |  |

| ADRESL      | 9Eh                                                | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                       |  |  |  |  |  |

| ADCON1      | 9Fh                                                | -000           | -000                                                      | -uuu                                                                            |  |  |  |  |  |

| PWMCON1     | 110h                                               | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                       |  |  |  |  |  |

| PWMCON0     | 111h                                               | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                       |  |  |  |  |  |

| PWMCLK      | 112h                                               | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                       |  |  |  |  |  |

| PWMPH1      | 113h                                               | 0000 0000      | 0000 0000                                                 | <u>uuuu</u> uuuu                                                                |  |  |  |  |  |

| PWMPH2      | 114h                                               | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                       |  |  |  |  |  |

| CM1CON0     | 119h                                               | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                       |  |  |  |  |  |

| CM2CON0     | 11Ah                                               | 0000 0000      | 0000 0000                                                 | นนนน นนนน                                                                       |  |  |  |  |  |

| CM2CON1     | 11Bh                                               | 0010           | 0010                                                      | uuuu                                                                            |  |  |  |  |  |

| OPA1CON     | 11Ch                                               | 0              | 0                                                         | u                                                                               |  |  |  |  |  |

| OPA2CON     | 11Dh                                               | 0              | 0                                                         | u                                                                               |  |  |  |  |  |

|             |                                                    |                |                                                           |                                                                                 |  |  |  |  |  |

#### TABLE 15-4: INITIALIZATION CONDITION FOR REGISTERS (CONTINUED)

$\label{eq:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:loge$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 15-5 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

6: Analog channels read 0 but data latches are unknown.

7: Analog channels read 0 but data latches are unchanged.

#### 15.3 Interrupts

The PIC16F785/HV785 has 11 sources of interrupt:

- External Interrupt RA2/INT

- TMR0 Overflow Interrupt

- PORTA Change Interrupt

- 2 Comparator Interrupts

- A/D Interrupt

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt

- EEPROM Data Write Interrupt

- Fail-Safe Clock Monitor Interrupt

- CCP Interrupt

The Interrupt Control register (INTCON) and Peripheral Interrupt register (PIR1) record individual interrupt requests in flag bits. The INTCON register also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE of the INTCON Register enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register and PIE1 register. GIE is cleared on Reset.

The Return from Interrupt instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INT-CON register:

- INT Pin Interrupt

- PORTA Change Interrupt

- TMR0 Overflow Interrupt

The peripheral interrupt flags are contained in the special register PIR1. The corresponding interrupt enable bit is contained in special register PIE1.

The following interrupt flags are contained in the PIR1 register:

- EEPROM Data Write Interrupt

- A/D Interrupt

- 2 Comparator Interrupts

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt

- Fail-Safe Clock Monitor Interrupt

- CCP Interrupt

When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt

- The return address is PUSHed onto the stack

- The PC is loaded with 0004h

For external interrupt events, such as the INT pin or PORTA change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 15-8). The latency is the same for one or twocycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts, which were ignored, are still pending to be serviced when the GIE bit is set again.

For additional information on Timer1, Timer2, comparators, A/D, Data EEPROM or CCP modules, refer to the respective peripheral section.

RA0

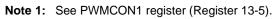

### 15.10 In-Circuit Debugger

\* Isolation devices (as required)

To Normal

Connections

Data I/O

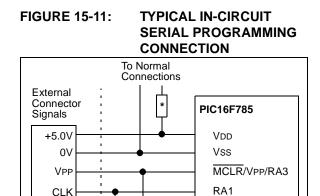

- In-circuit debugging requires clock, data and MCLR pins. A special 28-pin PIC16F785-ICD device is used with MPLAB<sup>®</sup> ICD 2 to provide separate clock, data and MCLR pins so that no pins are lost for these functions, leaving all 18 of the PIC16F785/HV785 I/O pins available to the user during debug operation.

- This special ICD device is mounted on the top of a header and its signals are routed to the MPLAB ICD 2 connector. On the bottom of the header is a 20-pin socket that plugs into the user's target via the 20-pin stand-off connector.

- When the ICD pin on the PIC16F785-ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 15-9 shows which features are consumed by the background debugger.

#### TABLE 15-9: DEBUGGER RESOURCES

| Resource       | Description                         |

|----------------|-------------------------------------|

| I/O pins       | ICDCLK, ICDDATA                     |

| Stack          | 1 level                             |

| Data RAM       | 65h-70h, F0h                        |

| Program Memory | Address 0h must be NOP<br>700h-7FFh |

For more information, see "*MPLAB*<sup>®</sup> *ICD 2 In-Circuit Debugger User's Guide*" (DS51331), available on Microchip's web site (www.microchip.com).

#### FIGURE 15-12: 28-PIN ICD PINOUT

| RETFIE           | Return from Interrupt                                                                |                                                             |                                                     |                          |  |  |

|------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------|--------------------------|--|--|

| Syntax:          | [ label ]                                                                            | RETFIE                                                      |                                                     |                          |  |  |

| Operands:        | None                                                                                 |                                                             |                                                     |                          |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                           |                                                             |                                                     |                          |  |  |

| Status Affected: | None                                                                                 |                                                             |                                                     |                          |  |  |

| Encoding:        | 00                                                                                   | 0000                                                        | 0000                                                | 1001                     |  |  |

| Description:     | Return fro<br>POPed a<br>is loaded<br>enabled b<br>Interrupt<br>INTCON<br>cycle inst | nd Top-c<br>in the P(<br>by setting<br>Enable b<br>Register | of-Stack (<br>C. Interru<br>g Global<br>oit, GIE ol | TOS)<br>pts are<br>f the |  |  |

| RLF              | Rotate L                                                                           | eft f thr                                        | ough Ca                                               | rry                       |  |  |

|------------------|------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------|---------------------------|--|--|

| Syntax:          | [ label ]                                                                          | RLF                                              | f,d                                                   |                           |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                     | 27                                               |                                                       |                           |  |  |

| Operation:       | See description below                                                              |                                                  |                                                       |                           |  |  |

| Status Affected: | С                                                                                  |                                                  |                                                       |                           |  |  |

| Encoding:        | 00                                                                                 | 1101                                             | dfff                                                  | ffff                      |  |  |

| Description:     | The content<br>rotated o<br>the Carry<br>result is p<br>If 'd' is '1<br>back in re | ne bit to<br>Flag. If<br>blaced ir<br>', the res | the left th<br>'d' is '0',<br>the W re<br>sult is sto | nrough<br>the<br>egister. |  |  |

C 🚽

Register f

RETLW **Return with Literal in W** Syntax: [label] RETLW k  $0 \le k \le 255$ Operands: Operation:  $k \rightarrow (W);$  $\mathsf{TOS}\to\mathsf{PC}$ Status Affected: None 11 01xx kkkk Encoding: kkkk The W register is loaded with Description: the eight-bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a two-cycle instruction.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                         |   |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                      |   |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                      |   |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                |   |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |   |  |  |  |  |

| Encoding:        | 00 1100 dfff ffff                                                                                                                                                                                                    |   |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right<br>through the Carry Flag. If 'd' is<br>'0', the result is placed in the W<br>register. If 'd' is '1' the result is<br>placed back in register 'f'. | 1 |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                             |

| Operands:        | None                                                                                                                                                       |

| Operation:       | $TOS\toPC$                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                       |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |

| SLEEP            | Go into Standby mode                                                                                                                                                    |                                                               |                                                                         |                           |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------|--|--|

| Syntax:          | [ <i>labe</i> l]                                                                                                                                                        | SLEE                                                          | Р                                                                       |                           |  |  |

| Operands:        | None                                                                                                                                                                    |                                                               |                                                                         |                           |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{W}DT \text{ prescaler,} \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$ |                                                               |                                                                         |                           |  |  |

| Status Affected: | TO, PD                                                                                                                                                                  |                                                               |                                                                         |                           |  |  |

| Encoding:        | 00                                                                                                                                                                      | 0000                                                          | 0110                                                                    | 0011                      |  |  |

| Description:     | is clear<br>TO is se<br>its pres<br>The pro                                                                                                                             | ed. Time<br>et. Watch<br>caler are<br>ocessor i<br>vith the c | n Status<br>out Stat<br>ndog Tim<br>cleared<br>s put into<br>oscillator | tus bit,<br>ier and<br>I. |  |  |

## 18.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

### 18.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## **19.0 ELECTRICAL SPECIFICATIONS**

#### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bies                                                                                    | 40 to 1125°C                |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Ambient temperature under bias                                                                                    | 40 t0 +125 C                |

| Storage temperature                                                                                               | 65°C to +150°C              |

| Voltage on VDD with respect to Vss                                                                                |                             |

| Voltage on MCLR with respect to Vss                                                                               | 0.3 to +13.5V               |

| Voltage on RB6 open-drain pin with respect to Vss                                                                 | 0.3 to +8.5V                |

| Voltage on all other pins with respect to Vss                                                                     | 0.3V to (VDD + 0.3V)        |

| Total power dissipation <sup>(1)</sup> (PDIP and SOIC)                                                            | 800 mW                      |

| Total power dissipation <sup>(1)</sup> (SSOP)                                                                     | 600 mW                      |

| Maximum current out of Vss pin                                                                                    |                             |

| Maximum current into VDD pin                                                                                      | 250 mA                      |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                      | ±20 mA                      |

| Output clamp current, loк (Vo < 0 or Vo >VDD)                                                                     |                             |

| Maximum output current sunk by any I/O pin                                                                        | 25 mA                       |

| Maximum output current sourced by any I/O pin                                                                     | 25 mA                       |

| Maximum current sunk by PORTA, PORTB, and PORTC (combined)                                                        | 200 mA                      |

| Maximum current sourced PORTA, PORTB, and PORTC (combined)                                                        | 200 mA                      |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD $-V$ | ЭН) х ЮН} + $∑$ (VOI х ЮL). |

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Note:** Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin, rather than pulling this pin directly to Vss.

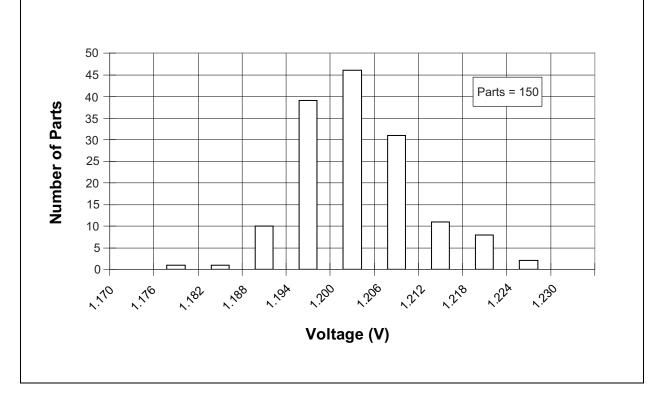

## 19.2 DC Characteristics: PIC16F785/HV785-I (Industrial)<sup>(1), (2)</sup>

| DC CHA                        | ARACTERISTICS          | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |      |       |            |                    |

|-------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--------------------|

| Param Device Observatoriation |                        |                                                                                                                                        |      |      |       | Conditions |                    |

| No.                           | Device Characteristics | Min                                                                                                                                    | Тур† | Max  | Units | Vdd        |                    |

| D010                          | Supply Current (IDD)   | —                                                                                                                                      | 11   | 23   | μA    | 2.0        | Fosc = 32 kHz      |

|                               |                        | —                                                                                                                                      | 18   | 38   | μΑ    | 3.0        | LP Oscillator mode |

|                               |                        | —                                                                                                                                      | 35   | 75   | μA    | 5.0        |                    |

| D011                          |                        | —                                                                                                                                      | 140  | 240  | μA    | 2.0        | Fosc = 1 MHz       |

|                               |                        | —                                                                                                                                      | 220  | 380  | μA    | 3.0        | XT Oscillator mode |

|                               |                        | —                                                                                                                                      | 380  | 550  | μA    | 5.0        | 7                  |

| D012                          |                        | —                                                                                                                                      | 260  | 360  | μΑ    | 2.0        | Fosc = 4 MHz       |

|                               |                        |                                                                                                                                        | 420  | 650  | μΑ    | 3.0        | XT Oscillator mode |

|                               |                        | _                                                                                                                                      | 0.8  | 1.1  | mA    | 5.0        |                    |

| D013                          |                        | —                                                                                                                                      | 130  | 220  | μΑ    | 2.0        | Fosc = 1 MHz       |

|                               |                        |                                                                                                                                        | 215  | 360  | μΑ    | 3.0        | EC Oscillator mode |

|                               |                        | _                                                                                                                                      | 360  | 520  | μA    | 5.0        |                    |