## Microchip Technology - PIC16HV785-I/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv785-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                       | 5   |

|-------|-------------------------------------------------------|-----|

| 2.0   | Memory Organization                                   | 9   |

| 3.0   | Clock Sources                                         | 23  |

| 4.0   | I/O Ports                                             | 35  |

| 5.0   | Timer0 Module                                         | 49  |

| 6.0   | Timer1 Module with Gate Control                       | 51  |

| 7.0   | Timer2 Module                                         | 55  |

| 8.0   | Capture/Compare/PWM (CCP) Module                      | 57  |

| 9.0   | Comparator Module                                     |     |

| 10.0  | Voltage References                                    | 70  |

| 11.0  | Operational Amplifier (OPA) Module                    | 75  |

| 12.0  | Analog-to-Digital Converter (A/D) Module              | 79  |

| 13.0  | Two-Phase PWM                                         | 91  |

| 14.0  | Data EEPROM Memory                                    | 103 |

| 15.0  | Special Features of the CPU                           | 107 |

| 16.0  | Voltage Regulator                                     | 126 |

| 17.0  | Instruction Set Summary                               |     |

| 18.0  | Development Support                                   | 137 |

| 19.0  | Electrical Specifications                             | 141 |

|       | DC and AC Characteristics Graphs and Tables           |     |

| 21.0  | Packaging Information                                 | 187 |

|       | ndix A: Data Sheet Revision History                   |     |

| Appe  | ndix B: Migrating from other PIC <sup>®</sup> Devices | 193 |

| Index |                                                       | 195 |

| The N | /icrochip Web Site                                    | 201 |

| Custo | mer Change Notification Service                       | 201 |

| Custo | mer Support                                           | 201 |

|       | er Response                                           | -   |

| Produ | Ict Identification System                             | 203 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 2.2.2.4 PIE1 Register

The Peripheral Interrupt Enable Register 1 contains the interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

## REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  |

|-------|-------|--------|-------|-------|-------|--------|--------|

| EEIE  | ADIE  | CCP1IE | C2IE  | C1IE  | OSFIE | TMR2IE | TMR1IE |

| bit 7 |       |        |       |       |       |        | bit 0  |

| Legend:         |                |                                                                                                          |                       |                    |

|-----------------|----------------|----------------------------------------------------------------------------------------------------------|-----------------------|--------------------|

| R = Readable    | bit            | W = Writable bit                                                                                         | U = Unimplemented bit | , read as '0'      |

| -n = Value at I | POR            | '1' = Bit is set                                                                                         | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7           | EEIE: E        | E Write Complete Interrupt E                                                                             | nable bit             |                    |

|                 |                | bles the EE write complete in<br>ables the EE write complete in                                          | •                     |                    |

| bit 6           | 1 <b>= Ena</b> | VD Converter Interrupt Enable<br>bles the A/D converter interru<br>ables the A/D converter interru       | pt                    |                    |

| bit 5           | 1 = Ena        | : CCP1 Interrupt Enable bit<br>bles the CCP1 interrupt<br>ables the CCP1 interrupt                       |                       |                    |

| bit 4           | 1 = Ena        | comparator 2 Interrupt Enable<br>bles the Comparator 2 interru<br>ables the Comparator 2 interru         | pt                    |                    |

| bit 3           | 1 = Ena        | comparator 1 Interrupt Enable<br>bles the Comparator 1 interru<br>ables the Comparator 1 interru         | pt                    |                    |

| bit 2           | 1 = Ena        | Oscillator Fail Interrupt Enabl<br>bles the Oscillator Fail interru<br>ables the Oscillator Fail interru | pt                    |                    |

| bit 1           | 1 = Ena        | Timer2 to PR2 Match Interro<br>bles the Timer2 to PR2 match<br>ables the Timer2 to PR2 matc              | n interrupt           |                    |

| bit 0           | 1 = Ena        | Timer1 Overflow Interrupt E<br>bles the Timer1 overflow inter<br>ables the Timer1 overflow inter         | rupt                  |                    |

## 3.4 Internal Clock Modes

The PIC16F785/HV785 has two independent, internal oscillators that can be configured or selected as the system clock source.

- The HFINTOSC (High-frequency Internal Oscillator) is factory calibrated and operates at 8 MHz. The frequency of the HFINTOSC can be user adjusted ±12% via software using the OSCTUNE register (Register 3-1).

- The LFINTOSC (Low-frequency Internal Oscillator) is uncalibrated and operates at approximately 31 kHz.

The system clock speed can be selected via software using the Internal Oscillator Frequency Select (IRCF) bits.

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS) bit (see **Section 3.5 "Clock Switching**").

## 3.4.1 INTRC AND INTRCIO MODES

The INTRC and INTRCIO modes configure the internal oscillators as the system clock source when the device is programmed using the Oscillator Selection (FOSC) bits in the Configuration Word (Register 12-1).

In **INTRC** mode, the OSC1 pin is available for general purpose I/O. The OSC2/CLKOUT pin outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTRCIO** mode, the OSC1 and OSC2 pins are available for general purpose I/O.

#### 3.4.2 HFINTOSC

The High-frequency Internal Oscillator (HFINTOSC) is a factory calibrated 8 MHz internal clock source. The frequency of the HFINTOSC can be altered approximately  $\pm 12\%$  via software using the OSCTUNE register (Register 3-1).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). One of seven frequencies can be selected via software using the IRCF bits (see **Section 3.4.4** "**Frequency Select Bits** (**IRCF**)").

The HFINTOSC is enabled by selecting any frequency between 8 MHz and 125 kHz (IRCF  $\neq$  000) as the system clock source (SCS = 1) or when Two-Speed Start-up is enabled (IESO = 1 and IRCF  $\neq$  000).

The HF Internal Oscillator (HTS) bit, in the OSCCON Register, indicates whether the HFINTOSC is stable or not.

## 3.4.2.1 Calibration Bits

The 8 MHz High-frequency Internal Oscillator (HFIN-TOSC) is factory calibrated. The HFINTOSC calibration bits are stored in the Calibration Word (CALIB) located in program memory location 2008h. The Calibration Word is not erased using the specified bulk erase sequence in the "*PIC16F785/HV785 Memory Programming Specification*" (DS41237) and does not require reprogramming. Reference the "*PIC16F785/ HV785 Memory Programming Specification*" (DS41237) for more information on the Calibration Word register.

Note: Address 2008h is beyond the user program memory space. It belongs to the special Configuration Memory space (2000h-3FFFh), which can be accessed only during programming. See "*PIC16F785/HV785 Memory Programming Specification*" (DS41237) for more information.

## 3.5 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bit.

## 3.5.1 SYSTEM CLOCK SELECT (SCS) BIT

The System Clock Select (SCS) bit, in the OSCCON Register, selects the system clock source that is used for the CPU and peripherals.

- When SCS = 0, the system clock source is determined by configuration of the FOSC<2:0> bits in Configuration Word (CONFIG).

- When SCS = 1, the system clock source is chosen by the internal oscillator frequency selected by the IRCF bits. After a Reset, SCS is always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bit. The user can monitor the OSTS (OSCCON<3>) to determine the current system clock source.

#### 3.5.2 OSCILLATOR START-UP TIME-OUT STATUS BIT

The Oscillator Start-up Time-out Status (OSTS) bit, (OSCCON<3>), indicates whether the system clock is running from the external clock source as defined by the FOSC bits, or from internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

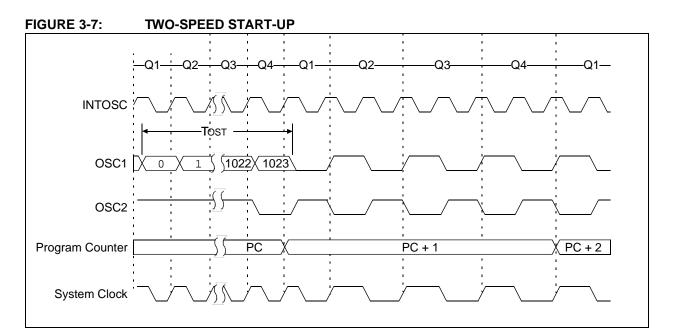

## 3.6 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the Oscillator Start-up Time and will cause the OSTS bit in the OSCCON Register to remain clear. When the PIC16F785/HV785 is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 3.3.1 "Oscillator Start-up Timer (OST)**"). The OST timer will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit in the OSCCON Register is set, program execution switches to the external oscillator.

## 3.6.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO = 1 (CONFIG<10>) Internal/External Switch Over bit.

- SCS = 0.

- Fosc configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after PWRT has expired, or

- Wake-up from Sleep.

If the external clock oscillator is configured to be anything other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

#### 3.6.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF bits (in the OSCCON Register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

## 3.6.3 CHECKING EXTERNAL/INTERNAL CLOCK STATUS

Checking the state of the OSTS bit in the OSCCON Register) will confirm if the PIC16F785/HV785 is running from the external clock source as defined by the Fosc bits in the Configuration Word (CONFIG) or the internal oscillator.

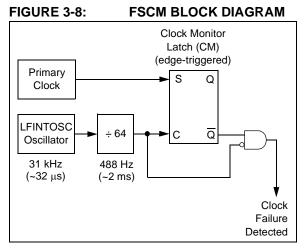

## 3.7 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) is designed to allow the device to continue to operate in the event of an oscillator failure. The FSCM can detect oscillator failure at any point after the device has exited a Reset or Sleep condition and the Oscillator Start-up Timer (OST) has expired.

The FSCM function is enabled by setting the FCMEN bit in Configuration Word (CONFIG). It is applicable to all external clock options (LP, XT, HS, EC, RC or I/O modes).

In the event of an external clock failure, the FSCM will set the OSFIF bit in the PIR1 Register and generate an oscillator fail interrupt if the OSFIE bit in the PIE1 Register is set. The device will then switch the system clock to the internal oscillator. The system clock will continue to come from the internal oscillator unless the external clock recovers and the Fail-Safe condition is exited. The frequency of the internal oscillator will depend upon the value contained in the IRCF bits (OSCCON<6:4>). Upon entering the Fail-Safe condition, the OSTS bit in the OSCCON Register is automatically cleared to reflect that the internal oscillator is active and the WDT is cleared. The SCS bit in the OSC-CON Register is not updated. Enabling FSCM does not affect the LTS bit.

The FSCM sample clock is generated by dividing the LFINTOSC clock by 64. This will allow enough time between FSCM sample clocks for a system clock edge to occur. Figure 3-8 shows the FSCM block diagram.

On the rising edge of the sample clock, the monitoring latch (CM = 0) will be cleared. On a falling edge of the primary system clock, the monitoring latch will be set (CM = 1). In the event that a falling edge of the sample clock occurs, and the monitoring latch is not set, a clock failure has been detected. The assigned internal oscillator is enabled when FSCM is enabled as reflected by the IRCF bits.

Note: Two-Speed Start-up is automatically enabled when the Fail-Safe Clock Monitor mode is enabled.

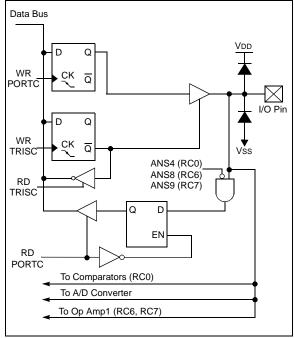

## 4.4 PORTC and TRISC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 4-8). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin). Example 4-3 shows how to initialize PORTC.

Reading the PORTC register (Register 4-7) reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the port data latch.

The TRISC register controls the direction of the PORTC pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

When RC4 or RC5 is configured as an op amp output, the corresponding RC4 or RC5 digital output driver will automatically be disabled regardless of the TRISC<4> or TRISC<5> value.

| Note: | The ANSEL0 (91h) and ANSEL1 (93h)          |

|-------|--------------------------------------------|

|       | registers must be initialized to configure |

|       | an analog channel as a digital input. Pins |

|       | configured as analog inputs will read '0'. |

| EXAMPLE 4-3: | INITIALIZING PORTC |

|--------------|--------------------|

|              |                    |

| BCF   | STATUS, RPO | ;Bank 0                |

|-------|-------------|------------------------|

| BCF   | STATUS, RP1 |                        |

| CLRF  | PORTC       | ;Init PORTC            |

| BSF   | STATUS, RPO | ;Bank 1                |

| CLRF  | ANSEL0      | ;digital I/O           |

| CLRF  | ANSEL1      | ;digital I/O           |

| MOVLW | 0Ch         | ;Set RC<3:2> as inputs |

| MOVWF | TRISC       | ; and set RC<5:4,1:0>  |

|       |             | ; as outputs           |

| BCF   | STATUS, RPO | ;Bank 0                |

#### **REGISTER 4-7: PORTC: PORTC REGISTER**

| R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x | R/W-x | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|----------------------|----------------------|-------|-------|----------------------|----------------------|----------------------|----------------------|

| RC7                  | RC6                  | RC5   | RC4   | RC3                  | RC2                  | RC1                  | RC0                  |

| bit 7                |                      |       |       |                      |                      |                      | bit 0                |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0

**RC<7:0>:** PORTC General Purpose I/O Pin bits 1 = Port pin is greater than VIH

- 0 = Port pin is less than VIL

- **Note 1:** Data latches are unknown after a POR, but each port bit reads '0' when the corresponding analog select bit is '1' (see Registers 12-1 and 12-2 on page 82).

#### REGISTER 4-8: TRISC: PORTC TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0

- TRISC<7:0>: PORTC Tri-State Control bits

- 1 = PORTC pin configured as an input (tri-stated)

- 0 = PORTC pin configured as an output

### 4.4.1 PORTC PIN DESCRIPTIONS AND DIAGRAMS

Each PORTC pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the comparator or the A/D, refer to the appropriate section in this Data Sheet.

## 4.4.1.1 RC0/AN4/C2IN+

The RC0 is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D Converter

- Non-inverting input to Comparator 2

## 4.4.1.2 RC6/AN8/OP1-

The RC6/AN8/OP1- pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D

- Inverting input for Op Amp 1

## 4.4.1.3 RC7/AN9/OP1+

The RC7/AN9/OP1+ pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D

- Non-inverting input for Op Amp 1

## FIGURE 4-10: BLOCK DIAGRAM OF RC0, RC6 AND RC7

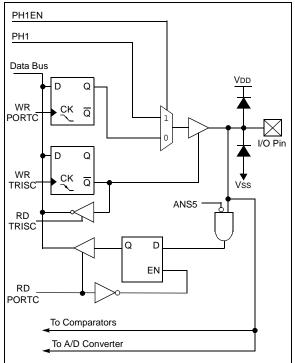

## 4.4.1.4 RC1/AN5/C12IN1-/PH1

The RC1 is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D Converter

- Analog input to Comparators 1 and 2

- Digital output from the Two-Phase PWM

## FIGURE 4-11: BLOCK DIAGRAM OF RC1

## 13.0 TWO-PHASE PWM

The two-phase PWM (Pulse Width Modulator) is a stand-alone peripheral that supports:

- Single or dual-phase PWM

- Single complementary output PWM with overlap/ delay

- Sync input/output to cascade devices for additional phases

Setting either, or both, of the PH1EN or PH2EN bits of the PWMCON0 register will activate the PWM module (see Register 13-1). If PH1 is used then TRISC<1> must be cleared to configure the pin as an output. The same is true for TRISC<4> when using PH2. Both PH1EN and PH2EN must be set when using Complementary mode.

## 13.1 PWM Period

The PWM period is derived from the main clock (Fosc), the PWM prescaler and the period counter (see Figure 13-1). The prescale bits of the PWMP Register, (see Register 13-2) determine the value of the clock divider which divides the system clock (Fosc) to the pwm\_clk. This pwm\_clk is used to drive the PWM counter. In Master mode, the PWM counter is reset when the count reaches the period count of the PER Register, (see Register 13-2), which determines the frequency of the PWM. The relationship between the PWM frequency, prescale and period count is shown in Equation 13-1.

## EQUATION 13-1: PWM FREQUENCY

$$PWM_{FREQ} = \frac{FOSC}{(2^{PWMP} \cdot (PER + 1))}$$

The maximum PWM frequency is Fosc/2, since the period count must be greater than zero.

In Slave mode, the period counter is reset by the SYNC input, which is the master device period counter reset. For proper operation, the slave period count should be equal to or greater than that of the master.

## 13.2 PWM Phase

Each enabled phase output is driven active when the phase counter matches the corresponding PWM phase count in the PH Register (see Register 13-3 and Register 13-4). The phase output remains true until terminated by a feedback signal from either of the comparators or the auto-shutdown activates.

Phase granularity is a function of the period count value. For example, if PER<4:0> = 3, each output can be shifted in 90° steps (see Equation 13-2).

## EQUATION 13-2: PHASE RESOLUTION

$Phase_{DEG} = \frac{360}{(PER+1)}$

## 13.3 PWM Duty Cycle

Each PWM output is driven inactive, terminating the drive period, by asynchronous feedback through the internal comparators. The duty cycle resolution is in effect infinitely adjustable. Either or both comparators can be used to reset the PWM by setting the corresponding comparator enable bit (CxEN, see Register 13-3). Duty cycles of 100% can be obtained by suppressing the feedback which would otherwise terminate the pulse.

The comparator outputs can be "held off", or blanked, by enabling the corresponding BLANK bit (BLANKx, see Register 13-1) for each phase. The blank bit disables the comparator outputs for 1/2 of a system clock (Fosc), thus ensuring at least Tosc/2 active time for the PWM output. Blanking avoids early termination of the PWM output which may result due to switching transients at the beginning of the cycle.

## 13.4 Master/Slave Operation

Multiple chips can operate together to achieve additional phases by operating one as the master and the others as slaves. When the PWM is configured as a master, the RB7/SYNC pin is an output and generates a high output for one pwm\_clk period at the end of each PWM period (see Figure 13-4).

When the PWM is configured as a slave, the RB7/ SYNC pin is an input. The high input from a master in this configuration resets the PWM period counter which synchronizes the slave unit at the end of each PWM period. Proper operation of a slave device requires a common external FOSC clock source to drive the master and slave. The PWM prescale value of the slave device must also be identical to that of the master. As mentioned previously, the slave period count value must be greater than or equal to that of the master.

The PWM Counter will be reset and held at zero when both PH1EN and PH2EN of the PWMCON0 Register are false. If the PWM is configured as a slave, the PWM Counter will remain reset at zero until the first SYNC input is received.

# PIC16F785/HV785

| REGISTER 1    | 3-2: PWMC                                 | LK: PWM CL                                          |                    | TROL REGIS       | TER              |                 |       |

|---------------|-------------------------------------------|-----------------------------------------------------|--------------------|------------------|------------------|-----------------|-------|

| R/W-0         | R/W-0                                     | R/W-0                                               | R/W-0              | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| PWMASE PWMP   |                                           | PWMP0                                               | PER4               | PER3             | PER2             | PER1            | PER0  |

| bit 7         |                                           |                                                     |                    |                  |                  |                 | bit ( |

| Legend:       |                                           |                                                     |                    |                  |                  |                 |       |

| R = Readable  | bit                                       | W = Writable                                        | bit                | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at | POR                                       | '1' = Bit is set                                    |                    | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|               |                                           |                                                     |                    |                  |                  |                 |       |

| bit 7         | 0 = PWM c                                 | WM Auto-Shuto<br>outputs are ope<br>down event has  | rating             |                  | inactive.        |                 |       |

| bit 6-5       | PWMP<1:0>:                                | PWM Clock P                                         | rescaler bits      |                  |                  |                 |       |

|               | 00 = pwm_c                                |                                                     |                    |                  |                  |                 |       |

|               |                                           | $lk = Fosc \div 2$                                  |                    |                  |                  |                 |       |

|               | $10 = pwm_c$                              |                                                     |                    |                  |                  |                 |       |

| 1.1.4.0       | •                                         | $k = Fosc \div 8$                                   |                    |                  |                  |                 |       |

| bit 4-0       | 00000 = Not<br>00001 = Per<br>0•••• = ••• | WM Period bits<br>used. (Period =<br>iod = 2/pwm_cl | = 1/pwm_clk)<br>k2 |                  |                  |                 |       |

|               | 10000 = Per<br>1•••• = •••                | iod = 17/pwm_                                       | clk                |                  |                  |                 |       |

|               |                                           | iod = 31/pwm_<br>iod = 32/pwm_                      |                    |                  |                  |                 |       |

## REGISTER 13-2: PWMCLK: PWM CLOCK CONTROL REGISTER

# PIC16F785/HV785

| REGISTER  | R 13-3: PWMF                                            | 'H1: PWM P                                              | HASE 1 CO                                              | NTROL REGI                         | STER              |                   |                |  |  |  |  |

|-----------|---------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|------------------------------------|-------------------|-------------------|----------------|--|--|--|--|

| R/W-0     | R/W-0                                                   | R/W-0                                                   | R/W-0                                                  | R/W-0                              | R/W-0             | R/W-0             | R/W-0          |  |  |  |  |

| POL       | C2EN                                                    | C1EN                                                    | PH4                                                    | PH3                                | PH2               | PH1               | PH0            |  |  |  |  |

| bit 7     |                                                         |                                                         |                                                        |                                    |                   |                   | bit            |  |  |  |  |

| Legend:   |                                                         |                                                         |                                                        |                                    |                   |                   |                |  |  |  |  |

| R = Reada | ble bit                                                 | W = Writable                                            | bit                                                    | U = Unimpler                       | nented bit_rea    | d as '0'          |                |  |  |  |  |

|           |                                                         |                                                         | x = Bit is unkr                                        | NOWD                               |                   |                   |                |  |  |  |  |

|           |                                                         | 1 = Dit 13 36                                           |                                                        |                                    | area              |                   | IOWIT          |  |  |  |  |

| bit 7     | POL: PH1 O                                              | utput Polarity b                                        | it                                                     |                                    |                   |                   |                |  |  |  |  |

|           | 1 = PH1 Pin                                             | -                                                       |                                                        |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | is active-high                                          |                                                        |                                    |                   |                   |                |  |  |  |  |

| bit 6     |                                                         | arator 2 Enabl                                          | e bit                                                  |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | $D < 1:0 > = 00^{(1)}$                                  |                                                        |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | is reset when                                           |                                                        | hiah                               |                   |                   |                |  |  |  |  |

|           |                                                         | ignores Comp                                            |                                                        | 5                                  |                   |                   |                |  |  |  |  |

|           | When COMC                                               | <u>D&lt;1:0&gt; = X1</u> (1                             | )                                                      |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | 1 = Complementary drive terminates when C2OUT goes high |                                                        |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | 0 = Comparator 2 is ignored                             |                                                        |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | 0 <u>D&lt;1:0&gt; = 10</u> (1<br>is no effect           | )                                                      |                                    |                   |                   |                |  |  |  |  |

| bit 5     |                                                         | arator 1 Enabl                                          | e bit                                                  |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | $D < 1:0 > = 00^{(1)}$                                  |                                                        |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | is reset when                                           |                                                        | hiah                               |                   |                   |                |  |  |  |  |

|           | 0 = PH1                                                 | ignores Comp                                            | parator 1                                              | 0                                  |                   |                   |                |  |  |  |  |

|           |                                                         | When COMOD<1:0> = $x1^{(1)}$                            |                                                        |                                    |                   |                   |                |  |  |  |  |

|           | 1 = Complementary drive terminates when C1OUT goes high |                                                         |                                                        |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | parator 1 is ig                                         |                                                        |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | $D < 1:0 > = 10^{(1)}$                                  | )                                                      |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | is no effect                                            |                                                        |                                    |                   |                   |                |  |  |  |  |

| bit 4-0   |                                                         | M Phase bits                                            | <b>、</b>                                               |                                    |                   |                   |                |  |  |  |  |

|           |                                                         | $D < 1:0 > = 00^{(1)}$                                  |                                                        |                                    |                   |                   |                |  |  |  |  |

|           | 00000 =                                                 |                                                         | -                                                      | -                                  | age of SYNC p     | ulse. All other P | 'H1 delays ai  |  |  |  |  |

|           | 00001 -                                                 | expressed relation PH1 is delayed                       |                                                        |                                    |                   |                   |                |  |  |  |  |

|           | •••••=                                                  | •                                                       | aby i pwii_c                                           |                                    |                   |                   |                |  |  |  |  |

|           | 11111 =                                                 | PH1 is delaye                                           | d by 31 pwm                                            | clk pulses                         |                   |                   |                |  |  |  |  |

|           | When COMC                                               | <u>D&lt;1:0&gt; = X1 c</u>                              | or 1x <sup>(1)</sup>                                   |                                    |                   |                   |                |  |  |  |  |

|           | 00000 =                                                 |                                                         |                                                        |                                    |                   |                   |                |  |  |  |  |

|           |                                                         |                                                         | ry drive starts                                        | 1 pwm_clk peri<br>/e to this time. | iod after falling | edge of SYNC p    | oulse. All oth |  |  |  |  |

|           | 00001 =                                                 | delays are exp                                          | ry drive starts<br>pressed relativ                     |                                    |                   |                   | oulse. All oth |  |  |  |  |

|           | •••• =                                                  | delays are exp<br>Complementa                           | ry drive starts<br>pressed relativ<br>ry drive start i | e to this time.                    | pwm_clk pulse     | 9                 | oulse. All oth |  |  |  |  |

## 13.9 Complementary Output Mode

The Two-Phase PWM module may be configured to operate in a Complementary Output mode where PH1 and PH2 are always 180 degrees out-of-phase (see Figure 13-5). Three complementary modes are available and are selected by the COMOD<1:0> bits in the PWMCON1 register (see Register 13-5). The difference between the modes is the method by which the PH1 and PH2 outputs switch from the active to the inactive state during the PWM period.

In Complementary mode, there are three methods by which the duty cycle can be controlled. These modes are selected with the COMOD<1:0> bits (see Register 13-5). In each of these modes, the duty cycle is started when the pwm\_count = PWMPH1<4:0> and terminates on one of the following:

- Feedback through C1 or C2

- When the pwm\_count equals PWMPH1<4:0>

- · Combined feedback and pwm\_count match

When COMOD<1:0> = 01, the duty cycle is controlled only by feedback through comparator C1 or C2. In this mode, the active drive cycle starts when pwm\_count equals PWMPH1<4:0> and terminates when comparator C1's output goes high (if enabled by PWMPH1<5> = 1) or when comparator C2 output goes high (if enabled by PWMPH1<6> = 1).

When COMOD<1:0> = 10, the duty cycle is controlled only by the PWM Phase counter. In this mode, the active drive cycle starts when the pwm\_count equals PWMPH1<4:0> and terminates when the pwm\_count equals PWMPH2<4:0>. For example, free running 50% duty cycle can be accomplished by setting COMOD<1:0> = 10 and choosing appropriate values for PWMPH1<4:0> and PWMPH2<4:0>.

When COMOD<1:0> = 11, the duty cycle is controlled by the phase counter or feedback through comparator C1 or C2. For example, in this mode, the maximum duty cycle is determined by the values of PWMPH1<4:0> (duty cycle start) and PWMPH2<4:0> (duty cycle end). The duty cycle can be terminated earlier than the maximum by feedback through comparator C1 or C2.

#### 13.9.1 DEAD BAND CONTROL

The Complementary Output mode facilitates driving series connected MOSFET drivers by providing dead band drive timing between each phase output (see Figure 13-6). Dead band times are selectable by the CMDLY<4:0> bits of the PWMCON1 register. Delays from 0 to 155 nanoseconds (typical) with a resolution of 5 nanoseconds (typical) are available.

## 13.9.2 OVERLAP CONTROL

Overlap timing can be accomplished by configuring the Complementary mode for the desired output polarity and overlap time (as dead time) then swapping the output connections and inverting the outputs. For example, to configure a complementary drive for 55 ns of overlap and an active-high drive output on PH1 and an active-low drive output on PH2, set the PWM control registers as follows:

- Connect PH1 driver to PH2 output

- Connect PH2 driver to PH1 output

- Initialize PORTC<1> to 1 (PH2 driver off)

- Initialize PORTC<4> to 0 (PH1 driver off)

- Set TRISC<1,4> to 0 for output

- Set PWMPH1<POL> to 1 (Inverted PH1)

- Set PWMPH2<POL> to 1 (Non-Inverted PH2)

- Set PWMCON1 for 55 ns delay and desired termination (comparator, count or both)

- Set PWMCON0 desired SYNC and auto-shutdown configuration and to enable PH1 and PH2

#### 13.9.3 SHUTDOWN IN COMPLEMENTARY MODE

During shutdown the PH1 and PH2 complementary outputs are forced to their inactive states (see Figure 13-5). When shutdown ceases the PWM outputs revert to their start-up states for the first cycle which is PH1 inactive (output undriven) and PH2 active (output driven).

## 14.1 EECON1 and EECON2 Registers

EECON1 is the control register with four low-order bits physically implemented. The upper four bits are nonimplemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit, clear it and rewrite the location. The EEDAT and EEADR registers are cleared by a Reset. Therefore, the EEDAT and EEADR registers will need to be re-initialized. Interrupt flag EEIF bit of the PIR1 Register is set when write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

| Note: | The   | EECON1,       | EEDAT      | and      | EEADR    |

|-------|-------|---------------|------------|----------|----------|

|       | regis | ters should i | not be mo  | odified  | during a |

|       | data  | EEPROM w      | rite (WR b | oit = 1) |          |

## REGISTER 14-3: EECON1: EEPROM CONTROL REGISTER

| U-0               | U-0                                                                  | U-0              | U-0 | R/W-x                | R/W-0 | R/S-0              | R/S-0 |

|-------------------|----------------------------------------------------------------------|------------------|-----|----------------------|-------|--------------------|-------|

| —                 | —                                                                    | —                | —   | WRERR                | WREN  | WR                 | RD    |

| bit 7             | bit 7 bi                                                             |                  |     |                      |       | bit 0              |       |

|                   |                                                                      |                  |     |                      |       |                    |       |

| Legend:           |                                                                      |                  |     |                      |       |                    |       |

| R = Readable b    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |     |                      |       |                    |       |

| -n = Value at POR |                                                                      | '1' = Bit is set |     | '0' = Bit is cleared |       | x = Bit is unknown |       |

|                   |                                                                      |                  |     |                      |       |                    |       |

| hit 7-1           | Il Inimpleme                                                         | ntad. Read as '  | o'  |                      |       |                    |       |

| only |

|------|

|      |

|      |

| only |

|      |

0 = Does not initiate an EEPROM read

| Mnemonic,<br>Operands |      | Description                  | Cycles       |       | 14-Bit | Opcode | Status | Natar           |       |

|-----------------------|------|------------------------------|--------------|-------|--------|--------|--------|-----------------|-------|

|                       |      | Description                  |              | MSb   |        |        | LSb    | Affected        | Notes |

|                       |      | BYTE-ORIENTED FILE REGI      | STER OPE     | RATIO | NS     |        |        |                 |       |

| ADDWF                 | f, d | Add W and f                  | 1            | 00    | 0111   | dfff   | ffff   | C,DC,Z          | 1,2   |

| ANDWF                 | f, d | AND W with f                 | 1            | 00    | 0101   | dfff   | ffff   | Z               | 1,2   |

| CLRF                  | f    | Clear f                      | 1            | 00    | 0001   | lfff   | ffff   | Z               | 2     |

| CLRW                  | -    | Clear W                      | 1            | 00    | 0001   | 0xxx   | xxxx   | Z               |       |

| COMF                  | f, d | Complement f                 | 1            | 00    | 1001   | dfff   | ffff   | Z               | 1,2   |

| DECF                  | f, d | Decrement f                  | 1            | 00    | 0011   | dfff   | ffff   | Z               | 1,2   |

| DECFSZ                | f, d | Decrement f, Skip if 0       | 1 <b>(2)</b> | 00    | 1011   | dfff   | ffff   |                 | 1,2,3 |

| INCF                  | f, d | Increment f                  | 1            | 00    | 1010   | dfff   | ffff   | Z               | 1,2   |

| INCFSZ                | f, d | Increment f, Skip if 0       | 1 <b>(2)</b> | 00    | 1111   | dfff   | ffff   |                 | 1,2,3 |

| IORWF                 | f, d | Inclusive OR W with f        | 1            | 00    | 0100   | dfff   | ffff   | Z               | 1,2   |

| MOVF                  | f, d | Move f                       | 1            | 00    | 1000   | dfff   | ffff   | Z               | 1,2   |

| MOVWF                 | f    | Move W to f                  | 1            | 00    | 0000   | lfff   | ffff   |                 |       |

| NOP                   | _    | No Operation                 | 1            | 00    | 0000   | 0xx0   | 0000   |                 |       |

| RLF                   | f, d | Rotate Left f through Carry  | 1            | 00    | 1101   | dfff   | ffff   | С               | 1,2   |

| RRF                   | f, d | Rotate Right f through Carry | 1            | 00    | 1100   | dfff   | ffff   | С               | 1,2   |

| SUBWF                 | f, d | Subtract W from f            | 1            | 00    | 0010   | dfff   | ffff   | C,DC,Z          | 1,2   |

| SWAPF                 | f, d | Swap nibbles in f            | 1            | 00    | 1110   | dfff   | ffff   |                 | 1,2   |

| XORWF                 | f, d | Exclusive OR W with f        | 1            | 00    | 0110   | dfff   | ffff   | Z               | 1,2   |

|                       |      | BIT-ORIENTED FILE REGIS      |              | ATION | IS     |        |        |                 |       |

| BCF                   | f. b | Bit Clear f                  | 1            | 01    | 00bb   | bfff   | ffff   |                 | 1,2   |

| BSF                   | f, b | Bit Set f                    | 1            | 01    | 01bb   | bfff   |        |                 | 1,2   |

| BTFSC                 | f, b | Bit Test f, Skip if Clear    | 1 (2)        | 01    | 10bb   | bfff   | ffff   |                 | 3     |

| BTFSS                 | f, b | Bit Test f, Skip if Set      | 1 (2)        | 01    | 11bb   | bfff   | ffff   |                 | 3     |

| 211.00                | ., 2 |                              |              |       | 1100   | 2111   |        |                 | •     |

| ADDLW                 | k    | Add literal and W            | 1            | 11    | 111x   | kkkk   | kkkk   | C,DC,Z          |       |

| ANDLW                 | k    | AND literal with W           | 1            | 11    | 1001   | kkkk   | kkkk   | Z               |       |

| CALL                  | k    | Call subroutine              | 2            | 10    | 0kkk   | kkkk   | kkkk   |                 |       |

| CLRWDT                | _    | Clear Watchdog Timer         | 1            | 00    | 0000   | 0110   | 0100   | TO,PD           |       |

| GOTO                  | k    | Go to address                | 2            | 10    | 1kkk   | kkkk   | kkkk   |                 |       |

| IORLW                 | k    | Inclusive OR literal with W  | 1            | 11    | 1000   | kkkk   | kkkk   | Z               |       |

| MOVLW                 | k    | Move literal to W            | 1            | 11    | 00xx   | kkkk   | kkkk   |                 |       |

| RETFIE                | _    | Return from interrupt        | 2            | 00    | 0000   | 0000   | 1001   |                 |       |

| RETLW                 | k    | Return with literal in W     | 2            | 11    | 01xx   | kkkk   |        |                 |       |

| RETURN                | _    | Return from Subroutine       | 2            | 00    | 0000   | 0000   | 1000   |                 |       |

| SLEEP                 | _    | Go into Standby mode         | 1            | 00    | 0000   | 0110   | 0011   | TO,PD           |       |

| SUBLW                 | k    | Subtract W from literal      | 1            | 11    | 110x   | kkkk   | kkkk   | C,DC,Z          |       |

|                       | ••   |                              | 1            | 1     |        |        |        | _,_ <b>_</b> ,_ |       |

## TABLE 17-2: PIC16F785/HV785 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

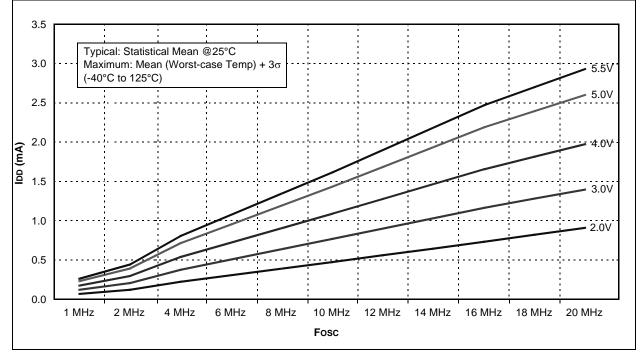

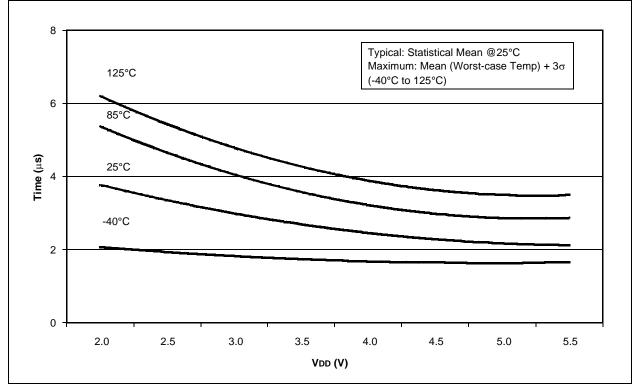

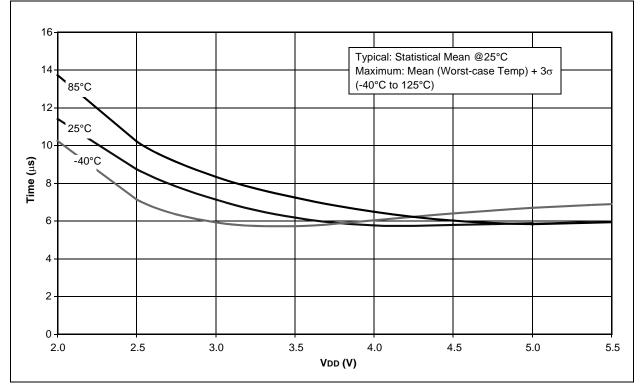

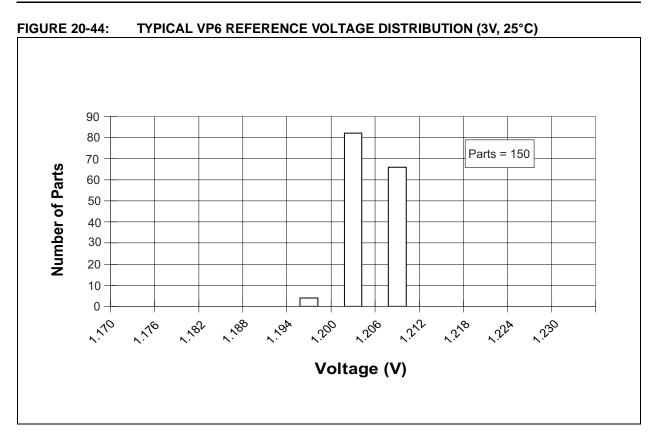

## 20.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

## PIC16F785/HV785

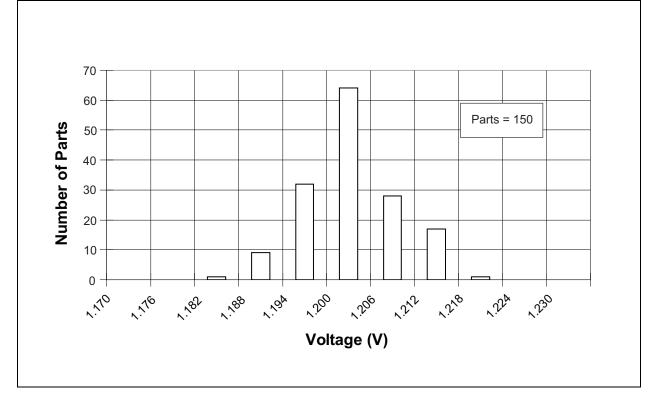

FIGURE 20-45: TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (3V, 85°C)

## INDEX

| Α                                        |

|------------------------------------------|

| A/D                                      |

| Acquisition Requirements86               |

| Analog Port Pins80                       |

| Associated Registers                     |

| Block Diagram                            |

| Calculating Acquisition Time             |

| Channel Selection 80                     |

| Configuration and Operation 80           |

| Configuring                              |

| Configuring Interrupt85                  |

| Conversion Clock                         |

| Effects of Reset                         |

| Internal Sampling Switch (Rss) Impedance |

| Operation During Sleep88                 |

| Output Format81                          |

| Reference Voltage (VREF)80               |

| Source Impedance86                       |

| Special Event Trigger 89                 |

| Specifications159, 160, 161              |

| Starting a Conversion81                  |

| Using the ECCP Trigger 89                |

| Absolute Maximum Ratings141              |

| AC Characteristics                       |

| Load Conditions150                       |

| ADCON0 Register                          |

| ADCON1 Register                          |

| Analog-to-Digital Converter. See A/D     |

| ANSEL Register                           |

| ANSEL0 Register 82                       |

| ANSEL1 Register 82                       |

| Assembler                                |

| MPASM Assembler138                       |

## В

| Block Diagrams                            |     |

|-------------------------------------------|-----|

| (CCP) Capture Mode Operation              |     |

| A/D                                       | 79  |

| Analog Input Model                        |     |

| CCP PWM                                   | 60  |

| Clock Source                              | 23  |

| Comparator 1                              | 64  |

| Comparator 2                              | 66  |

| Compare                                   |     |

| CVref                                     | 71  |

| Fail-Safe Clock Monitor (FSCM)            | 31  |

| In-Circuit Serial Programming Connections | 125 |

| Interrupt Logic                           |     |

| On-Chip Reset Circuit                     |     |

| OPA Module                                | 75  |

| PIC16F785/HV785                           | 5   |

| RA0 Pin                                   |     |

| RA1 Pin                                   |     |

| RA2 Pin                                   |     |

| RA3 Pin                                   |     |

| RA4 Pin                                   |     |

| RA5 Pin                                   |     |

| RB4 and RB5 Pins                          | 43  |

| RB6 Pin                                   |     |

| RB7 Pin                                   |     |

| RC0 and RC1 Pins                          |     |

| RC0, RC6 and RC7 Pins                     |     |

| RC1 Pin                                   |     |

| RC2 and RC3 Pins 47            |

|--------------------------------|

| RC4 Pin 47                     |

| RC5 Pin 48                     |

| Resonator Operation            |

| Timer1 51                      |

| Timer2                         |

| TMR0/WDT Prescaler 49          |

| Two Phase PWM                  |

| Complementary Output Mode 101  |

| Simplified Diagram92           |

| Single Phase Example 98        |

| VR Reference74                 |

| Watchdog Timer (WDT) 121       |

| Brown-out Reset (BOR) 110      |

| Associated Registers112        |

| Calibration 111                |

| Specifications154              |

| Timing and Characteristics 154 |

## С

| C Compilers                                      |       |

|--------------------------------------------------|-------|

| MPLAB C18                                        | . 138 |

| MPLAB C30                                        |       |

| Capture Module. See Capture/Compare/PWM (CCP)    |       |

| Capture/Compare/PWM (CCP)                        | 57    |

| Associated Registers                             |       |

| Associated Registers w/ Capture/Compare/Timer1 . |       |

| Capture Mode                                     |       |

| CCP1 Pin Configuration                           |       |

| Compare Mode                                     |       |

| CCP1 Pin Configuration                           |       |

| Software Interrupt Mode                          |       |

| Special Event Trigger and A/D Conversions        |       |

| Timer1 Mode Selection                            |       |

| Prescaler                                        |       |

| PWM Mode                                         |       |

| Duty Cycle                                       |       |

| Effects of Reset                                 |       |

| Example PWM Frequencies and Resolutions          |       |

| Operation in Power Managed Modes                 |       |

| Operation with Fail-Safe Clock Monitor           |       |

| Setup for Operation                              |       |

| Setup for PWM Operation                          |       |

| Specifications                                   |       |

| Timer Resources                                  |       |

| CCP. See Capture/Compare/PWM (CCP)               |       |

| CCP1CON Register                                 | 57    |

| CCPR1H Register                                  |       |

| CCPR1L Register                                  |       |

| Clock Sources                                    |       |

| CM1CON0                                          |       |

| CM2CON1                                          |       |

| Code Examples                                    |       |

| Assigning Prescaler to Timer0                    | 50    |

| Assigning Prescaler to WDT                       |       |

| Changing Between Capture Prescalers              |       |

| Data EEPROM Read                                 |       |

| Data EEPROM Write                                |       |

| EEPROM Write Verify                              |       |

| Indirect Addressing                              |       |

| Initializing A/D                                 |       |

| Initializing PORTA                               |       |

| Initializing PORTB                               |       |

| Initializing PORTC                               |       |

|                                                  |       |

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | <u>x /xx xxx</u>                                                                                                                                                                                                                                                                             | Examples:                                                                                                                                         |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                | Temperature Package Pattern<br>Range                                                                                                                                                                                                                                                         | <ul> <li>a) PIC16F785 - E/SO 301 = Extended temp.,<br/>SOIC package.</li> <li>b) PIC16F785 - I/ML = Industrial temp., QFN<br/>package.</li> </ul> |

| Device:               | PIC16F785 <sup>(1)</sup> , PIC16HV785 <sup>(1)</sup> , PIC16F785T <sup>(2)</sup> ,<br>PIC16HV785T <sup>(2)</sup> ;<br>VDD range 4.2V to 5.5V<br>PIC16F785 <sup>(1)</sup> , PIC16HV785 <sup>(1)</sup> , PIC16F785T <sup>(2)</sup> ,<br>PIC16HV785T <sup>(2)</sup> ;<br>VDD range 2.0V to 5.5V |                                                                                                                                                   |

| Temperature<br>Range: | $I = -40^{\circ}C \text{ to } +85^{\circ}C \text{ Industrial})$<br>$E = -40^{\circ}C \text{ to } +125^{\circ}C \text{ Extended})$                                                                                                                                                            |                                                                                                                                                   |

| Package:              | ML = QFN<br>P = PDIP<br>SO = SOIC<br>SS = SSOP                                                                                                                                                                                                                                               | Note 1: F = Standard Voltage Range<br>LF = Wide Voltage Range                                                                                     |

| Pattern:              | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                                                                                                                                                                                                    | 2: T = in tape and reel PLCC, and TQFP<br>packages only.                                                                                          |

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

## ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

## ASIA/PACIFIC

India - Bangalore Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

## EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869